Professional Documents

Culture Documents

XC2064 Xilinx

XC2064 Xilinx

Uploaded by

micaelfn0 ratings0% found this document useful (0 votes)

16 views93 pagesOriginal Title

XC2064-Xilinx

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

16 views93 pagesXC2064 Xilinx

XC2064 Xilinx

Uploaded by

micaelfnCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 93

Chapter 4

Designing FPGAs with HDL

Xilinx FPGAs provide the benefits of custom CMOS VLSI and allow

you ‘0 avoid the initial cost, time delay, and risk of conventional

masked gate array devices. In addition to the logic In the CLBs and

IOBs, the XC4000 family and XC5200 family FPGAs contain system-

oriented features such as the following,

+ Global low-skew clock or signal distribution network

+ Wide edge decoders (XC4000 family only)

+ On-chip RAM and ROM (XC4000 family and Spartan)

+ IEEE 1149.1 — compatible boundary sean logic support

+ Flexible I/O with Adjustable Slew-rate Control and Pull-up/

Pull-down Resistors

+ 12-mA sink current per output and 24-mA sink per output pair

+ Dedicated high-speed carry-propagation circuit

You can use these device characteristics to improve resource utiliza

tion and enhance the speed of critical paths in your HDL designs. The

imples in this chapter are provided to help you incorporate thes

system features into your HDL designs,

This chapter includes the following sections.

ew Clock Buffers

+ “Using Global Low-s

section

+ "Using Dedicated Global Set/Reset Resource” section

incoding State Machines” section,

ising Dedlicated 1/0 Decoders” section

+ “Instantiating LogiBLOX Modules” section

‘+ “Implementing Memory” section

iopsys (XSI) Synthesis and Simulation Design Guide — 0401737 01 41

‘Synopsys (XSI) Synthesis and Simulation Design Guide

+ ‘Implementing Boundary Scan (TAG 1149.1)" section

ith IOBs" section

+ ‘Implementing Logic

+ ‘Implementing Multiplexers with Tristate Buffers” section

+ "Using Pipelining” section

+ "Design Hierarchy

section

Using Global Low-skew Clock Buffers

42

For designs with global signals, use global clock bulfers to take

advantage of the low-skew, high-drive capabilities of the dedicated

global buffer tree of the target device. When you use the Insert Pads

command, the FPGA Compiler automatically inserts a BUFG generic

clock bufler whenever an input signal drives a clock signal. The

Xilinx implementation software automatically selects the clock buffer

that is appropriate for your specified design architecture. If you want,

to use a specific global buffer, you must instantiate it.

You can instantiate an architecture-specific buffer if you understand

the architecture and want to specify how the resources should be

used. Each XC40006/L and Spartan device contains four primary

and four secondary global buffers that share the same routing

resources. XCA00DEX/XL/XV devices have sixteen global buffers:

each buffer has its own routing resources. XC5200 devices have four

dedicated global butlers in each comer of the device.

XC4000 EX/XL/XV devices have two different types of global buffer,

Global Low-Skew Buffers (BUFGLS) and Global Early Buffers

(BUFGE). Global Low-Skew buffers are standard global buffers that

should be used for most internal clocking or high anout signals that

must drive a lange portion of the device. There are eight BUFGLS.

buffers available, two in each corner of the device. The Global Early

buffers are designed to provide faster clock access, but CLB access Is

limited to one quadrant of the device. I/O access is also limited. Simi-

latly, there are eight BUFGEs, two in each comer of the device,

Because Global carly and Global Low-Skew Buffers share a single

pad. a single IPAD can drive a BUFGE, BURGLS or both in parallel.

‘The parallel configuration is especially useful for clocking the fast.

capture latches of the device. Since the Global Early and Clobal Low-

‘Skew Buffers share a common input, they cannot be driven by two

Unique signals.

Xilinx Development System

Designing FPGAs with HDL.

You can use the following criteria to help select the appropriate

global buffer for a given design path.

+ The simplest option is to use a Global Low-Skew Buffer.

+ Ifyou wanta faster clock path, use a BUEG. Initially, the software

will try to use a Global Low-Skew Buffer, I timing requirements

are not met, a BURGE is automatically used if possible.

+ Ifa single quadrant of the chip is sufficient for the clocked logle,

and timing requires a faster clock than the Global Low-Skew

buffer, use a Global Early ButTer.

Note: For more information on using the XC4000 EX/XL/XV device

family global buffers, refer to the online Xilinx Data Book or the

Xilinx web site at hitp://wwwailin.com.

For XC4000B/L and Spartan devices, you can use seconclary global

buffers (BUFCS) to buffer high-fanout, low-skew signals that are

sourced from inside the FPGA. To access the secondary global clock

buffer for an internal signal, instantiate the BURGS_F cell, You can

use primary global buffers (BUFGP) to distribute signals applied to

the FPGA from an external source. Intemal signals can be globally

distributed with a primary global buffer, however, the signals must

be driven by an extemal pin,

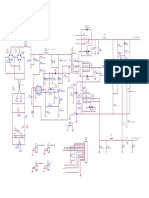

XC4Q00E devices have four primary (BUFGP) and four secondary

(BUFGS) global clock buffers that share four global routing lines, as

shown in the following figure.

‘Synopsys (XSI) Synthesis and Simulation Design Guide 43

‘Synopsys (XSI) Synthesis and Simulation Design Guide

socks

aurcs

Packs

surcs B

|uFGP

aura PGCKE

SEH

FEE as

eurcP

panels!

BUFGP pocKs

euFGP

Figure 4-1 Global Buffer Routing Resources (XC4000E,

Spartan)

44

Xilinx Development System

Designing FPGAs with HDL.

Input Register

Output Register

| fener

Stet

Figure 4-2 Global Butter Routing Resources

These global routing resources are only available for the eight global

buffers. The eight global nets run horizontally across the middle of

the device and can be connected to one of the four vertical longlines

that distribute signals to the CLBs in a column, Because of this

arrangement only four of the eight global signals are available to the

CLBs in a column. These routing resources are “free” resources

because they are outside of the normal routing channels. Use these

resources whenever possible. You may want to use the secondary

bulfers first because they have more flexible routing capabilities.

You should use the global buffer routing resources primarily for high-

fanout clocks that require low skew, however, you can use them to

drive certain CLB pins, as shown in the following figure. In addition,

Synthesis and Simulation Design Guide 45

‘Synopsys (XSI) Synthesis and Simulation Design Guide

46

‘you can use these routing resources to drive high-fanout clock

‘enables, clear lines, and the clock pins (K) of CLBs and 1OBs.

In the figure shown, the C pins drive the input to the H function

‘generator, Direct Data-in, Preset, Clear, or Clock Enable pins. The F

and G pins ate the inputs to the F and G function generators, respec-

tively.

uy wy

Figure 4-3 Global Longlines Resource CLB Connections

If your design does not contain four high-fanout clocks, tse these

routing resources for signals with the next highest fanout, To

routing congestion, use the global buffers to route high-fanout

signals. These high-fanout signals include clock enables and reset

signals (not global reset signals). Use global buffer routing resources

to reduce routing congestion; enable routing of an otherwise

Uunroutable design; and ensure that routing resources are available for

critical nets

Xilinx recommends that you assign up to four secondary global clock

buffers to the four signals in your design with the highest fanout

(such as clock nets, clock enables, and reset signals). Clock signals,

that require low skew have priority over low-fanout non-clock

signals. You can source the signals with an input buffer or a gate

Internal to the design. Generate internally sourced clock signals with

a register to avoid unwanted glitches. The synthesis tool ean Insert

xglobal clock buffers or you can instantiate them in your HDL code.

Xilinx Development System

Designing FPGAs with HDL.

Note: Use Global Set/Reset resources when applicable. Refer to the

“Using Dedicated Global Set/Reset Resource” section in this chapter

for more information,

Inserting Clock Buffers

Note: Refer to the Synopsys (XSI) Interface/Tutorial Guide for more

Information on inserting I/O buffers and clock buffers.

Synopsys tools automatically insert a secondary global clock buffer

6onall input ports that drive a register’s clock pin or a gated clock

signal. To disable the automatic insertion of clock buffers and specify

the ports that should have a clock buffer, perform the following steps

1. Inthe Synopsys Compiler, ports that drive gated clocks or a

register’s clock pin are assigned a clock attribute. Remove this

altribute from ports tagged with the clock attribute by typing:

set_pad_type -no_clock "*”

2, Assign a clock attribute to the input ports that should have a

BUFGS as follows:

set_pad_type -clock {input ports)

3. Enter the following commands:

set_port_is pad “+”

insert_pads

The Insert Pads command causes the FPGA Compiler to auito-

matically insert a clock buffer to ports tagged with a clock

attribute,

To insert a global buifer other than a BUFGS, such as a BUFGP, use

the following commands.

1. Use the following command on all ports with inferred buffers

set_port_is pad “*”

2. Specify the buffer as follows.

set_pad_type exact BUFGP_F (port_list)

You can replace BUFGP_F with another supported buffer for the

device you are targeting, Refer to the Synopsys (XSI) Interface/

Tutorial Guide for list of supported buffers. Port_list specifies the

port(s) for the buffer,

‘Synopsys (XSI) Synthesis and Simulation Design Guide “7

‘Synopsys (XSI) Synthesis and Simulation Design Guide

3. Generate the buffers for the device as follows.

insert_pads

Instantiating Global Clock Buffers

You can instantiate global buflers in your code as described in this

section.

Instantiating Butters Driven from a Port

You can instantiate global buflers and connect them to high-fanout

ports in your code rather than inferring them from a Synopsys script.

Ifyou do instantiate global buffers that are connected toa port, check.

‘your Synopsys script to make sure the Set Port Is Pad command is not

‘specified for the buffer.

set_port_is_pad (ist ofall ports except instantiated_buller port)

insert_pads

set_port_is pad *#”

renove_attribute {instantiated buffe_port) port_is_pad

Ansert_pads

Instantiating Buffers Driven from Internal Logic

You must instantiate a global buffer in your code in order to use the

dedicated routing resource If a high-fanout signal Is sourced from

Internal flip-flops or logie (such as a clock divider or multiplexed

clock), or if clock Is driven from the Internal oscillator or non-ced-

cated 1/0 pin, The following VHDL and Verllog examples are exam-

ples of Instantiating a BUFGS for an internal multiplexed clock

cireult, A Set Dont Touch attribute is adided to the instantiated

‘component.

48 Xilinx Development System

Designing FPGAs with HDL.

+ VHDL.

This is an example of an instantiation of

global buffer (BUFGS) from an internally

driven signal, a multiplexed clock.

duly 1997

Library TEES;

use IEEE.std_logic 1164.al1;

entity clock_mux is

port (DATA, SEL: in sTo_Losrc;

SLOW_CLOCK, FAST_CLOCK: in STD_LOsIC;

Dour: out STD_LOGIC) ;

fend clock mux;

architecture XILINX of clock mux is

signal cLock: sTD_Locic;

signal CLOCK_GBUF: STD_LOSIC;

component BUFGS

port (I: in sTD_LoGrc;

(0: out s7D_LoGrC);

fend component;

process (SEL)

(seL = 11") then

Lock <= FAST_CLOcKy

else

end Sf; ~

end process;

port map (I <> clock,

0 => CLOCK_GBUF) ;

Data_Pat

begin

process (CLOCK_GBUF, DATA)

‘Synopsys (XSI) Synthesis and Simulation Design Guide 49

‘Synopsys (XSI) Synthesis and Simulation Design Guide

AE (CLOCK_GAUF ‘event and CLOCK_GBUP="1') then

DOUT <= DATA;

end ifs

end process;

fend XILINX;

+ Verilog

11 CLOCK_NOX.V uw

// This 48 an example of an instantiation of //

J/ global buffer (BUFGS) from an internally //

// driven signal, a multipled clock. “

11 September 1997 u“

MALATE

nodule clock mux (DATA, SEL, SLOW_CLOCK, FAST_CLOCK, DOUT) ;

input DATA, SEL;

input SLOW_CLOCK, FAST_CLOCK;

output DovT;

reg clock;

wire CLOCK_GBUF;

reg DOUT;

always @ (SEL)

begin

Af (Seb == 1'b1)

CLOCK <= FAST_cLOCK;

else

(CLOCK <= SLON_cLOCK;

end

BUFGS GRUF_FOR_MUX_CLOCK (.0(CLOCK_GBUF), 1 (CLOCK));

always @ (posedge CLOCK_sBUF)

DOUT = DATA;

endnodule

Using Dedicated Global Set/Reset Resource

C4000 and Spartan devices have a dedicated Global Set/Reset

(GSR) net that you can use to initialize all CLBs and IOBs, When the

4.10 Xilinx Development System

Designing FPGAs with HDL.

GSR is asserted, every flip-flop in the FPGA is simultaneously preset

or cleared. You can access the GSR net from the GSR pin on the

STARTUP block or the GSRIN pin of the STARTBUF (VHDL).

Since the GSR net has dedicated routing resources that connect to the

Preset o Clear pin of the flip-flops, you do not need to use general

purpose routing or global buffer resources to connect to these pins. If

‘your design has a Preset or Clear signal that effects every flip-flop in

‘your design, use the GSR net to increase design performance and

reduce routing congestion.

‘The XC5200 family has @ dedicated! Global Reset (GR) net that resets

all device registers. As in the XC4000 and Spartan devices, the

STARTUP or STARTBUF (VHDL) block must be instantiated in your

code in order to access this resource. The XC3000A devices also have

dedicated Global Reset (GR) that is connected to a dedicated device

pin (see device pinout). Since this resource is always active, you do

not need to do anything to activate this feature.

For XC4000, Spartan, and XC5200 devices, the Global Set/Reset (GSR

‘or GR) signal is, by default, set to active high (globally resets device

when logic equals 1). Foran active low reset, you can instantiate an

inverter in your code to invert the global reset signal. The inverter is

absorbed by the STARTUP block and does not use any device

resources (function generators), Even though the inverted signal may

be behaviorally described in your code, Xilinx recommends instanti-

ating the inverter to prevent the mapping of the inverter into a CLB

function generator, and subsequent delays to the reset signal and)

unnecessary use of device resources Also make sure you put a Don’t

‘Touch attribute on the instantiated inverter before compiling your

design. If you do not add this attribute, the inverter may get mapped

into a CLB function generator.

Note: For more information on simulating the Global Set/Reset, see

the "Simulating Your Design” chapter.

Startup State

‘The GSR pin on the STARTUP block or the GSRIN pin on the

STARTBUF block drives the GSR net and connects to each flip-flop's

Preset and Clear pin, When you connect a signal from a pad! to the

STARTUP block's GSR pin, the GSR net is activated. Since the GSR

net is built into the silicon it does not appear in the pre-routed netlist

file. When the GSR signal is asserted High (the default) all flip-flops

‘Synopsys (XSI) Synthesis and Simulation Design Guide 401

‘Synopsys (XSI) Synthesis and Simulation Design Guide

412

and latches are set to the state they were in at the end of configura-

tion. When you simulate the routed design, the gate simulator trans-

lation program correctly models the GSR function,

Note: For the XC3000 family and the XC5200 family, all flip-flops and

latches are reset to zero after configuration.

Preset vs. Clear (XC4000, Spartan)

‘The XC4000 family flip-flops are configured as either preset (asyn-

chronous set) or clear (asynchronous reset). Automatic assertion of,

the GSR net presets or clears each flip-flop. You can assert the GSR

pin at any time to produce this global effect, You can also preset or

lear individual flip-flops with the flip-flop’s dedicated Preset or

Clear pin, When a Preset or Clear pin on a flip-flop is connected to an

active signal, the state of that signal controls the startup state of the

flip-flop. For example, if you connect an active signal to the Preset

pin, the flip-flop starts up in the preset state. If you do not connect the

Clear or Preset pin, the default startup state isa clear state. To change

the default to preset, assign an INIT=S attribute to the flip-flop from

the Synopsys run script, as follows.

set_attribute “ll” fpga_xilinx init_state -type

string *s”

1/0 fiip-flopsand latches do not have individual Preset or Clear pins.

‘The default value of these flip-flops and latches is clear. To change the

default value to preset, assign an INIT=S attribute,

Note: Refer to the Synopsys (XSI) Interface/Tutorial Guide for informa-

ton on changing the initial state of registers that do not use the Preset

or Clear pins.

Increasing Performance with the GSR/GR Net

Many designs contain a net that initializes most of the flip-flops in the

design. If this signal can initialize al the flip-flops, you can use the

GSR/GR net. You should always include a net that initializes your

design to a known state,

‘To ensure that your HDL simulation results at the RTL level match

the synthesis results, write your code so that every flip-flop and latch

is preset or cleared when the GSR signal is asserted. The Synthesis

tool cannot infer the GSR/GR net from HDL code. To utilize the GSR

Xilinx Development System

Designing FPGAs with HDL.

net, you must instantiate the STARTUP or STARTBUF block (VHDL),

as shown in the "No_GSR Implemented with Gates” figure.

Design Example without Dedicated GSR/GR:

Resource

In the following VHDL and Verilog designs, the RESET signal initial

Ives all the registers in the design; however, it does not use the ded

cated global resources, The RESET signal Is routed using regular

routing resources. These designs include two 4-bit counters. One

‘counter counts up and Is reset to all zeros on assertion of RESET and

the other counter counts down and Is reset to all ones on assertion of

RESET. The "No_GSR Implemented with Gates” figure shows the

No_GSR design Implemented with gates.

+ VHDL-No GSR

-- NO_GSR Example

“= The signal RESET initializes all registers

-- May 1997

Library TEE

use TBEE.std_logic_1164.all;

use TBEE.std_logic_unsigned.all

entity no_ger is

port (CLOCK: in STD_Lostc;

RESET: in STD_LOGIC)

UPCHT: out STD_LOGIC VECTOR (3 downto 0);

DNCNT: out STD_LOGIC_VECTOR (3 downto 0));

fend no_gsr;

architecture SIMPLE of ne_gar is

signal UP_CNT: STD_LOGIC_VECTOR (3 downto 0);

signal DN_CNT: STD_LOGIC_VECTOR (3 downto 0);

begin

UP_COUNTER: process (CLOCK, RESET)

begin

Sf (RESET = '1") then

UP_CNT <= "9000";

elsif (CLOCK'event and CLOCK = '1") then

UP_CNT <= UP_CNT + 1;

end iff

‘Synopsys (XSI) Synthesis and Simulation Design Guide 413

‘Synopsys (XSI) Synthesis and Simulation Design Guide

end process;

DNLCOUNTER: process (CLOCK, RESET)

begin

if (RESET = ‘1") then

DN_cwT <= "1111

elsif (CLOCK'event and CLOCK = '1') then

DNLCWT <= DNLCWT = 17

end iff

end process;

DNCNT <= DN_CNT;

end SIMPLE;

+ VHDL-NoGR

NO_GR.VED Example

The signal RESET initializes all registers

Without the use of the dedicated Global Reset routing

December 1997

Library TEE!

use IBEE.std_logic 1164.all;

use TEEE.std_logic_unsigned.all;

entity no_gr is

port (CLOCK: in STD_LocIC;

RESET: in STD_LOGIC;

UPCNT: out STD_LOGIC_VECTOR (3 downto 0);

DNCNT: out STD_LOGIC VECTOR (3 downto 0);

end no_gry

architecture XILINX of ne_gr is

signal UP_CNT: STD_LOGIC_VECTOR (3 downto 0);

signal DN_CNT: STD_LOGIC_VECTOR (3 downto 0);

begin

UP_COUNTER: process (CLOCK, RESET)

begin

if (RESET = '1') then

up_cwt <= "9000";

elsif (CLOCK’event and CLOCK = '1') then

44 Xilinx Development System

Designing FPGAs with HDL.

UB_cwT <= UP_eNT +1;

end iff

end process;

DN_COUNTER: process (CLOCK, RESET)

begin

Af (RESET = '1') then

DNLewT <= "411

elsif (CLOCK’event and CLOCK = '1") then

DN_CNT <= DNLCNT - 17

end if;

end processy

fend XILINX;

+ Verilog - No GSR

(* O_GSR Example

+ Synopsys HDL synthesis Design Guide for FPGAS

+ The signal RESET initializes all registers

* December 1997 */

module no_gst ( CLOCK, RESET, UPCNT, DNCHT) ;

input CLOCK, RESET;

eutput [3:0] UecNT;

output [3:0] pNCNT;

eg [3:0] UPCHT;

reg [3:0] DNCNT;

always & (posedge CLOCK or posedge RESET) begin

Af (RESET) begin

UPCNT = 460000;

DNCNT = 4*bii11;

end else begin

UPCNT = UpcHT + 1'biy

DNCNT = DNCHT - 1'bi;

end

end

fendnedule:

‘Synopsys (XSI) Synthesis and Simulation Design Guide 415

‘Synopsys (XSI) Synthesis and Simulation Design Guide

+ Verilog -No GR

/* WO_GR.V Example

+ The signal RESET initializes all registers

% Aug 1997 4/

nodule no_gr { CLOCK, RESET, UPCNT, DNCNT);

input CLOCK, RESET;

output [3:0] UPCNT;

output [3:0] DNCNT;

reg [3:0] UPCuT;

reg [3:0] DNCNT;

always @ (posedge CLOCK er posedge RESET) begin

if (RESET) begin

UPCNT = 460000;

DNCNT = 4*bi111;

end else begin

UPCNT = UPCHT + L'bI;

DNCHT = DNCHT - 1"B1;

end

end

endnodule

416

Xilinx Development System

Designing FPGAs with HDL.

Figure 4-4 No_GSR Implemented with Gates

Symopsys (XSI) Synthesis and Simulation Design Guide 417

‘Synopsys (XSI) Synthesis and Simulation Design Guide

418

Design Example with Dedicated GSR/GR Resource

‘To reduce routing congestion and improve the overall performance of

the reset net in the No_GSR and No_GR designs, use the dedicated

GSR or GR net instead of the general purpose routing, Instantiate the

STARTUP or STARTBUF block in your design and use the GSR or GR

pin on the STARTUP block (or the GSRIN pin on the STARTBUP

block) to access the global reset net. The modified designs (Use_GSR

and Use_GR) are included at the end of this section. The Use_GSR

«design implemented with gates is shown in. “Use_GSR Implemented

with Gates” figure,

In XC4000 and Spartan designs, on assertion of the GSR net, flip-flops

return toa clear (or Low) state by default. You can override this

default by describing an asynchronous preset in your code, or by

adding the INIT-S attribute to the flip-flop (described later in this

section) from the Synopsys run seript

In XC5200 family designs, the GR resets all flip-flops in the device to

a logic zero, Ifa flip-flop is described as asynchronous preset to a

logie 1, Synopsys automatically infers a flip-flop with a synchronous

preset, and the M1 software puts an inverter on the input and output

of the device to simulate a preset,

‘The Use_GSR and Use_GR designs explicitly state that the down-

counter resets to all ones, therefore, asserting the reset net causes this

counter (0 reset to a default of all zeros. You can use the INIT =.

ute to prevent this reset to zeros.

+ Attach the INIT=S attribute to the down-counter flip-flops as

follows:

set_attribute cell name fpga_xilinx init_state

-type string “Ss”

Note: The "\” character represents a continuation marker.

This command allows you to override the default clear (or Low)

state when your code does not specify a preset condition.

However, since attributes are assigned outside the HDL code, the

code no longer accurately represents the behavior of the design.

Note: Refer to the Synopsys (XSI) Interface/Tutorial Guide for more

Information on assigning attributes,

Xilinx Development System

Designing FPGAs with HDL.

‘The STARTUP block must not be optimized during the synthesis

process, Add a Don’t Touch attribute to the STARTUP or STARTBUF

block before compiling the design as follows:

set_dont_touch cell_instance_name

+ VHDL - Use_GSR (C4000 family)

-- USE_GSR.VHD Example

-- The signal RESET is connected to the GSRIN pin of

<= the STARTAUP block

= May 1987

library TEE?

Library UNISIM;

use IBEE.std_logic 1164.al1;

use TEEE.std_logic_unsigned.all;

use UNISIN.all;

entity use_gsr is

in s7D_Losrc;

+ in STD_LOGIC;

out STD_LOGIC_VECTOR (3 downto 0);

out STD_LOGIC_VECTOR (3 downte 0})7

architecture XILINX of use_ger is

component STARTSUF

port (GSRIN: in STD_LostC);

GSROUT: out STD_LOGIC);

fend component;

signal RESET_INT: STD_Lostc;

signal UP_CHT: STD_LOGIC_VECTOR (3 downto 0);

signal DN_CNT: STD_LOGIC_VECTOR (3 downto 0);

begin

UL: STARTBUF port map(GSRIN->RESET, GSROUT->RESET_INT) ;

UP_COUNTER: process (CLOCK, RESET_INT)

begin

Af (RESET_INT = 111) then

UP_cNT <= "0000";

elsif CLOCK'event and CLOCK =

at) then

‘Synopsys (XSI) Synthesis and Simulation Design Guide

419

‘Synopsys (XSI) Synthesis and Simulation Design Guide

ub_cwt <= uP_ewt - 1;

end iff

end process;

DN_COUNTER: (CLOCK, RESET_INT)

begin

Af (RESETLINT = '1') then

DNLeWT <= "111

eleif CLOCK‘ event and CLOCK = ‘1") then

DN_CNT <= DNLCNT - 17

end if;

end processy

fend XILINX;

+ VHDL-Use_GR

USE_GR.VHD Version 1.0

Xilinx HDL Synthesis Design Guide

The signal RESET initializes all registers

Using the global reset resources since

STARTBUF block waa added

December 1997

library TEE;

Library UNISIM;

use IBEE.std_logic 1164.al1;

use TEEE.std_logic_unsigned. all;

use UNTSIN.all;

entity use_gr is

port ( CLOCK: in STD_Lostc;

RESET: in STD_LOsIC;

UPCHT: out STD_LOGIC VECTOR (3 doxnto 0);

DNCHT: out STD_LOGIC VECTOR (3 doxnto 0);

end use_gr?

architecture XILINX of use_gr is

420 Xilinx Development System

Designing FPGAs with HDL.

component STARTSUF

port (GSRIN: in STD_Losrc;

GSROUT: out STD_LOSIC);

fend component;

signal RESET_INT: STD_Lostc;

signal UP_CHT: STD_LOGIC_VECTOR (3 doxnte 0)

signal DNLCHT: STDLLOSTC_VECTOR (3 downto 0);

begin

UL: STARTBUF port map(GSRIN->RESET, GSROUT->RESET_INT) ;

UP_COUNTER: process (CLOCK, RESET_INT)

begin

Af (RESET_INT = 111) then

UP_cNT <= "0000";

elsif (CLOCK’event and CLOCK = '1') then

UP_CNT <= UP_CNT + 17

fend if;

end process;

DNLCOUNTER: process (CLOCK, RESET_INT)

begin

if (RESET_INT ~ 11") then

DNLeWT <= "2111";

elsif (CLOCK'event and CLOCK = '1") then

DN_CUT <= DILCWT ~ 17

end if;

end process;

upeNT <= UP_cNT;

fend XILINX;

+ Verilog - Use_GSR

TELLTALE

11 USE_GSR.V Version 1.0 wu

// Xilinx HDL synthesis Design Guide “

// The signal RESET initializes all registers //

// Using the global reset resources (STARTUP) //

U1 December 1997 uv

TELLTALE

‘Synopsys (XSI) Synthesis and Simulation Design Guide 421

‘Synopsys (XSI) Synthesis and Simulation Design Guide

module use_gsr ( CLOCK, RESET, UPCNT, DNCHT);

input CLOCK, RESE

output [3:0] UecwT;

output [3:0] DNCNT;

reg [3:0] vPCHT;

reg [3:0] DNCHT;

STARTUP Ul (.GSR(RBSET)) j

always @ (posedge CLOCK or posedge RESET) begin

Af (RESET) begin

UPCNT = 4*b0000;

DNCNT = 4"b1111;

end else begin

UPCNT = UPCHT + 1'bI;

DNCNT = DNCNT - 1'biy

end

end

endnodule

+ Verilog - Use_GR

VTL

11 USE_GR.V Version 1.0 "

// Xilinx AOL Synthesis Design Guide “W

// The signal RESET initializes all registers //

// vsing the global reset resources since //

J] STARTUP block instantiation was added //

11 December 1397 “W

SUT LT

module use_gr ( CLOCK, RESET, UPCNT, DNCNT);

input CLOCK, RESET;

output [3:0] UPCNT;

output [3:0] pNeNT;

reg [3:0] UPCNT;

reg [3:0] pxour;

STARTUP UI (.

GR (RESET) );

422 Xilinx Development System

always @ (posedge CLOCK of posedge RESET) begin

Af (RESET) begin

UPCNT = 4"b0000;

DNCWT = 4"b1111;

end else begin

UPCHT = UPCHT + 1'bi;

DNCHT = DNCHT - 1"biy

end

end

enanoduLe

‘Synopsys (XSI) Synthesis and Simulation Design Guide

Designing FPGAs with HDL.

4.23

‘Synopsys (XSI) Synthesis and Simulation Design Guide

90>

no

Figure 4-5 Use_GSR Implemented with Gates

424 Xilinx Development System

Designing FPGAs with HDL.

Design Example with Active Low GSR/GR Signal

‘The Active_Low_GSR design is identical to the Use_GSR design

except an INV is instantiated and connected between the RESET port

and the STARTUP block, Also, a Set_dont_touch attribute is added! to

the Synopsys script for both the INV and STARTUP or STARTBUF

(VHDL) symbols. By instantiating the inverter, the global set/reset

signal is now active low (logic level 0 resets all FPGA flip-flops), The

inverter is absorbed into the STARTUP block in the device and no

CLB resources are used to invert the signal. VHDL and Verilog

Active_Low_CSR designs are shown following.

+ VHDL - Active Low CSR

= ACTIVE_LON_GSR.VHD Version 1.0

-- Xilinx HDL synthesis Design Guide

-- The signal RESET is inverted before being

<= connected to the GSRIN pin of the STARTEUF

-- The inverter will be absorbed by the STARTSUP

== September 1997

Library IEE=;

Library UNTSIM;

use TBEE.std_logic_1164.all;

use TEBE.sté_logic_unsigned.all;

use UNISIN.all;

entity active_low_gar is

port ( CLOCK: in sTD_LostC;

RESET: in STD_LOGIC;

UPCHT: out STD_LOGIC_VECTOR (3 doxnto 0);

DNCHT: out STD_LOGIC_VECTOR (3 doxnte 0))7

end active_low_gar;

architecture XILINX of active low.

component Tv

port (I: in sT>_Locrc;

0: out stD_LoGrc);

fend component;

component STARTSUP

port (GSRIN: in STD_Losrc;

GSROUT: out STD_LOSIC);

‘Synopsys (XSI) Synthesis and Simulation Design Guide 4.25

‘Synopsys (XSI) Synthesis and Simulation Design Guide

fend component;

signal RESETNOT: — STD_LOGIC

signal RESETNOT_INT: sTD_LOGIC;

signal UP_cNT: STD_LOGIC_VECTOR (3 downto 0);

signal DN_cNT: STD_LOGIC_VECTOR (3 downto 0);

begin

UL: INV port map(I => RESET, 0 => RESET_NOT);

U2: STARTBUF port map (GSRIN->RESET_NOT,

(GSROUT=>RESET_NOT_INT) ;

UP_COUNTER: process (CLOCK, RESET_NOT_INT)

begin

Af (RESET_NOT_INT = 11") then

uP_cwT <= "9000";

elsif (CLOCK’event and CLOCK = '1") then

UP_CNT <= UP_CNT + 1;

end iff

end process;

DILCOUNTER: process (CLOCK, RESET_NOT_INT)

begin

Af (RESET_NOT_INT = 11") then

DNLCWT <= "1111

elsif (CLOCK'event and CLOCK = '1") then

DMLCNT <= DNLCWT = 1;

end iff

end process;

DNCNT <= DN_eNT;

fend XILINX;

+ Verilog - Active low GSR

TULLE

1) ACTIVE_LOW_GSR.V Version 1.0

// Xilinx BDL Synthesis Design Giude

// The signal RESET is inverted before being

“

uv

a

// connected to the GSR pin of the STARTUP block //

// The inverter will be absorbed by STARTUP in M1 //

426

Xilinx Development System

Designing FPGAs with HDL.

// Inverter is instantiated to avoid being mapped //

11 inte a LUT by Synopsys “

11 Septenber 1997 u“

MALLETT

module active low_gsr ( CLOCK, RESET, UPCNT, DNCNT);

snput CLOCK, RESET;

output [3:0] uecnT;

output [3:0] DNCNT;

wire RESET_NOT;

eg [3:0] UPCNT;

eg [3:0] DNCNT;

INV UL (.O(RESET_NOT), -1(RESET));

STARTUP U2 (.GSR(RESET_NOT) };

always @ (posedge CLOCK or posedge RESET_NOT)

begin

if (RESET_NOT)

begin

UECHT = 4*50000;

DNeWT = 4p1112;

end

else

begin

UPeNT = UPCHT + 1'BL;

DNeNT = DNCHT - 1"bI;

end,

end

endnodule

Encoding State Machines

‘The traditional methods used to generate state machine logic result in

highly-encoded states, State machines with highly-encodled state

variables typically have minimum number of flip-flops and wide

‘combinatorial functions. These characteristics are acceptable for PAL,

and gate array architectures. However, because FPGAs have many

flip-flops and narrow function generators, highly-encoded state vari-

ables can result in inefficient implementation in terms of speed and

density.

‘Synopsys (XSI) Synthesis and Simulation Design Guide 427

‘Synopsys (XSI) Synthesis and Simulation Design Guide

‘One-hot encoding allows you to ereate state machine implementa-

tions that are more efficient for FPGA architectures. You ean create

state machines with one flip-flop per state and decreased width of

combinatorial logie. One-hot encoding is usually the preferred

method for large FPGA-hased state machine implementation. For

small state machines (fewer than 8 states), binary encoding may be

more efficient. To improve design performance, you ean divide lange

(greater than 32 states) state machines into several small state

machines and use the appropriate encoding style for each.

Three design examples are provided in this section to illustrate the

three coding methods (binary, enumerated type, and one-hot) you

‘can use to create state machines. All three examples contain an iclen-

tical Case statement. To conserve space, the complete Case statement

is only included in the binary encoded state machine example; refer

to this example when reviewing the enumerated type and one-hot

examples.

Note: The bold text in each of the three examples indicates the

portion of the code that varies depending on the method used to

encode the state machine.

Using Binary Encoding

The state machine bubble diagram in the following figure shows the

‘operation of a seven-state machine that reacts to inputs A through E

as well as previous-state conditions. The binary encoded method of

coding this state machine is shown in the VHDL and Verilog exam-

ples that follow. These design examples show you how to take a

«design that has been previously encoded (for example, binary

encoded) and synthesize it to the appropriate decoding logic and,

registers. These designs use three flip-flops to implement seven

states,

428 Xilinx Development System

Designing FPGAs with HDL.

Ne

Figure 4-6 State Machine Bubble Diagram

VHDL - Binary Encoded State Machine Example

RINARY.VHD Version 1.0

-- Example of a binary encoded state machine

== Xilinx HDL synthesis Design Guide for FPGAS

May 1597

Library TEE!

use TBEE.std_logic 1164.al1;

use TEEE.std_logic_unsigned.all;

entity binary is

port (CLOCK, RESET : in STD_LOGIC;

By By C; Dy B: in BOOLEAN?

SINGLE, MULTI, CONTIG: out STD_LoGIC);

end binary;

architecture BEHV of binary is

type STATE TYPE is (S1, 52, 83, S4, 85, 86, 87);

attribute ENUM ENCODING: STRING;

attribute ENUM ENCODING of STATE TYPE:type is

aaa";

001 010 011 100 101 110

Symopsys (XSI) Synthesis and Simulation Design Guide 429

‘Synopsys (XSI) Synthesis and Simulation Design Guide

signal CS, NS: STATE_TYPE;

begin

SYNC_PROC: process (CLOCK, RESET)

begin

if (RESET-'1") then

cs <= sl;

elsif (CLOCK'event and CLOCK = '1") then

cs <= NS;

end iff

end process; --End REG_PROC

CoMB_PROC: process (CS, A, By C, Dy B)

begin

case CS is

when SI

MULTE

contre

if (A and not B and ¢) then

NS <= S27

elsif (A and B and not Cc) then

NS < 54;

else

NS <= Sty

end if;

when $2 —)

MULTE <= 2

coutie <= '0

SINGLE <= '0

if (not D) then

NS <= 83;

else

Ns <= $4

end if;

when $3 ->

MULTI <= "0";

CONTIG <= '1'}

SINGLE <= 10";

Af (A or D) then

NS <= $4;

else

MS < 53;

4:30

Xilinx Development System

Designing FPGAs with HDL.

end ify

when s4

MULTE <= ‘18

contig <= 11";

SINGLE <= "0";

Af (@ and B and not c) then

NS <= 85;

else

NS

wort <4;

coNtEG <= "0";

SINGLE <= '0"

NS <= $6

when $6 —>

MULTE <= '0";

CONTIG <= 1";

SINGLE <= '1"

4£ (not E) then

NS <= 87;

else

us

fend ifs

when S7 ->

MULTI <= ‘0";

CONTIG <= ‘15;

SINGLE <= "0";

if (E) then

NS <= Sly

else

us <= 81;

end if;

end case;

end process; -- End COMB_PROC

fend BERY;

Verilog - Binary Encoded State Machine Example

TALULALLLLLL TALL ALLTEL

// BINARY.V Version 1.0 “

// Bxample of a binary encoded state machine //

// Xilink HDL Synthesis Design Guide for FPGAS //

AY May 1387 “

TELLTALE LLL LETTE

‘Synopsys (XSI) Synthesis and Simulation Design Guide 431

‘Synopsys (XSI) Synthesis and Simulation Design Guide

module binary (CLOCK, RESET, A, By C, D, Ey

SINGLE, MULTI, CONTIG);

input CLOCK, RESET;

input Ay By Cy Dy Ey

output SINGLE, MULTI, CONTIG;

reg SINGLE, MULTI, CONTIG;

// Declare the symbolic names for states

paraneter [2:0] //synopsys enum STATE_TYPE

s1 = 3°B001,

52 = 3'a10,

583 = 3*b011,

4 - 3°B100,

85 = 3°B101,

56 = 3'b110,

87 = 3'b111;

// Declare current state and next state variables

eg [2:0] /* synopsys enum STATETYPE */ CS;

reg [2:0] /* synopsys enum STATE_TYPE */ NS}

/1 synopsys state_vector cs

always @ (posedge CLOCK or posedge RESET)

begin

Af (RESET == 1'b1)

cs = Sly

else

cs = Ns;

end

always @ (CS or A or B or C or D or D or &)

begin

case (CS) //synopsys full_case

si:

begin

MOLTE = 1'b0;

contis = 1'b0;

SINGLE = 1'20;

if (ae -B Ec)

us = 82;

else if (A ke B && =C)

4:32 Xilinx Development System

Ns = $4;

else

NS = 51)

end

2:

begin

MOLTT = 1'b1;

contre = 1'»0;

SINGLE = 120;

Af (1D)

us = 53;

else

Ns = st;

end

53:

begin

MULTE = 1";

conrrG = 1'b1;

SINGLE = 1'b0}

4£ (a IL DD

NS = $4;

else

NS = 53;

end

st:

begin

MOLTE = 1'b1;

contre = bi;

SINGLE = 1'20;

if (ae Bae

NS = 85;

else

Ns = sa;

end

35:

begin

MOLE = 1'b1;

courts = 1'»0;

SINGLE = 1b0;

MS = S65

end

S68:

begin

MOLE = 1'b0;

contis = 1'b1;

‘Synopsys (XSI) Synthesis and Simulation Design Guide

Designing FPGAs with HDL.

4.33

‘Synopsys (XSI) Synthesis and Simulation Design Guide

SINGLE

if (1B)

us

else

Ns

te

end

37:

begin

MULTE

contis

SINGLE,

if (B)

NS = sly

else

Ns

a%b0;

abi

10;

end

endease

end

endnedule

Using Enumerated Type Encoding

434

‘The recommended encoding style for state machines depends on

which synthesis tool you are using, You can explicitly declare state

vectors or you can allow the Synopsys tool to determine the vectors.

Synopsys recornmends that you use enumerated type encoding to

specify the states and use the Finite State Machine (FSM) extraction

‘commands to extract and encocte the state machine as well as to

perform state minimization and optimization algorithms, The

‘enumerated type method of encoding the seven-state machine is

shown in the following VHDL and Verilog examples. The encoding

style is not defined in the code, but can be specified later with the

FSM extraction commands. Alternatively, you can allow the

‘Synopsys compiler to select the encoding style that results in the

lowest gate count when the design is synthesized.

Note: Refer to the previous VHDL and Verilog Binary Encoded State

‘Machine examples for the complete Case statement portion of the

code,

Xilinx Development System

Designing FPGAs with HDL.

VHDL- Enumerated Type Encoded State Machine

Example

Library TEBE;

use IEEE.std_logic 1164.al1;

entity enum is

port (CLOCK, RESET : in STD_LOGIC;

Ay By C, Dy Ez in BOOLEAN;

SINGLE, MULTI, CONTIG: out STD_LOGIC);

fend enum;

architecture BENV of enum ie

type STATE TYPE is (S1, 52, 83, 54, 55, 56, 57);

signal cs, NS: STATE_TYPE;

begin

SYNC_PROC: process (CLOCK, RESET)

begin

if (RESET="1") then

cs <= si

elsif (CLOCK'event and CLOCK = '1") then

end if;

fend process; --End sytc_pRoc

coms_pROC: process (C3, A, B, Cy Dy B)

begin

MULTE <= tot;

courie <= to";

SINGLE <= "0";

‘Synopsys (XSI) Synthesis and Simulation Design Guide 4.35

‘Synopsys (XSI) Synthesis and Simulation Design Guide

TALL TALE TLL

1) BNUM.V Version 1.0 “

// Bxample of an enunerated encoded state machine //

// Rilinx HDL synthesis Design Guide for FPGAS //

11 May 1997 au

TTT LEA

module enum (CLOCK, RESET, Ay By Cr Dy Ey

SINGLE, MULTI, CONTIG) ;

input CLOCK, RESET;

input Ay By Cy Dy By

output SINGLE, MULTI, CONTIG;

reg SINGLE, MULTI, conTIG;

// Declare the symbolic names for states

paraneter [2:0] //synopsys enum STATE_TYPE

S1 = 3°B000,

52 = 3*B001,

53 = 3*b010,

384 = 3*b011,

$5 - 3°b100,

86 = 3°b101,

87 = 3'b110;

// Declare current state and next state variables

reg [2:0] /* synopays enum STATETYPE */ cS;

reg [2:0] /* synopsys enum STATE_TYPE */ NS;

Jf synopsys state_vector cs

always @ (posedge CLOCK or posedge RESET)

begin

if (RESET == 1'bL}

cS = sly

else

cs = NS;

end

always @ (CS or A or B or C or D or D or E)

begin

4.36 Xilinx Development System

Usi

Designing FPGAs with HDL.

(C8) //synopsys full_case

sl:

begin

MULTI = 1"b0;

conrrG = 1'b0;

SINGLE = 1'b0;

Af (A && ~B Ge C)

Ns = 527

else if (A 66 Be -C)

NS = S47

else

Ns = siz,

end

ing One-Hot Encoding

‘The following examples show a one-hot encoded state machine. Us

this method to control the state vector specification or when you

want to specify the names of the state registers. These examples use

‘one flip-flop for each of the seven states,

Note: Refer to the previous VHDL and Verilog Binary Encoded State

‘Machine examples for the complete Case statement portion of the

code. See the "Accelerate FPGA Macros with One-Hot Approach”

appendix for a detailed description of one-hot encoding and its appli:

cations,

VHDL - One-hot Encoded State Machine Example

Library TeEE;

use IEEE.std_logic 1164.al1;

use TERE.std_logic_unsigned.all;

entity one_hot is

port (CLOCK, RESET : in STD_LOGIC;

A

B,C, Dy B: in BOOLEAN;

SINGLE, MULTI, CONTIG: out STD_LOGIC);

fend one_hoty

architecture BEHV of one_hot is

‘Synopsys (XSI) Synthesis and Simulation Design Guide 437

‘Synopsys (XSI) Synthesis and Simulation Design Guide

type STATE TYPE is (S1, $2, $3, S4, $5, 86, 87);

attribute ENUM ENCODING: STRING;

attribute ENUM_ENCODING of STATE_TYP!

(9001000 0010000 0100000 1000000 *.

type is "0000001 0000010 0000100

signal CS, NS: STATE_TYPE;

begin

SYNC_PROC: process (CLOCK, RESET)

begin

if (RESET-"1") then

cs <8;

elsif (CLOCK"event and CLOCK = '1") then

cs <= Ns;

end if;

end process; --End S¥Nc_pRoc

COMB_PROC: process (CS, A, By C, Dy B)

begin

case CS is

when S1 =>

MULTI. <= tot;

conTIS <= '0';

SINGLE <= "0"

Af (A and not B and ¢) then

NS <= 52;

elsif (A and B and not c) then

Ns < 84;

else

WS <= Si;

end ifs

4.38

Xilinx Development System

Designing FPGAs with HDL.

Verilog - One-hot Encoded State Machine Example

TALTEEL LLL TLL LLL

// ONB_HOT.¥ Version 1.0 uw

// Bxample of @ one-hot encoded state machine //

J/ Xilinx HDL synthesis Design Guide for FPGAS //

AY May 1387 “

TTL LALLA LATTA

module one_hot (CLOCK, RESET, Ay By Cy Dy Ey

SINGLE, MULTI, CONTIG);

input CLOCK, RESET)

input, By Cy Dy Ey

output SINGLE, MULTI, conTrG;

reg SINGLE, MULTI, CONTIG;

// declare the symbolic nanes for states

parameter [6:0] //synopsys enum STATS TYPE

si = 7*p0000001,

52 = 7"0000010,

3 - 1"B0000100,

84 = 7'0001000,

85 = 7*b0010000,

36 = 7"B0100000,

87 = 1"B1000000;

// Declare current state and next state variables

reg [2:0] /* synopsys enum STATE_TYPE */ CS;

reg [2:0] /* synopays enum STATETYPE */ NS;

/1 synopsys state_vector CS

always @ (posedge CLOCK or posedge RESET)

begin

if (Reser

cS = Sl;

else

apt)

end

always @ (CS or A or B or C or D or D or &)

begin

case (CS) //synopsys full_case

si

‘Synopsys (XSI) Synthesis and Simulation Design Guide 439

‘Synopsys (XSI) Synthesis and Simulation Design Guide

440

end

begin

MULTI = 1'bO;

CONTIG = 1'b0;

SINGLE = 1'20;

AE (A 66 -B aC)

NS = 52;

else if (A Ge B Ge =C)

NS ~ 54;

else

NS = Sly

Summary of Encoding Styles

In the three previous examples, the state machine's possible states are

defined by an enumeration type. Use the following syntax to define

an enumeration type.

type type_name is (enumeration_iteral {, enumeration literal):

After you have defined an enumeration type, declare the signal repre-

senting the states as the enumeration type as follows:

type STATE_TYPE is S1, $2, $3, $4, $5, $6, $7):

signal CS, NS: STATE_TYPE,

‘The state machine described in the three previous examples has

seven states. The possible values of the signals CS (Current_State)

and NS (Next State) are SI, $2, .. $6, $7,

To select an encoding style for a state machine, specify the state

vectors. Alternatively, you can specify the encoding style when the

state machine is compiled. Xilinx recommends that you specify an

encoding style. IF you do not specify a style, the Synopsys Compiler

selects a style that minimizes the gate count. For the state machine

shown in the three previous examples, the compiler selected the

binary encoded style: $1="000", S2="001", S3="010", S4="011",

S5="100", Sé="101", and S7="110",

You can use the FSM extraction too! to change the encoding style of a

state machine. For example, use this tool to convert a binary-encoded

state machine to a one-hot encoded state machine, The Synopsys.

‘enum.script file contains the commands you need to convert an

Xilinx Development System

Designing FPGAs with HDL.

enumerated types encoded state machine to a one-hot encoded state

machine,

Note: Refer to the Synopsys documentation for instructions on how

to extract the state machine and change the encoding style.

Comparing Synthesis Results for Encoding Styles

The following table summarizes the synthesis results from the

different methods used to encode the state machine in the three

previous VHDL and Verilog state machine examples. The results are

for an XCA005EPC84-2 device

Note: The Timing Analyzer was used to obtain the timing results In

this table.

Table 4-1 State Machine Encoding Styles Comparison

(XC4005E-2)

5 i Enum

Comparison | One-Hot Binary lonetea

‘Occupied CLBS 6 9 6

CLB Flip-flops 6 3 7

PadTosetup [94ns@) _[134ns) _[96n8@)

ClockToPad (151m) [151ns@) [14908 3)

ClockTSewp _[130ns@) __[139ns@) [10.1 ns 8)

_a:The number in parentheses represents the CLB block level delay

‘The binary-encocted state machine has the longest ClockToSetup

delay. Generally, the FSM extraction tool provides the best results

because the Synopsys Compiler reciuces any redundant states and

‘optimizes the state machine after the extraction.

Initializing the State Machine

When you use one-hot encoding, add the following lines of code to

‘your design to ensure that the FPGA Is initialized to a Set state.

+ VHDL.

YYNC_PROC! process (CLOCK, RESET

Symopsys (XSI) Synthesis and Simulation Design Guide 441

‘Synopsys (XSI) Synthesis and Simulation Design Guide

Af (RESET="1") then

cs <= sl;

+ Verilog

always @ (posedge CLOCK or posedge RESET)

begin

if (RESET

cs

Ve

Alternatively, you can assign an INIT=S attribute to the initial state

register to specify the initial state,

set_attribute “cS_reg<0>"\

fpga_xilinx_init_state -type string “s”

Note: The "\" character in this command represents a continuation

marker,

In the Binary Encode State Machine example, the RESET signal forces

the S1 flip-flop to be preset {initialized to 1) while the other flip-flops

are cleared (initialized to 0).

Using Dedicated I/O Decoders

‘The periphery of XC4000 family deviees has four wide decoder

circuits at each edlge. The inputs to each decoder are any of the 1OB

signals on that edge plus one local interconnect per CLB row or

column, Each decoder generates a High output (using a pull-up

resistor) when the AND condition of the selected inputs or their

complements is true, The decoder outputs drive CLB inputs so they

‘can be combined with other logic or can be routed directly to the chip

outputs.

‘To implement XC4000 family edge decoders in HDL, you must

instantiate edge decoder primitives. The primitive names you can use

vary with the synthesis tool you are using. Using the Synopsys tools,

you can instantiate the following primitives: DECODE1_IO,

DECODE!_INT, DECODE4, DECODES, and DECODEI6. These

primitives are implemented using the dedicated 1/0 edge clecoders.

‘The XC4000 family wide decoder outputs are effectively open-drain

and require a pull-up resistor to take the output High when the spec-

ified pattern is detected on the decoder inputs. To attach the pull-up

resistor to the output signal, you must instantiate a PULLUP compo-

nent.

442 Xilinx Development System

Designing FPGAs with HDL.

‘The following VHDL example shows how to use the I/O edge

decociers by instantiating the decode primitives from the XSI library.

Each decoder output is @ function of ADR (IOB inputs) and CLB_INT

(local interconnects). The AND function of each DECODE output and,

Chip Select (CS) serves as the source ofa flip-flop Clock Enable pin.

‘The four edge decoders in this design are placed on the same device

edge. The “Schematie Block Representation of I/O Decoder” figure

shows the schematic block diagram representation of this I/O

decoder design.

VHDL - Using Dedicated /0 Decoders Example

“Bdge Decoder

=-A XC4000 LCA has special decoder circuits at each edge. These decoders

~-are open-drained wired-AND gates. hen one or more of the inputs (I) are

“Low output (0) is Low. When all of the inputs are High, the output is ——

--High.A pull-up resistor must be connected to the output node to achieve

n-a true logic High.

Library ree!

use IBEE.STD_LOGIC_1164-al1;

se TEEE/STD_LOGIC_UNSIGNED all;

entity ic_decoder is

port (ADR: in std logic_vecter (4 downto 0);

C5: in std logics

DATA: in std_logic_vector (3 downto 0);

CLOCK: in std_logic;

QUT: out std logic vector (3 doxnte 0))7

fend to_decoder;

architecture STRUCTURE of io_decoder is

COMPONENT DECODEL_10

PORT ( 1: IN std_logic;

0: OUT std_logic );

END COMPONENT;

component pECoDEL_inr

PORT ( I: IN std_togic;

0: OUT std_legic );

END COMPONENT;

component DECODES

PORT ( A3, A2, Al, AO: IN std logic;

‘Synopsys (XSI) Synthesis and Simulation Design Guide 443

‘Synopsys (XSI) Synthesis and Simulation Design Guide

0: ovT std_legic );

END COMPONENT;

coupowent PULLUP

PORT ( 0: OUT stdlogic 17

END COMPONENT;

Internal Signal peclarations —

signal DECODE, CLKEN, CLB_INT: std_logic_vector (3 downto 0);

signal ADRINV, CLBLINV: std logic vector (3 downto 0);

begin

ADRLINV <= net ADR (3 downto 0);

CLBLINY <= not CLB_INT;

Instantiation of Edge Decoder: output "DECODE(O)" ~

AD: DECODE4 port map (ADR(3), ADR(2), ADR(1), ADR_INV(0}, DECODE(0));

Al: DECODEI_IO port map (ADR(4), DECODE(O));

AZ: DECODEL_INT port map (CLB_INV(0), DECODE(0));

A3: DECODEI_LINT port map (CLB_INT(1), DECODE(0));

Ad: DECODEI_INT port map (CLB_INT(2), DECODE(0));

AS: DECODEI_LINT port map (CLB_INT(3), DECODE(0));

AG: PULLUP port map (DECODE (0) );

Instantiation of Edge Decoder: Output "DECODE(1)" —

DECODE4 port map (ADR(3), ADR(2), ADR_INV(1), ADR(O), DECODE(1));

+ DECODEL_IO port map (ADR(4), DECODE(1));

2: DECODEI_INT port map (CLA_INT(O), DECODE(1))s

3: DECODEI_INT port map (CLB_INV(1), DECODE(1));

B4: DECODEI_INT port map (CLA_INT(2), DECODE(1))s

BS: DECODEI_INT port map (CLB_INT(3), DECODE(1));

B6: PULLUP port map (DECODE(1)}7

4M Xilinx Development System

Designing FPGAs with HDL.

Instantiation of Edge Decoder: Output "DECODE(2)" —

2 DECODE4 port map (ADR(3), ADR_INV(2), ADR(1), ADR(O), DECODE(2));

CL: DECODEI_TO port map (ADR(4}, DECODE(2));

DECODEL_INT port map (CLB_INT(0), DECODE(2));

3+ DECODEI_INT port map (CLB_INT(1), DECODE(2))+

2 DECODEL_INT port map (CLB_INV(2), DECODE(2));

(5+ DECODEI_INT port map (CLB_INT(3), DECODE(2))+

PULLUP port map (DECODE(2));

Instantiation of Edge Decoder: output "DECODE(3)" ~

DO: DECODE4 port map (ADR_INY(3), ADR(2), ADR(1), ADR(O), DECODE(3));

D1

DECODEI_IO port map (ADR(4), DECODE(3)) 3

2: DECODEI_INT port map (CLB_INT(O), DECODE(3));

D3: DECODEI_INT port map (CLA_INT(1), DECODE(3))s

D4: DECODEI_INT port map (CLB_INT(2), DECODE(3))+

DS: DECODEI_INT port map (CLA_INV(3), DECODE(3))s

D6: PULLUP pert map (DECODE(3)}7

CLKEN is the AND function of CS & DECODE:

CLKEN (0) <= CS and DECODE(O)

CLKEN (2) <= CS and DECODE(L);

CLKEN (2) <= CS and DECODE(2);

CLKEN (3) <= CS and DECODE(3);

Internal 41-bit counter —:

process (CLOCK)

begin

Af (CLOCK'event and CLOCK='1") then

CLALINT <= CLINT + 1;

end ifs

fend process;

‘Synopsys (XSI) Synthesis and Simulation Design Guide 4.45

‘Synopsys (XSI) Synthesis and Simulation Design Guide

QOUT(0)" Data Register Enabled by "CLKEN(0)*.

process (CLOCK)

begin

Af (CLOCK‘event and CLock="1") then

Af (CLKEN(0) = 11") then

90UT (0) <= DATA(O);

fend if;

end if

end process;

"Q0UT(1)" Data Register Enabled by "CLKEN(L)"

process. (CLOCK)

begin

Lf (CLOCK‘ event and CLocK="1") then

Af (CEREN(L) = '1*) then

‘QUT (1) <= DATA(I);

end if;

end ify

end process;

‘OUT (2)" Data Register Enabled by "CLEN(2)"~

process (CLOCK)

begin

Af (CLOCK'event and CLOCK="1") then

Af (CLKEN(2) = '1!) chen

(9ur (2) <= DATA(2);

end if;

end if;

end process;

QOUT(3)" Data Register Enabled by "CLAEN(3)*

process (CLOCK)

begin

Af (CLOCK‘event and CLock="1") then

Af (CEREN(3) = '1") then

QOUT (3) <= DATA(3);

end if

end ify

end process;

fend STRUCTURE;

446 Xilinx Development System

Designing FPGAs with HDL.

Figure 4-7 Schematic Block Representation of /O Decoder

Note: In the previous figure, the pull-up resistors are inside the

Decoder blocks.

Instantiating LogiBLOX Modules

Note: Refer to the LogiBLOX Reference/User Guide for detailed instruc-

tons on using LogiBLOX.

Synopsys can infer arithmetic DesignWare modules from VHDL or

Verilog code for these operators: +. <, +1.-1. These

adders, subiracters, comparators, incrementers, andl decrementers

use FPGA dedicated device resources, such as carry logic, to improve

the speed and area of designs, For bus widths greater than four,

DesignWare modules are generally faster unless multiple instances of

the same function are compiled together. For more information on the

DesignWare libraries, refer to the Synopsys (XSI) interface/Tutorial

Guide.

If you want to use a module that Is not in the DesignWare libraries, or

if you want better performance or area, you can use LogiBLOX to

Symopsys (XSI) Synthesis and Simulation Design Guide 447

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Schematic Motherboard Biostar G41D3C PDFDocument32 pagesSchematic Motherboard Biostar G41D3C PDFManuel Prado40% (5)

- Aoc Le50d5530-80Document100 pagesAoc Le50d5530-80micaelfnNo ratings yet

- Aoc Le55d6730-80Document102 pagesAoc Le55d6730-80micaelfnNo ratings yet

- 1ZC12 1ZC120Document3 pages1ZC12 1ZC120micaelfnNo ratings yet

- NUWTR v5.09.04 Support Body ListDocument10 pagesNUWTR v5.09.04 Support Body ListmicaelfnNo ratings yet

- Philips+40PFT5100+TPS15 1A+LADocument112 pagesPhilips+40PFT5100+TPS15 1A+LAmicaelfnNo ratings yet

- SMS Power Vision MPV 2 e 3KVA (T0403707)Document1 pageSMS Power Vision MPV 2 e 3KVA (T0403707)micaelfnNo ratings yet

- User GuideDocument193 pagesUser GuidemicaelfnNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : 4 X 47W MOSFET Quad Bridge Power AmplifierDocument12 pagesObsolete Product(s) - Obsolete Product(s) : 4 X 47W MOSFET Quad Bridge Power AmplifiermicaelfnNo ratings yet

- VideoGame Nº 13Document69 pagesVideoGame Nº 13micaelfnNo ratings yet

- 2A (Inverter) : Comp VCC RT NC CS VCC OUTDocument2 pages2A (Inverter) : Comp VCC RT NC CS VCC OUTmicaelfnNo ratings yet

- Nrf2401A: Single Chip 2.4 GHZ TransceiverDocument40 pagesNrf2401A: Single Chip 2.4 GHZ TransceivermicaelfnNo ratings yet

- RF 300CH 11440 KysanDocument2 pagesRF 300CH 11440 KysanmicaelfnNo ratings yet