Professional Documents

Culture Documents

3/2/1-Phase Synchronous-Rectified Buck Controller For Mobile GPU Power

3/2/1-Phase Synchronous-Rectified Buck Controller For Mobile GPU Power

Uploaded by

Paulo Cohen FariasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

3/2/1-Phase Synchronous-Rectified Buck Controller For Mobile GPU Power

3/2/1-Phase Synchronous-Rectified Buck Controller For Mobile GPU Power

Uploaded by

Paulo Cohen FariasCopyright:

Available Formats

uP9509

3/2/1-Phase Synchronous-Rectified Buck Controller

for Mobile GPU Power

General Description Features

The uP9509 is a 3/2/1-phase synchronous-rectified buck Support NVIDIA’s Open VReg Type-2+ PWMVID

controller specifically designed to work with 4.5V ~ 26V Technology

input voltage and deliver high quality output voltage for high- Wide Input Voltage Range 4.5V ~ 26V

performance graphic processor power.

Robust Constant On-Time Control

The uP9509 adopts proprietary RCOTTM technology, 3/2/1 Phase Operation

providing flexible selection of output LC filter and excellent

transient response to load and line change. Two Integrated MOSFET Drivers with Shoot-

Through Protection and Internal Bootstrap

The uP9509 supports NVIDIA Open Voltage Regulator-2+ Schottky Diode

with PWMVID feature. The PWMVID input is buffered and

Adjustable Current Balancing by RDS(ON) Current

filtered to generate accurate reference voltage, and the

Sensing

output voltage is precisely regulated to the reference input.

Adjustable Operation Frequency

The uP9509 integrates two bootstrapped MOSFET gate

drivers and one PWM output achieving optimal balance External Compensation

between cost and flexibility. The uP9509 uses MOSFET Dynamic Output Voltage Adjustment

RDS(ON) current sensing for channel current balance. Adjustable Per-Phase Over Current Limit

Other features include accurate and reliable over current Power Good Indication

limit protection, adjustable on-time setting, power saving Over Voltage Protection

control input, and power good output. This part is available

Under Voltage Protection

in a VQFN4x4 - 24L package.

Adjustable Soft-Start Time

Ordering Information Over Temperature Protection

RoHS Compliant and Halogen Free

Order Number Package Type Top Marking

uP9509PQAG VQFN4x4 - 24L uP9509P Applications

Middle-High End GPU Core Power

Note:

(1) Please check the sample/production availability with High End Desktop PC Memory Core Power

uPI representatives. Low Output Voltage, High Power Density DC-DC

(2) uPI products are compatible with the current IPC/JEDEC Converters

J-STD-020 requirement. They are halogen-free, RoHS Voltage Regulator Modules

compliant and 100% matte tin (Sn) plating that are suitable

for use in SnPb or Pb-free soldering processes. Pin Configuration

17 UGATE2

16 PGOOD

18 BOOT2

15 ISEN1

14 ISEN2

13 ISEN3

PHASE2 19 12 COMP

LGATE2 20 11 FB

PVCC 21 10 FBRTN

GND

PWM3 22 9 TON

LGATE1 23 8 VREF

PHASE1 24 7 REFIN

BOOT1 1

UGATE1 2

EN 3

PSI 4

VID 5

6

REFADJ

uP9509-DS-C3000, Dec. 2015 1

www.upi-semi.com

uP9509

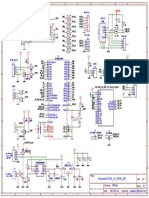

Typical Application Circuit

1.8V

VREF PGOOD

PVCC 5V

REFADJ

VIN = 5V~20V

VSS_SNS REFIN TON

VID BOOT1

EN UGATE1

1.8V

PSI PHASE1 VOUT

ISEN1

VIN = 5V~20V LGATE1

BOOT VCC 5V

UGATE

PWM PWM3

PHASE

BOOT2

LGATE GND

UGATE2

Driver

ISEN3 PHASE2

0.5kohm

COMP ISEN2

FB LGATE2

GND FBRTN

VSS_SNS

VCC_SNS

2 uP9509-DS-C3000, Dec. 2015

www.upi-semi.com

uP9509

Functional Pin Description

N o. Name Pin Function

BOOT for Phase 1. Connect a capacitor form this pin to PHASE1 to form a bootstrap circuit for

1 BOOT1

upper gate driver of the phase 1.

2 UGATE1 Upper Gate Driver for Phase 1. Connect this pin to the gate of phase 1 upper MOSFET.

3 EN Enable. Chip enable.

4 PSI Pow er Saving Input. An input pin receiving power saving control signal from GPU.

5 VID VID. PWMVID input pin.

Reference Adjustment. PWMVID output pin. Connect this pin with an RC integrator to generate

6 REFADJ

REFIN voltage.

Reference Input. Connect this pin to an external reference voltage through a resistor or connect

7 REFIN

to the output of the REFADJ circuit.

Reference Voltage. 2V LDO voltage output pin. Connect an at least 1uF decoupling capacitor

8 VREF

between this pin and GND.

On-time Setting Pin. Connect a resistor from this pin to VIN to set the on-time of the upper

9 TON

MOSFET.

Return for the Reference Circuit. Connect this pin to the ground point where output voltage is

10 FBRTN

to be regulated.

11 FB Feedback Pin. This pin is the inverting input of the error amplifier.

12 COMP Compensation Output. This pin is the output of the error amplifier.

ISEN3. Connect this pin to the PHASE3 pin with 0.5kohm to sense phase 3 output current. DO

13 ISEN3

NOT use other resistor.

14 ISEN2 ISEN2. Connect this pin to the PHASE2 pin with a resistor to sense phase 2 output current.

15 ISEN1 ISEN1. Connect this pin to the PHASE1 pin with a resistor to sense phase 1 output current.

Pow er Good Indication. Open-drain structure. Connect this pin to a voltage source with a pull-up

16 PGOOD

resistor.

17 UGATE2 Upper Gate Driver for Phase 2. Connect this pin to the gate of phase 2 upper MOSFET.

BOOT for Phase 2. Connect a capacitor form this pin to PHASE2 to form a bootstrap circuit for

18 BOOT2

upper gate driver of the phase 2.

Phase Pin for Phase 2. This pin is the return path of upper gate driver for phase 2. Connect a

19 PHASE2

capacitor from this pin to BOOT2 to form a bootstrap circuit for upper gate driver of the phase2.

20 LGATE2 Low er Gate Driver for Phase 2. Connect this pin to the gate of phase 2 lower MOSFET.

Supply Input for the IC. Voltage power supply of the IC. Connect this pin to a 5V supply and

21 PVC C

decouple using at least a 1uF ceramic capacitor.

PWM Output of Phase 3. Connect this pin to the PWM input pin of the companion gate driver.

22 PWM3

Connect this pin to GND when maximum 2 phase operation.

23 LGATE1 Low er Gate Driver for Phase 1. Connect this pin to the gate of phase 1 lower MOSFET.

Phase Pin for Phase 1. This pin is the return path of upper gate driver for phase 1. Connect a

24 PHASE1

capacitor from this pin to BOOT1 to form a bootstrap circuit for upper gate driver of the phase 1.

Exposed Pad Ground. Tie this pin to ground island/plane through the lowest impedance connection available.

uP9509-DS-C3000, Dec. 2015 3

www.upi-semi.com

uP9509

Functional Block Diagram

PGOOD

TON

EN

POR

Soft Start OVP

& UVP POR PVCC

Power OK OTP

BOOT1

OCL

UGATE1

Gate

Control PHASE1

COMP

Logic

LGATE1

REFIN GM On-Time

FB Generation

FBRTN BOOT2

Ramp

OVP OVP Generation Current UGATE2

UVP UVP Balance

Gate

Control PHASE2

Phase Logic

Selection

LGATE2

PSI

PWM3

Linear

VREF PVCC

Regulator

ISEN3

S/H GM

REFADJ

Current ISEN2

H/L S/H GM

VID Limit

Detector

ISEN1

S/H GM

4 uP9509-DS-C3000, Dec. 2015

www.upi-semi.com

uP9509

Functional Description

Supply Input and Power On Reset Voltage Control Loop and PWMVID Function

The uP9509 receives supply input from PVCC pin to provide Figure 2 illustrates the voltage control loop of the uP9509.

current to gate drivers and internal control circuit. PVCC is FB and REFIN are negative and positive inputs of the Error

continuously monitored for power on reset. The POR level Amplifier respectively. The Error Amplifier modulates the

is typical 4.1V at rising. The TON pin voltage is used for COMP voltage VCOMP of buck converter to force FB voltage

on-time calculation and should be connected to the supply VFB follows VREFIN.

input of power stage.

The uP9509 integrates floating MOSFET gate driver that COMP

are powered from the PVCC pin. A bootstrap schottky diode

is embedded to facilitates PCB design and reduce the total

BOM cost. No external Schottky diode is required in real

applications. An external Schottky diode with lower voltage

drop can improve the power conversion efficiency. FB

Phase Number of Operation (Hard-wire Programming) REFIN EA

The uP9509 supports 3/2/1 phase operation. The maximum VREF

phase number of operation is determined by checking the

PWM3 status when POR. Connect PWM3 pin to GND with R2 2V

100kΩ resistor for maximum 2-phase operation; Connect REFADJ

ISEN2 to PVCC with 100kΩ resistor for maximum 1-phase R1

operation. Once selected, the maximum phase number of R3 RSTDBY

operation is latched and can only be changed at the next

POR. C

R4

VSTDBY

Constant On-Time Setting

The uP9509 adopts a compensated constant-on-time R5

control scheme. A resistor RTON connected to TON pin VSS_SNS FBRTN

programs the constant on time according to the equation:

VID

1200 PWMVID

1000 Figure 2. Voltage Control Loop

Switching Frequency (kHz)

The PWMVID signal from GPU is applied to the VID pin,

800 which is the input pin of the internal buffer. This buffer plays

the role of level shifting, and the output of this buffer is

600 injected into the external RC integrator to generate REFIN

voltage, which can be calculated as:

400

VREFIN =

200 R2// (R3 + R4 + R5) R4 + R5

VVREF × D × × +

R1 + R2// (R3 + R4 + R5) R3 + R4 + R5

0

0 200 400 600 800 1000 R1// (R3 + R4 + R5 ) R4 + R5

VVREF × ×

RTON (kΩ) R2 + R1// (R3 + R4 + R5 ) R3 + R4 + R5

Figure 1. Switching Frequency vs. RTON where VREFIN,DC is the DC voltage of REFIN, VVREF is the

voltage of VREF (typically 2V), and D is the duty cycle of

VOUT RTON PWMVID input.

TON ( ns ) = × × 100 (ns)

VIN 9

where RTON is in kΩ, VIN is the supply input voltage and

VOUT is the output voltage.

uP9509-DS-C3000, Dec. 2015 5

www.upi-semi.com

uP9509

Functional Description

Boot Voltage and Standby Mode

The new generation PWMVID structure includes two ISEN3

operation modes other than normal operation: boot mode Current

Balance GM

and standby mode. During boot mode, the GPU stops Amplifier

sending PWMVID signal and the input of the PWMVID buffer ICS1

ISEN2

is floating. The REFADJ pin enters high impedance state ICS2 Sample &

ICS3 Hold

after the VID pin enters tri-state region, and the REFIN GM

voltage can then be calculated as: Amplifier

Over Current

Limit

R4 + R5 ISEN1

VREFIN,BOOT = VVREF ×

R 2 + R3 + R 4 + R5 GM

Amplifier VDC

During standby mode, other than GPU stopping the

PWMVID transaction, an external system standby signal

additionally controls the entry of standby mode. An

additional external switch should be connected in parallel Figure 4. RDS(ON) Current Sensing Scheme

with the original PWMVID resistors as shown in Figure 3 The GM amplifier senses the voltage drop across the low-

to generate the standby mode voltage: side MOSFET and converts it into current signal each time

it turns on. The sampled and held current is expressed as:

VREFIN,STDBY =

(R3 + R4 + R5) // RSTDBY × R4 + R5 ICSX =

(ILX × RDS(ON) + VDC )

VVREF ×

R2 + (R3 + R4 + R5) // R STDBY R3 + R4 + R5

RISENX

where ILX is the phase N current in Ampere, RDS(ON) is the

on-resistance of low-side MOSFET of the power stage in

REFIN mΩ, VDC is an internal 30mV voltage source, and RISENX is

VREF

the external sensing resistor connected at ISENx pins. In

this current sense mechanism, the valley of the inductor

R2 2V current is sampled and held. Therefore, the equivalent

REFADJ sensed current can be described by the following equation:

R1

1

R3 RSTDBY

ILX _ SH = ILX _ AVG − × ∆ILX

2

C

R4

VSTDBY

The sensed current ILX_SH is mirrored to the current balance

circuit, comparing between each other, and generating

R5

current adjusting signals for each phase. These current

VSS_SNS FBRTN adjusting signals are fed to the on-time circuit of the uP9509

VID to separately adjust each phase on-time for the purpose of

adjusting current balance.

PWMVID

Soft-Start and Power Good

Figure 3. Standby Mode Configuration

A built-in soft-start is used to prevent surge current from

Channel Current Balance power supply input during turn on. The error amplifier is a

The uP9509 senses phase currents for current balance by three-input device. Reference voltage VREFIN or the internal

the means of on-resistance of power stage low-side soft-start voltage SS whichever is smaller dominates the

MOSFET as shown in Figure 4. behavior of the non-inverting inputs of the error amplifier.

SS internally ramps up to PVCC with a slew rate

determined by VREFIN after the soft start cycle is initiated.

Accordingly, the output voltage will follow the SS signal

and ramp up smoothly to its target level. The output voltage

ramp-up time can be selected through a resistor which is

connected from LGATE2 to GND. The output ramp-up

selection table shown as following table.

6 uP9509-DS-C3000, Dec. 2015

www.upi-semi.com

uP9509

Functional Description

Over Current Limit

RLG2 Output Voltage Ramp Up Time

The uP9509 monitors the inductor valley current by low

15k 150us side MOSFET RDS(ON) when it turns on. The over current

limit is triggered once the sensing current level is higher

20k 500us

than VOC. When triggered, the over current limit will keep

30k 1ms high side MOSFET off even the voltage loop commands it

to turn on.

Open 1.5ms

The output voltage will decrease if the load continuously

Table 1. Output Ramp Up Time Setting demands more current than current limit level. The current

Power Saving Mode limit threshold is set by connecting a resistor (Roc) from

LGATE1 to GND. The voltage across PHASE and GND pins

The uP9509 provides power saving features for platform is compared with VOC for current limit. The current limit

designers to program platform specific power saving threshold is calculated as:

configuration. There are four operation modes: multi-phase

CCM, multi-phase DCM, single-phase CCM, and single- VOC (mV ) I RIPPLE

phase DCM. The uP9509 switches between these four I LIM (A ) = +

RDS (ON ) 2

operation modes according to the input voltage level of the

PSI pin. Figure 5 shows typical PSI application circuit, And , Roc resistance can be calculated as:

and table 1 shows recommended PSI setting voltage level

500mV

of four operation modes. In single-phase operation, the ROC (kΩ ) =

uP9509 auto-selects phase 1 to be the operating phase. In VOC (mV ) − 20mV 255

× (uA ) + 5uA

DCM, the uP9509 automatically reduces switching 180mV 8

frequency at light load to maintain high efficiency. As the

load current decreases, the rectifying MOSFET is turned VOC is the per-phase GND-PHASE voltage when the power

off when zero inductor current is detected, and the converter stage low-side MOSFETs is turned-on; RDS(ON) is the on-

runs in discontinuous conduction mode. resistance of equivalent per-phase power stage low side

MOSFET and IRIPPLE is the peak-to-peak inductor ripple

1.8V current at steady state.

Over Voltage Protection (OVP)

PSI

The OVP is triggered if VFB > 1.5xVREFIN sustained 6us.

Power State

H-L Logic

Selection When OVP is activated, the uP9509 turns on all low-side

MOSFET and turns off all high-side MOSFET. The over

voltage protection is a latch-off function and can only be

reset by PVCC re-POR or EN restart.

Figure 5. PSI application circuit Under Voltage Protection (UVP)

The under voltage protection is triggered if VFB < 0.5xVREFIN

Operation Mode Recommended Voltage Setting at PSI sustained 10us. When UVP is activated, the uP9509 turns

off all high-side and low-side MOSFET. The under voltage

Multi-Phase CCM 1.8V

protection is a latch-off function and can only be reset by

Multi-Phase DCM 1.2V PVCC re-POR or EN restart.

Single-Phase CCM 0.6V Over Temperature Protection (OTP)

Single-Phase DCM GND The uP9509 monitors the temperature of itself. If the

temperature exceeds typical 150oC, the uP9509 is forced

Table 2. Recommended PSI Setting into shutdown mode. The over temperature protection is a

latch-off function and can only be reset by PVCC re-POR

or EN restart.

uP9509-DS-C3000, Dec. 2015 7

www.upi-semi.com

uP9509

Absolute Maximum Rating

(Note 1)

Supply Input Voltage, PVCC ----------------------------------------------------------------------------------------------------------- -0.3V to +6.5V

BOOTx to PHASEx

DC ---------------------------------------------------------------------------------------------------------------------------------------- -0.3V to +6V

PHASEx to GND

DC ---------------------------------------------------------------------------------------------------------------------------------------- -0.7V to +28V

< 100ns ----------------------------------------------------------------------------------------------------------------------------------- -8V to +36V

BOOTx to GND

DC ---------------------------------------------------------------------------------------------------------------------------------------- -0.3V to +34V

< 100ns ----------------------------------------------------------------------------------------------------------------------------------- -5V to +42V

UGATEx to PHASEx

DC ---------------------------------------------------------------------------------------------------------------------------------------- -0.3V to +6V

< 100ns ----------------------------------------------------------------------------------------------------------------------------------- -5V to +7V

LGATEx to GND

DC ---------------------------------------------------------------------------------------------------------------------------------------- -0.3V to +6V

< 100ns ----------------------------------------------------------------------------------------------------------------------------------- -5V to +7V

Other Pins ------------------------------------------------------------------------------------------------------------------------------------- -0.3V to +6V

Storage Temperature Range ----------------------------------------------------------------------------------------------------------- -65oC to +150oC

Junction Temperature ------------------------------------------------------------------------------------------------------------------------------------ 150oC

Lead Temperature (Soldering, 10 sec) ------------------------------------------------------------------------------------------------------------ 260oC

ESD Rating (Note 2)

HBM (Human Body Mode) --------------------------------------------------------------------------------------------------------------------- 2kV

MM (Machine Mode) ----------------------------------------------------------------------------------------------------------------------------- 200V

Thermal Information

Package Thermal Resistance (Note 3)

VQFN4x4 - 24L θJA --------------------------------------------------------------------------------------------------------------------- 40oC/W

VQFN4x4 - 24L θJC ----------------------------------------------------------------------------------------------------------------------- 4oC/W

Power Dissipation, PD @ TA = 25OC

VQFN4x4 - 24L ------------------------------------------------------------------------------------------------------------------------------------ 2.5W

Recommended Operation Conditions

(Note 4)

Operating Junction Temperature Range ------------------------------------------------------------------------------------------- -40oC to +125oC

Operating Ambient Temperature Range ------------------------------------------------------------------------------------------- -40oC to +85oC

Input Voltage, VIN ---------------------------------------------------------------------------------------------------------------------------- 4.5V to 26V

Control Voltage, VPVCC --------------------------------------------------------------------------------------------------------------------- 4.5V to 5.5V

Note 1. Stresses listed as the above Absolute Maximum Ratings may cause permanent damage to the device. These

are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated

in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions

for extended periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

Note 3. θJA is measured in the natural convection at TA = 25oC on a low effective thermal conductivity test board of

JEDEC 51-3 thermal measurement standard.

Note 4. The device is not guaranteed to function outside its operating conditions.

8 uP9509-DS-C3000, Dec. 2015

www.upi-semi.com

uP9509

Electrical Characteristics

(PVCC = 5V, TA = 25OC, unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Units

Supply Input

VREFIN = 0.9V, EN = 1.8V, VFB = 1V,

Quiescent Current IQ -- 1 -- mA

no switching

Shutdown Current ISHDN E N = 0V -- 2 -- uA

PVCC POR Threshold VPVCCRTH VPVCC rising 3.9 4.1 4.3 V

PVCC POR Hysteresis VPVCCHYS -- 0.3 -- V

VREF Voltage Accuracy VREF 1.98 2 2.02 V

VREF Sourcing Current IREF 10 -- -- mA

Control Input: EN

Logic Low Threshold VEN_L -- -- 0.6 V

Logic High Threshold VEN_H 1.2 -- -- V

Internal Pull-down Current IEN -- 10 -- uA

Reference Voltage

REFIN Disable Threshold -- 0.1 -- V

External Rererence Voltage Range VREFIN 0.2 -- 2 V

On Time

One Shot Width TON VIN = 12V, VOUT = 1.2V, FSW = 300kHz -- 333 -- ns

Minimum Off Time TOFF_MIN -- 300 -- ns

Minimum On Time TON_MIN -- 80 -- ns

Error Amplifier

Open Loop DC Gain AO Guaranteed by Design -- 70 -- dB

Gain Bandwidth Product GEW(EA) Guaranteed by Design -- 10 -- MHz

Offset Voltage VOS(EA) -1 -- 1 mV

Trans-conductance GM -- 2020 -- uA/V

Maximum Current (Source & Sink) ICOMP 300 -- -- uA

Current Sense Amplifier (Current Balance)

Input Offset Voltage VOFF_CSA -1 -- 1 mV

Max Sourcing Current ISRC_CSA 100 -- -- uA

ISENx Voltage V D C _C S A 25 30 35 mV

Internal Current Sense Resistance RSENX_INT -- 4 -- kΩ

FB R TN

FBRTN Current IFBRTN EN = 1.4V, no switching -- -- 500 uA

uP9509-DS-C3000, Dec. 2015 9

www.upi-semi.com

uP9509

Electrical Characteristics

Parameter Symbol Test Conditions Min Typ Max Units

Soft Start

Initialization Time at POR TINIT_POR -- -- 350 us

Initialization Time TINIT -- -- 250 us

PWMVID Buffer

VID Input Low Level VIL_VID -- -- 0.6 V

VID Input High Level VIH_VID 1.2 -- -- V

VID Tri-state Delay TTRI_VID -- 100 -- ns

VREFADJ Source Resistance RBF_SRC ISRC = 1mA -- 20 -- Ω

VREFADJ Sink Resistance RBF_SNK ISNK = 1mA -- 20 -- Ω

PSI

Multi-Phase CCM 1.6 -- -- V

Multi-Phase DCM 1 -- 1.4 V

Power Saving Mode Logic V PSI

Single-Phase CCM 0.4 -- 0.8 V

Single-Phase DCM -- -- 0.2 V

Gate Drivers

Upper Gate Source RUG_SRC IUG = -80mA -- 1 2 Ω

Upper Gate Sink RUG_SNK IUG = 80mA -- 0.5 1 Ω

Lower Gate Source RLG_SRC ILG = -80mA -- 1 2 Ω

Lower Gate Sink RLG_SNK ILG = 80mA -- 0.4 0.8 Ω

Dead Time TDT -- 30 -- ns

Internal Bootstrap Schottky Diode

Forward Voltage VF Forward Bias Current = 3.5mA -- 0.33 -- V

Zero Current Detection Threshold

Zero Current Threshold VZC -0.5 -- 0.5 mV

Protection

OCP Threshold VOC 20 -- 200 mV

OVP Threshold VOVP VFB/VREFIN 150 -- -- %

UVP Threshold VUVP VFB/VREFIN 40 -- 50 %

O

OTP Threshold -- 150 -- C

Pow er Good Indicator

PGOOD Output Low Level ISINK = 4mA -- -- 0.3 V

Leakage Current V P G = 5V -- -- 0.1 uA

10 uP9509-DS-C3000, Dec. 2015

www.upi-semi.com

uP9509

Package Information

VQFN4x4 - 24L

0.30 - 0.50

2.30 - 2.80

2.30 - 2.80

3.90 - 4.10

3.90 - 4.10 0.18 - 0.30

Bottom View - Exposed Pad

Pin 1 mark

0.80 - 1.00

0.0 - 0.05 0.20 REF

Note

1.Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

2.Dimensions in Millimeters.

3.Drawing not to scale.

4.These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

uP9509-DS-C3000, Dec. 2015 11

www.upi-semi.com

uP9509

Important Notice

uPI and its subsidiaries reserve the right to make corrections, modifications, enhancements, improvements, and other

changes to its products and services at any time and to discontinue any product or service without notice. Customers

should obtain the latest relevant information before placing orders and should verify that such information is current and

complete.

uPI products are sold subject to the taerms and conditions of sale supplied at the time of order acknowledgment.

However, no responsibility is assumed by uPI or its subsidiaries for its use or application of any product or circuit; nor

for any infringements of patents or other rights of third parties which may result from its use or application, including but

not limited to any consequential or incidental damages. No uPI components are designed, intended or authorized for

use in military, aerospace, automotive applications nor in systems for surgical implantation or life-sustaining. No license

is granted by implication or otherwise under any patent or patent rights of uPI or its subsidiaries.

COPYRIGHT (C) 2015, UPI SEMICONDUCTOR CORP.

uPI Semiconductor Corp. uPI Semiconductor Corp.

Headquarter Sales Branch Office

9F.,No.5, Taiyuan 1st St. Zhubei City, 12F-5, No. 408, Ruiguang Rd. Neihu District,

Hsinchu Taiwan, R.O.C. Taipei Taiwan, R.O.C.

TEL : 886.3.560.1666 FAX : 886.3.560.1888 TEL : 886.2.8751.2062 FAX : 886.2.8751.5064

12 uP9509-DS-C3000, Dec. 2015

www.upi-semi.com

You might also like

- Description Features: The Future of Analog IC TechnologyDocument20 pagesDescription Features: The Future of Analog IC TechnologyValdir KoxinhaprNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFAnalia Madeled Tovar JimenezNo ratings yet

- Bare-Hand Live-Line Work Safety: BCM Series of Boom Current MonitorsDocument2 pagesBare-Hand Live-Line Work Safety: BCM Series of Boom Current MonitorsRogério Paião0% (1)

- Service Manual: HR-S3902U, HR-S3912U, HR-S3912U, HR-S5902U, HR-S5912U, HR-S5912UDocument20 pagesService Manual: HR-S3902U, HR-S3912U, HR-S3912U, HR-S5902U, HR-S5912U, HR-S5912URenatoMaia0% (1)

- Clevo, 71r A14HV6 T840Document40 pagesClevo, 71r A14HV6 T840Jonathan BiondiNo ratings yet

- Panasonic Tc-L32e5 CH La35 PDFDocument69 pagesPanasonic Tc-L32e5 CH La35 PDFAnonymous h80fVW100% (1)

- Pioneer sc-89 sc-87 rrv4550 Av Receiver PDFDocument89 pagesPioneer sc-89 sc-87 rrv4550 Av Receiver PDFAlexandru PădeanuNo ratings yet

- Fuente 32ld874ht PDFDocument13 pagesFuente 32ld874ht PDFies837No ratings yet

- Kirisun PT8100-Service-ManualDocument35 pagesKirisun PT8100-Service-ManualRobertino100% (1)

- Service Manual: Mini Component Sound SystemDocument44 pagesService Manual: Mini Component Sound SystemAndres Florentin Pizarro Lazarte100% (1)

- Mobile Communications Product GuideDocument2 pagesMobile Communications Product GuideЖељко Гелић100% (1)

- Green-Mode PWM Controller With Frequency Trembling and Integrated ProtectionsDocument18 pagesGreen-Mode PWM Controller With Frequency Trembling and Integrated ProtectionsAndres AlegriaNo ratings yet

- IT8720F CxsDocument1 pageIT8720F CxslioNo ratings yet

- Nobreak NhsDocument1 pageNobreak Nhsatomo33100% (2)

- LGP55-13LPB Eay62811001 Pldk-L212aDocument75 pagesLGP55-13LPB Eay62811001 Pldk-L212aSebastián OctavianoNo ratings yet

- Panasonic TX-40DX600E LA64Document93 pagesPanasonic TX-40DX600E LA64Marcelo Silvano PenedoNo ratings yet

- Esq Nobreak T0319500 Net SensationDocument1 pageEsq Nobreak T0319500 Net SensationrenanNo ratings yet

- 1 2 3 Vin Vout: Presonus Audio Electronics, IncDocument5 pages1 2 3 Vin Vout: Presonus Audio Electronics, IncJJ MMNo ratings yet

- Turnstile 61-200-3103 User ManualDocument20 pagesTurnstile 61-200-3103 User ManualGuillermo GarciaNo ratings yet

- Schematic - Ampcontrol f103 - Ampcontrol f103 2.8 Ili9341 SPI - 20190212135815 PDFDocument1 pageSchematic - Ampcontrol f103 - Ampcontrol f103 2.8 Ili9341 SPI - 20190212135815 PDFmarius tanjalaNo ratings yet

- Alimentation JinglingDocument23 pagesAlimentation Jinglingmarciovirtuatec1013No ratings yet

- Boost Controller For Wled Driver in Medium-Sized LCD Panel: (Top View)Document14 pagesBoost Controller For Wled Driver in Medium-Sized LCD Panel: (Top View)Loengrin MontillaNo ratings yet

- HP 15 Quanta Y19C Y11A VINE Y33 PV DAY11AMB6E0 IT8987E SchematicsDocument34 pagesHP 15 Quanta Y19C Y11A VINE Y33 PV DAY11AMB6E0 IT8987E Schematicsyeneider barlizaNo ratings yet

- Denon Avr-1908 788 ServiceDocument260 pagesDenon Avr-1908 788 ServiceClaudio Hector Arrosa100% (1)

- APC Silcon 60 80kW 208 480V User Guide PDFDocument34 pagesAPC Silcon 60 80kW 208 480V User Guide PDFft1ft1No ratings yet

- 8131 DatasheetDocument9 pages8131 DatasheetLuis AbrahamNo ratings yet

- LG 42PJ250-SA Chassis PB02ADocument70 pagesLG 42PJ250-SA Chassis PB02AamaralfassNo ratings yet

- LG Eay62609701 Pspi-L103aDocument23 pagesLG Eay62609701 Pspi-L103aIvanilto Martins da Cruz100% (1)

- 11 Schematic DiagramDocument95 pages11 Schematic DiagramAdriaan VorsterNo ratings yet

- SOD-80 (Melf) DiodesDocument3 pagesSOD-80 (Melf) DiodesWalter MarquezNo ratings yet

- SOYEA LCD Service Manual PDFDocument40 pagesSOYEA LCD Service Manual PDFraipedriNo ratings yet

- 2N7002 (W4R)Document4 pages2N7002 (W4R)DuanReisNo ratings yet

- Uninterruptible Power Supply Circuitry Design Apc Smartups 1000Document19 pagesUninterruptible Power Supply Circuitry Design Apc Smartups 1000Negru P. PlantatieNo ratings yet

- BM 81004 MuvDocument52 pagesBM 81004 MuvHamza Abbasi AbbasiNo ratings yet

- Irs 2092Document18 pagesIrs 2092Hernan Ortiz EnamoradoNo ratings yet

- Ap 3502 em Regulador DCDC s1005Document11 pagesAp 3502 em Regulador DCDC s1005gerson evandro hanauerNo ratings yet

- Schematic - Xiegu G90 - PWR - SectionDocument1 pageSchematic - Xiegu G90 - PWR - Sectionmy_scribd_20100607No ratings yet

- TV LCD Treinamento SamsungDocument119 pagesTV LCD Treinamento SamsungCabral RANo ratings yet

- Megmeet mp113 Led Power Supply PDFDocument12 pagesMegmeet mp113 Led Power Supply PDFH S Mann100% (1)

- Lenovo E130 Quanta LI2 AMD Brazos Rev 2.0 Schematic DiagramDocument40 pagesLenovo E130 Quanta LI2 AMD Brazos Rev 2.0 Schematic DiagramЮрий ПокровскийNo ratings yet

- Single Synchronous Buck Controller: RT8202/A/BDocument18 pagesSingle Synchronous Buck Controller: RT8202/A/BMax ReparNo ratings yet

- Datasheet LD7523 PDFDocument18 pagesDatasheet LD7523 PDFIvica ConićNo ratings yet

- DW1601 DW1702 DW1703 DW1705 DW1707 and DW1901 Release Notes CS WIN81 Combo 02 09 2015Document17 pagesDW1601 DW1702 DW1703 DW1705 DW1707 and DW1901 Release Notes CS WIN81 Combo 02 09 2015FernandoFloresNo ratings yet

- Bazooka W2DU 1Document5 pagesBazooka W2DU 1ChasNo ratings yet

- SD6109Document10 pagesSD6109Alonso Corado100% (1)

- Power Supply 40-PWL20C-PWI1XG Philips TCS1.0L LA PDFDocument2 pagesPower Supply 40-PWL20C-PWI1XG Philips TCS1.0L LA PDFIader SalgadoNo ratings yet

- Sp431 High Voltage Adjustable Precision Shunt RegulatorsDocument11 pagesSp431 High Voltage Adjustable Precision Shunt Regulatorsagmnm1962No ratings yet

- Service Manual KSDT863Document24 pagesService Manual KSDT863osmel100% (1)

- C550 ICL Schematics: Capacitor ResistorDocument106 pagesC550 ICL Schematics: Capacitor ResistoryencoNo ratings yet

- BenQ FP222WH Product Service Manual Level 2 Version 001Document56 pagesBenQ FP222WH Product Service Manual Level 2 Version 001Mateja RadičevićNo ratings yet

- D 450Document6 pagesD 450Jose Benavides100% (1)

- Catalog 2013Document38 pagesCatalog 2013Mahmoud ElrefaeyNo ratings yet

- Schema Generator Max038Document8 pagesSchema Generator Max038gibonulNo ratings yet

- Videocon - Chassis Nano3 CST - Nano4 CSTDocument29 pagesVideocon - Chassis Nano3 CST - Nano4 CSTchanchaldatta0% (1)

- uP1624P uPISemiconductorDocument18 pagesuP1624P uPISemiconductorSony SanNo ratings yet

- Rt8816a-06 Gtx1070 Gigabyte MemoriasDocument21 pagesRt8816a-06 Gtx1070 Gigabyte Memoriastechgamebr85No ratings yet

- Dual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocument21 pagesDual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesДмитрий НичипоровичNo ratings yet

- DS8816ADocument21 pagesDS8816AAgustin AyalaNo ratings yet

- Up1605 uPISemiconductorDocument23 pagesUp1605 uPISemiconductorRBN HMNo ratings yet

- FEBFL7732 - L26U017B: User Guide ForDocument20 pagesFEBFL7732 - L26U017B: User Guide Fornmo1122No ratings yet

- Service Manual: Room Air ConditionerDocument114 pagesService Manual: Room Air Conditionernmo1122No ratings yet

- Cisco - Comandos e Configurações (Nardelis)Document5 pagesCisco - Comandos e Configurações (Nardelis)nmo1122No ratings yet

- Q1900M PDFDocument55 pagesQ1900M PDFnmo1122No ratings yet

- PD55B2-Drv 150uh L9101: 100KF RQ9102 1KF RQ9104Document2 pagesPD55B2-Drv 150uh L9101: 100KF RQ9102 1KF RQ9104nmo1122100% (1)

- BN44 00508BDocument6 pagesBN44 00508BAntonio Carlos100% (1)

- Q1900M PDFDocument55 pagesQ1900M PDFnmo1122No ratings yet

- Matrix Glitcher TutorialDocument19 pagesMatrix Glitcher TutorialAlessandro MajoniNo ratings yet

- Axle Tech Datos TecnicosDocument2 pagesAxle Tech Datos TecnicosFredy VelazquezNo ratings yet

- Esab Origomig l405 2Document2 pagesEsab Origomig l405 2Hairu LuckyNo ratings yet

- Astable MultivibratorDocument38 pagesAstable MultivibratorSherry Sher0% (1)

- Shoji Lamp PDFDocument2 pagesShoji Lamp PDFBenivaldo Do Nascimento JuniorNo ratings yet

- Airbus Commercial Aircraft AC A330Document630 pagesAirbus Commercial Aircraft AC A330César Gómez AlgarraNo ratings yet

- Ultra GammaView Aluminus 4555 - U12-40720-ManualDocument1 pageUltra GammaView Aluminus 4555 - U12-40720-ManualDNo ratings yet

- Verification Manual: WR Written By: The Soilvision Systems Ltd. Team Last Updated: Tuesday, February 20, 2018Document49 pagesVerification Manual: WR Written By: The Soilvision Systems Ltd. Team Last Updated: Tuesday, February 20, 2018Nilthson Noreña ValverdeNo ratings yet

- L30-L132 RSDocument8 pagesL30-L132 RSMaulana FathanyNo ratings yet

- Two Linguistic Treatises On The Patagonian or Teheulche PDFDocument51 pagesTwo Linguistic Treatises On The Patagonian or Teheulche PDFCarito SuarezNo ratings yet

- Circular MotionDocument15 pagesCircular MotionARUNESH PRATAP SINGHNo ratings yet

- Study of Consumer Preference Towards Cadbury and Nestle ChocolatesDocument74 pagesStudy of Consumer Preference Towards Cadbury and Nestle ChocolatesDeepak TansarNo ratings yet

- Strategic Methods For Talaash Who Only A Few Know About.20121210.184809Document2 pagesStrategic Methods For Talaash Who Only A Few Know About.20121210.184809anon_378198209No ratings yet

- Elastimold TerminalesDocument12 pagesElastimold TerminalesLeonel OjedaNo ratings yet

- PP Mother AssessmentDocument10 pagesPP Mother Assessmentapi-455745761100% (1)

- 8.isotonik SolutionDocument3 pages8.isotonik SolutionGovindan KanapathyNo ratings yet

- Ginni International Limited-1Document17 pagesGinni International Limited-1Charanpreet SinghNo ratings yet

- Book Slides Managing Epidemic WHODocument255 pagesBook Slides Managing Epidemic WHOAatif HussainNo ratings yet

- Parker - Hydraulic CylinderDocument30 pagesParker - Hydraulic Cylinderalvaromviegas_191514No ratings yet

- Subspaces of Vector Spaces Math 130 Linear AlgebraDocument2 pagesSubspaces of Vector Spaces Math 130 Linear AlgebraKothapalli Likhith Sri SaiNo ratings yet

- Simulator TutorialsDocument29 pagesSimulator TutorialstmadamolekunNo ratings yet

- Car Maintenance Basics: Owner's ManualDocument8 pagesCar Maintenance Basics: Owner's ManualAmer GonzalesNo ratings yet

- JOURNAL Sharps Management and The Disposal of Clinical WasteDocument5 pagesJOURNAL Sharps Management and The Disposal of Clinical WasteVincent ReyesNo ratings yet

- The House That Ruth Built A New Stadium, The First Yankees ChamDocument456 pagesThe House That Ruth Built A New Stadium, The First Yankees ChamLeighNo ratings yet

- BloodHorseDaily 20230928Document26 pagesBloodHorseDaily 20230928colabdullasiamNo ratings yet

- Food Safety and Skill TheoryDocument121 pagesFood Safety and Skill Theorywiljhon guilotNo ratings yet

- Anakem PsDocument5 pagesAnakem PsZetsu BlackNo ratings yet

- Lesson # 1 The Voice of God: Questions From Previous Board PapersDocument26 pagesLesson # 1 The Voice of God: Questions From Previous Board PapersmunawarNo ratings yet

- True False Not Given (Reading)Document5 pagesTrue False Not Given (Reading)Công Dương NguyễnNo ratings yet

- Inoculum Development For Industrial Fermentation PDFDocument15 pagesInoculum Development For Industrial Fermentation PDFSabarishNo ratings yet

- Case Study On PIA CrisesDocument2 pagesCase Study On PIA CrisesNadeem Ansari100% (1)