Professional Documents

Culture Documents

Sorting The Numbers in Ascending Order AIM: EXP - NO: 1 DATE: 10.09.09

Uploaded by

manishas121Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sorting The Numbers in Ascending Order AIM: EXP - NO: 1 DATE: 10.09.09

Uploaded by

manishas121Copyright:

Available Formats

EXP.

NO: 1

DATE : 10.09.09

SORTING THE NUMBERS IN ASCENDING ORDER

AIM

To write a program for sorting the given numbers in ascending order by using

8086.

ALGORITHM

i. Initialize the needed registers.

ii. Compare the successive numbers stored in register array.

iii. If lesser go to step v.Else go to next step.

iv. Rearrange the array contents and repeat the procedure.

v. If the count is not zero go to step ii.Else decrement the counter and repeat

the process.

vi. Stop the program.

PROGRAM

ADDRESS MNEMONICS

1000 MOV CL, 10

1003 MOV CH, 0

1006 DEC CH

1008 XOR DI, DI

100A MOV BX, 1200

100E MOV DL, [BX+DI+1]

1011 CMP DL, [BX+DI+2]

1014 JBE 101F

1016 MOV AH, [BX+DI+2]

1019 MOV [BX+DI+2], DL

101C MOV [BX+DI+1], AH

MEC 1 DEPARTMENT OF ECE

101F INC DI

1020 DEC CH

1022 JNZ 100E

1024 DEC CL

1026 JNZ 1003

1028 HLT

OBSERVATION

ADDRESS INPUT OUTPUT

1201 09 01

1202 35 02

1203 22 04

1204 40 05

1205 05 06

1206 02 07

1207 06 09

1208 07 22

1209 04 35

120A 01 40

RESULT

Thus the program was executed and the result was verified.

MEC 2 DEPARTMENT OF ECE

EXP.NO: 2

DATE : 10.09.09

SORTING THE NUMBERS IN DESCENDING ORDER

AIM

To write a program for sorting the given numbers in descending order by

using 8086.

ALGORITHM

i. Initialize the needed registers.

ii. Compare the successive numbers stored in register array.

iii. If lesser go to step v Else go to next step.

iv. Rearrange the array contents and repeat the procedure.

v. If the count is not zero then go to step ii.Else decrement the counter and

repeat the process.

vi. Stop the program.

PROGRAM

ADDRESS MNEMONICS

1000 MOV CL, 10

1003 MOV CH, 10

1006 DEC CH

1008 XOR DI, DI

100A MOV BX, 1200

100E MOV DL, [BX+DI+1]

1011 CMP DL, [BX+DI+2]

1014 JAE 101F

1016 MOV AH, [BX+DI+2]

1019 MOV [BX+DI+2], DL

101C MOV [BX+DI+1], AH

MEC 3 DEPARTMENT OF ECE

101F INC DI

1020 DEC CH

1022 JNZ 100E

1024 DEC CL

1026 JNZ 1003

1028 HLT

OBSERVATION

ADDRESS INPUT OUTPUT

1201 09 40

1202 35 35

1203 22 22

1204 40 09

1205 05 07

1206 02 06

1207 06 05

1208 07 04

1209 04 02

120A 01 01

RESULT

Thus the program was executed and the result was verified.

EXP.NO: 3

MEC 4 DEPARTMENT OF ECE

DATE : 10.09.09

SEARCHING A NUMBER IN AN ARRAY

AIM

To write a program for searching a number in the given array using 8086.

ALGORITHM

i. Initialize the needed registers.

ii. Compare the number to be searched with those stored in the array.

iii. If equal, go to next step. Else repeat the procedure.

iv. Stop the program.

PROGRAM

ADDRESS MNEMONICS

1000 MOV DL, 12H

1003 MOV CL, 09

1006 MOV BX, 1800H

100A MOV CH, 00H

100D MOV DI, 0000H

1011 MOV DH, [BX+DI+1]

1014 CMP DL, DH

1016 JE 1024

1018 INC DI

1019 DEC CL

101B JNZ 1011

101D MOV [1300],CH

1021 JMP 1028

1024 MOV [1300], DL

1028 HLT

MEC 5 DEPARTMENT OF ECE

OBSERVATION

ADDRESS INPUT OUTPUT

1800 09

1801 01

1802 02

1803 03

1804 04

12

1805 05

1806 06

1807 07

1808 08

1809 12

RESULT

Thus the program was executed and the result was verified.

MEC 6 DEPARTMENT OF ECE

EXP.NO: 4

DATE : 17.09.09

LENGTH OF A STRING

AIM

To write a program to determine the length of a string by using 8086.

ALGORITHM

i. Initialize the needed registers.

ii. Compute the length of the string and store the result in specified register.

iii. Stop the program.

PROGRAM

ADDRESS MNEMONICS

1000 MOV SI, 1200

1004 MOV DX, 0000H

1008 MOV AH, 00

100B MOV AL, [SI]

100D INC SI

100E CMP AH, AL

1010 JZ 1016

1012 INC DX

1013 JMP 100B

1016 MOV [1300], DX

101A HLT

MEC 7 DEPARTMENT OF ECE

OBSERVATION

ADDRESS INPUT OUTPUT

1200 AB

1201 CD

1202 EE

05

1203 AE

1204 BC

1205 00

RESULT

Thus the program was executed and the result was verified.

MEC 8 DEPARTMENT OF ECE

EXP.NO: 5

DATE :17.09.09

PACKING AND UNPACKING

AIM

To write a program to pack & unpack the numbers using 8086.

ALGORITHM

i. Initialize the needed registers.

ii. Load the input value.

iii. Clear the MSB.

iv. Rotate LSB 4 times left and move to AL.

v. AND AX with D0F0.

vi. Move the LSB of AX to AL.

vii. Load the input value to the AL.

viii. Add AL&BL.

ix. HLT.

MEC 9 DEPARTMENT OF ECE

PROGRAM FOR PACKING

ADDRESS MNEMONICS

1000 MOV AL,[1300]

1004 MOV AH, 00

1008 MOV CL, 04H

100B ROL AL, CL

100D AND AX, 00F0H

1012 MOV BL, AL

1017 MOV AL, [1301]

101B AND AL, BL

101D MOV [1302], AL

1022 HLT

OBSERVATION

ADDRESS INPUT ADDRESS OUTPUT

1300 03

1302 32

1301 02

MEC 10 DEPARTMENT OF ECE

PROGRAM FOR UNPACKING

ADDRESS MNEMONICS

1000 MOV AL,[1300]

1004 MOV AH, 00

1008 AND AX, 00F0H

100C MOV CL, 04H

1010 ROR AL, CL

1012 MOV [1301], AL

1016 MOV AL, [1300]

101A MOV AH, 00H

101E AND AX, 000F

1024 MOV [1302], AL

1028 HLT

OBSERVATION

ADDRESS INPUT ADDRESS OUTPUT

1301 03

1300 32

1302 02

RESULT

Thus the program was executed and the result was verified.

EXP.NO: 6

DATE : 24.09.09

MEC 11 DEPARTMENT OF ECE

1’s COMPLEMENT AND 2’s COMPLEMENT

AIM

To write a program to 1’s & 2’s complement of the given number using 8086.

ALGORITHM

i. Initialize the needed register.

ii. Load AX with the data.

iii. Take NOT of AX.

iv. Move the content in AX to [1400].

v. Stop the program.

1’S COMPLEMENT PROGRAM

ADDRESS MNEMONICS

1000 MOV AX,1234

1004 NOT AX

1006 MOV [1400],AX

100A HLT

OBSERVATION

ADDRESS INPUT ADDRESS OUTPUT

1400 CB

1000 1234

1401 ED

2’S COMPLEMENT PROGRAM

MEC 12 DEPARTMENT OF ECE

ADDRESS MNEMONICS

1000 MOV AX, 4231

1004 NEG AX

1006 MOV [1500], AX

100A HLT

OBSERVATION

ADDRESS INPUT ADDRESS OUTPUT

1500 DF

1000 4321

1501 BC

RESULT

Thus the program was executed and the result was verified.

EXP.NO:7

MEC 13 DEPARTMENT OF ECE

DATE : 24.09.09

SOLVING A BOOLEAN EXPRESSION

AIM

To write a program to determine Boolean expression by using 8086.

ALGORITHM

i. Initialize the needed registers and load them with the data.

ii. Perform OR operation with BL &BH.

iii. Perform OR operation with AH&BL.

iv. Perform OR operation with AL&AH.

v. Move the content of the AL to AH.

vi. Stop

PROGRAM

ADDRESS MNEMONICS

1000 MOV AL, [1100]

1003 MOV AH, [1101]

1006 MOV BL, [1102]

1009 MOV BH, [1103]

100C OR BL, BH

100E AND AH, BL

1010 OR AL, AH

1012 MOV [1104], AL

1016 HLT

MEC 14 DEPARTMENT OF ECE

OBSERVATION

F=AB’CDE’+A’BCD (BCD+EFGH)

ADDRESS INPUT

1100 B7

1101 7F

1102 FF

1103 FF

1104 FF

RESULT

Thus the program was executed and the result was verified.

MEC 15 DEPARTMENT OF ECE

EXP.NO: 8

DATE : 01.10.09

FOUR-BIT FULL ADDER

AIM

To simulate a 4-bit full adder in VHDL by using Modelsim simulation tool

with Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

iv. Define structural modeling of 4-bit full adder.

v. End architecture.

BLOCK DIAGRAM

MEC 16 DEPARTMENT OF ECE

VHDL code

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

Entity fourbitadder is

Port ( a : in STD_LOGIC_VECTOR (3 downto 0);

b : in STD_LOGIC_VECTOR (3 downto 0);

cin : in STD_LOGIC;

sum : out STD_LOGIC_VECTOR (3 downto 0);

cout : out STD_LOGIC);

end fourbitadder;

architecture behavioral of fourbitadder is

signal c1,c2,c3 : STD_LOGIC;

component singlebitadder

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

cin : in STD_LOGIC;

sum : out STD_LOGIC;

carry : out STD_LOGIC);

end component;

begin

s1:singlebitadder port map (a(0), b(0), cin, sum(0), c1);

s2:singlebitadder port map (a(1), b(1), c1, sum(1), c2);

s3:singlebitadder port map (a(2), b(2), c2, sum(2), c3);

MEC 17 DEPARTMENT OF ECE

s4:singlebitadder port map (a(3), b(3), c3, sum(3), cout);

end Behavioral;

VHDL code for Single bit adder

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

Entity singlebitadder is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

cin : in STD_LOGIC;

sum : out STD_LOGIC;

carry : out STD_LOGIC);

end singlebitadder;

architecture behavioral of singlebitadder is

begin

sum<=a xor b xor cin;

carry<=(a and b) or (b and cin) or (a and cin);

end Behavioral;

MEC 18 DEPARTMENT OF ECE

OUTPUT WAVEFORM

RESULT

Thus the 4 bit full adder was simulated by using Modelsim simulation tool

with Xilinx ISE.

MEC 19 DEPARTMENT OF ECE

EXP.NO: 9

DATE : 01.10.09

FOUR-BIT FULL SUBTRACTOR

AIM

To simulate a 4-bit full subtractor in VHDL by using Modelsim simulation

tool with Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

iv. Define structural modeling of 4-bit subtractor.

v. End architecture.

BLOCK DIAGRAM

A3 B3 A2 B2 A1 B1 A0 B0

C=1

3

2

3

2

1

FA FA FA FA

BORROW

D3 D2 D1 D0

MEC 20 DEPARTMENT OF ECE

VHDL code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity subtractor is

port(a,b:in std_logic_vector(3 downto 0);

c:in std_logic;

d:out std_logic_vector(3 downto 0);

borrow:out std_logic);

end subtractor;

architecture Behavioral of subtractor is

signal cbar,b0bar,b1bar,b2bar,b3bar:std_logic;

signal b1,b2,b3:std_logic;

component fulladder is

port(A,B,Cin:in std_logic;

S,Co:out std_logic);

end component;

begin

cbar<=not(c);

b0bar<=not(b(0));

b1bar<=not(b(1));

b2bar<=not(b(2));

b3bar<=not(b(3));

MEC 21 DEPARTMENT OF ECE

s1:fulladder port map(a(0),b0bar,c,d(0),b1);

s2:fulladder port map(a(1),b1bar,b1,d(1),b2);

s3:fulladder port map(a(2),b2bar,b2,d(2),b3);

s4:fulladder port map(a(3),b3bar,b3,d(3),borrow);

end Behavioral;

VHDL code for Single bit adder

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

Entity singlebitadder is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

cin : in STD_LOGIC;

sum : out STD_LOGIC;

carry : out STD_LOGIC);

end singlebitadder;

architecture behavioral of singlebitadder is

begin

sum<=a xor b xor cin;

carry<=(a and b) or (b and cin) or (a and cin);

end Behavioral;

MEC 22 DEPARTMENT OF ECE

OUTPUT WAVEFORM

RESULT

Thus the 4 bit subtractor was simulated by using Modelsim simulation tool

with Xilinx ISE.

MEC 23 DEPARTMENT OF ECE

EXP.NO: 10

DATE : 01.10.09

8 - BIT RIPPLE CARRY ADDER

AIM

To simulate a 8 bit ripple carry adder in VHDL by using Modelsim simulation

tool with Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

iv. Define structural modeling of 8-bit ripple carry adder..

v. End architecture.

BLOCK DIAGRAM

MEC 24 DEPARTMENT OF ECE

VHDL Code

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

Entity ripplecounter is

Port ( a,b : in STD_LOGIC_VECTOR (7 downto 0);

cin : in STD_LOGIC;

cout : out STD_LOGIC;

sum : out STD_LOGIC_VECTOR (7 downto 0));

end ripplecounter;

Architecture Behavioral of ripplecounter is

component fulladder

Port ( x : in STD_LOGIC;

y : in STD_LOGIC;

z : in STD_LOGIC;

c : out STD_LOGIC;

s: out STD_LOGIC);

end component;

signal c:std_logic_vector(7 downto 0);

begin

stages:for i in 7 downto 0 generate

lowbit: if i=0 generate

fa1: fulladder port map (a(0),b(0),cin,c(0),sum(0));

MEC 25 DEPARTMENT OF ECE

end generate;

otherbits: if i/=0 generate

fa2: fulladder port map (a(i),b(i),c(i-1),c(i),sum(i));

end generate;

end generate;

cout<=c(7);

end Behavioral;

VHDL code for Full Adder

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

Entity fulladder is

Port ( x : in STD_LOGIC;

y : in STD_LOGIC;

z : in STD_LOGIC;

c : out STD_LOGIC;

s : out STD_LOGIC);

end fulladder;

Architecture Behavioral of fulladder is

begin

s<=x xor y xor z;

c<= (x and y) or (y and z) or (z and x);

end Behavioral

MEC 26 DEPARTMENT OF ECE

OUTPUT WAVEFORM

RESULT

MEC 27 DEPARTMENT OF ECE

Thus the 8- bit ripple carry adder was simulated by using Modelsim

simulation tool with Xilinx ISE.

EXP.NO: 11

DATE : 08.10.09

MULTIPLEXER AND DEMULTIPLEXER

AIM

To simulate multiplexer and demultiplexer in VHDL by using Modelsim

simulation tool with Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

iv. Define dataflow modeling of multiplexer and demultiplexer.

v. End architecture.

BLOCK DIAGRAM OF MULTIPLEXER

MEC 28 DEPARTMENT OF ECE

VHDL code for Multiplexer

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity FOURTOONE is

port(a,b,c,d:IN STD_LOGIC;

s0,s1:IN STD_LOGIC;

e:OUT STD_LOGIC);

end FOURTOONE;

architecture DATAFLOW of FOURTOONE is

signal s0bar,s1bar:STD_LOGIC;

begin

s1bar<=not(s1);

s0bar<=not(s0);

MEC 29 DEPARTMENT OF ECE

e<=(((a and s0bar)and s1bar)or ((b and s0bar)and s1)or((c and s1)and s0bar)or

((d and s0)and s1));

end DATAFLOW;

BLOCK DIAGRAM OF DEMULTIPLEXER

VHDL code for Demultiplexer

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity demux is

port(D,s1,s0:in std_logic;

y0,y1,y2,y3:out std_logic);

end demux;

architecture Behavioral of demux is

begin

y0<=D and(not s1)and(not s0);

MEC 30 DEPARTMENT OF ECE

y1<=D and(not s1)and(s0);

y2<=D and(s1)and(not s0);

y3<=D and(s1)and(s0);

end Behavioral;

OUTPUT WAVEFORM -MULTIPLEXER

MEC 31 DEPARTMENT OF ECE

OUTPUTWAVEFORM-DEMULTIPLEXER

RESULT

Thus the Multiplexer and Demultiplexer was simulated by using Modelsim

simulation tool with Xilinx ISE.

EXP.NO: 12

DATE : 08.10.09

ENCODER

AIM

To simulate an encoder in VHDL by using Modelsim simulation tool with

Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

iv. Define behavioral modeling of encoder.

v. End architecture.

MEC 32 DEPARTMENT OF ECE

BLOCK DIAGRAM OF ENCODER

VHDL code for Encoder

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.NUMERIC_STD.ALL;

entity encoder is

port(A:in std_logic_vector(7 downto 0);

Y:out std_logic_vector(2 downto 0));

end encoder;

architecture Behavioral of encoder is

begin

MEC 33 DEPARTMENT OF ECE

--1:case statement

process(A)

begin

case A is

when "00000001"=>Y<="000";

when "00000010"=>Y<="001";

when "00000100"=>Y<="010";

when "00001000"=>Y<="011";

when "00010000"=>Y<="100";

when "00100000"=>Y<="101";

when "01000000"=>Y<="110";

when "10000000"=>Y<="111";

when others=>Y<="XXX";

end case;

end process;

end Behavioral;

--2:selected signal assignment

with A select

Y<="000" when "00000001",

"001" when "00000010",

"010" when "00000100",

"011" when "00001000",

"100" when "00010000",

"101" when "00100000",

"110" when "01000000",

"111" when "10000000",

"XXX" when others;

end Behavioral;

OUTPUT WAVEFORM:

MEC 34 DEPARTMENT OF ECE

RESULT:

Thus the Encoder was simulated by using Modelsim simulation tool with Xilinx ISE.

EXP.NO: 13

DATE : 22.10.09

DECODER

AIM

To simulate a Decoder in VHDL by using Modelsim simulation tool with

Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

iv. Define behavioral modeling of decoder.

MEC 35 DEPARTMENT OF ECE

v. End architecture.

BLOCK DIAGRAM OF DECODER

VHDL code for Decoder

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.NUMERIC_STD.ALL;

entity decoder is

port(A:in integer range 0 to 7;

Y:out std_logic_vector(7 downto 0));

end decoder;

architecture Behavioral of decoder is

begin

MEC 36 DEPARTMENT OF ECE

--1:case statement

process(A)

begin

case A is

when 0 =>Y<="00000001";

when 1=>Y<= "00000010";

when 2=>Y<="00000100";

when 3=>Y<="00001000";

when 4=>Y<="00010000";

when 5=>Y<="00100000";

when 6=>Y<="01000000";

when 7=>Y<="10000000";

end case;

end process;

end Behavioral;

--2:signal state assignment

with A select

Y<= "00000001"when 0,

"00000010"when 1,

"00000100"when 2,

"00001000"when 3,

"00010000"when 4,

"00100000"when 5,

"01000000"when 6,

"10000000"when 7;

end Behavioral;

--3: for statement

process(A)

begin

for N in 0 to 7 loop

if(A=N)then

MEC 37 DEPARTMENT OF ECE

Y(N)<='1';

else

Y(N)<='0';

end if;

end loop;

end process;

end Behavioral;

OUTPUT WAVEFORM

RESULT

Thus the Decoder was simulated by using Modelsim simulation tool with

Xilinx ISE.

EXP.NO: 14

DATE : 22.10.09

FOUR-BIT COMPARATOR

AIM

To simulate a 4-bit comparator in VHDL by using Modelsim simulation tool

with Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

MEC 38 DEPARTMENT OF ECE

iv. Define dataflow modeling of comparator.

v. End architecture.

BLOCK DIAGRAM OF COMPARATOR

VHDL code for Comparator

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity comparator is

port(a3,a2,a1,a0,b3,b2,b1,b0:in std_logic;

e,gt,lt:out std_logic);

end comparator;

architecture Behavioral of comparator is

signal e3,e2,e1,e0,gt3,gt2,gt1,gt0,lt3,lt2,lt1,lt0:std_logic;

MEC 39 DEPARTMENT OF ECE

begin

e3<=a3 xnor b3;

e2<=a2 xnor b2;

e1<=a1 xnor b1;

e0<=a0 xnor b0;

e<=e3 and e2 and e1 and e0;

gt3<=a3 and (not b3);

gt2<=e3 and a2 and (not b2);

gt1<=e3 and e2 and a1 and (not b1);

gt0<=e3 and e2 and e1 and a0 and (not b0);

gt<=gt3 or gt2 or gt1 or gt0;

lt3<=(not a3)and b3;

lt2<=e3 and (not a2)and b2;

lt1<=e3 and e2 and(not a1) and b1;

lt0<=e3 and e2 and e1 and(not a0)and b0;

lt<=lt3 or lt2 or lt1 or lt0;

end Behavioral;

OUTPUT WAVEFORM

MEC 40 DEPARTMENT OF ECE

RESULT:

Thus the 4-bit Comparator was simulated by using Modelsim simulation tool

with Xilinx ISE.

EXP.NO: 15

DATE : 29.10.09

SYNCHRONOUS COUNTER

AIM

To simulate a synchronous counter in VHDL by using Modelsim simulation

tool with Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

MEC 41 DEPARTMENT OF ECE

iv. Define behavioral modeling of synchronous counter.

v. End architecture.

STATEDIAGRAM

VHDL code for Synchronous counter

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity counter is

port(rst,clk:in std_logic; updown:in std_logic;

count:out std_logic_vector(15 downto 0));

end counter;

MEC 42 DEPARTMENT OF ECE

architecture Behavioral of counter is

signal temp:std_logic_vector(15 downto 0);

begin

process(clk,rst,updown)

begin

if(rst='1')then

temp<="0000000000000000";

elsif(clk'event and clk='1')then

if (updown = '1')then

temp<=temp+1;

else

temp<=temp-1;

end if;

end if;

end process;

count<=temp;

end Behavioral;

OUTPUT WAVEFORM

MEC 43 DEPARTMENT OF ECE

RESULT

Thus the Synchronous counter was simulated by using Modelsim simulation

tool with Xilinx ISE.

EXP.NO: 16

DATE : 29.10.09

MEC 44 DEPARTMENT OF ECE

ASYNCHRONOUS COUNTER

AIM

To simulate an asynchronous counter in VHDL by using Modelsim simulation

tool with Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

iv. Define behavioral modeling of asynchronous counter.

v. End architecture.

VHDL code for Asynchronous counter :

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.NUMERIC_STD.ALL;

entity asynccounter is

port(clk,reset:in std_logic;

y:out std_logic);

end asynccounter;

architecture Behavioral of asynccounter is

signal div2,div4,div8,div16:std_logic;

begin

process (clk,reset,div2,div4,div8)

begin

if(reset='0')then

MEC 45 DEPARTMENT OF ECE

div2<='0';

elsif rising_edge(clk)then

div2<=not div2;

end if;

if(reset='0')then

div4<='0';

elsif rising_edge(div2)then

div4<=not div4;

end if;

if(reset='0')then

div8<='0';

elsif rising_edge(div4)then

div8<=not div8;

end if;

if(reset='0')then

div16<='0';

elsif rising_edge(div8)then

div16<=not div16;

end if;

if(reset='0')then

y<='0';

elsif rising_edge(clk)then

y<=div16;

end if;

end process;

end Behavioral;

MEC 46 DEPARTMENT OF ECE

OUTPUT WAVEFORM

RESULT

Thus the Asynchronous counter was simulated by using Modelsim simulation

tool with Xilinx ISE.

EXP.NO: 17

DATE : 02.11.09

MEC 47 DEPARTMENT OF ECE

MOORE MACHINE

AIM

To simulate a Moore machine in VHDL by using Modelsim simulation tool

with Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

iv. Define behavioral modeling of Moore machine.

v. End architecture.

STATE DIAGRAM:

VHDL Code

MEC 48 DEPARTMENT OF ECE

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

Entity moore is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

w : in STD_LOGIC;

z : out STD_LOGIC);

end moore;

Architecture Behavioral of moore is

type state_type is(a,b,c);

signal y:state_type;

begin

process(rst,clk)

begin

if (rst='0')then

y<=a;

elsif(clk'event and clk='1')then

case y is

when a=>

if(w='0')then

y<=a;

else

y<=b;

end if;

MEC 49 DEPARTMENT OF ECE

when b=>

if(w='0')then

y<=a;

else

y<=c;

end if;

when c=>

if(w='0')then

y<=a;

else

y<=c;

end if;

end case;

end if;

end process;

z<='1' when y=c else'0';

end Behavioral;

MEC 50 DEPARTMENT OF ECE

OUTPUT WAVEFORM

RESULT

Thus the Moore machine was simulated by using Modelsim simulation tool

with Xilinx ISE.

EXP.NO: 18

DATE : 02.11.09

MEC 51 DEPARTMENT OF ECE

MEALY MACHINE

AIM

To simulate a mealy machine in VHDL by using Modelsim simulation tool

with Xilinx ISE.

ALGORITHM

i. Define library.

ii. Declare entity with port list.

iii. Declare architecture.

iv. Define behavioral modeling of mealy machine.

v. End architecture.

STATE DIAGRAM

VHDL Code

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

Entity mealy is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

MEC 52 DEPARTMENT OF ECE

w : in STD_LOGIC;

z : out STD_LOGIC);

end mealy;

Architecture Behavioral of mealy is

type state_type is(a,b);

signal y:state_type;

begin

process(rst,clk)

begin

if (rst='0')then

y<=a;

elsif(clk'event and clk='1')then

case y is

when a=>

if(w='0')then

y<=a;

else

y<=b;

end if;

when b=>

if(w='0')then

y<=a;

else

y<=b;

end if;

end case;

MEC 53 DEPARTMENT OF ECE

end if;

end process;

process(y,w)

begin

case y is

when a=> z<='0';

when b=> z<=w;

end case;

end process;

end Behavioral;

OUTPUT WAVEFORM

RESULT

Thus the Mealy machine was simulated by using Modelsim simulation tool

with Xilinx ISE.

EXP.NO: 19

DATE : 14.11.09

MEC 54 DEPARTMENT OF ECE

NMOS INVERTER & CMOS INVETER

AIM

To design and simulate the NMOS and CMOS INVERTER circuit using

Pspice AD.

ALGORITHM

i. Define NMOS INVERTER and CMOS INVERTER..

ii. Define corresponding voltage as input.

iii. Design the value of resistance between each node.

iv. Declare models with corresponding length to width ratio.

v. Check the output.

CIRCUIT DIAGRAM FOR NMOS INVERTER

PROGRAM

MEC 55 DEPARTMENT OF ECE

NMOS INVERTER

VDD 1 0 DC 5V

VIN1 3 0 DC 0V

RL 2 0 500K

M1 1 2 2 2 NMOD1 L=1U W=5U

.MODEL NMOD1 NMOS (VTO=-1.2 KP=1E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

M2 2 3 0 0 NMOD2 L=1U W=5U

.MODEL NMOD2 NMOS(VTO=2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

.TRAN 1US 100US

.TF V(2) VIN1

.OP

.PLOT TRAN V(2)V(3)

.PROBE

.END

CIRCUIT DIAGRAM FOR CMOS INVERTER

MEC 56 DEPARTMENT OF ECE

PROGRAM

CMOS INVERTER

VDD 1 0 DC 5V

VIN1 2 0 DC 5V

RL 3 0 500K

M1 3 2 1 1 PMOD1 L=1U W=20U

.MODEL PMOD1 PMOS (VTO=-2 KP=1E-4 CBD=5PF RD=5 RS=-2 RB=0

CGSO=1PF CGBO=1PF)

M2 3 2 0 0 NMOD1 L=1U W=5U

.MODEL NMOD1 NMOS(VTO=2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

.TRAN 1US 100US

.TF V(3) VIN1

.OP

.PLOT TRAN V(3)V(2)

.PROBE

.END

WAVEFORM FOR NMOS INVERTER

MEC 57 DEPARTMENT OF ECE

WAVEFORM FOR CMOS INVERTER

RESULT

Thus the NMOS and CMOS INVERTER circuit was designed and simulated

using Pspice AD.

MEC 58 DEPARTMENT OF ECE

EXP.NO: 20

DATE : 21.11.09

NMOS NAND GATE & CMOS NAND GATE

AIM

To design and simulate the NMOS and CMOS NAND gate using Pspice AD.

ALGORITHM

i. Define NMOS and CMOS NAND gate.

ii. Define corresponding voltage as input.

iii. Design the value of resistance between each node.

iv. Declare models with corresponding length to width ratio.

v. Check the output.

CIRCUIT DIAGRAM FOR NMOS NAND GATE

PROGRAM

MEC 59 DEPARTMENT OF ECE

NMOS NAND GATE

VDD 6 0 DC 5V

VIN1 1 0 DC 0V

VIN2 2 0 DC 5V

RL 5 0 500K

R1 2 3 5K

M1 6 5 5 5 NMOD1 L=1U W=5U

.MODEL NMOD1 NMOS (VTO=-1.2 KP=1E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

M2 5 1 4 4 NMOD2 L=1U W=5U

.MODEL NMOD2 NMOS (VTO=1.2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

M3 4 3 0 0 NMOD3 L=1U W=5U

.MODEL NMOD3 NMOS (VTO=1.2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

.TRAN 1US 100US

.TF V (3) VIN1

.OP

.PLOT TRAN V (5) V (1) V (2)

.PROBE

.END

CIRCUIT DIAGRAM FOR CMOS NAND

MEC 60 DEPARTMENT OF ECE

PROGRAM

CMOS NAND GATE

VDD 5 0 DC 5V

VIN1 1 0 DC 5V

VIN2 6 0 DC 5V

RL 4 0 500K

R1 6 2 5K

M1 4 1 5 5 PMOD1 L=1U W=20U

.MODEL PMOD1 PMOS (VTO=-2 KP=1E-4 CBD=5PF RD=5 RS=-2 RB=0

CGSO=1PF CGBO=1PF)

M2 4 2 5 5 PMOD2 L=1U W=20U

.MODEL PMOD2 PMOS(VTO=-2 KP=1E-4 CBD=5PF RD=5 RS=-2 RB=0

CGSO=1PF CGBO=1PF)

M3 4 1 3 3 NMOD1 L=1U W=5U

.MODEL NMOD1 NMOS(VTO=2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

MEC 61 DEPARTMENT OF ECE

M4 3 2 0 0 NMOD2 L=1U W=5U

.MODEL NMOD2 NMOS(VTO=2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

.TRAN 1US 100US

.TF V(4) VIN1

.OP

.PLOT TRAN V(4)V(1)V(6)

.PROBE

.END

WAVEFORM FOR NMOS NAND GATE

MEC 62 DEPARTMENT OF ECE

WAVEFORM FOR CMOS NAND GATE

RESULT

Thus the NMOS and CMOS NAND gate was designed and simulated using

Pspice AD.

EXP.NO: 21

DATE : 23.11.09

MEC 63 DEPARTMENT OF ECE

NMOS NOR GATE & CMOS NOR GATE

AIM

To design and simulate the NMOS AND CMOS NOR gate using Pspice AD.

ALGORITHM

i. Define NMOS and CMOS NOR gate.

ii. Define corresponding voltage as input.

iii. Design the value of resistance between each node.

iv. Declare models with corresponding length to width ratio.

v. Check the output.

CIRCUIT DIAGRAM OF NMOS NOR

PROGRAM

MEC 64 DEPARTMENT OF ECE

NMOS NOR

VDD 5 0 DC 5V

VIN1 1 0 DC 0V

VIN2 2 0 DC 5V

RL 4 0 500K

R1 2 3 5K

M1 4 1 0 0 NMOD1 L=1U W=20U

.MODEL NMOD1 NMOS (VTO=1.2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

M2 4 3 0 0 NMOD2 L=1U W=5U

.MODEL NMOD2 NMOS(VTO=1.2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

M3 5 5 4 4 NMOD3 L=1U W=5U

.MODEL NMOD3 NMOS(VTO=-1.2 KP=1E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

.TRAN 1US 100US

.TF V(3) VIN1

.OP

.PLOT TRAN V(4)V(1)V(2)

.PROBE

.END

CIRCUIT DIAGRAM OF CMOS NOR

MEC 65 DEPARTMENT OF ECE

PROGRAM

CMOS NOR

VDD 5 0 DC 5V

VIN1 1 0 DC 5V

VIN2 6 0 DC 5V

RL 3 0 500K

R1 6 2 5K

M2 3 1 4 4 PMOD2 L=1U W=20U

.MODEL PMOD2 PMOS (VTO=-2 KP=1E-4 CBD=5PF RD=5 RS=-2 RB=0

CGSO=1PF CGBO=1PF)

M1 4 2 5 5 PMOD1 L=1U W=20U

.MODEL PMOD1 PMOS(VTO=-2 KP=1E-4 CBD=5PF RD=5 RS=-2 RB=0

CGSO=1PF CGBO=1PF)

M3 3 6 0 0 NMOD1 L=1U W=5U

.MODEL NMOD1 NMOS(VTO=2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

MEC 66 DEPARTMENT OF ECE

M4 3 1 0 0 NMOD2 L=1U W=5U

.MODEL NMOD2 NMOS(VTO=2 KP=4.5E-4 CBD=5PF RD=5 RS=2 RB=0

CGSO=1PF CGBO=1PF)

.TRAN 1US 100US

.TF V(3) VIN1

.OP

.PLOT TRAN V(3)V(1)V(6)

.PROBE

.END

WAVEFORM OF NMOS NOR

MEC 67 DEPARTMENT OF ECE

WAVEFORM OF CMOS NOR

RESULT

Thus the NMOS and CMOS NOR gate was designed and simulated using

Pspice AD.

EXP.NO: 22

DATE : 03.12.09

MEC 68 DEPARTMENT OF ECE

LINEAR CONVOLUTION

AIM

To write a program for linear convolution in C language and implement on

TMS 5416 processor using Code Composer studio.

ALGORITHM

i. Start the program.

ii. Get the two sequence x(n) and h(n) in matrix form.

iii. Find the length of sequence x(n) and denote it as ‘L’.

iv. Find the length of sequence h(n) and denote it as ‘M’.

v. Find the value of N ,where N = L + M -1 samples.

vi. The convolved sequence is denoted as y(n).

vii. y(n) is given by the formula,

y(n) =∑ {x(k) h(n-k) } where n =0 to N

viii. Terminate the process.

PROCEDURE FOR OPERATING DIGITAL SIGNAL PROCESSOR

i. Open Code Composer Studio make sure the DSP kit is turned on.

ii. Start a new project using ‘Project-new ‘ pull down menu, save it in a separate

directory (c:\ccstudio\myprojectc) with name lconv.pjt

iii. Write a c coding for sampling a sinusoidal signal and save it in the current

project location as lconv.c

iv. Add the source file lconv.c to the project using ‘project –Add files to the

project pull down the menu.

v. Add the linker command file hello.cmd from the location

(c:\ccstudio\tutorial\disk 5416\hello1\hello.cmd ).

vi. Add the run time support library rts500.lib from the location

(c:\ccstudio\c5400\cgtools\lib\rts500.lib).

vii. Compile the program using ‘Project-compile’ pull down menu.

viii. Build the program using ‘Project-Build ‘pull down menu.

ix. Load the program (lconv.out) in program memory of DSP chip using ‘File-

load program’ pull down menu.

MEC 69 DEPARTMENT OF ECE

x. Run the program using the ‘Debug-Run ‘pull down menu.

xi. View the output graphically using ‘View -> graph -> time and frequency’ pull

down menu.

PROGRAM

#include<stdio.h>

main( )

int m=4;

int n=4;

int i=0,j;

int x[10]={1,2,3,4,0,0,0,0};

int h[10]={1,2,3,4,0,0,0,0};

int y[10];

for(i=0;i<m+n-1;i++)

y[i]=0;

for(j=0;j<=i;j++)

y[i]=x[j]*h[i-j];

for(i=0;i<m+n-1;i++)

printf(“%d\n”,y[i]);

OUTPUT

MEC 70 DEPARTMENT OF ECE

1

10

20

25

36

16

RESULT

Thus the program for Linear convolution using C language was implemented

and its result was verified.

EXP.NO: 23

DATE : 04.12.09

MEC 71 DEPARTMENT OF ECE

CIRCULAR CONVOLUTION

AIM

To write a program for circular convolution in C language and implement on

TMS 5416 processor using Code Composer studio.

ALGORITHM

i. Start the program.

ii. Get the two sequence x(n) and h(n) in matrix form.

iii. Find the length of sequence x(n) and denote it as ‘L’.

iv. Find the length of sequence h(n) and denote it as ‘M’.

v. Find the value of N ,where N = L + M -1 samples.

vi. The convolved sequence is denoted as y(n).

vii. y(n) is given by the formula,

y(n) =∑ {x(k) h(n-k) } where n =0 to N

viii. Terminate the process.

PROCEDURE FOR OPERATING DIGITAL SIGNAL PROCESSOR

i. Open Code Composer Studio, make sure the DSP kit is turned on.

ii. Start a new project using ‘Project-new ‘ pull down menu, save it in a separate

directory (c:\ccstudio\myprojectc) with name circonv.pjt

iii. Write a c coding for sampling a sinusoidal signal and save it in the current

project location as circonv.c

iv. Add the source file circonv.c to the project using ‘project –Add files to the

project ‘ pull down the menu

v. Add the linker command file hello.cmd from the location

( c:\ccstudio\tutorial\disk 5416\hello1\hello.cmd )

vi. Add the run time support library rts500.lib from the location

(c:\ccstudio\c5400\cgtools\lib\rts500.lib)

vii. Compile the program using ‘Project-compile’ pull down menu.

viii. Build the program using ‘Project-Build ‘pull down menu.

ix. Load the program (circonv.out) in program memory of DSP chip using ‘File-

load program’ pull down menu.

MEC 72 DEPARTMENT OF ECE

x. Run the program using the ‘Debug-Run ‘pull down menu.

xi. View the output graphically using ‘View -> graph -> time and frequency’ pull

down menu.

PROGRAM

#include<stdio.h>

int m,n,x[30],h[30],y[30],i,j,temp[30],k,x2[30],a[30];

void main()

printf(“enter the length of the first seq\n”);

scanf(“%d”,&m);

printf(“enter the length of the second seq\n”);

scanf(“%d”,&n);

printf(“enter the first seq\n”);

for(i=0;i<m;i++)

scanf(“%d”,&x[i]);

printf(“enter the second seq\n”);

for(j=0;j<n;j++)

scanf(“%d”,&h[j]);

if(m-n!=0)

if(m>n)

for(i=n;i<m;i++)

h[i]=0;

n=m;

MEC 73 DEPARTMENT OF ECE

for(i=m;i<n;i++)

x[i]=0;

m=n;}

y[0]=0;

a[0]=h[0];

for(j=1;j<n;j++)

a[j]=h[n-j];

for(i=0;i<n;i++)

y[0]+=x[i]*a[i];

for(k=1;k<n;k++)

y[k]=0;

for(j=1;j<n;j++)

x2[j]=a[j-1];

x2[0]=a[n-1];

for(i=0;i<n;i++)

a[i]=x2[i];

y[k]=x[i]*x2[i];

printf(“the circular convolution is\n”);

for(i=0;i<n;i++)

printf(“%d\t”,y[i]);

MEC 74 DEPARTMENT OF ECE

INPUT

M=4

N=4

3210

1100

OUTPUT

3531

RESULT

Thus the program for circular convolution using C language was implemented

and its result was verified.

MEC 75 DEPARTMENT OF ECE

You might also like

- Equity Valuation: Models from Leading Investment BanksFrom EverandEquity Valuation: Models from Leading Investment BanksJan ViebigNo ratings yet

- Monte Carlo Frameworks: Building Customisable High-performance C++ ApplicationsFrom EverandMonte Carlo Frameworks: Building Customisable High-performance C++ ApplicationsRating: 1.5 out of 5 stars1.5/5 (2)

- Microprocessor LABDocument106 pagesMicroprocessor LABHari GNo ratings yet

- Micro Processsor and Micro Controller: Laboratory ManualDocument85 pagesMicro Processsor and Micro Controller: Laboratory ManualATMAKURI S V N ANJANEYA SESHASAINo ratings yet

- CSE IV MP Lab ManualDocument122 pagesCSE IV MP Lab ManualAmarkavi Balu supper childNo ratings yet

- Ec8681-Microprocessors and Microcontrollers Lab-1732123961-Cse IV MP Lab Manual FinDocument114 pagesEc8681-Microprocessors and Microcontrollers Lab-1732123961-Cse IV MP Lab Manual Fingokul docNo ratings yet

- MicroprocessorDocument8 pagesMicroprocessorمحمدضيأ الدينNo ratings yet

- Experiment No:7 Square Wave Generation: Daq InterfaceDocument28 pagesExperiment No:7 Square Wave Generation: Daq Interface19501A0459 MAKANA PRASANNA LAKSHMINo ratings yet

- Ec8681-Microprocessors and Microcontrollers Laboratory-1053372192-Cse MPMC Lab ManualDocument116 pagesEc8681-Microprocessors and Microcontrollers Laboratory-1053372192-Cse MPMC Lab ManualgowsalyaNo ratings yet

- Keyboard and Display Interface Memory Address Label Mnemonics Opcode CommentsDocument3 pagesKeyboard and Display Interface Memory Address Label Mnemonics Opcode Comments15 Kowshick ShalomNo ratings yet

- Ra191104010652 Exp-3 MmitDocument14 pagesRa191104010652 Exp-3 Mmitswagata mandalNo ratings yet

- Interfacing of Analog To Digital ConverterDocument2 pagesInterfacing of Analog To Digital Converterparameshraja069891No ratings yet

- 10 - Simple Mud Engineerv1.22Document22 pages10 - Simple Mud Engineerv1.22Abdul Hameed OmarNo ratings yet

- Mpi - Lab No - 2Document5 pagesMpi - Lab No - 2Muhammad Waleed Khan100% (1)

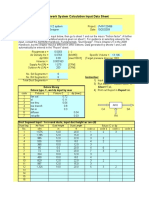

- Ductwork System Calculation Input Data Sheet: Fixture Library Fixture Type, C, and DP Input by UserDocument8 pagesDuctwork System Calculation Input Data Sheet: Fixture Library Fixture Type, C, and DP Input by Usersunii19847908No ratings yet

- MP LAB Cse ManualDocument140 pagesMP LAB Cse ManualJaganNo ratings yet

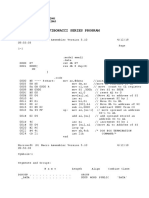

- CICS Transaction Dump AnalysisDocument99 pagesCICS Transaction Dump AnalysisSergio MoraNo ratings yet

- CGS 3269 Computer Architecture Concepts Assignment #3Document5 pagesCGS 3269 Computer Architecture Concepts Assignment #3HagiNo ratings yet

- ESSS Acceptance Report TU02531DDocument200 pagesESSS Acceptance Report TU02531DRavi KumarNo ratings yet

- MPECC08 Practical FileDocument13 pagesMPECC08 Practical FileSpace GoobieNo ratings yet

- Basic Arithmatic Operations I) Addition Memory Address Label Mnemonics Opcode CommentsDocument4 pagesBasic Arithmatic Operations I) Addition Memory Address Label Mnemonics Opcode Comments15 Kowshick ShalomNo ratings yet

- Practical No. 8 (A) : Address Label Mnemonics Hexcode CommentDocument4 pagesPractical No. 8 (A) : Address Label Mnemonics Hexcode CommentSwapnil KansaraNo ratings yet

- Lecture-2 Recitation DLDDocument30 pagesLecture-2 Recitation DLDJunaid KhalidNo ratings yet

- Fibonacci Series Program: Hitesh Vadgama 1712061 Rishi Molia 1712063Document2 pagesFibonacci Series Program: Hitesh Vadgama 1712061 Rishi Molia 1712063Hitesh VadgamaNo ratings yet

- Regrinder PLCDocument32 pagesRegrinder PLCerik masongNo ratings yet

- Chap 2 Number Systems Operations and CodesDocument28 pagesChap 2 Number Systems Operations and CodesDuy Phan PhúNo ratings yet

- Job InformationDocument12 pagesJob InformationHitendra KhachaneNo ratings yet

- Experiment 3: Decision Making and Looping Operation Using 8086Document5 pagesExperiment 3: Decision Making and Looping Operation Using 8086praveenembd1No ratings yet

- S7 DefinitionDocument5 pagesS7 DefinitionNabilBouabanaNo ratings yet

- Topic 5: 8086 Assembly Language Programming (24 Marks)Document38 pagesTopic 5: 8086 Assembly Language Programming (24 Marks)2008 AvadhutNo ratings yet

- Ramos Logic Circuits Number System Common Number SystemDocument8 pagesRamos Logic Circuits Number System Common Number SystemAlyssa RamosNo ratings yet

- Template - Test Scenario v1.0Document335 pagesTemplate - Test Scenario v1.0nikhil9213No ratings yet

- Sorting A Series of 10 Numbers: FlowchartDocument4 pagesSorting A Series of 10 Numbers: Flowchartnothing noNo ratings yet

- MPMC Lab Assignment-2: Microprocessors AND MicrocontrollersDocument23 pagesMPMC Lab Assignment-2: Microprocessors AND MicrocontrollersECE BNo ratings yet

- Assignment 1 PDFDocument1 pageAssignment 1 PDFmiza adlinNo ratings yet

- Calculated Values of DEQ Variables: POLYMATH ReportDocument1 pageCalculated Values of DEQ Variables: POLYMATH Reportmiza adlinNo ratings yet

- Experiment No 3 (MP)Document9 pagesExperiment No 3 (MP)kartikpatil0211No ratings yet

- Experiment NoDocument3 pagesExperiment NoFaiyaz Rahman SaminNo ratings yet

- SM Series: Aluminium Electrolytic CapacitorDocument2 pagesSM Series: Aluminium Electrolytic CapacitorStuxnetNo ratings yet

- Program 3 Multibyte Addition 8086Document14 pagesProgram 3 Multibyte Addition 8086Sisay DeresaNo ratings yet

- Chap 2Document52 pagesChap 2MUHAMMAD NIZAMUDDIN ROSLINo ratings yet

- Experiment 3Document3 pagesExperiment 3blacktee moNo ratings yet

- Topic 1 - Numbering SystemDocument35 pagesTopic 1 - Numbering SystemfarahNo ratings yet

- Nguyen Ngoc Nhan De160211 SE1705Document4 pagesNguyen Ngoc Nhan De160211 SE1705Doodle DooNo ratings yet

- Basic EE ECE PDFDocument7 pagesBasic EE ECE PDFrianna rose dela cruzNo ratings yet

- Dse Gencomm enDocument38 pagesDse Gencomm enbaguspermana7No ratings yet

- Number SystemDocument7 pagesNumber SystemdreamdalesocietyNo ratings yet

- Mbr1060Ctl Schottky Rectifier: Sangdest Microelectronics Green ProductsDocument6 pagesMbr1060Ctl Schottky Rectifier: Sangdest Microelectronics Green ProductsManos MagicasNo ratings yet

- Model QPDocument3 pagesModel QPKarthik Kudroli JKSHIMNo ratings yet

- PFC Workshop 01 Co Dap AnDocument4 pagesPFC Workshop 01 Co Dap Antrương nhuNo ratings yet

- Interfacing 8086 With 8255Document32 pagesInterfacing 8086 With 8255Sunitha Josephine75% (4)

- Institute of Business ManagementDocument3 pagesInstitute of Business ManagementAli KhanNo ratings yet

- Basic PLCDocument34 pagesBasic PLCESHA VARSHNEYNo ratings yet

- Experiment Name Experiment NoDocument7 pagesExperiment Name Experiment NoReena KaleNo ratings yet

- Workshop 01Document5 pagesWorkshop 01Huu hien NguyenNo ratings yet

- Shivam 8085Document16 pagesShivam 8085White RockNo ratings yet

- Answer All Parts of The Question TogetherDocument2 pagesAnswer All Parts of The Question TogetherSHIFA SAIMANo ratings yet

- Scrolling ProgramsDocument6 pagesScrolling ProgramsSivakumar SankaranarayananNo ratings yet

- CPE 221 Test 1 Solution Spring 2016Document4 pagesCPE 221 Test 1 Solution Spring 2016Kyra LathonNo ratings yet

- Distributed Process Control ReportFrom EverandDistributed Process Control ReportNo ratings yet

- Noise Margins For The CMOS Inverter: - Noise Margin Related To K - When K 1, NM NM 0.93 V (Better Than NMOS)Document16 pagesNoise Margins For The CMOS Inverter: - Noise Margin Related To K - When K 1, NM NM 0.93 V (Better Than NMOS)KumarNo ratings yet

- DLC LAB - 08 - Student - ManualDocument10 pagesDLC LAB - 08 - Student - ManualImtiaj SajinNo ratings yet

- EC1401 VLSI - Question Bank (N.shanmuga Sundaram)Document35 pagesEC1401 VLSI - Question Bank (N.shanmuga Sundaram)Dr. N.Shanmugasundaram50% (2)

- of Principles of Cmos Vlsi DesignDocument34 pagesof Principles of Cmos Vlsi Designkavyashree_pNo ratings yet

- Design and Performance Analysis of 2Document24 pagesDesign and Performance Analysis of 2Dilip Kumar100% (1)

- Microelectronic Circuits, 8e Sedra, Smith, Carusone, GaudetDocument2 pagesMicroelectronic Circuits, 8e Sedra, Smith, Carusone, GaudetBobNo ratings yet

- Logic Design 1 PDFDocument74 pagesLogic Design 1 PDFSydney BajentingNo ratings yet

- Experiment Using Capture CMOS & NMOSDocument14 pagesExperiment Using Capture CMOS & NMOSS.DharanipathyNo ratings yet

- Experiment-1 Aim: VDD=5V VT,n=0.8V VT,p=-0.8V (W/L) p=2.5 (W/L) n=1 Technology=1μ1Document5 pagesExperiment-1 Aim: VDD=5V VT,n=0.8V VT,p=-0.8V (W/L) p=2.5 (W/L) n=1 Technology=1μ1Timir PatelNo ratings yet

- Large List of Intel Interview QuestionsDocument4 pagesLarge List of Intel Interview QuestionsvaghelamiralNo ratings yet

- Fac 3Document54 pagesFac 3Srinivas Rao YandrapuNo ratings yet

- ASIC & FPGA Chip Design:: Mahdi ShabanyDocument102 pagesASIC & FPGA Chip Design:: Mahdi ShabanyKevin NguyenNo ratings yet

- A Low Power Schmitt Trigger Design Using SBT Technique in 180nm CMOS TechnologyDocument4 pagesA Low Power Schmitt Trigger Design Using SBT Technique in 180nm CMOS TechnologySowmya ReddyNo ratings yet

- Switch Level ModelingDocument8 pagesSwitch Level Modelingsindhuja selvamNo ratings yet

- 2v. Transistor Presentation EetDocument80 pages2v. Transistor Presentation EetDan ChapsNo ratings yet

- Ee5311 Module 4 Comb CKTDocument72 pagesEe5311 Module 4 Comb CKTAnmol SinhaNo ratings yet

- Lecture 21Document21 pagesLecture 21KumarNo ratings yet

- CAD For VLSI Design - 1: V. Kamakoti and Shankar BalachandranDocument17 pagesCAD For VLSI Design - 1: V. Kamakoti and Shankar BalachandranRajeev PandeyNo ratings yet

- RIT Models For LTSPICEDocument3 pagesRIT Models For LTSPICEDavid Villamarin RiveraNo ratings yet

- VLSI Circuit Design Process-Unit-IIDocument51 pagesVLSI Circuit Design Process-Unit-IICatherineNo ratings yet

- DC Characteristics of A CMOS Inverter: Out inDocument31 pagesDC Characteristics of A CMOS Inverter: Out insai jagadeeshNo ratings yet

- Noc18 Ee33 Assignment5Document6 pagesNoc18 Ee33 Assignment5Hari PrasathNo ratings yet

- Analog Electronics Constant GM CircuitDocument11 pagesAnalog Electronics Constant GM CircuitMonique Kirkman-BeyNo ratings yet

- Hspice Simulation of SRAM PDFDocument65 pagesHspice Simulation of SRAM PDFYatheesh KaggereNo ratings yet

- High Speed Integrated Circuit TechnologyDocument372 pagesHigh Speed Integrated Circuit TechnologyZied Houaneb100% (1)

- VLSI Made Easy - VLSI Interview QuestionsDocument21 pagesVLSI Made Easy - VLSI Interview QuestionsAnupam DubeyNo ratings yet

- Stick Diagrams by S.N.bhat, Lecturer, Dept of EC Engg., M.I.T ...Document19 pagesStick Diagrams by S.N.bhat, Lecturer, Dept of EC Engg., M.I.T ...arthy_mariappan3873No ratings yet

- Mentor Graphics ProcedureDocument49 pagesMentor Graphics Proceduresai prasadNo ratings yet

- DEE6113 - Practical Work4 PDFDocument10 pagesDEE6113 - Practical Work4 PDFFonzBahari0% (1)