Professional Documents

Culture Documents

BIT3252A

Uploaded by

Siva Anand.PCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BIT3252A

Uploaded by

Siva Anand.PCopyright:

Available Formats

Beyond Innovation Technology Co., Ltd.

BIT3252A

BIT3252A

Low Cost PWM Controller

built in

55V NMOS

Version: A2

Please read the notice stated in this preamble carefully before

accessing any contents of the document attached.

Admission of BiTEK’s statement therein is presumed

碩 頡 科 技 once

B i T the

EK

document is released to the receiver.

管 May 16, 2007 制

DCC CONTROLLED

2007/04/26 Confidential, for authorized user only page 1 of 8

DOC NO.W-DS-0002

Beyond Innovation Technology Co., Ltd. BIT3252A

Notice:

Firstly, the information furnished by Beyond Innovation Technology Co. Ltd. (BiTEK) in this document is believed to be

accurate and reliable and subject to BiTEK’s amendment without prior notice. And the aforesaid information does not

form any part or parts of any quotation or contract between BiTEK and the information receiver.

Further, no responsibility is assumed for the usage of the aforesaid information. BiTEK makes no representation that

the interconnect of its circuits as described herein will not infringe on exiting or future patent rights, nor do the

descriptions contained herein imply the granting of licenses to make, use or sell equipment constructed in accordance

therewith.

Besides, the product in this document is not designed for use in life support appliances, devices, or systems where

malfunction of this product can reasonably be expected to result in personal injury. BiTEK customers’ using or selling

this product for use in such applications shall do so at their own risk and agree to fully indemnify BiTEK for any damage

resulting from such improper use or sale.

At last, the information furnished in this document is the property of BiTEK and shall be treated as highly

confidentiality; any kind of distribution, disclosure, copying, transformation or use of whole or parts of this document

without duly authorization from BiTEK by prior written consent is strictly prohibited. The receiver shall fully compensate

BiTEK without any reservation for any losses thereof due to its violation of BiTEK’s confidential request. The receiver is

deemed to agree on BiTEK’s confidential request therein suppose that said receiver receives this document without making

any expressly opposition. In the condition that aforesaid opposition is made, the receiver shall return this document to

BiTEK immediately without any delay. -Version A4

碩頡科技 BiTEK

管 May 16, 2007 制

DCC CONTROLLED

2007/04/26 Confidential, for authorized user only page 2 of 8

DOC NO.W-DS-0002

Beyond Innovation Technology Co., Ltd. BIT3252A

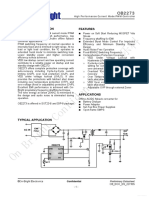

Features: Pin Layout:

y Voltage Mode PWM Controller

y Low 0.2V reference Voltage 1 8

VDD OUT

y 330KHz Operation

EA GND

y Over Voltage Protection

CMP GND

y Internal Soft-Start

INN OVP

y Built-in 55V NMOS 4 5

y Internal UVLO (Under Voltage Lock Out)

y Limited Output Duty Cycle Absolute Ratings: (if Ta=25℃)

y Low Shutdown current (0.1uA) VDD…………………………...…………-0.3 ~ +8 V

y SOP-8 Package GND…………………..…………………±0.3 V

Output Voltage……………….…….……-0.3 ~ 55 V

Operating Ambient Temperature……….0 ~ 70 ℃

General Description: Extreme Operating Ambient Temp……-40 ~ 85 ℃ ***

The BIT3252A is a high frequency PWM controller Operating Junction Temperature….….+150 ℃

which integrates the required functions for a boost Storage Temperature……………..…….-55~ 150 ℃

converter in a small SOP-8 package. A low 0.2V

feedback voltage makes the system with high Recommended Operating Condition:

efficiency and its over voltage protection function Supply Voltage…………………………….4~ 8 V

makes the system reliable. Built-in 55V/1.2A NMOS Operating Frequency………………….….330KHz

save the space of PCB and simplify the circuit design. Operating Ambient Temperature………...0 ~ 70 ℃

With CMOS process which greatly reduces the

operating current, BIT3252A is very suitable for LED Thermal Resistance θ JA θ JC :

backlight application.

( SOP8 ) 105 50 ℃/W

Functional Block Diagram:

EA OVP GND

VDD = 4.0V ~ 8.0V

Band Gap

Voltage

References

EAN UVLO 4.0V

EA

EA EHV

3.6V

HV

ERR_OVP OVPN HV

+ ERR_OVP

LATCH OUT

1.5V -

Digital

1.75V + Control BUFFER

- PWMOUT Circuit

EHV Triangle

OVPN +

CMP

-

6.75K 7.05K PWM Comparator

0.308V 1.8V

0.2V +

0.45K

-

0.75K

Error Amplifier Triangle

Triangle Wave

Generator

碩頡科技 BiTEK

INN CMP VDD

管 May 16, 2007

BIT3252A 制

*** For Extreme Operating Ambient Temperature, the supply voltage should be limited. The recommended voltage

range is from 4.5V to 7.5V. DCC CONTROLLED

2007/04/26 Confidential, for authorized user only page 3 of 8

DOC NO.W-DS-0002

Beyond Innovation Technology Co., Ltd. BIT3252A

Pin Description:

Pin No. Names Description

1 VDD Supply voltage input.

2 EA Enable Control Pin

3 CMP The output of the error amplifier. CMP is force to low when VDD < 3.6V.

PWM controller input, the inverting input of error amplifier. INN is pulled high to

4 INN

reduce the CMP when VDD < 3.6V

5 OVP Over Voltage detection pin

6 GND Ground

7 GND Ground

8 OUT Output pin

Function Description:

The PWM Controller: The pulse width modulation Initial Setting: BIT3252A provides the system a fast

control circuit includes a ramp wave generator, an error transient response by setting a suitably initial voltage in .

amplifier and a comparator. These devices provide the Vinn and Vcmp that can be referred as below conditions.

required functions for the PWM feedback control

application. The inverting input of the error amplifier is

pulled high to reduce its output CMP when VDD<3.6V.

The maximum duty cycle of the PWM controller is limited Table 1. Initial setting Voltage

to 93% Voltage Setting(@5V) VEA VDD VOVP

VINN =0.68V, VCMP =0.53V VEA > 1.2V VDD < 3.6V VOVP < 1.5V

The Over Voltage Protection: BIT3252A has an OVP VINN =0.68V, VCMP =0.53V VEA < 0.8V VDD > 4.0V VOVP < 1.5V

pin that is used to detect the converter output voltage, VINN =0.68V, VCMP =0.53V VEA > 1.2V VDD > 4.0V VOVP > 1.5V

when there is a voltage higher than 1.5V sensed in this The Setting Equation is:

pin, BIT3252A will latch off its output This latch off VINN =0.68V+0.12V*(VDD-5) (1)

function can make system operation more reliable. The VCMP =0.53V+0.08V*(VDD-5) (2)

latched off status can be released by reducing the

supply voltage to lower than 3.6V. Vcmp

Vinn

UVLO: The Under-Voltage Lock-Out circuit turns the Vcmp

output driver off when the supplying voltage is lower than

3.6V

Vinn=0.2V

Enable Control: BIT3252A is enabled when V(EA) ≧

1.2V and disabled when V(EA) ≦ 0.8V. In addition,

BIT3252A has an internal 80K±15% ohm pull low resistor Initial start up time

in this pin make itself normally in the OFF state or

shutdown mode operation. Figure 1. Initial transient response

(VDD=5V, VINN =0.68V, VCMP =0.53V)

碩頡科技 BiTEK

管 May 16, 2007 制

DCC CONTROLLED

2007/04/26 Confidential, for authorized user only page 4 of 8

DOC NO.W-DS-0002

Beyond Innovation Technology Co., Ltd. BIT3252A

DC/AC Characteristics:

Parameter Test Conditions Min. Typ.(Limits) Max. Unit

Reference Voltage

Measured with

Output voltage shorted INN CMP pins 0.194 0.2 0.206 V

VDD=5V, Ta=25°C

VDD=4 ~ 8V,

Line regulation 2 20 mV

Ta=25°C

Under Voltage Look Out

Upper threshold voltage Ta=25°C 3.6 3.8 4.0 V

Hysteresis Note2 0.1 0.2 0.3 V

Ramp Wave Generator

Frequency 300 330 360 KHz

Output peak (Internal ) 1.7 1.8 1.9 V

Note 1

Output valley (Internal) 0.25 0.308 0.35 V

Error Amplifier

Open loop gain 60 80 dB

Note 1

Unit gain band width 1 1.5 MHz

Over Voltage Protection

OVP threshold voltage VDD=5V, Ta=25°C 1.45 1.55 1.65 V

Enable Control

Turn on Threshold 1.2 V

VDD=5V, Note 1

Turn off Threshold 0.8 V

Internal MOS

VDD=5V, Ta=25°C,

Switch Leakage 10 uA

Note 1, Note 2

Drain-Source Voltage Note1 55 V

Drain-Source Breakdown Voltage Turn-off, Ids=250uA 55 V

Drain Current - Continuous Note1 1.2 A

Output

VDD=5V, Ta=25°C,

Maximum Duty Cycle 90 93 95 %

330KHz.

Ta: ambient temperature.

Note 1. Only guaranteed by simulation or sampled evaluation during –40~+85°C. Not 100% tested.

Note 2. The voltages of the output drivers are pulled to GND in each off states.

* Please note that EA pin should be pulled low, then VDD power could be shut off.

碩頡科技 BiTEK

管 May 16, 2007 制

DCC CONTROLLED

2007/04/26 Confidential, for authorized user only page 5 of 8

DOC NO.W-DS-0002

Beyond Innovation Technology Co., Ltd. BIT3252A

Layout Notice:

Some of the pins are very sensitive to noise. Please follow the bellowing guideline to make the layout:

Note 1. Please keep the capacitor between VDD and GND as close as possible. Noisy IC VDD may trigger UVLO.

Note 2. Figure 2 is an example of making shortest traces between VDD and GND. The layout traces are under the IC.

1 8

VDD OUT

EA GND

CMP GND

INN OVP

4 5

Figure 2

Order Information:

BIT3252A-SO

SO: SOP

Part number

Beyond Innovation Technology Co., Ltd.

碩頡科技 BiTEK

管 May 16, 2007 制

DCC CONTROLLED

2007/04/26 Confidential, for authorized user only page 6 of 8

DOC NO.W-DS-0002

Beyond Innovation Technology Co., Ltd. BIT3252A

Soldering Information

Reflow Soldering:

The choice of heating method may be influenced by plastic QFP package). If infrared or vapor phase heating is

used and the package is not absolutely dry (less than 0.1% moisture content by weight), vaporization of the small

amount of moisture in them can cause cracking of the plastic body. Preheating is necessary to dry the paste and

evaporate the binding agent. Preheating duration: 45 minutes at 45 °C.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to

the printed-circuit board by screen printing, stenciling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, convection or convection/infrared heating in a conveyor type oven.

Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 270 °C depending on solder paste material. The top-surface

temperature of the packages should preferable be kept below 245 °C for thick/large packages (packages with a thickness

3

≧ 2.5 mm or with a volume ≧ 350 mm so called thick/large packages). The top-surface temperature of the

packages should preferable be kept below 260 °C for thin/small packages (packages with a thickness < 2.5 mm and a

3

volume < 350 mm so called thin/small packages).

Stage Condition Duration

1’st Ram Up Rate max3.0+/-2℃/sec -

Preheat 150℃~200℃ 60~180 sec

2’nd Ram Up max3.0+/-2℃/sec -

Solder Joint 217℃ above 60~150 sec

Peak Temp 260 +0/-5℃ 20~40 sec

Ram Down rate 6℃/sec max -

Temp (℃)

260

217

200

150

25

RT

60~ 180 60~150 Time(sec)

Wave Soldering:

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards

with a high component density, as solder bridging and non-wetting can present major problems.

碩頡科技 BiTEK

Manual Soldering:

Fix the component by first soldering two diagonally-opposite end leads. Use 管 May(24

a low voltage 16,V 2007 制

or less) soldering

iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a

dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds

DCCbetween 270 and 320 °C.

CONTROLLED

2007/04/26 Confidential, for authorized user only page 7 of 8

DOC NO.W-DS-0002

Beyond Innovation Technology Co., Ltd. BIT3252A

Package Information :

Unit: mm

SOP type :

碩頡科技 BiTEK

管 May 16, 2007 制

DCC CONTROLLED

2007/04/26 Confidential, for authorized user only page 8 of 8

DOC NO.W-DS-0002

You might also like

- 9623 BIT3251 DatasheetDocument7 pages9623 BIT3251 Datasheet81968No ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- BIT3251 Datasheet PDFDocument7 pagesBIT3251 Datasheet PDFElectronica Libra Libra100% (1)

- Bit 3251Document7 pagesBit 3251Paulo Roberto s freireNo ratings yet

- High Performance PWM Controller: Beyond Innovation Technology Co., LTDDocument11 pagesHigh Performance PWM Controller: Beyond Innovation Technology Co., LTDRodolfo CarruyoNo ratings yet

- Datasheet PDFDocument8 pagesDatasheet PDFmcr16986No ratings yet

- 2fyl1ql5 BIT3715Document3 pages2fyl1ql5 BIT3715JourneyNo ratings yet

- Data Sheet: Beyond Innovation Technology Co., LTDDocument6 pagesData Sheet: Beyond Innovation Technology Co., LTDOlivier OuinaNo ratings yet

- Bit 3260Document1 pageBit 3260Iader Salgado100% (1)

- Bit3260 PDFDocument1 pageBit3260 PDFSteven Orozco100% (1)

- Data SheetDocument1 pageData Sheetcelestino secundinoNo ratings yet

- Bit 3260Document7 pagesBit 3260prem rajNo ratings yet

- BIT3368ODocument1 pageBIT3368OUncle Pane73% (15)

- Current Mode LED Driver: General Description FeaturesDocument1 pageCurrent Mode LED Driver: General Description FeaturesEnrique LandraNo ratings yet

- vc-02 v1.0.0 SpecificationDocument16 pagesvc-02 v1.0.0 SpecificationMarin MarinovNo ratings yet

- 4 Amp Over-Voltage Protection IC With Sense Output: Preliminary Datasheet KTS1681Document12 pages4 Amp Over-Voltage Protection IC With Sense Output: Preliminary Datasheet KTS1681José RepuestoNo ratings yet

- Vc-02-Kit Specification v1.0.0Document15 pagesVc-02-Kit Specification v1.0.0Marin MarinovNo ratings yet

- Bit 3267Document1 pageBit 3267Franklin Jimenez90% (10)

- ISO1H812GDocument23 pagesISO1H812Gmar_barudjNo ratings yet

- TCK401G Datasheet en 20191213Document13 pagesTCK401G Datasheet en 20191213tahri mohammedNo ratings yet

- Is Now Part ofDocument9 pagesIs Now Part ofFlorin SoareNo ratings yet

- Features General Description: Two-Phase Buck PWM Controller With Integrated MOSFET DriversDocument26 pagesFeatures General Description: Two-Phase Buck PWM Controller With Integrated MOSFET DriversMoisesNo ratings yet

- HIP6302CBDocument16 pagesHIP6302CBterry panNo ratings yet

- ACPL-C87AT/ACPL-C87BT: Data SheetDocument16 pagesACPL-C87AT/ACPL-C87BT: Data SheetMattias RahmNo ratings yet

- Three-Phase Brushless Motor Driver For Office Equipment ApplicationsDocument10 pagesThree-Phase Brushless Motor Driver For Office Equipment ApplicationsottoNo ratings yet

- OB2263 On-Bright PDFDocument13 pagesOB2263 On-Bright PDFamaliah bamesuNo ratings yet

- Ob2262 Usado em Fonte Proview MLT 198aDocument13 pagesOb2262 Usado em Fonte Proview MLT 198aHeron Cesar VieiraNo ratings yet

- Specification Status: Released: PolyzenDocument8 pagesSpecification Status: Released: PolyzenDwi TourNo ratings yet

- Datasheet Bit3715 PMW Monitor LCD AcerDocument11 pagesDatasheet Bit3715 PMW Monitor LCD AcershibatoyanNo ratings yet

- Features General Description: High-Speed High-Side MOSFET DriverDocument9 pagesFeatures General Description: High-Speed High-Side MOSFET DriverPaulo SilvaNo ratings yet

- Iw248 Datasheet-3075945Document19 pagesIw248 Datasheet-3075945hussamNo ratings yet

- Iw1819 DatasheetDocument21 pagesIw1819 DatasheetGonzaloNo ratings yet

- UTC Unisonic Tech UT3232G S16 R - C84913Document7 pagesUTC Unisonic Tech UT3232G S16 R - C84913KURALMOZHI RAMESHNo ratings yet

- Bit 3713Document11 pagesBit 3713Jan RiskenNo ratings yet

- ISO5500 2.5-A Isolated IGBT, MOSFET Gate Driver: 1 Features 3 DescriptionDocument45 pagesISO5500 2.5-A Isolated IGBT, MOSFET Gate Driver: 1 Features 3 DescriptionBubai BhattacharyyaNo ratings yet

- Bit 3269Document6 pagesBit 3269zubiNo ratings yet

- Bit 3715Document11 pagesBit 3715Rocko RattNo ratings yet

- FG Wilson DCP-10Document32 pagesFG Wilson DCP-10Aung AungNo ratings yet

- OB2273 On BrightDocument12 pagesOB2273 On BrightCarlos PosadaNo ratings yet

- Abcdef Abcdef: SpecificationDocument22 pagesAbcdef Abcdef: SpecificationSiam_SquareNo ratings yet

- LED Driver Built-In 100V MOS: BIT3367ADocument1 pageLED Driver Built-In 100V MOS: BIT3367AHéctor López ViverosNo ratings yet

- Bd9141muv eDocument25 pagesBd9141muv eKris OscarNo ratings yet

- Ob2262 Datasheet PDFDocument13 pagesOb2262 Datasheet PDFjesus cautivoNo ratings yet

- General Description: EMI Filter Ac in DC OutDocument13 pagesGeneral Description: EMI Filter Ac in DC Outjesus cautivoNo ratings yet

- Ob2262 Ver2.0 Datasheet PDFDocument13 pagesOb2262 Ver2.0 Datasheet PDFjesus cautivoNo ratings yet

- ZK Speedface-V3l Quick Start Guide en v1.1 2Document14 pagesZK Speedface-V3l Quick Start Guide en v1.1 2alphaconceptincNo ratings yet

- Sunrom 814104Document13 pagesSunrom 814104Valentin LeonteNo ratings yet

- MC44608 Few External Components Reliable and Flexible SMPS ControllerDocument15 pagesMC44608 Few External Components Reliable and Flexible SMPS Controllervali dNo ratings yet

- Sim6880m Driver Motor 3 PhaseDocument52 pagesSim6880m Driver Motor 3 Phaseluis albertoNo ratings yet

- LTC4286Document43 pagesLTC4286Muhammad Qasim RaufNo ratings yet

- Ω Ω Ω Ω Ω, 1.3A Power Switch with Programmable Current LimitDocument14 pagesΩ Ω Ω Ω Ω, 1.3A Power Switch with Programmable Current LimitSurendra SharmaNo ratings yet

- LB11827Document11 pagesLB11827Syed Khawar MukhtarNo ratings yet

- MIC5237 500ma Low Dropout Regulator DS20006095B-2907947Document19 pagesMIC5237 500ma Low Dropout Regulator DS20006095B-2907947fxwiredNo ratings yet

- ADuM5020 5028Document20 pagesADuM5020 5028IulianCioarcaNo ratings yet

- DCP-20 Genset Control ManualDocument65 pagesDCP-20 Genset Control Manualandy habibiNo ratings yet

- 1.0 Features 2.0 Description: Digital PWM Current-Mode Controller For Quasi-Resonant OperationDocument20 pages1.0 Features 2.0 Description: Digital PWM Current-Mode Controller For Quasi-Resonant OperationMisael GonzalezNo ratings yet

- Pentagram Business PlanDocument13 pagesPentagram Business PlantroubledsoulNo ratings yet

- MTE Radionuclear THYROID FK UnandDocument44 pagesMTE Radionuclear THYROID FK UnandAmriyani OFFICIALNo ratings yet

- 173544avaya Aura AES 7-0 JTAPI Programmers GuideDocument88 pages173544avaya Aura AES 7-0 JTAPI Programmers GuideAhmed SakrNo ratings yet

- JLPT N2 Vocab - 04Document345 pagesJLPT N2 Vocab - 04raj_kumartNo ratings yet

- Order of Nine Angles: RealityDocument20 pagesOrder of Nine Angles: RealityBrett StevensNo ratings yet

- Klarna: Klarna A Company Valued To Be 5.5 Billion and 8 Most Valued Fintech Company in The WorldDocument1 pageKlarna: Klarna A Company Valued To Be 5.5 Billion and 8 Most Valued Fintech Company in The WorldChetan NarasannavarNo ratings yet

- The Confederation or Fraternity of Initiates (1941)Document82 pagesThe Confederation or Fraternity of Initiates (1941)Clymer777100% (1)

- Section 9 - Brickwork and BlockworkDocument6 pagesSection 9 - Brickwork and BlockworkShing Faat WongNo ratings yet

- Arc Studio ReviewerDocument62 pagesArc Studio ReviewerKristine100% (1)

- Sap Successfactors Training Materials Guide: April 2020Document4 pagesSap Successfactors Training Materials Guide: April 2020pablo picassoNo ratings yet

- Duck 2019Document52 pagesDuck 2019Adrian BAGAYANNo ratings yet

- Fire Safety Management - Traditional Building Part#2Document194 pagesFire Safety Management - Traditional Building Part#2Yoyon Haryono100% (1)

- Wa0009.Document14 pagesWa0009.Pradeep SinghNo ratings yet

- Kami Export - Tools in Studying Environmental ScienceDocument63 pagesKami Export - Tools in Studying Environmental ScienceBenBhadzAidaniOmboyNo ratings yet

- Indian School Bousher Final Term End Exam (T2) : Academic Session - 2021-22 Grade: 7Document7 pagesIndian School Bousher Final Term End Exam (T2) : Academic Session - 2021-22 Grade: 7Shresthik VenkateshNo ratings yet

- R. K. NarayanDocument9 pagesR. K. NarayanCutypie Dipali SinghNo ratings yet

- Lozada Vs MendozaDocument4 pagesLozada Vs MendozaHarold EstacioNo ratings yet

- Life Without A Centre by Jeff FosterDocument160 pagesLife Without A Centre by Jeff Fosterdwhiteutopia100% (5)

- Rapidjson Library ManualDocument79 pagesRapidjson Library ManualSai Kumar KvNo ratings yet

- The Nation State and Global Order A Historical Introduction To ContemporaryDocument195 pagesThe Nation State and Global Order A Historical Introduction To Contemporaryrizwan.mughal1997100% (1)

- COSMO NEWS September 1, 2019 EditionDocument4 pagesCOSMO NEWS September 1, 2019 EditionUnited Church of Christ in the PhilippinesNo ratings yet

- Arthropods: Surviving The Frost: Charmayne Roanna L. GalangDocument2 pagesArthropods: Surviving The Frost: Charmayne Roanna L. GalangBabes-Rose GalangNo ratings yet

- High-Performance Cutting and Grinding Technology For CFRP (Carbon Fiber Reinforced Plastic)Document7 pagesHigh-Performance Cutting and Grinding Technology For CFRP (Carbon Fiber Reinforced Plastic)Dongxi LvNo ratings yet

- DeathoftheegoDocument123 pagesDeathoftheegoVictor LadefogedNo ratings yet

- Jao Vs Court of Appeals G.R. No. 128314 May 29, 2002Document3 pagesJao Vs Court of Appeals G.R. No. 128314 May 29, 2002Ma Gabriellen Quijada-TabuñagNo ratings yet

- Rectification of Errors Accounting Workbooks Zaheer SwatiDocument6 pagesRectification of Errors Accounting Workbooks Zaheer SwatiZaheer SwatiNo ratings yet

- Waa Sik Arene & Few Feast Wis (FHT CHT Ste1) - Tifa AieaDocument62 pagesWaa Sik Arene & Few Feast Wis (FHT CHT Ste1) - Tifa AieaSrujhana RaoNo ratings yet

- Pedia Edited23 PDFDocument12 pagesPedia Edited23 PDFAnnJelicaAbonNo ratings yet

- HSG 9 Tienganh 2019Document7 pagesHSG 9 Tienganh 2019Bảo HoàngNo ratings yet

- Presbuteroi (Elders) and Episkopoi (Overseers) and Are Described in 1 Tim 3 and TitusDocument15 pagesPresbuteroi (Elders) and Episkopoi (Overseers) and Are Described in 1 Tim 3 and TitusNimaro Brenda100% (1)