Professional Documents

Culture Documents

Micro Procesador - TMP47C434

Micro Procesador - TMP47C434

Uploaded by

Tecnico Genio0 ratings0% found this document useful (0 votes)

6 views27 pagesOriginal Title

MICRO PROCESADOR - TMP47C434

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views27 pagesMicro Procesador - TMP47C434

Micro Procesador - TMP47C434

Uploaded by

Tecnico GenioCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 27

TOSHIBA

TMP47C43.4/634/034

CMOS 4-BIT MICROCONTROLLER

TMP47C434N, TMP47C634N

TMP47C434F, TMP47C634F

The 47C434/634 are based on the TLCS-470 CMOS series. The 47¢434/634 have on-screen display circuit to

display characters and marks which indicate channel or time on TV screen, A/D converter input, and D/A,

converter output.

TMPa7cesar

sow Rane PACKAGE [ PIGGYBACK (adapier rocked)

ass xii | 256x0-bit

sraaxanit | saacait

FEATURES

@4-bit single chip microcomputer

instruction execution time : 1 9ys (at 4.2 MHz)

#92 basic instructions

Table look-up instructions

Subroutine nesting : 15 levels max.

6 interrupt sources (External : 2, Internal : 4)

Ali sources have independent latches each, and multiple

interrupt conteol is available

#10 port (30 pins)

© Input — 2 por Spins

* 10 Tports 25 pins

interval Timer

Two 12-bit Timer/Counters

Timer, event counter, and pulse width measurement mode

@watchdog timer

‘Serial Interface with B-bit buffer

+ Simultaneous transmission and reception capability

* Externaliinternal clock, leading/trailing edge shift, 4/8-bit

On-screen display circuit

© Character patterns 48 characters,

© Charactersdisplayed: 16 columns x2 lines

© Composition 8x8 dots (smoothing function)

+ Size of character 2 kinds (line by line)

Color of character 7 kinds (character by character}

* Variable display position : horizontal / vertical 64 steps

D/A converter (Pulse width modulation) outputs

14-bit resolution 1 channel

* Git resolution 4 channels

43-bit A/D converter input

Auto frequency control signal (S-shaped curve) detection

Horizontal synchronous signal is detected by timer/counter

‘Remote control signal preprocessing capability

@High current outputs

LED direct drive capability (typ. 20mA x 4 bits)

HOLD function - Battery/Capacitor back-up

aro

Ga cc

Sgt

rwparcssan

nereesan

rae

me “

Rei

erarcesae

ersressar

soicea

Tpa7co3ae

‘#Real Time Emulator : BM47C834A

anna

TOSHIBA

‘TMP47C434/634/034

PIN ASSIGNMENT (TOP VIEW)

soiree cn gpree

agin a= 2 pw

my = 2 fb moe

mapa G3 ses

room = de 3 hla ween

i lesel a el 33:38 38-30-29 2827-26 25 20:

mode ase _

sa +07 36 fearon AY TT leche,

eee et ee) 93150) —~ SOE 6 v0 fas

eed x og Sy 3 bean

an Gate) ee 10 33 ee ee " igi

wae Git ea aii ——aa]a0 16 boas

mace x soem er 5 fee

ote 5 sofa ats SBSoen

eae ee

ate = a

‘ae a

xa —> G15, 8 °

xo = G16 27 423 4 5 $78

wom iz 2%

we ds i bo ves

ee eee

to =o ace

mo da Pos

BLOCK DIAGRAM 2520 pata

; 7

sesorisan ers aerate!

Se —————

ome a LI T___II

pe] fae] 1 ec) fee Te] [onmenoy | pose

as [RAM adress butler RAN Counter

tt L i Face [sew] OT

a Te Gon conver i toa

ee ——— Tine cre a £

Sevorn fiber L_ ator ; = a o

Bee g ae aE TE

ahi el an

a a, ae wa

Siew se a ee

Sot eit, ROY SORE porn

‘soe "Fe en

tendo ter outt

rptipst

4114

TOSHIBA TMP47C434/634/034

PIN FUNCTION

PINNaMe | _InpuvOutpur FUNCTIONS

Koa = KOO. input ait input por

4:80 pore with atch. bit DIA converter PWM) output

wo(outmut) | Winer used as input port or D/A

converteroutputspins, thetatch | raya va converter (PAN output

must besetto"1"

53-51 v0

50 (PWG) wOfoutpue 6b: VA converter Pw output

, ‘i port with iteh

83 REO C2 When used a input port, the latch must be set .0 "1"

pale ca ein portwit latch

When vid ahinput part, watchdog

a7 (WO) wofoutpur) | simeroutputpin, orA/D converter | watchdog timer output

input pin the loth must beset to

r70(cm) worinuy |“ Bic A converter input

0300) Timericounter exteralinput

‘bit WO port with ate

‘When used arinput port, externa | External ntesrupt input

wotimout) | interruptingut pn, oF

81 (12) ee eee mputpin, | Timercounter? external nput

a0 (N72) eee External interrupt 2 input

92 (8CR) woWwor seit clock vO

bit VO port with atch

91 (50) Wo(oups) | Whenused asinput portorseial | Sera! data output

the latch must beset to "1°

89960) worinpur | °" Sera cata input

eines Pit vO port with atch

outpux vo) When used asinout port, the atch must be

ana) AGB output atte “t

2 Oviput

+ tau Output (output) | Foreus signal output Background braking contr! signal output

0, vo ‘npat Horizontal synehronoussandl input, Vertical synchranous signalaut

loser, osca input. output | Resonator connecting pin of anacren display circuit

Resonator connecting in

bx, x0uT input, ovpit

For inguting external lok, XIN s ued and XOUT opened

fad input eset gral mput

HO iRkoy ‘rputinout) | HOLD requesureleasesgnsl input | Sense nput

rest japut Testain fr out going tes! Be opened or fired to lowevel

v0 vv

Power suopiy

vss ov¢cnoy

ans

TOSHIBA TMP47C43.4/634/034

OPERATIONAL DESCRIPTION

Concerning the 47€434/634, the configuration and functions of hardwares are described.

As the description is provided with pronty on those parts differing from the 47C660/860, the technical date

sheets for the 47C660/860 shall also be referred to.

1. SYSTEM CONFIGURATION

(1) Program Memory (ROM)

(2) Data Memory (RAM)

(3) Operation clock changeover contr

(a) vO Ponts

(5) On-screen display (05D) control circuit

(6) A/O converter (comparator) input

(7) DiA converter (Pulse Width Modulation) output

2. INTERNAL CPU FUNCTION

2.1 Program Memory(ROM)

Programs are stored in address 0000 to 17FFy of 47C634 and in address 0000 to OFFFy of 47C434. By the

ROM data reference instruction [LOH A,@DC +, LOL A,@DC}, the fixed data in address 1000) to 17FFx:

and 0000 to OFFF1 can be loaded to the accumulator, respectively.

Adeess ass

00004 00004

Program

aan Program

|

orn, | a ort

1000, | Program

| ea ||

Fine

|

Data

a) arcass (0) a7cesa

Figure 2-1. Program Memory

Note. With the 47C434, permanent data are stored at addresses 0000 ~ OFFFH but, when checking

47434 operation using a piggy-back chip, it is necessary to store the permanent data to

addresses 1000 - 1FFFy, either

aa 4116

TOSHIBA

TMP47C434/634/034

2.2 Data memory (RAM)

The 47C634 contains 2:

x4 bits data memory bank 0 (DMBO) and 1284 bits data memory bank 1

(OMB1). The 47C434 contains 256 x 4 bits data memory (OMB0). The bank is controlled by OMB.

Adress Address

004 4 —

pmo | omso

00,

as

(a)

47C434 RAM Configuration (b) 47C634 RAM Configuration

Figure 2-2, Data Memory (RAM)

2.3 Operation clock changeover control

On the 47C434/634 only single clock mode is available. As single clock mode is automatically selected at

the initilization, there is no necessary to set system clock control command register (OP 16)

Singleclock mode

Normal: a

High-freq : Oxiiating

Lowtreq : Oxilating

Don't select

Hich-treq oscitating

fowireg : Stopped

Reset

ign-ireq: stopped

Low-irea : Stopped

Figure 2-3. Operation Mode Transition Diagram

any

TOSHIBA ‘TMP47C434/634/034

3. PERIPHERAL HARDWARE FUNCTION

3.1 V0 ports

The 47C434/634 have 91/0 ports (30 pins) each as follows.

3 KO; dbitinput

2 RA,RS : d-bitinpuvoutput (shared with pulse width modulation output)

3% AB 4-bit inputioutput

) R7 —; @-bit inpuvioutput (shared with comparator input and watchdog timer output)

% R& —; 4-bit npuvoutput (shared with external interrupt input and timer/counter input)

© R9 — ; 3+bit inpuvoutput (shared with serial port)

RA; 2-bitinpuvoutput (shared with on-screen display output)

® ke 1-bit sense input (shared with hold request /release signal input)

‘This section describes ports of @ and @ which are changed from the 47C660/860, and it describes port of

|, which item of on-screen display circuit.

‘Table 3-1 lists the port address assigments and the i/O instructions that can access the ports.

(1) Port Ra (RA3-R40)

This is a 4-bit UO port with latch. Its a port common to DIA converter(PWM) output port. Ré port

output buffers are Tristate, and each bit of them can be controled independently by the program

Controling the Tri-state is performed by the command register accessed as port address OPOO.

When some bit of the OP0O is 0, the corresponding bit of the output buffers becomes high

impedance state. The output latch should be set to “1” when the port is used as PYM output

port,the PWN output should be to “Hi level[PYVM data is all "O")when the port is used as R 4 port.

‘The output buffers should be set to high impedance state,when the port is used as input port. And

the R4 output latch be set to “1”, PWM output be set to "High" level, and the output buffer be set

to High-Inpedance state during reset.

Ra Port Address OPO4IPOA)

3 2 1 °

Rea Raa nay

mwas) | cpwaneay | wir

input dats

ouiputdate

ft pase)

wins

Inputaata -

Output date

— Tee rn,

rae | pf} _

a

Inout date |

Tateh ~

Ouipurcata

{Tras RT)

inpur dat -

ouput data Treo 06)

opo0 [in aave

ome

cok NITES UTESTP

Figure 3-1. Port Ra PWM)

. 4.118

TOSHIBA ‘TMPA7C434/634/034

(2) Port RS (RS3-R50)

The 4-bit VO port with latch. The only RSO pin share D/A converter (PWM) output. The port output

buffers are tri-state, and each bit of them can be controled independently by the program.

Controling the tri-state is performed by the command register accessed as port address OP 13,

Example: LD A.#1121g —; OP1FA1111g

out A,x0P13

OUT OSH, n0PU5 RS porte-Si,

AS Port (Port Address OPOS/ P05)

2 2 1 °

nS Rs? RS R50

rv

input ote

output data ns3.a51

F354

‘put ata

output data 50 (TR

ad

P13

SET/CLR | IN/TEST/TESTP

Figure 3-2. Port RS

(3) Port 87 (873-870)

The 4:bit UO port with latch. When used as.an input port, the latch should be set to "1", The lateh

is initialized to "1" during reset. R72, R73 pins s VO port usually.

Pin R70 (CIN) is shared with the digital input usual and the A/O converter (comparator) input for

‘Auto Frequency Control signal detection. CIN input is comparator input and setting of 3-bit DIA

convert for reference voltage are performed by the comand register, Pin R71 (WTO) is shared with

the watchdog timer output. R70, R71 pins latch is initialized to "1" during reset, and they are able

10 use UO port usually

input data t—<}y

ss

inputseiecior reference voltage

ate

fe

RY VO Pert (Port address |PO7/0PO7) input data ‘arepsarUl jel1as 40 ndu!smeIs au: 910N

swesBo1d 1950 ay) J0} 3geUeAeUN “2818 PIAIISO/ 9) 5UEIW,-—. “1 31ON

: : : SI = a TienGer OTF Tou sBIR] ar

2 : > = = io = tos 08 powepon| at

: : : = : 8 = remiooz amuse ieee ata

: 2 : = Z 8 = fPawo> {nn aui pemjeoun| St

Z : : : : 2 = pas rear ata

: : : = - 3 7 pare posuepon| vt

2 : : z : 8 =| enuoordnusns) ton rotor eel 4

: : : = : 8 : rand spsuen ep ed povnapun| at

2 : : : : 8 : somes 9)09 Ane pouanun| ch

2 : : : : : : I pounspun| 31

2 : : : : 6 : reaver sn Sopanienn Poujepon| a

: 2 = : : s : avapun| 9

2 : : : : 6 : jones (od sudonns = nt meee ates

: 2 = : : iS : senvos indo touenso> are saviapun| Zh

: : : : 5 S : = fh

2 : = : Z : pou vonviado vo.

: : : : a g S eas Fa

- 5 i jenuos orp sav0idond

S 5 ° c pane eeee cmowrndorsmes] 30

7 : 5 a i. wos nso,

2 ° ° aneniosyoyonue>ayouy| anjen yuno> jonve> stouey| 0

- . a 5 a : “onaer ewes 050 — 20

2 : : S : = = @

: ° - 3 9° 3 ved nine va wodinduvu] vo

- fs) = S 8 é $e nding fedeaies ater

: 3 : 3 8 & Ted andi By aiedures| 90

3 5 : S } é $e ining ce tdurce] 20

3 3 . ) ° i) vod andino 94 vod indur sy] 90,

5 3 : 2 § 6 ed indi Sedinduse| $0

3 8 : 5 8 & 308 inno re Sioeinass| 30

- = : : : 7 ae = %

: = : - : : = = Fa

: 7 : : : : = 3

: a : 6 é wosineox| "00

Wisk leewas| wan vo |. | @vn@ino| 5 2 w "ne 7"

19 | gra usail a’en 135 | HORNE [HH 1m ME TOL ae sine

ven On

4.120

TOSHIBA ‘TMP47C434/634/034

3.2 On-screen display (OSD) circuit

‘An on-screen display (O50) circuit used to display characters and symbols in built into the TV screen,

Amaximum of 32 characters.as 16 columns? lines,out of 48 character patterns can be displayed at a

time

3.2.1 OSD Circuit Function

Number of characters aBkinds

@ Number of charactersdisplayed 32 characters(16 columns x ines)

® Composition of a character 8x8 dots (with smoothing function)

&) Size of character 2 kinds (selectable line by line)

'5 Color of character 7 kinds (selectable character by character)

(© Display position variable horizontal 64 steps, vertical 64 steps

3.2.2 OSD Circuit Configuration

ose C+} Sxilaon

—)) pba

co ees

Vertical Counter | pee

Peete

Figure 3-4, OSD Circuit

3.2.3 OSD Circuit Control

The OSD circuit is controlled by the command selector (OPOC) and control register (OPIA). Table 3-2

shows the relationship between OPOC and OP1A. OP1A is multiplexed with the six output control

registers which conteol the display start position, color of character and character size of character, and

the two transfer control registers which transter character data to the display memory.

The output control registers consist of 8 bits and all bits can be written by accessing OP1A two times.

However, the second access is not required unless the second data are changed. The addressed "0 to 5”

are assigned to the six output control registers. OPA can be accessed by writing the address of the

control register where data are to be changed to OPOC, The transfer control registers can be accessed by

writing "6" or "7" to OPOC. The transfer contro! registers have a 12-bit configuration and can access

COPIA three times succession. The first access sets which column is displayed within one line 16 columns.

The second and third accesses written 6 bit of character data

The display memory has a 16-columns x 9-bit x 2 lines configuration with a one-to-one correspondence to

the number of columns displayed on the screen, The display data consist of 6 character data bits and 3

color data bits for a total of 9 bits, When “6” is written to OPOC, line 1 is stored to the display memory,

when "7" is written to OPOC, line 2 is stored. That is after accessing OPOC, the character data specified

the second and third times are weitten to the display memory area specified in the first OP1A access

color data joaded to control register DCRS0. Thus color can be specified for each

character, After setting of ali contiol cegistersis completed, the character data read from the character

ROM(00 to 2Fyjare output to the R, Gand 8 pins together with the color data by setting OPOC to “F”

° a2

TOSHIBA

‘TMP47C434/634/034

(050 command

(080 contol register tobe accessed through OPIA,

selector 0°06) “ a

‘Control forthe horizontal stor position ofthe fini play Hine

a 2 1 o

ug pero [- [| asis [sta] cist accons

enor [asia [Hse | nst1 | msi} (astaccess)

‘Contador the vertical start postion ofthe fst play hine

3 2 1 0

u coca [= =| Sis [_vsta] (se acces

coca [ysis [vere _| vsit_[ vsio_} stacces)

‘Contol for the harizonial stor position ofthe second spay line.

3 2 1 0

: perzo [_- =| vss [Ws2a | castacces

cess [Tas [Hse | Hser | HS20 | astaccess)

‘Contol for the vertical sar position ofthe second disply line

3 2 ‘ 0

3 cee [Te =] vss] vse] cst acces)

ocean [yaaa [sex | vser [v2] astacess)

‘Conta for the choracter sizes smoothing switch and O30 output paarities

3 2 1 °

H crag [e271 [cso [Git [G10] st acces

ocrar [esnaz [suv [vw | aca | (astaccess)

‘Conia fr the color egater and O50 output buflers tate

3 2 1 °

5 oceso [not] Got] a0T | (tstacces)

ces: [cera] core [cory | toro | staccess)

“lay memory write made forte brat display Lneaddress 00 OF)

3 2 1 0

6 May | oma? | omat [OMAD] (Istaccess)

5 =| cmas | enaa | tastacces)

eas | ear [cat | crao | cast acces)

Gisplay memary wile mode forthe second display lne(aadeess 10-17)

3 2 1 0

7 MAS | OMA? | MAI | BWAD_] (Istaccess)

5 =| ceas | chad | (2staccess

Cas | Gad _[ cAI | cRAO) Gxtaccoss

é Aisplay OFF

F ‘splay ON

Table 3-2. OSD control commands and control registers

4122

TOSHIBA ‘TMP47C434/634/034

«

) Composition of character and smoothing function

Each character is compsited by 8x8 dots. Each dot corresponds to a bit in the character ROM,

Figure 3-5. (a) shows an example Composition of a character.

Smoothing function is the function to make characters look smooth. In the time the smoothing

function is enabled, additional dots are displayed in the middle of the place where two dots

contact each other only at a corner. Controlling of the smoathing function is performed by ESMZ

in the OSD control register DCRA1. Figure 3-5. (b} shows an example of the smoothing function

(a) without smoothing (b) with smoothing

Figure 3-5. Composition of character and smoothing function

(2). Character size and color to display

Size of the characters displayed on screen is selectable line by line from 2 sizes. The size of the first

and second display line is disignated by C$11-CS10 and C521-C520 in the OSD control register

DcRao,respectively.

Table 3-3 shows the setting values and character sizes of DCRAO,

Table 3-4 shows the display character sizes,

One out of seven colors can be selected for each character to be displayed and are determined by

RDT,GDT,and BOT of OCRSO. The color data are written to the display memory automatically at the

same time as character data are written

eee | ad Te

Comacersne | cipiine | soelyine pape) (eee

cweraay — | csar | cs20 | est | esto onsen | ROT | cor | sor

smatcraracter | + [0 | a | 0 Blank ofola

laygecnoracter | 0 | a | o | 4 Ave ota) tons ian

aspiyor | oc | o | o | 0 Green of: fo

Figure 3-3. Designation of character size sian o fafa

= ea Lodee

mall character | large character

azenda o | 1

ot site Byox Mose | ATuox sTose

Yellow fo

eharacersize | 1619 x 18tosc_ | 32Ta0% I7Tosc

white a |

Note. Tio the period of horizontal synchrorous signal

Tose :the period of OSD clock oscillation Note. Colorto display: RGB pin uses Red,

Green, Blue such as.

Figure 3-4, characterize Table 3-5. select of color to display

a)

Display start position

Display start position of each display line on screen can be shifted by software

The vertical and horizontal display starting position for the first line is determined by HS10 to 15

and VS10 to 15 of OCROG to 11

e vertical and horizontal display starting position for the second line is determined by HS20to25

and V520 to 25 of DCR20 to 31 Each has a resolution of 64 steps

The control register and display line on screen are shown in Table 3-6.

ana

TOSHIBA ‘TMP47C434/634/034

FIRST DISPLAY AINE

wi T 7

82

Figure 3-6. TV screen image

symaou ‘CONTENTS

isto-nsis | hontontel star postion ofthe tus aisplay line

HSt = (32 KHSIS 4 16x 4514 © BxcHS13 6 @HSIZ 62xHSIT #HSIO) x8 6X) Tose

somvsis | Ystical stor postion of the fist display ine

VS1= G2XVSIS + I6XVSI4 + BXVSIS + 4xVSIZG 2A VSIT 4 VSIO) KATO

wis20~1525 | POtHOnto! star postion ofthe second diply line

HSQ= (32 xHS2S + V6 HS24 BKHS23 ¢ @xHS22 6 2 HS2 HS2O) x4 oH) Tose

vsi

ar patton ofthe second display ine

2525 + 16 VS24 6 8x V529 14x VS22 «2H VIZ VSIO) KATH

Note. _X. Xi 17 when small character

X's 34 when large character.

sition

s20~vs2s

Table 3-6. Display start

+ The vertical display positions of lines 1 and 2 can be specified independently but,to

prevent overlapping of the two lines on the display, the value for the vertical display

position of line 2 must satisty ( VS2>VS1 + C511 x 16TH + C510 x 32TH

3.2.4 Y/BL signal

ne ¥ signal (the logical or output of the 8, G and @ signals) makes the display clearer by deleting the

background only where characters are displayed. The BL signal deletes the entire background for one

character (88 dots) and is output for al data except that at address 2Fy in the character ROM.

The ¥iBt pin is used fer both Y signal and BL signal output. Which of the two signals is to be output is

determined by the upper 2 bits of OPOA. The dotted lines in Figure 3-7 show the YIBL signal output being

2, 26) GaP

“(OL “ 45) BYBSA | aa

WPS

Figure 3-7. Example of Y and BL signal output

2 4124

TOSHIBA

TMP47C434/634/034

3.2.5 Control of OSD outputs buffer

The OSD outputs for ¥,BL and RGB use tri ~ state output buffers for which the respective polarities can be

inverted. Polarity is controlied by ORC41 and tri ~sta

te is controlled by DRC51

Bit 3 of ORCAT is used for controlling the smoothing function

vogue oe | wmoo | UR wo wet

3 | ewe |__| smoouina ov mooring OW

2 aw a acive Fgh ‘civ om

ones

ow py active righ ve Low

| ace | ace dove gn sive Low

3 | ts | viet | ovpabutte or* | ovpuouteron

2 | |e output butter OF | outputbutfer on

ones:

roan | os aurputbuteror* |” ouiptbutler on

oar |e cuiput utter OFF |” cutputbuter ON

Figure 3-7. Control

3.2.6 RA Port Function

R signal output and G signal output po:

possible as normal lO ports. RA port and V/BL select

of 0S output

ts are also used asl/O ports. When not used for colar signals,use is

1on is performed by OPOA,

Aiso,the upper 2 bits of IPOA are used to input the OSD display status.

[Levon

portaddeess_ 1P0A,

vor [vor oat

Le

RAO output

RAL output

‘control of O$0 output and RA port

opoas | OPOAZ peo pane

ope pepeleyy

ope fawo fo} a Pe |

1 1 | RAO, Rat | 6 [eu

[fest aisplay ine sispoy ON

1 fst display tine display OFF

0: second display line display ON

Figure 3-8

1 :second display line displey OFF

Port RA

4125,

TOSHIBA

3.2.7 Character ROM (Standard characters)

‘TMP47C434/634/034

Figure 3-9 shows the standard pattern characters and symbols available as character data. Character

patterns can also be set by the user. For details, refer to the section on piggyback chip 47C034,

or

of,

=

=

eer

” a

1 : a

(ume d

4 Foot

0 9 n

b i

2 ri 7

Me

@

,

8 a

rf Spe a

| | | para

Py i

1 1 3

7 5 7 fi w az)

a} i ar =

5 i. i t

2m 28 a 2

5 .

: Me a

raat ‘ _

ue 5

28 x 2

Teague

Figure 3-9. Character ROM address and character pattern

TOSHIBA TMP47C434/634/034

3.3 3-bit A/D converter (Comparator) input

Comparator input consists of a comparator and a 3-bit D/A comvertor. AFC input voltage can be detected.

Jn B steps by sensing bit 0 of 1PO7 while cahnging the reference voltage (D/A convertor output voltage)

‘with the command register (OP 12)

70 pin is also used for comparator input. Bit 3is used to set R70 pin for ordinary digital input.

The comparator is disabled and bit 3 is set to “0” during reset. The latch should be set to “1” when R70

pin is used for comparator input and digital input.

3.3.1 Circuit Configuration

digital input

cy (}-—_}_mmecainget comparator

af soko

ceovetet_[rearence we,

vole

orn wr

aT ster

Figure 3-10. Comparator input circuit

3.3.2 Control of Comparator Input

The reference voltage of the comparator is set using the lower 3 bits of the command register. Table 3.

shows the reference voltage when Voo = SV.

Comparator input control command registor (Port address P12),

3 2 1 0 (OPi2 | reference

eA, sre {intial value 0000) 21 0| voltage tv

0.0.0). 98

[Comparator input control eel

0 = Disable oro) 18

\ = Enable ort) 256

a roof 312

seting value ofrelerence voltage tov} 398

5) Vase Woo te mv 8T¥I vyof aa

ey vit S00

Figure 3-11, Control Command Registor Table 3-8 Reference Voltage

. 4127

TOSHIBA ‘TIMP47C434/634/034

3.4 D/A converter (PWM) output

The 47C434/634 have five channels built-in D/A converter (Pulse width Modulation) outputs. PW

output can easily be obtained by connecting an external iow pass filter.

WMA outputs data are multiplex to the Ra port and R50 pin, When the R4 (PWM) port and R50 pin are

used for PW output, the corresponding bits of 84, R50 output latch should be set to "1". The Ré, RS

output latch is initialized to "1" during reset.

Pa

written to the

outputis controlled by the buffer selector (OP17) and the data transfer buffer (OP18). PWM data

ata transfer buffer can be sent to the PWM data latch by writing “Cx” to the buffer

selector, and PWM output PYM output. PWM data transferred to the PWM data latch remain intact

Until overwritten. Resetting and holding clear the buffer selector, data transfer buffer and PWM data

latch to "0" (PWM output is "H” level)

3.4.1 Configuration of Pulse Width Modulation circuit

Configuration of pulse width modulation circuit shown in Figure 3-13,

3.4.2 Output waveform of PWM circuit

(1) PMO output

PWIMO is 2 PWM output controlled by 14 bits data. The basic period of the PWWIOis Try = 215 / fe

‘The higher 8 bits of 14 bits data are used to control the pulse width of the pulse output with the

period of Ts = Taa/ 64, which is the sub - period of the FWMO. When the 8 bits data are decimal n

(0 = n= 255), this pulse width becomes xo, where to = 2/ fe

The lower 6 bits of 14 bits data are used to control the generation of an additional to wide pulse in

each Ts period. When the 6 bits data are decimal m (0 = m 5 63), the additional pulse is

generated in each of m periods out of 64 periods contained in a Ty period. The relationship

between the 6 bits data and the position of Ts period where the additional pulse is generated is

shown in Table 3:9

a

WMT-PWINd output

Each of PWV to PWNS is a PWM output controlled by 6 bits data. The period of them is Tw = 27/

fc. When the 6 bits data are decimal k (0 < k < 63), the pulse width becomes kx tg. The waveform

is also illustrated in Figure 3-12

to | Pulsewidth= (a+ to

Tw

“TULL JULI.

Figure 3-12, PWN Output Waveform (its shown to the additional pulse Ts 1) and Ts (63) of the PUTMO)

4128

TOSHIBA ‘TMP47C434/634/034

a . _

musics ca

SPs Pe

a : 5 as

2 7 = fe ALO"

oT fs Rs Nc

2 < 2 Se fm

2 ‘ gMENM “

- i . : Oj} PWMO

3 x T MATCH SIGNAL | R

elie E z 5

‘ : i ast\

° fi Ss

* § #

2 nN? 5 a3] [J Ey enn

. 2 Bas

| He ube

Se Ze Fre

2 oP FEW] BEND Kae:

7 alltel mascusenat |) Ofee PRE

eee anes = a

4 als| i uD] Ee

. eal tee ;

= HPL aN] Kawe oc

® oy: - T suzanscu |, Of* PMS

cf ST are z =

: i BNE

& ie z= rer

-) ot Ss f" EY| os IN ALLO

Li} by: Us rrr aes

: nae

Figure 3-12, Pulte With Modulation ic

4129

TOSHIBA TMP47C434/634/034

eens Flav portional Tpwhare De guppies gereaTed

bio 3

bier 16,48

wie 8, 24, 40, 56

bia 4, 12, 20, 28, 36, 44, 52, 60

bite 2,6, 10, 14, 18, 22,26, 30,-~, 58, 62

bits 13.5, 7.9, 11,13, 15, 12.0, 58, 61, 63

ote, When the corresponding bits "17, tis Output

Table 3-9, Correspondence between 6 bits data and the additional pulse generated Ts periods

3.4.3 Control of PWM circuit (Data transfer)

AWRI output is controlled by writing output data to a data transfer buffer (OP18). For writing, the

output data are divided using the buffer selector (OP17). Buffer numbers are assigned to the data

transfer buffers for these divided data, after which the data are written as shown in Table 3-10.

Gh The number of the transfer buffer to which the data are to be written is written to the

buffer selector (OP 17)

The corresponding PWM data are written to the selected buffer (OP 18),

Operations ‘D and 2 are repeated, continuously writing data to the transfer buffer.

When all of the output data have been written. “Cy” is written to the buffer selector.

‘While the output data are being writen to the transfer buffer, the previously written data are being

output. For PWIND output, switching to PWM output occurs at a maximum of 215/fc (sec] (at 4NtH2,

8192s) after "Cy" is written to the buffer selector. For PWM through PW output data switching, this

requires fc isec| (at aMHz, 12843)

saa

3 Bit of PWMD transfer buffer 13 ~ 10, write | Preceding data

Table 3-10, The bit and Butter number of data transfer Buffer

4.130

TOSHIBA ‘TMP47C434/634/034

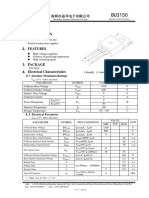

ELECTRICAL CHARACTERISTICS,

[ABSOLUTE MAXIMUM RATINGS | (Vss=0V)

PARAMETER SYMBOL ins RATING usr

supply Vottege Voo 703107 v

input Vottage Mine =0310Von+03 |v

= Vourr | Except sink open drain pin =9340¥e0+03 |

Voura_|Sink open drain pin except 7 port =931010

Tourn | AB port 30

Jourput Current (Per pin} ma

Tours | RP. 88. #9 port 32

[Ouiput Govrent (Tora E tou [Ab prot oo ub

Power Dissipation PD 600 mw

Soldering Temperature time} he veo oe | oo.

Storage Temperature na = 550 135 ©

Operaung Temperature Top 300070 c

RECOMMENDED OPERATING CONDITIONS | (Vs5=OV, Tope = ~30t0 70°C)

PARAMETER [SY™BO PINs CONOITION win wax [UT

ame Rorna a

supply Voltage Yoo so |v

inthe O10 mode |__ 2°

Viny_[ xcept rysteresis input Yoo x07

Inputrighvokage — | vy | Hysteressinpot woor4sv [vopx075 | voo | v

va Vop pe

ans [Koper with pull-apipal-down 30] 70] 150

Input Ressance Ka

Ana__[ RESET 100] 720] 450

‘uiputleokage Trstaie

Current uo |R6, RB, ASport(opendrain) _ | Voo= 5.5¥, Vour = 5.5V_ -|- 22] 0

Sutput tion Von _[ por toush-pui voo=asv.ions 200 | zal = | = |

Voltage Nong | Ror tstate) one 8 8¥, tows -o7ma | ail — | —

Nous [#7 R6,Ropon op=45¥. lo. =18mA

Output tow voltage To [por trate) Rio0 45¥. lo =07mA Tyr py

Ouiputiow current fig, [REpOrt von = 85, Vou 1.04 = [0 [= [ma

Suppiyeurent | Voo=55¥, - | af elma

Jintbe Noe! mod fen ates

suapiycurrent — |, Voo=55¥ = | os] 10] va

fintne HOLD mode)

Note 1. Typ. values show those at Topr =25,Voo =5V.

Note 2. Input Currentiy : The current through resistor is not included, when the pull-up

pulldown resistor is contained,

Note 3. Supply Current: Vin=5.3VI0.2V

The KO port is open when the pull-up | pull-down resistor is

contained.

The voltage applied to the R port is within the valid range Vu or

Vn

A/D CONVERTER CHARACTERISTICS

PARAMETER [pvmeou Pins CONDITION win | We. unit

Anologinautvetiage [Yan [cin vs | -

‘ArOcomersonevor | — eniee 88

4.132

TOSHIBA ‘TMP47C434/634/034

AC CHARACTERISTICS | (Vs5=0V, Vop=4.510 6.0V, Topr= ~20t0 70°C)

PARAMETER [p-ma00 CONDITION Min Tye. | Max. [UNIT

instruction Cyle Time ty 19 - | [

ighlevel Clock Pulzewietn | wen |

Forenternal cock operation 0 - | - fo

Lowlevel lock Pulse wiathy | twee

Shit data Hola Time ‘soe ostey-300 | - | - | os

Note, Shift data Hold Time

External ecu for SEK pin and SO pin

veo xe

oka

o- 4

Lsope

so

ae

RECOMMENDED OSCILLATING CONDITIONS

[RECOMMENDED OS¢

(1) ames.

Ceramic Resonator

c5a4,00MG (Murata)

KBR-4.00MS, (KYOCERA)

Crystal Oscillator

2048-6F 4.0000 (ToYOcom)

(2) 400KH2

Ceramic Resonator

cseao08 (Murata)

kaR.4008 (KYOCERA)

(3) SMe (for DOS)

LC Resonator

TBEKSES-30361FBY (TOUKOU)

Sevial port (Completion af transmission)

Grout

ov

(Ws5#0V, Voo =45 to 6.0V, Topr= 30 to 70°C)

xn xour

T 7

br,

Gam = Crour 20F a

i

ain xour

rout =220pF,

= 5.8K e0ce

Can Ceour = 100, ol

Raour = 10K2. in a

4.133

TOSHIBA ‘TMP47C434/634/034

TYPICAL CHARACTERISTICS

y Reta Koport gp Reta Reset pin

Ka i

rr 400

soo 4 oe

“0 200} ote

0 a)

oem)

Jou Vou CMOS Rp 14, HECWIN CMOS tone Jon Vou THLSTATE port.

fou « ton

w Voo=45¥ f Tyon=5.5v jo Voo=48V)

wnt rede a rezaee os rizane

400 800 . 20

300 sao as

|

=209 : 400 aro}

=109 nia =200 |

| |

‘ Von oLod Ww 8 Vou

a 8 ze BM OM

Rport \ Ps, Pe pont Jot. Vou TRISTATE port

nn iki] on=45V T

7 a beer |

“a (meezre |

20 6

| |

4 0 ‘

rr] |

a Co o 2 4

0 Vo, 0 Yo. 0 LI vu,

oe oa 2 oe 012 oa 88 1a)

Inn- Von. hp WoB=e

maftaszee | | nai] Nove s 6

4 : 4

Tt

Lt} |

* I

1 : |

2 t ii

(Le Yon 0 rol I t

. 6 or ea F 4 Maat

4134

TOSHIBA TMP47C434/634/034

INPUT/OUTPUT CIRCUITRY

(1) Control pins

Inputioutput circuitries of the 47C434/634 control pins are shown below.

conraowem | 00 caRCUITRY REMARKS

05C. erable —

_*~} Resonator connecting pins

xn Input w— R =1K0 (yp.

xout ouput a a Ry =1.sMa (yp)

5 fo =24i (4p

ah xoUr

‘shee Hysteresis input

a fas Contained pullupresstor

aE Input i

Hysteresisinput

inp . ,

(serve input

(taputh 9)

A= 1x0 yp)

& Contsinesputidown

: ~<}- "OO resistor

est Inpvt a

ay =70K0 (yp)

or R= 1KO typ)

OSC. enable =

* Oscilation terminals for DOS:

scr Input to a =k (yp)

a a ‘s . Ry Ry = 1SMQ (typ)

at Ry =2K0 (typ)

ox

Synchronous signal input

co .

wo input 6 ih Hystereisinput

Re tk (yp)

4135,

TOSHIBA ‘TMP47C434/634/034

(2) 0 ports

The inputioutput crcuitries of the 47C434/634 V/0 ports are shown below, any one of the circuitries

(PB, PC, PF, PU) can be chosen by a code as a mask option,

von [0 TNOUTOUTPUTERCUITAY nd CODE ery

fn Poa

' Putlup

00 ; 5

0 | put es Iho pultcomavesitor

~ J push-putl

1h Comparator input

x ‘R70 pin)

4 | neixa'wyed

Init ez

—beHé aeiKa yp)

| eoerancugs eis

iby foo) SM — 7 Sst 50)

Ragipwnia= {A80 18)

Ra3cbwhi) > she

ASD.PWH) > See iIntD

mt Seto)

Ne Ne

Ne ne

Bee Ne

asa Reb

roiciniee SHo10¢

anitnTOh = eaeset

Rae Sour

me oan

Koo csr

wr “ose

kon 5c

ro 25

Ne Bi 2 a

foe 7

Reies 25 &

nee H26G) a0 7 GB

tae gpQ 2 Os

Prom q2a@) 6 Ox

bie GB@un os BP es

tae 438 QSh wee

rae gn @ 2 4 @ ash Son

W855 432@ ono 9 GD 53 S20

PIN FUNCTION (Top of the package)

[7 Pananae input | Output FUNCTIONS

mo Outeut | Frown memory suaren ont

7 8 input [rogram memory aatainput

fe Chpenabie signal vipat

: oro [PPansblesignatovie

ee

vee

7 Power supply

eno.

A.C. CHARACTERISTICS

[acares delay time tao |¥ss=0¥,von=a5t06 ou = = 150 8

Data Sewn Tine s__ [C= 1009 wo | = = oF

Data Hold Time in [ropes -aoro70re o | - 1 - 7

4.137

TOSHIBA ‘TMP47C434/634/034

NOTES FOR USE

(1) Program memory

Figure 1 shows the program storage area, The 47C034 has a data table at addresses 2000-217F

(48 characters x 16 bits) for on-screen display data so that characters and symbols can be displayed

on TV screens, Thus, a 64k EPROM is not used.

128K _EPOM 126K EPROM 128K EPROM

000 0000, 00005

Program

Program Program

(cara) ° oa

ore

obo 1000 1000

(ata) (date)

1780 | “Data conversion able

iver | 22) i

(Note) Don't vie ot eee

= Don'tuse

EEO [Dota conversion table

2000 2000 2000

Oisplaysatatabie > splay data table splay data table

ho pay data tabi pine eDiplay data tab die |_ Display data tab

Don't use Dor'tuse > Dorttuse

BHF are are

(a) 47ca3a ) a7ce3a to 47635

Figure 1. Program area

Note. When using the 47C034 to check 47€635 operation, place data conversion tabels at two

locations. With the 47C434, permanent data are placed at addresses 0000-0FFFy but, when

the 47C034 is used, itis necessary to put the same data that is at addresses Q000-OFFFy at

1000}, and following addresses. Also, with the 47C634 and 47C635, the permanent data at

addresses 1000-17FFy are read out when the permanent data at addresses 1800-1FFFy are

accessed

4.138

TOSHIBA TMP47C434/634/034

(2) Data table for on-screen display (05D)

With the 47C034, an OSD display character ROM is generated inside the EPROM used. The

characters configured using the data loaded to EPROM addresses 2000-217Fx are display on the TV

screen, therefore, characters can be freely set by the user. When a program is being submitted,

write the character data to 2000, and the following addresses. Figure 1-2 shows typical character

(8 x B bits) addresses and data, Figure 1-3 shows alist of standard patterns in hexadecimal.

address 0004 78 84

O10" 78

3a

cuore cata 020 18 26

030 78 64

2010 Ty 040 78 84

5 ’ Tas 950 10 23

a 060 Fe 82

v2 | TTT me 070 FE 80

non os 980 76 82

050 38 10

zoe | 0 AQ Be 84

ais 20 960 82 Co

Sco 38 4a

2016 40 950 38 44

207 re eo 7¢ 82

GF 82 82

Figure 2. Typical character 10 92 92

Note. The data area for one character

fs 8 bytes. The starting address 140 90 40

is the value entered at the 180 CO CO

character ROM address (00-2F) 189 FC EC

specified by the upper 6 bits of

the 9-bit program aree (000- Figure 3, Standard character data (from address 2000s)

17F uh

(3) Inputoutpy ports

The inputioutput circuit for the 47C034 inputioutput ports is the same as that of

and 47€635 (code : PC), except that a pulldown resistor is not built into the KO port

When using as code P8 or PC evaluators, itis necessary to connect an external resistor

he 4704341634

a) Cou: 98 (0) Code: 9c

Figure 4 VO code and external circuitry

Note. The 47¢434/634 do not have built-in PI, P2 and R3 ports. Also, the 47C034 pins RA0-

R43 and R50 form a tristate output buffer; therefore, caution is required when using

as the 47C434/634 code PF

4139

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5819)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Manual PBP1Document10 pagesManual PBP1Tecnico GenioNo ratings yet

- AN5165KDocument25 pagesAN5165KTecnico GenioNo ratings yet

- S3K60Document2 pagesS3K60Tecnico GenioNo ratings yet

- FL400 THRU FL408: In-Line Miniature Single Phase Silicon Bridge VOLTAGE - 50 To 800 Volts CURRENT - 4.0 AmperesDocument2 pagesFL400 THRU FL408: In-Line Miniature Single Phase Silicon Bridge VOLTAGE - 50 To 800 Volts CURRENT - 4.0 AmperesTecnico GenioNo ratings yet

- RD2003Document3 pagesRD2003Tecnico GenioNo ratings yet

- SBR10100CTB: V (V) I (A) V (V) at +25°C I (Ma) at +25°CDocument5 pagesSBR10100CTB: V (V) I (A) V (V) at +25°C I (Ma) at +25°CTecnico GenioNo ratings yet

- Features: Maximum Ratings and Electrical CharacteristicsDocument2 pagesFeatures: Maximum Ratings and Electrical CharacteristicsTecnico GenioNo ratings yet

- Shindengen: General Purpose RectifiersDocument6 pagesShindengen: General Purpose RectifiersTecnico GenioNo ratings yet

- KSC2331 NPN Epitaxial Silicon Transistor: FeaturesDocument3 pagesKSC2331 NPN Epitaxial Silicon Transistor: FeaturesTecnico GenioNo ratings yet

- Data Sheet: PDTC143ZTDocument8 pagesData Sheet: PDTC143ZTTecnico GenioNo ratings yet

- 4 44 4.1 .1 .1 .1 Absolute Maximum Ratings: WWW - Jdsemi.cnDocument3 pages4 44 4.1 .1 .1 .1 Absolute Maximum Ratings: WWW - Jdsemi.cnTecnico GenioNo ratings yet

- STR-W6754: Universal-Input/100 W Off-Line Quasi-Resonant Flyback Switching RegulatorDocument8 pagesSTR-W6754: Universal-Input/100 W Off-Line Quasi-Resonant Flyback Switching RegulatorTecnico GenioNo ratings yet