Professional Documents

Culture Documents

CMOS-Based Physically Unclonable Functions: A Review

CMOS-Based Physically Unclonable Functions: A Review

Uploaded by

JessicaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CMOS-Based Physically Unclonable Functions: A Review

CMOS-Based Physically Unclonable Functions: A Review

Uploaded by

JessicaCopyright:

Available Formats

CMOS-Based Physically Unclonable Functions:

A Review and Tutorial

Kamal Y. Kamal, Radu Muresan, and Arafat Al-Dweik

ABSTRACT This article reviews complementary metal-oxide-semiconductor (CMOS) based physically

unclonable functions (PUFs) in terms of types, structures, metrics, and challenges. The article reviews and

classifies the most basic PUF types. The article reviews the basic variations originated during a metal–oxide–

semiconductor field-effect transistor (MOSFET) fabrication process. Random variations at transistor level

lead to acquiring unique properties for electronic chips. These variations help a PUF system to generate a

unique response. This article discusses various concepts which allow for more variations at CMOS

technology, layout, masking, and design levels. It also discusses various PUF related topics.

INDEX TERMS Hardware security, IoT, PUF, RFID, smart card.

I. INTRODUCTION against counterfeiting [8], [28]–[32]. The mobility of objects

Hardware authentication is getting rising importance to cope adds more security threats; for example, a smart card would

with the growing security concerns. Counterfeiting is among sometimes operate in untrusted environments where an

the significant threats to supervisory control and data attacker may have time and tools to breach it[33], [34].

acquisition (SCADA) and the internet of things (IoT) [1]–[5]. The main contributions of this article are as follows:

Counterfeiting an object such as sensor, radio-frequency

identification (RFID) tag, machine-readable document, or - Review PUFs types, applications, and challenges.

RFID-tagged product involves various security and safety

- Classify PUF into various categories.

aspects [6], [7]. This urge to adopt a verification approach that

enables an authorized organization to remotely check a - Present simplified mathematical representation for a PUF

device’s authenticity [8]–[18]. Furthermore, there is a rapid basic metrics.

growth of contactless machine-readable passports, persons - Review the sources of MOSFET variations and help draw

mobility monitoring tags, vehicle mobility monitoring tags a road map for complementary metal-oxide-

[19], public transportation smart tickets [20], shipped goods semiconductor (CMOS) based PUF design and

mobility monitoring tags [21], physical access smart cards manufacturing, toward acquiring unique devices.

[22], banking smart cards, and near field communication

(NFC) in smartphones [23]. Many of those devices have been II. PRELIMINARIES

vulnerable to security attacks [24]–[26]. This section presents a PUF’s basic concepts, properties, and

On-chip hardware security for intellectual property (IP) terms. It also reviews the origins of a MOSFET-based chip

copyright protection of integrated circuits and other objects uniqueness. It then discusses various guidelines to acquire

sometimes requires authenticity solutions. Storing on-chip such unique properties during a PUF chip fabrication process.

secret key is not a secure approach against invasive and side-

channel attacks. Cloning an identification number (ID) stored A. Notations and Definitions

on a non-volatile memory (NVM) of some smart cards is easy, In this article, random variables are denoted in upper-case

instant, and costs only tens of US dollars for the reader/writer symbols; for example, X represents the input challenge bits to

equipment and tens of cents for a blank smart card [27]. the PUF system; while, Y represents the noisy output response

Embedding a physically unclonable function (PUF) within an bits of the system. When a response is considered a reference,

electronic chip helps secure a smart card or an RFID tag it is denoted as R. If Y is a random vector, then its length

VOLUME XX, 2017

(the number of the string bits) is denoted as ‖Y‖ . Hamming

distance, D (Y1 ; Y2 ) between two vectors (or strings) Y1 and

Y2 with an equivalent number of bits, represents the number

of bits that have the same position within a vector but with

different values, i.e., D( Y1 ; Y2 ) ≜ { j: Y1, j ≠ Y2, j }, where (j)

indexes the position of the compared bits within the two

vectors, Y1 and Y2 .

Defining a PUF requires to identify the random function.

FIGURE 1. PUF authenticity cause and effect block diagram.

Definition 1: A random function is a function for which

knowing some inputs and outputs does not enable guessing

the output against the other non-observed inputs [35].

A PUF can then be defined as:

Definition 2: A PUF is an unclonable physical function

whose output is hard to determine theoretically but can be

measured experientially. In other words, a PUF is a unique

physical function that is easy to evaluate, yet impossible to

clone physically and hard to model mathematically. A PUF

security is hereditary, so any device equipped with an

inseparable PUF becomes unique and unclonable. [35]–[38].

A string of bits inputted to a random physical function is

called a challenge word, and the output is called a response

word. Utilizing PUFs for authentication purposes does not

require a unique challenge word but a unique response word FIGURE 2. Similar PUFs generate different responses.

against each challenge word, i.e., the uniqueness of an

concentrations [42]. These random fabrication variations

individual PUF instance is attributed to its challenge-

unintentionally form unique properties for each chip entity,

response pair (CRP) uniqueness.

which makes it possible to authenticate each chip. It is

There have been several attempts to authenticate physical

common to consider security systems equipped with PUFs

objects; however, most researchers consider the dawn of

as physical disorder security-based systems [43].

PUFs was when Ravikanth introduced the concept of a one-

way physical function [37], [38], which was initially

B. PUF Properties

proposed for low-cost physical tokens.

There are several basic properties required for identification

Variations throughout a manufacturing process create

and authentication, and some additional properties are

distinct properties for the manufactured object, and since

specifically required for authentication applications [44].

those variations happened out of control, replicating them is

not possible, which makes such an object physically • Defining Properties for PUFs

unclonable. An object with distinct properties, if cha llenged, The following points highlight the most fundamental

would generate a response that forms a unique CRP. This properties for PUFs whether it is meant for

presents an authentication method for that object, among its authentication or identification applications:

peers, as shown in Fig. 1. If a PUF device is used for - A PUF should be physically unclonable.

authentication purposes (and not as a key generator), it does

not have to generate a unique response per se, but the CRP A PUF should be identifiable among other instances. 1

should be unique compared to other PUF devices. Such a - Robustness (or reproducibility), i.e., a PUF repeatedly

physical ID is considered to be a dynamic ID. gives the same output response against the same input

Various sources of random variations usually accompany challenge.

what presumably considered as similarly manufactured PUF

- The defining properties of a PUF should be unique

devices [39]. Such PUFs form a PUF class (Pclass ) [40]. When

among other instances.2

applying an input challenge (C) to such PUFs, each PUF

would generate a distinct response (R), as shown in Fig. 2. - A response should be evaluable; otherwise, the physical

[41] system cannot be considered as a feasible PUF.

For example, similar MOSFETs among different PUF Although there is no standard evaluability measure, the

chips within a Pclass can have distinctive properties due to average time to obtain a response has been considered

fabrication variations in: 1) size, due to etching and coating as a metric in many research articles.

processes; 2) gate insulator thickness (t ox ); and 3) doping - A PUF should be feasible to construct.

VOLUME XX, 2017

[96]–[105], coating PUF [106], connect PUF [107], [108],

• Other Properties

and printed differential circuit (DiffC) PUF [109]. An

There are other extra qualities which a PUF should

extreme case of a weak PUF is a construction that only has a

have to be secure for authentication purposes:

single challenge word. Such a construction is called

- Truly Unclonable: A secure PUF system would better physically obfuscated key (POK) [44], [31], [110].

have mathematical unclonability, i.e., a secure PUF Chen et al. [111] considered that a strong PUF can serve

system would not be modellable. True unclonability of in challenge-response authentications, whereas a weak PUF

a PUF implies both physical unclonability and generates a physically obfuscated key that can be used for

mathematical unclonability. encryption. If the verifier side can decrypt the message with

- One-way Function: A PUF is considered as a one-way the archived key (public or private), then the PUF is

function if observing its response does not help to authenticated. In general, it is not safe to send a response

discern the input challenge; otherwise, the PUF is then from a weak PUF device unless it is encrypted or hashed;

mathematically modelable and thereby insecure. therefore, communications are usually done through an

algorithm that is physically linked to the PUF, like an

- Temper Evident: A PUF has such a quality if its application program interface (API). Such PUFs are known

response changes after an invasive attack. This is an as controlled PUFs (CPUFs) [35], [112], [113].

essential property for physically securing the PUF and

accrediting remote authentication. 2) STRONG PUF:

A strong PUF is an ideal concept, and yet no known PUF

It is important to note: has been considered as one. All the proposed PUFs are just

1) As marked by 1 and 2 , many researchers try to make PUFs candidates. The distinction between a strong and weak PUF

do both identification and authentication tasks, using a was first introduced by Guajardo et al. [65] and discussed

further by Rührmair et al. [114], then by Konigsmark et al.

PUF’s response as an ID [45], [44], and some systems

[115]. Strong PUFs are sometimes called physical random

utilize the response as an encryption key [46].

functions [116], [45] or physical one-way functions [37],

2) Mathematical unclonability and the one-wayness are both [38]. A PUF is considered strong if even when tested by an

be elements of the unpredictability. attacker for a long time, it sustains its unpredictability for the

non-observed CRP sets [43], [44]. From easier to harder,

3) A PUF’s properties and formulations can take various

Rührmair et al. [54] attacked arbiter PUF [116], XOR arbiter

forms [47]–[50], [31]. Using PUFs for identification PUF [117], feed-forward arbiter PUF [118], and lightweight ,

and/or key generation eliminates the tolerance for errors. secure PUF [119]. Rührmair et al. considered that a PUF’s

strength depends on number of the CRPs, which implies the

A PUF is considered weak or strong, based on its security numbers of the challenge and response bits. However, this

level, as follows: was not enough to prevent modeling attacks by machine

learning (ML) methods, such as support vector machines or

1) WEAK PUF:

perceptrons.[54], [120]. Rührmair et al. [114] concluded that

A weak PUF may have no or a few input challenges and

the more analog components within an electronic PUF

usually used to generate an ID. In such PUFs, the number of

system, the more resilient it would be to ML attacks; thus the

CRPs is mostly linearly related to the logical units of the

authors nominated PUF power grid. power grid PUF [121],

PUF, such as the PUF ring oscillator. Weak PUFs are

cellular nonlinear networks (CNN) PUF [122], [123],

vulnerable to modeling attacks, whether they have a small crossbar PUF [124]–[126] as possible candidates for the

number of CRPs [51] or a large number of CRPs [52]. Beside strong PUF title.

extending the number of CRP words, longer challenge words This article adopts strict conditions for a strong PUF, as it

also can slow but cannot stop modeling attacks [53]. It is should meets all the following security aspects:

clear that digital-based PUFs, whether delay-based or

memory-based, are vulnerable to modeling attacks [51]– • Physical Unclonability

[59]. Statistical and random disorders of manufacturing make

Examples of weak PUFs: power-up flip-flop PUF [60], it infeasible to produce identical PUFs even by the same

[61], shift register delay PUF [62], buskeeper PUF [63], manufacturing process. That is why such physical entities

power-up static random-access memory (SRAM) PUF [64]– are considered physically unclonable.

[79], data retention voltage (DRV) SRAM PUF [80], • Mathematical Unclonability (Unpredictability)

destabilized SRAM PUF [81]–[83], SRAM failure PUF [84], A strong PUF concept implies high unpredictability, i.e.,

SRAM transformed PUF [85], [86], and memory cell-based mathematical modeling is difficult. A mathematical

chip authentication (MECCA) PUF [87], latch PUF [88]– unclonability of a PUF depends on:

[93], artificial fingerprint device (AFD) PUF [94], [95],

- Anti-Modeling Complexity: The interactions of

dynamic random-access memory (DRAM) latency PUF

challenge bits within a strong PUF should be

VOLUME XX, 2017

complicated enough to make it infeasible for a computer et al. [140] considered that the basic PUF metrics are

program to predict the response with high probability randomness, uniqueness.

(Pr), and with a reasonable time, even if many previous

• Randomness

CRPs were observed [127]. The term high probability

The randomness of a response bit means that there is no

refers here to (1− negligible). Many modeling attacks bias toward a logic ‘1’ or ‘0’, and the ideal case is when

have succeeded in modeling various digital-based PUFs;

the probability to obtain each value is 50%.

both memory and delay-based PUFs [51]–[59], [128],

[129], while that is not the case for mixed-signal PUFs. • Uniqueness

This can be attributed to the difficulty of modeling The uniqueness of a Pclass represents the average

mixed-signal PUFs. distinctness of a PUF instance among others; it is usually

measured by the average of the inter-Hamming distance

- Number of CRPs: A strong PUF should have many

(inter-HD) among response words of the tested PUF

CRPs, so the verifier may not have to reuse the same

instances aginst a challenge word. The ideal average inter-

challenge twice. Although, that did not help protect the

HD is 50%, which simply means when a challenge is

arbiter PUF [116], XOR arbiter PUF [117], feed-

applied to two different PUF instances, half of the

forward arbiter PUF [118], and lightweight, secure PUF

response word bits will be different.

[119] from modeling attacks [52], but it can make such

attacks less feasible within a reasonable time frame • Reliability

[130], [131]. Some research papers suggested 30-bit The reliability represents the ability to reproduce the

CRP sets (one billion CRPs) or higher immunize a same response against a challenge. Some researchers

strong PUF for modeling attacks [132], [133]. Others measure a PUF reliability by bit error rate (BER), while

have recommended at least 64-bit CRPs [134]. others measure it by intra -Hamming distance (intra -HD).

Intra-HD is the number of the flipped response bits when

• Accessibility

re-applying the same challenge to the same PUF instance.

Another condition which a strong PUF must fulfill is

The intra -HD is sometimes measured under similar or

that even when an attacker can observe the input

different ambient environments, such as temperature and

challenges and read out their corresponding response

power supply conditions [140]. More intra -HD details are

without restriction, it remains immune to modeling attacks

in Section B.

(to predict the unobserved responses). In other words, a

strong PUF does not need to restrict the access to its input

This article tends to more detailed evaluation metrics that

nor its output with a secure communication protocol. The

are close to those of Maes [141], [142], based on inter-HD

non-restricted accessibility can enable an attacker to test

and intra -HD.

several CRPs; however, having so many probable CRP

sets makes it infeasible for an attacker to test them all with

A.Inter-Hamming Distance

a reasonable time. Encrypting or hashing the responses is

Hamming distance between two responses (Y1,i,α , and Y2,i,α )

usually done on-chip before sending it to the verifier side;

of two individual instances of a PUF construction against a

however, for strong PUFs, encrypting and/or hashing is

challenge Xi under the same environmental conditions (α) is

just recommended rather than essential [135].

called the inter-distance between the two PUF individuals

• Anti-Tamper Sensitivity (Dinter (X i )), or (Dinter ), for short, and at standard

1-2, α 1-2,i, α

A strong PUF should have a self-distracting quality

when an invasive attack is applied to its physical conditions, it can be denoted as (Dinter

1-2, i

) or (Dinter

1-2

).

components, in other words, the PUF responses after an Noting that whenever the inter-distance is discussed, α

invasive attack should not be the same as before the attack. should be identical for both of the compared PUF instances;

therefore, the notation α although it usually appears within

III. EVALUATION METRICS OF PUFs the measured response as Y1,i,α , but it does not usually appear

There are many metrics to evaluate PUFs in terms of within the inter-distance notation as (Dinter 1-2 ), as both Y1 and

identifiability, reliability, and security [136], [137], [32]. Y2 are supposed to be performed at the two PUF chips under

Maiti grouped the parameters into three dimensions: device, the same environmental conditions α.

space, and time [138]. The device dimension includes It is common to evaluate the inter-distance among several

uniqueness, bit-aliasing, and probability of misidentification; non-repeated pairs (Npair) of PUF individuals within the same

the space dimension includes uniformity and diffuseness (or Pclass . The inter-distance parameter characterizes the

randomness); and the time dimension includes relia bility, uniqueness of a PUF instance among the other tested PUFs

correctness, and steadiness. However, some metrics have within a Pclass .The average inter-distance (Dinter ave,i ) is based on

similar mathematical representations, like the uniformity comparing the differences among responses of all tested PUF

with randomness, and reliability with correctness [139]. Gao pairing combinations within a Pclass . Thereby, Dinter ave,i

VOLUME XX, 2017

indicates the average uniqueness of the Pclass , which refers to a degree of tolerance, or an ECC unit is to be used to correct

the relative uniqueness of any PUF individual among the such bits. In general, regardless of the differences in the

other individuals within that class. The sources of uniqueness environmental conditions, the rate of the correct bits to the

are not attributed to the uniqueness of the response, as the total response bits is referred to as

response by itself is not necessarily unique. Still, the CRP is reproducibility/steadiness/stability/ or robustness of the

supposed to be unique within the tested Pclass [49]. It is Pclass . The average intra -distance distribution ( μintra ) is

important to emphasize that whenever determining the determined by re-challenging the same PUF individual many

average uniqueness of a Pclass , it is simpler to assume that any times to measure multiple D values at various environmental

change in α would affect all the PUF individuals equally, conditions regarding Y1,α1 , which is measured at standard

thereby (Dinter

ave,i ) remains the same; however, this assumption conditions. The ideal value of D is zero, so as for its average

might not be precise and implies a margin of tolerance. The distribution, μintra .

average inter-distance (Dinter

ave,i

). The formulation is detailed in

Appendix A. C. Identifiability

Identifying a PUF chip instance among its siblings is

Definition 3: An evaluable (Pclass ) shows a high attributed to a CRP combination uniqueness. Neither the

probability of uniqueness if Dinter

ave,i is high, i.e., applied challenge sets nor the generated response sets are

Pr( large Dinter

ave,i

) is high. required to be unique.

Noting that the qualifiers ‘large’ and ‘high’ are context- Definition 4: An evaluable Pclass shows identifiability if a

specific [44], [49]. In general, a high probability refers to (1− response of a PUF of each tested instance is reproducible,

negligible). Such uniqueness is usually tested at normal unique, and Pr (D intra

i

< Dinter

ave,i ) is high.

working conditions α. Based on Dinter ave,i , it is also common to In other words, when applying the same challenge X i ,

determine the average inter-distance distribution (μinter ) of a under the same environmental conditions α to various PUF

Pclass , as detailed in Appendix B. individuals within a Pclass , and the measured noisy response

Alternatively, through simulation, it is also possible to Yi,α of that PUF individual (for example, PUF 1 ) is distinct

determine μinter by using only one PUF chip by randomly among the responses of other PUF individuals within that

varying some properties of its physical components. This is Pclass , then that PUF1 is considered identifiable among its

commonly applied through Monte-Carlo randomness peers [44], [49]. Such a response can be an identity and

simulation. The optimum value for μinter to achieve the most would usually have a CRP would have a high probability of

randomness of the responses within a Pclass is 50%. This being unique within that Pclass . Noting that the identifiability

means: of a Pclass is usually tested at normal working conditions, then

α here refers to normal working conditions (voltage,

1) Among the tested PUF individuals within a Pclass against

temperature, etc.). The term ‘normal’ working conditions

a challenge, on average, half of the responses’ bits are

here may carry different indications depending on the PUF

not correlated.

targeted application and the used technology to construct the

2) The (μinter = 50%) represents an unbiased uniqueness PUF. For MOSFET-based PUFs, it may refer to a supply

and identifiability of the PUF individuals within the Pclass voltage of 1 V, for example, and a temperature of 25 o C to

[143]–[145]. 27 o C.

3) For a single individual instance of a PUF construction, The assumption here is that the environmental effects on a

the distance between two separately measured responses PUF unit when it generates its response against a randomly

against the same challenge is zero. A PUF designer chosen challenge Xi is the same against any other challenge,

usually aims to attain such an optimal value as an then Dintraave,i,α remains the same for any Xi . The other

indication of reliability. assumption is considering any change in α would equally

affect all the individuals within a Pclass , and therefore Dinter

ave,i

B. Intra-Hamming Distance remains the same.

For an individual PUF chip, the reproducibility of a

response against a challenge can be measured by re-applying D Reproducibility and Authentication Tolerance

the same challenge, under the same environmental For a single PUF construction such as a PUF chip, the

conditions (α) . Hamming distance D (Y1 ; Y2 ), in this case, uncertainty about the expected response to a challenge

it represents the intra-distance. The distance notation should be significant when an attacker does not have access

between the two noisy responses may refer to ironmental to that PUF instance. For a single individual PUF instance,

conditions (α1 ) and (α2 ), then the distance notation the distance between two separately measured responses

becomes D (Y1,α1 ; Y2, α2 ). Some of the faulty bits can be (repeatedly) against the same Xi , under the same α, should

ignored if the authentication is designed in a way that permits ideally be zero or should be small. This can be denoted as:

VOLUME XX, 2017

Dintra

i = D (Y1,α1 ; Y'1,α1 ). unclonability are in Appendix C.

Definition 5: An evaluable Pclass shows reproducibility if: F. PUF Anti-Tamper Sensitivity (Tamper Evidence)

Pr ( small Dintra

i

) is high One of the approaches to the study a PUF chip is by

Amid added noise and random errors, a PUF usage relies on accessing the internal structure of the chip. If the responses

measuring the response, which implies a degree of error are no longer the same, then the chip has the advantage of

tolerance [49], [44]. In some cases, an error-correcting code being anti-tamper sensitive. The tampred chip is considred

can be omitted. In such a case, only a predefined number of as another chip that is clone to the original chip. In other

bit errors is accepted; i.e., if the allowable Hamming distance words, if the genuine PUF (before the physical invasion), is

as a predetermined error threshold (∆) is not exceeded, then denoted as PUF1 , and its noisy response against a challenge

the PUF authentication is declared as ‘pass’. If ||Yi −Ri || ≤ ∆, word Xi was Y1, i , after the invasion, its would produce a

then the authentication is considered successful. This implies different output response Y2 , and the chip can be regarded as

ignoring the errors if their value is less than the

another one, that can be denoted as PUF2 or PUFclone .

predetermined threshold (∆), without needing to use any

A convenient approach to study the tamper effect on a PUF

helping data (Wi ) to correct those errors; where (i) is the CRP

is usually made by comparing the output response before and

index.

after the tamper. That is usually done by determining

The permitted tolerance threshold (∆) is related to the

following four parameters [50], [146], [147]: Dintra

1-2,i,α between the noisy response (Y1,i,α ) of the untampered

(PUF1 ), the response after tampering (Y2,i,α). The reason

1) BIT REJECTION RATE (BRR)

behind applying the intra -distance checkup rather than the

The ratio of the non-reliable bits to the total number of

inter-distance one is because it is assumed that the verifier

response bits. Such non-reliable bits are usually ignored.

side does not know about the tamper attempt and would still

2) BIT ERROR RATE (BER) consider the PUF as if it the sam e one. By extending the

The ratio of the fa ulty bits to the total number of response tamper concept discussed in [49], then it is possible to test

bits. the anti-tamper sensitivity, as: Dintra

1-2,i,α =||Y1,i,α − Y2,i,α ||. At

3) FALSE ACCEPTANCE RATE (FAR): standard conditions (α), the equation can be written as

The probability for a biometric security system to incorrectly Dintra

1-2 =|| Y1 − Y2 ||, for short.

accept an access attempt by an unauthorized user. There are three possibilities for a tamper sensitivity of a

4) FALSE RECOGNITION RATE (FRR) Pclass :

The probability that a biometric security system will 1) A very good tamper evidence indication is when (Y 2 ) is

incorrectly reject an access attempt by an authorized user. It very much different from (Y1 ), in other words, both are

is determined by dividing the number of false acceptances by less correlated to each other, which leads to a very high

the number of authentication attempts.

intra-distance (Dintra

1-2 ) among their responses. In other

words, if: Dinter intra

a ve < D1-2 . That means (PUF2 ) is distinct, not

E. PUF Physical Unclonability

only from (PUF1) but also from the entire (P class ). The

The physical unclonability of a PUF system within its class

can be defined as: larger the Dintra

1-2 is, the more anti-tamper the Pclass would be.

Definition 6: An evaluable Pclass shows physical 2) A good tamper-wise security indication is when (Y2 )

unclonability if it is hard to control its physical creation differs from (Y1 ), but not much. In other words, there is

procedure. still some correlation between (Y2 ) and (Y1 ); which leads

This definition is also applicable to the to a medium (Dintra 1-2 ), in other words;

mathematical/logical unclonability if it is hard to find a If: Dinter

ave ≤ D intra

1-2 ≤ Dinter , ∃1 ≤ i ≤ Nchallenge

precise mathematical model that can emulate the physical , then: PUF2 ≠ PUF1; however, still PUF2 ∈ Pclass

functionality of a PUF structure. or Pr (Dintra

1-2

) = 0 for at least one challenge (Xi ) is high.

Hypothetically, if the fabrication process first created the

(original) individual (PUF1 ) and attempted to create the 3) A bad tamper-wise security indication is when the

forged individual (PUFclone), then the clone can be checked response (Y2 ) is very nearly similar to (Y1 ) in term of intra -

by an inter-distance rule. The physical clonability can be distance (Dintra

1-2

) such that;

tested in the form of inter-Hamming distance Dinter 1-clone,i, α If: Dintra

1-2, i = 0 , ∀1 ≤ i ≤ Ncha , then PUF2 (Xi ) ≡PUF1 (Xi ).

between the responses of the Y1,i,α , Yclone,i,α of both the Alternatively, in less restricted mode:

original and the cloned PUFs. In this test, responses are If: Dintra

1-2, i = 0 , ∃1≤ i ≤ Nchallenge , then: (PUF2

measured against the same challenge (X) indexed by (i), (Xi ))≅(PUF1 (Xi )), where (N challenge ) represents the number

under the same environmental conditions α. Detailed of the tested challenges. In both last cases (2 and 3), it is

formulations of the inter-distance approach to check concluded that the tested PUF design (the entire Pclass ) is not

VOLUME XX, 2017

sensitive enough against tampering, in other words, it does statistical test suit (Diehard) in 1995 [149], the national

not have a tamper evidence quality [44]. institute of standards and technology presented its statistical

test suit (NIST STS) in 2001 [150], L’Ecuyer and Simard

Detecting the cloned PUF depends on the precision of the presented their (TestU01) in 2007 [151].

response measuring and the permissible tolerance range (∆), In general, the NIST STS kit is currently the most standard

which is based on the chosen values of the FAR and the FRR randomness test battery, and it showed that the responses of

of the authentication process. Using a less tamper sensitive some PUFs are sufficiently random [152]–[154]. However,

PUF system or adopting a high FAR by the verifier means the relevancies of some tests are debatable [155], [156], and

allowing more tolerance. Some systems might generate Y2,i the kit was updated in 2008 [157], 2010 [158], and is still

that is still similar to Y1,i , then with the help of W1,i , the under revision, development, and optimization [159], [160],

authentication would be still possible, and the verifier can be [155].

deceived. It is safer for a PUF to include a tamper-evidence It is worth remarking that, if the PUF response is intended

feature, which is considered a self-destructive ability, and for cryptographic applications, more tests are to be carried

such a PUF is also called fragile PUF [148]. out on the entire cryptographic module in order to improve

its protection across four levels, according to ISO/IEC 19790

G. PUF Unpredictability (Mathematical Unclonability) [161]. Furthermore, the module is to be accredited according

Beside physical unclonability, a secure PUF must have an to the federal information processing standards (FIPS) 140

unpredictability quality, i.e., the unobserved responses are [162], [163].

supposed to be sufficiently random [49]. Mathematical

cloning tends to be an easier approach of PUF cloning, where 3) LARGE NUMBER OF UNIQUE CRPS:

an attacker does not create a physical clone of the PUF, but The PUF is supposed to have very large CRP sets. Otherwise,

an algorithmic (or behavioral) clone model. An attacker can the attacker can try all possible challenges, then records their

apply black box testing approaches to design such a responses, then no secret response key is left undisclosed.

mathematical model, usually through applying ML The number of CRPs is usually, but not always, exponential

algorithms on a CRPs training set. Obviously, the larger the to the of the components used to build a PUF [43].

training set, the more likely the ML is to succeed in modeling Data randomness is usually assessed according to the

the PUF. entropy concept. Entropy is a measure of the uncertainty one

At the testing phase, when the mathematical clone model has about the outcome of a random variable distributed

is tested against a new challenge among the CRPs testing set, according to a given distribution; it also represents the

it is common to calculate Hamming inter-distance between unpredictability of a secret random variable [44]. There is

the generated response string of bits and the original Shannon’s entropy [164], which was formulated further by

response string from the testing set, as in Appendix C. Cover et al. [165], and a less minimum entropy margin

proposed by Rényi [166], which Dois discussed further

H. Randomness (Entropy) Tests and Accreditations [167], [168].

A single number by itself cannot be described as random, but

a series of numbers can show randomness; thereby, to I. Correlation Among Bits

maintain unpredictability, the CRP lists should fulfill the Neighboring cells must not influence each other to avoid

following conditions: security threats. Correlation between cells would reduce the

number of possible combinations and thus would increase

1) CHALLENGE LIST RANDOMNESS the risk of successful brute-force attacks. To check whether

The verifier is supposed to adopt an adaptive random a correlation exists between neighboring response bits

challenge selection approach to achieve unpredictability of (Rn , Rn-j ), with a la g of (j), and an autocorrelation function

the next challenge. (AC ), then: ACXX (j)= ∑n=N

XX n=1 R n R , where (N) is the total

n-j

2) RESPONSES LIST RANDOMNESS number of response bits.

Responses to different challenges must be independent. If ACXX (j)=1, or (−1), then the data at lag (j) are

That does not only imply the random correlation between completely correlated; while, if ACxx (j)=0, then the data are

independent responses, but it also implies there is no completely uncorrelated [50].

historicity in the PUF, i.e., no previous challenge or response

can affect the next response. Response bits should have a J. Correlation Among Chips

degree of randomness to protect the PUF against modeling If the layout of an electronic chip is not done carefully, the

attacks; thus, responses of many PUFs were tested using output responses of some cells within a PUF system may

statistical test suites for random a nd pseudorandom number depend on the positions of these cells. In such a case, the cells

generators. tend to generate some specific response values, which leads

There are various well-known randomness testing software to a security threat, since knowing the output of one chip

suits, also called test batteries. Marsaglia presented his

VOLUME XX, 2017

makes it easier to guess the response of other chips within The enrollment phase, also known as learning or training

the Pclass . PUFs usually generate each of their response bits phase, should be performed before releasing the PUF to the

individually, the correlation among chips in the form of inter- end-user, and it can be briefed as:

Hamming Distance (Dinter i ) can be determined similarly. If a 1) Assigning an ID to identify each tag/smart card chip,

response string of bits of a PUF chip is considered as a

then archive it within a database on a trusted server.

reference, then the mean value of all Hamming distances to

the responses of the other tested chips against the same 2) The PUF entity is challenged with a challenge word

challenge (Xi ), and under the same environmental conditions indexed by (i) as Xi , to generate output response data

(α), can be represented as (Dinter ave,i ). The optimum target of

(Ri ), and an error-correcting or helping data (Wi ). In

(Dinter

a ve,i ) is 50%, which means there is no correlation among most PUFs, Wi is stored on-chip in an NVM, to be used

the tested PUF chips within that class [50]. However, some later during the authentication phase to correct the noisy

tolerance is usually accepted, especially when a PUF response Yi and generate a corrected response (Si ).

generates a large number of response bits, such as 64 or 128, Storing Wi on-chip poses a security threat. A safer

then having (Dinterave,i ) of (50 ± 2)%, for example, would not

approach is to store Wi on a secure server, either of the

help an attacker to model the PUF. After all, the adoption of verifier’s side or as an independent third party,

a specified tolerance rate depends on the nature of the especially in the case of an untrusted verifier [50]. The

application. verifier can correct the received noisy response Yi using

Wi to determine the related corrected response (S i ). The

K. One-Wayness archived number of CRPs would depend on the

In computer science, a one-way function is defined as a application. For example, for a PUF that is embedded

function that is easy to compute on every input, but hard to into a credit/debit card, the verifier should test and save

invert to determine each input [37], [38], [49]. The terms many CRPs. Otherwise, if that PUF is embedded in an

‘easy’ and ‘hard’ here are in the sense of computational RFID tag within an on-shelf item in a supermarket, then

complexity, especially as polynomial-time problems. A such a verifier’s database would only need to include

function is usually considered a one-way function if for a one or a few CRPs if considering the possibility of

given input challenge (X1,i,α ), indexed by (i), under returning the purchased item, then resell it for multiple

environmental conditions (α), it is easy to measure the noisy times.

output response (Y1,1,α ), but for a given response (Y1,2,α ), it

Due to noise during the enrolment phase, the reference

is hard to predict the input challenge (Xpredict,2,α, ) as an

response (R i ) is measured against a challenge (Xi ) for several

inversion of the response: times. Later, those independent challenges (X1 ,…, X ),

Xpredict,2,α = inv (Y1,2,α ) Ncha

In other words, the inversion has a negligible probability and their corresponding reference responses (R1 ,…, R )

Ncha

if: are saved in the verifier database, where (Ncha ) is the

Pr( || X1,2,α -Xpredict,2,α || = 0 ), for more than one (i)) is low, maximum number of possible CRP sets. For example, if the

then the PUF function can be considered as a one-way number of the challenge bits (n = 64), then the number of

function until proving the opposite by figuring out an possible CRP sets is: Ncha = 2 n = 2 64 .

inversion model. For each Xi , it is expected that the measured response Yi

during the verification phase would be slightly different from

IV. PUF USAGE PHASES AND COMMUNICATIONS Ri , which was measured during the enrolment phase. That

In order to understand the PUF usage phases, first it is

relation can be represented as: Y=R+E, where (E) represents

necessary to distinguish authentication (or verification) from the error, and it is assumed to be zero during the enrolment

identification of an object. In case of identification, the phase. In this article, X, R, Y, and E are digital numbers of n

system recognizes an object, such as a smart card, by reading bits.

a serial number stored on a non-volatile memory (NVM), the During the verification phase, to improve the reliability of

system then matches that ID against any archived ID code. the response detection, the device manages the difference

Whereas an authentication process is based on a comparison between Y and R via a signal processing function (G):

of a received biometric pattern with a pattern archived since Si =G(Wi , Yi ), where (Wi ) is any form of helping data, which

the training (or enrolment) phase. For each of the assists error-correction. When: Si =Ri , then the authentication

identification and authentication cases, the system usually is successful.

adopts some FAR and FRR to decide whether the similarity To sum up, the verifier’s database must archive the PUF chip

is sufficient or not. The usage of a PUF consists of two ID (i.e., serial number) linked to the following data lists:

phases, enrollment phase and authentication phase [169]. - Challenge X: X1 ,…, X N

cha

A. Enrollment Phase

VOLUME XX, 2017

Next, the card-reader uses a public or symmetric key, which

- Response R: R1 ,…, R N

cha is read from the NVM, to encrypt/decrypt the

- Helper data W: W1 ,…, W N communications with the verifier side.

cha

For a PUF-based contact/contactless smart card/RFID tag,

the underlying authentication protocol between the user and

B. Authentication Phase

the verifier sides illustrated in Fig.4 can be briefed as

During the authentication phase, Si is compared to R i , or if

follows:

no helper data are used, then Yi can be compared to R i

instead. The helper data can either be stored on NVM at the User: The authentication phase starts when a package that

PUF side [170] to help the ECC to correct Yi to R i , or contains a PUF device is scanned by an RFID scanner at a

externally on the server [171], where Yi is point of sale, for example. Similarly, for financial cards, the

corrected/compared with R i . The latter scenario allows Yi to reader can be an RFID scanner or a card-reader. The ID is

serve authentication purposes only, unlike the first approach, usually embedded within an RFID tag/smart card in various

where R i for authentication and as a cryptographic key. It is forms [50]:

also possible that the server sends the archived helper data to - If the ID is stored outside the chip, then it is to be read

the ECC on the PUF chip, to generate Ri for from a magnetic strip or barcode.

authentication/cryptographic key purposes [171]. In either

- The ID is stored on-chip in an NVM, which is the case

way, if the correction is done at the PUF side, it is also

of most RFID tags and smart card chips. The ID can be

possible to attain integrity by hashing R i and send it to the

generated using another on-chip PUF. The claimed ID is

server, which has also archived the hashed R i since the

sent to the verifier side; it would mostly be encrypted.

enrollment phase, to compare with. There are several

authentication protocols for strong PUFs [172] and weak Verifier: The received ID leads the VS to access the

PUFs [173]–[176]; however, the authentication protocols are related CRP list, which was stored previously (during the

out of the scope of this article. Here we mention a basic enrollment phase) on the secure server. The VS can then

authentication protocol, considering that the verifier side is randomly choose an index (i) then send the indexed

trustworthy and immune from external and internal attacks. challenge (Xi ) to the PUF, where the archived CRP list

However, the communications between the PUF at a client- indexes each CRP and its helper data as (Xi , Ri , Wi ).

side and a bank, for example, as a verifier-side, are still to be Key-generating PUFs usually have their helper data stored

encrypted [177]. The serial number of card/tag is usually on-chip, such as an ECC. Alternatively, a PUF can have its

stored on magnetic strip/NVM. It is equivalent to the helper data (Wi ) received along with the challenge from the

ID/username in internet terminologies, while the PIN code verifier side. Authentication-only PUFs can store their helper

represents the password. data on the verifier’s side, which processes the response.

If a smart card is not tapped on the card-reader machine, it This latter approach is safer and reduces the cost of the chip

does not utilize the embedded RFID feature; instead, the in terms of area, power and complexity.

client inserts the chip contacts into a card-reader and enters

User: The user reader challenges the PUF embedded

a PIN code, which adds more security, as it proves that the

client knows the secret PIN stored on the NVM. The card- within the submitted smart card or the RFID tag, with

reader sets local secure communications with the smart card. challenges Xi , measures (possibly noisy) response Yi , then

sends it to the verifier.

FIGURE 4. PUF authentication phase of an object with a trusted verifier.

VOLUME XX, 2017

Verifier: Due to the environmental driven errors during Besides, there is less protection for the user-side (i.e., the

the verification phase, the noisy measured response Y i client) against insider frauds within the bank. To solve that,

usually differs from the referenced response R i which has a bank might not have all the database lists; instead, some are

been measured during the enrolment phase. Therefore, even kept at another independent 3 rd party server. For example, the

the simplest authentication protocol needs to include the 3 rd party server can have (ID, i, Wi , Ri ) lists, while the verifier

following basic steps: server would only ha ve (ID, i, Xi ) lists. When the verifier

receives a claimed ID from the user-side, it arbitrarily

• To eliminate the computational time of non-correctable

chooses a one-time verification index (i), then sends the

responses, the verifier may first determine whether

related challenge word (Xi ) to the user-side. At the same

||Yi −Ri || ≤ ∆, where (∆) is the predetermined error

time, it sends the user ID and the chosen (i) to the 3 rd party

threshold, upon which the VS sets the FAR and FRR

server, asking for the related helper data Wi . When the

limits, and ||Yi −Ri || is the difference among bits of the verifier gets back the non-corrected noisy response Yi from

response during verification (i.e., authentication) phase Yi

the user-side, it can correct it, then sends it to the 3 rd party

to the response measured during enrolment phase R i . This

server, which compares it to Ri and approves the

difference is called Hamming distance (HD, or D for authentications. In this case, both the user and the verifier are

short), and since the test in the above case involves all protected and responsible at the same time. Exactly as having

response bits of both phases, so it is just like comparing a safe banking box, which cannot be accessed without

the entire response of two different PUF instances, then inserting both the client’s and the bank’s keys, so any party

such a distance is considered as inter-Hamming Distance cannot disclaim the process. However, discussing various

(Dinter

i,α ) [50]. authentication protocols is out of the scope of this article.

• When the difference ||Yi −Ri || exceeds (∆), then Yi is far

V. SOURCES OF VARIATIONS

from being correlated with R i . If this difference (or the

All known electronic PUFs are based on the unintentional

error) is uncorrectable nor ignorable, then the verifier

(usually software) denies the authentication. While, if the variations during a fabrication process. The terms

difference is less than (∆), then the verifier approves the ‘mismatch’ and ‘variation’ are interchangeable throughout

authentication claim. this article. Fabrication variations can lead to distinct

responses among multiple PUF individuals within a Pclass.

When ||Yi −Ri ||≤ ∆, the verifier calculates the corrected This is an essential quality for identification purposes, and

response Si using the helper data Wi of the measured Yi, as such variations are permanent. On the other hand, variations

Si =G(Wi ,Yi ), then the verifier checks whether ||Si −Ri ||=0; in the working environment, such as voltage and

i.e. (Si =Ri ); if not, then the authentication is denied, else it temperature, are temporary sources of response variations.

is successful.

To maintain a high-security level, the used (Xi , Ri , Wi ) A. Sources of Permanent Variations

templet can be deleted from the database, so it may not be Unintentional variation in MOSFET properties wafer-to-

used again. After a successful authentication phase, an wafer and across the wafer (die-to-die) influence

connections, such as the variations in metal thickness due to

encrypted access approval code number is sent to the user,

damascene process (e.g., copper polishing), is around (10-

sometimes by using Yi as a session encryption key. On the

20)% and the variation in the threshold volta ge (VT ) is

user side, the smart card, for example, uses its PUF session

around 10% [180], while the variation in dielectric thickness

response Yi to decrypt that permission code. The PUF design

at wafer level is around 5% [180], [181]. There is a lso an

should make sure that the generated response Yi , which is example of an arbiter PUF which is based on the variations

sent to the verifier side, is stable during the authentication in propagation delay. It has reported an inter-chip (die-to-

phase. If the transaction requires exchanging secret messages die) response variation of (17-23)% for the regular arbiter,

between the smart card and the verifier (e.g., for a financial and (28-38)% for the feed-forward arbiter PUF [116], such

transaction), a secure authenticated channel can be set variation depends on the die and the wafer locations.

between the verifier and the card using the response Yi as an Operating a MOSFET-based PUF circuit at the sub-threshold

encryption key for the transaction session. voltage level allows the distinct properties of the circuits to

play a bigger role so that a PUF circuit would generate a

C. Untrusted Verifier more distinctive response [182].

There are usually two sides of the transaction: 1) an end-user, In CMOS-based PUFs, there are two main sources of

which is to be verified, and 2) a verifier side, a bank, for mismatches; permanent and temporary [183], [184], [50].

example. There are various verification protocols to protect The permanent mismatches are attributed to variations

the verifier side from outsiders’ frauds and MIT attacks during fabrication. From the fabrication view side, there are

[178]. On the other hand, the user side is only protected by two main types of variations: global/systematic variation

chip-and-PIN, which was proven to be breakable [179]. sources and local/stochastic variation sources.

VOLUME XX, 2017

A.1. Global Mismatch Sources The introduction of strain silicon to move silicon atoms

These variations are attributed to inaccuracies in the farther apart reduces the atomic forces that interfere with the

production process. They can be chip-to-chip, wafer-to- movement of electrons through the transistors and thus

wafer, and lot-to-lot variations. Approximately, 20% of the improving the mobility, which enhances the chip

variability is attributed to production inaccuracy [39], [50]. performance and lowers the power consumption. Therefore,

Global/ extrinsic process variations are caused, for example, electrons can move faster, allowing strained silicon

by temperature gradients across the wafer during annealing, transistors to switch faster [192]. Silicon straining

or process variations during photoresisting development, technology has begun with 90 nm technology, which has led

etching, or photolithographic variations. Systematic to more variation; as in addition to lithogra phy-related

variations, light density and focus variations in the geometry variations, additional variations have been added

lithography system, refers to a systematic offset applied to a due to spacing, distances to shallow trench insulation, and

group of adjacent layout patterns. For example, over the contact positions. Using regularized design and dummy

entire wafer, threshold voltage gradients can occur and may features can significantly reduce the impact of systematic

converge toward a particular value, depending on the variabilities [183].

position/ direction of the MOSFET [50].

2) STATISTICAL LOCAL PROCESS VARIATIONS

These types of local mismatches are also known as random

A.2. Local Mismatch Sources

local process variations and usually attributed to stochastic

These variations are attributed to random (stochastic)

differences at the atomic level. Up to date, it is not possible

variations within a chip. Some variations during the

to fully control the process at the atomic level. Moreover, the

fabrication process of MOSFET devices are inevitable, such

as variations of charge, material, non-uniformity of smaller the minimal feature size, the higher the influence of

interfaces, and granularity of fabrication materials [185]. In each atom. Fluctuations in the physical thickness of a gate

general, the local mismatches are the most vital for most oxide present a significant source of local mismatch. When

a transistor is scaled-down, the thickness of the gate oxide

electronic PUFs, which depend on differences among multi-

can be only several atomic layers with a typical

paths within a chip, where bits propagate [186]. Local

semiconductor-to-insulator interface roughness of around 1–

variations of nano MOSFET processes can be classified as

2 atomic layers. The variance of such a small thickness can

systematic local process variations, and statistical local

be as high as 50%. [193]–[195]. That entails variation of

process variations [183].

carriers’ mobility, which varies the gate current. Sub-100 nm

1) SYSTEMATIC LOCAL PROCESS VARIATIONS transistors have different mismatch sources which vary with

The primary source of systematic local process variations is the type of the transistor. Some examples are:

attributed to the low resolution of the lithography process. - In polysilicon gated transistors, the mismatch is usually

The imprecision issues of lithography are decreased by caused by the variation (fluctuation) in doping

resolution enhancement techniques (RETs), such as: 1) concentration in the gate region, unlike metal gate

applying phase information to the ma sk, which is called transistors with a high-k dielectric material.

phase shift masking (PSM); 2) optimizing the light

illumination angles, which is called mask off-axis - In fully depleted silicon on isolator (SOI) transistors, the

illumination (OAI); 3) controlling the illumination's threshold voltage varies with the body thickness [196];

polarization, which is called source mask optimization therefore, when comparing with the MOSFET, a

(SMO); and 4) optimizing the mask pattern, which is known MOSFET with a metal-gate and high-k insulator would

as optical proximity correction (OPC) [187]–[191]. In order have less threshold voltage fluctuation [197].

to understand the importance of RETs, it is worth mentioning In planar bulk MOSFET, there are three major random

that immersion lithography and OPC techniques enable local mismatch sources [50]:

foundries to produce 45 nm nodes using 193 nm steppers,

1) Random discrete doping (RDD)

mainly by using directional pattern effects and mask shadow Random discrete doping (RDD) or random dopant

techniques [183]. Local systematic variances are caused by fluctuation (RDF) is originated during ion implanting and

lithography issues, such as light phase shift, layout-mediated redistributing during high annealing temperatures. RDD is

strain, and well proximity. Although new lithographic the main source of mismatch (variability), mainly at channel

developments have

region. However, the 22 nm node technology and beyond

narrowed the local systematic variances of lithography to have thinner bodies and lightly doped chann els, which

some extent, RETs still preserve their importance to reduce reduces RDD effect dramatically [198], [195].

local systematic variations. For instance, even when using

extreme ultraviolet lithography (EUL) with a laser beam 2) Line edge roughness (LER), and line width

wavelength of (13.4 nm), still OPC is needed to enhance roughness (LWR)

pattern pitch and direction.

VOLUME XX, 2017

Fluctuations of the edges across a patterned line, such as a PGG variability; but, it introduces both high-K granularity

gate, a fin, or a nanowire line, are inevitable; the LER (morphology) and work-function variations instead [207],

represents the length variation, while the LWR represents the [208].

width variation. Both LER and LWR are caused by Materials, technologies, and transistor dimensions

tolerances in materials and tools used in lithography contribute to variation; therefore, there is no absolute answer

processes, mainly through photoresist process (jaggedness, to the question. ‘which transistor type has the most statistical

striations, and rippling) and etching [196], [199], [195], local variations?

[200]. The granularity of the photoresist, with other factors, In general, to obtain a Pclass where the PUF individuals

introduces unavoidable LER in the gate [183]. have high identifiability (uniqueness), it is recommended

that the designers and the manufacturers to contradict any

3) Poly-gate granularity (PGG) variation-limiting approach. The manufacturers can apply

It refers to the effect of poly-silicon grain boundary

PUF-aware OPC to improve the uniqueness of the PUF

distribution on the threshold voltage. When a transistor has a

individuals with the Pclass [209], [210]. Scaling down the

polysilicon gate, then PGG is an important source of

transistor feature size can also contribute to the uniqueness

variation (or mismatch). This variability is attributed to the

of a PUF response. The 45 nm-based PUFs would have more

doping non-uniformity (fluctuation) when having a rapid variations and thus uniqueness than 65 nm -based PUFs, and

diffusion. The granularity becomes a significant source of the 28 nm PUFs would have more variations and uniqueness

variability when the grain size becomes comparable to the than 45 nm PUFs [211]. In general, as the MOSFET device

transistor feature size (L/W) [196], [201], [202]. In bulk scale goes down, as more the intrinsic variation of a device’

MOSFETs, the doping concentration in the polysilicon gate

parameters would be [211].

region plays an important role, where the surface Fermi-level

pinning at the poly-Si grain boundaries dominates the poly-

B. Sources of Temporary Variations

Si.; while that is not the case in a metal gate with high -k Temporary mismatches are also classified as reversible

dielectric insulation material. It is concluded that for a PUF mismatch sources and irreversible mismatch sources.

device to have a larger PGG effect as a source of variance,

using a poly gate is recommended over the metal gate. 1) REVERSIBLE MISMATCH SOURCES

Various poly-Si based transistors for PUFs were proposed to The environmental conditions of a PUF at an authentication

enhance uniqueness [203]–[205]. time would differ from those at the enrollment phase, which

would vary the generated response. Such a response

In general, for a planner transistor, RDD usually variation is usually considered an error, and the collective

dominates the mismatching behavior. However, RDD and effect of all the environmental variations on a PUF is

PGG induced competing variabilities at 35 nm and 25 nm considered a temporary source of error. These variations

channel lengths. For shorter channel lengths, if the LER happen during the authentication phase, when the

could be scaled according to the International Technology environmental conditions vary, such as of the supplied

Roadmap for Semiconductors (ITRS) as 1.2, 1, 0.75, and 0.5 voltage (VDD) and/or the ambient temperature, such

nm for the 35, 25, 18, and 13 nm channel length transistors variations may alter the response bit(s). That may have a

requirements, then RDD becomes the dominant source of significant impact on the reliability of the PUF, particularly

variability of the threshold voltage (VTH ). However, if LER since it is not possible to control the environmental factors

remains at (LER≅ 4 nm), then LER becomes the dominant on the verifier side during the authentication phase, as can be

source of induced potential variabilities, which pins the done in the laboratory during the enrollment phase [31].

channel due to the very high concentration of mobile carriers

2) IRREVERSIBLE MISMATCH SOURCES

(especially the electrons in n-MOSFETs) below the 25 nm

The properties of an electronic device vary during the device

channel length [206], [185]. Both RDD and the interface

lifetime, and such variations are usually referred to as

roughness introduces significant statistical variability in the

transient variations. Such variations are not temporary, nor

gate leakage current [183]. With the further reduction of the

exist at the manufacturing time, and are not even constant

gate oxide thickness and doping concentration at the

throughout the lifetime of the object. For example, an

interface as low as possible, the impact of the surface

electronic device ages throughout its lifetime, and the

potential pinning at the poly-Si gate grain boundaries will

properties of the device continue to change gradually.

increase. The use of poly-Si micro-grains can reduce the

Accelerated aging experiments were performed on a PUF

fluctuations, as variability will be reduced if the

ring oscillator based on a 90 nm field-programmable gate

characteristic size of the grain is much smaller than the array (FPGA), and the results showed a significant aging

device dimensions; thus, the associated potential fluctuations effect on the response, which reduces PUF reliability .

will be self-averaged in the device. However, the best However, aging did not affect the randomness, which

approach would be using amorphous poly-Si or a uniformly maintained the PUF uniqueness [212], [184]. Other

structured metal gate [206]. Using a metal gate eliminates the accelerated aging experiments were applied on various 65

VOLUME XX, 2017

nm based PUF chips to measure the change in negative bias These ra ndom variations create distinct parameters for each

temperature instability (NBTI). The results showed that MOSFET. A parametric variation is usually a source of

among the tested memory-based PUFs, SRAM and bus- disturbance for most applications, while for PUFs, it can be

keeper PUFs are less affected by aging than latch and DFF an excellent source of entropy to generate device-specific

PUFs [213]. response bits [8]. This section discusses the intrinsic

variations’ effects on the threshold voltage (VT).

C. Temperature effect on MOSFET threshold voltage The initial threshold voltage value of a MOSFET at zero-

and inversion charge bias (VT0 ) depends on the flatband voltage, the bulk

The electronic charge which occupies a MOSFET’s gate potential, the oxide electrical capacitance per unit area (C ox ),

surface can cause a shift in flat-band voltage (Vfb ) [190]. and the depletion layer charges. The variation in the initial

However, as the applied voltage is varied, the Fermi energy threshold voltage (∆VT0 ) plays a vital role in forming

at the oxide-semiconductor interface changes a lso and distinctive properties for a PUF chip. The polarities of VT

affects the occupancy of the surface states. Considering that and VT0 are positive for an n-MOSFET and negative for a

(∅st ) is the surface potential at the threshold voltage level positive- channel metal–oxide–semiconductor field-effect

(VT ), then: transistor (p-MOSFET). In both MOSFET types, there is a

roll-off voltage that contributes to │∆VT0 │, which reduces

Where (Cox ) is the oxide electric capacitance, (εs ) is the

│VT0 │. For generic (non-PUF) applications, chip designers

kT NA try to reduce the intrinsic variations by taking into

∅st = ±2 ln (1) consideration some factors, which are briefed here at

q ni

technology, layout and mask, and schematic levels. The

introduction of strained silicon since 90 nm CMOS

√2qNA εs |∅st | technology and below enabled the electrons to move faster,

VT = Vfb + ∅st ± (2)

Cox which ultimately made MOSFETs switch faster.

Straining the silicon results in better MOSFET

performance and lower energy consumption. However, it

silicon permittivity, (k) is Boltzman’s constant, (T) is the causes more deterministic, or systematic variability in a

temperature, (q) is the electron charge, (n i ) the intrinsic MOSFET’s parameters, such as C ox , MOSFET channel

carrier concentration, (N A ) is the acceptor doping width (W), and charge carrier mobility (µ); μ can be defined

concentration in p-substrate, which is replaced by (ND ) as as electron/hole mobility for the n/p channel as (μ n /μp ) [214].

donor doping concentration in case of n- substrate. For (1) Statistical variability is attributed to random variations in

and (2), the positive signs are for p-substrate and the negative parameters like VT0 , μ, Cox , L, or W. The variation of VT0 is

signs for n-substrate. For p-substrate, VT in (2) becomes the most prominent parameter and is primarily ascribed to

lower at low temperatures [190]. At the inversion region of RDF, surface roughness, oxide charge, and LER [189]. The

a MOSFET, the total capacitance (when the drain and the variation in VT0 depends mainly on RDF, as the dopant

source are shorted externally) equals the series combination concentration can vary up to ±10% [215].

of gate poly-silicon capacitance (Cpoly ), the oxide electric In this article, fabrication variations of a MOSFET are

capacitance (Cox ) and the inverted channel capacitance studied at technology, layout and masking, and schematic

(Cinv ). If the applied voltage at the gate is (VG ), and the design levels.

threshold voltage is (VT ), then: 1) VARIATIONS AT TECHNOLOGY LEVEL

The variation of t ox gained more importance as the

Qinv = Cox (VG -VT ) (3) technology shrinks down. Using high-k insulators with

larger physical t ox abates its influence on variation. Unlike

εox tox , the effect of the oxide charge on VT value does not

Qinv = (VG -VT ) (4)

tox represent a significant factor in modern fabrication

technologies, especially when a MOSFET works at strong

inversion mode [216]. Let K’=µC ox (W/L), then an RDF of

The channel charge (Qinv ) increases at low temperatures, 10% with 5% variation in t ox can lead to variation of 100 mV

and this produces a rise in the total capacitance of the series in VT0 , 15% in K’, and 5% in the source-bulk (C SB) and the

combination (Cpoly ), (Cox ), and (Cinv ) [190]. drain-bulk (C DB) junction capacitances [217]. SOI

technology mitigates RDF, but an ultra -thin body SOI

MOSFET raises more uniformity concerns. The high -k

VI. UTILIZING FABRICATION VARIATIONS FOR PUFs

This section discusses some major variations which occur insulated metal gate technology reduces RDF but creates

throughout the fabrication process of a MOSFET-based chip. metal gate granularity (MGG), which becomes among the

major sources of ∆VT0 in scaled bulk-MOSFETs [218]. In

general, a MOSFET fabrication technology tends to decrease

│∆VT0 │by: 1) strict control over doping fluctuation of the

source and the drain; 2) strict control over the critical

geometrical dimensions, such as the gate length and width of

the MOSFET; 3) scaling up the gate insulator thickness; and

4) scaling up the junction depth [219]. Choosing a MOSFET

manufacturing technology with less control of characteristics

can better serve chip authenticity applications.

2) VARIATIONS AT LAYOUT AND MASKING LEVELS

Low lithography resolution is a major source of systematic

local process variations. Such imprecision is treated with

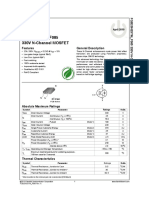

resolution enhancement techniques, such as phase shift FIGURE 5. Regions of planar n-MOSFET.

masking by adding phase information to the mask, off -axis

illumination to optimize the angles of light illuminating the Le = L − (∆LS + ∆LD ) (6)

mask, source polarization to control of the polarization of the

illumination, source mask optimization, and OPC to without applying any external voltage at the MOSFET. After

optimize the mask pattern [220], [221], [187], [190], [189], applying a voltage on the drain/source, lateral extents of the

[191]. Besides the lithography-related geometry variations, p-n depletion regions of the bulk-source and the bulk-drain

additional variations are added due to spacing, distances to are produced, they are denoted here as (∆L S) and (∆LD ),

the shallow trench isolation, and position variances of respectively. When a voltage is applied at the gate, there will

contacts. A regularized design and dummy features can be a shared gate-source/gate-drain influence on the depletion

greatly reduce the impact of systematic variability [183]. charges of the channel at the source/drain sides, respectively.

Among the basic layout approaches tha t are commonly The remaining distance between the source and drain

applied to reduce such variations are: 1) matching the depletion is considered the effective channel length (L e),

orientation of the transistors’ layouts to decrease mobility where the diffusion charges are influenced by the gate

variations, 2) laying out transistors as close as possible and voltage only [211]. Then the Le is calculated as:

using common centroid layout to minimize gradients The effective length exists only when the channel is formed

throughout the fabrication process, 3) using dummy gates at by applying external voltages at the MOSFET, while bulk -

the sides of transistor layouts, 4) not laying out contacts on source and the bulk-drain depletions exist even without

top of active gates, and 5) not laying out metal lines across applying any external voltage to any of the MOSFET’s

active gates [50]. Within an electronic PUF circuit, wherever terminals. A typical channel region contains only about L1.5 e

the intrinsic variations are desired, the layout and masking dopant atoms; therefore, as a MOSFET fabrication process

processes can follow special approaches to oppose or at least is scaled down, mismatch due to dopant fluctuation

avoid any variation-limiting techniques. increases [223]. Furthermore, since VT is inversely

3) VARIATIONS AT SCHEMATIC DESIGN LEVEL proportional to the square root of the device area [224];

An intrinsic-based variation of a MOSFET’s parameter therefore, the current will have a similar dependency on the

among similarly designed MOSFETs within a chip is usually area. For example, in analog designs, to improve the current

referred to as intra -die variation or mismatch. These matching by a factor of 2, the device area is quadrupled. One

variations can be due to random local effects (such as the of the approaches to achieve that is doubling both W and L.

non-flatness of the polysilicon gate due to granularity) and to In small-geometry devices, various factors contribute to

tox gradients over the chip. The general trend of MOSFET ∆VT0 , such as non-uniform vertical and lateral doping

technology evolution is toward smaller horizontal concentrations, short channel effect (SCE), narrow width

dimensions, smaller physical t ox , smaller junction depth, effect (NWE), and drain-induced barrier lowering (DIBL)

heavier substrate doping, and (although not always) lower [217]. At the schematic design level, a designer can choose

power supply voltage. In Fig. 5, a planar bulk MOSFET has L and W of the MOSFETs. In short-channel MOSFETS, the

as a mask length (LM); this length is reduced due to depletion SCE varies VT0 by a value denoted as (∆VSCE T0 ), then:

of the source and drain junctions by a length (L dep ) on each

side, leaving a channel length (L), which is determined as VT =VT0 ± ∆VSCE

T0 (7)

[222]:

Where (±∆VSCE

T0 ) is considered positive, despite the

L = LM − 2 Ldep (5) channel type. The variation’s sign in (2.18.3) is negative for

n- channel and positive for p-channel. In other words, the

It is important to emphasize that L, L M, and Ldep exist even term (± ∆VSCE

T0 ) always carries an opposite sign to VT0 , as the

depletion regions around the junctions (the wells) reduce V T, MOSFETs [201].

where |∆VSCE

T0 | ∝ (Xj /L) [225]. - For resistors, an N-well diffusion resistor is less

On the other hand, in narrow-channel MOSFETs, when W susceptible to the intrinsic variations due to its lower

is on the same magnitude order as the maximum depletion doping and larger volume. Furthermore, it is made of

region thickness Xdm, another source of variation that monocrystalline materials, which reduces the impact of

contributes to VT must be considered. In addition to the oxide defects and grain borders [228]. Alternatively, a

thickness above the channel (tox), there is a thick field oxide MOSFET-base resistor is more susceptible to the

(FOX), which covers the region around the channel to resist intrinsic variations.

the surface leakage currents between adjacent MOSFETs. From all the above, to improve the uniqueness of MOSFET-

The overlapped area between the gate electrode and FOX based PUF design, it is significant to include short-channel

develops a low depletion region, which raises V T. This MOSFETs and/or narrow-channel MOSFETs. In either way,

phenomenon is known as the narrow width effect (NWE) VT would be more distinct among the equally scaled

[226]. The narrow-channel-based variation of VT0 is denoted MOSFETs, which can eventually lead to more distinctive

as (∆VNWE

T0 ), which always carries a positive sign. Then it PUF chips. Since such differences are attributed to random

affects VT as [225]: intrinsic variations, it is quite probable to have unique

properties for each PUF chip. Reversing or at least avoiding

any variation-limiting approach allow for more intrinsic

VT =VT0 ± ∆VNWE

T0 (8)

variations, which can create unique PUF chips. Furthermore,

scaling down a MOSFET increases the sensitivity to

Where the sign in (2.18.4) is positive for n-channel and

threshold voltage variations [229].

negative for p-channel. In other words, the term ± ∆VNWE T0

always has a similar sign to VT0 , and if the absolute values VII. PUF TYPES AND APPLICATIONS

are considered, the narrow channel causes extra depletion This section lists the most basic types of PUFs and classifies

charge that ultimately increases |VT |. Combining SCE and them according to various categories and focuses on

NWE, then VT is determined as: electronic PUFs.

A. PUF Overview and Classifications

VT =VT0 ± ∆VSCE NWE

T0 ± ∆VT0 (9)