Professional Documents

Culture Documents

Designing A Dual-Fuel Motor Management System With Zynq: Frank de Bont

Uploaded by

SaasiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Designing A Dual-Fuel Motor Management System With Zynq: Frank de Bont

Uploaded by

SaasiCopyright:

Available Formats

Designing a dual-fuel motor

management system with Zynq

Frank de Bont Cereslaan 10b

5384 VT Heesch

Trainer / Consultant

+31 (0)412 660088

info@core-vision.nl

www.core-vision.nl

BRINGING

BRINGING YOU

YOU THE

THE NEXT

NEXT LEVEL

LEVEL IN

IN EMBEDDED

EMBEDDED DEVELOPMENT

DEVELOPMENT 1

_

_

Agenda

Customer Requirements

Engine Management System

LNG Supply

Sensors / Actuators

AR Electronic Control Unit

Zynq Architecture

Design Flow and Tools

High-Speed ADC IP-block

Software Partitioning and Communication Channels

Why Linux with Xenomai

eMMC Configuration

Who is Core|Vision

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 2

_

Customer Requirements

1

-

Design a dual-fuel motor management system

54255**slide

with real-time control

Hardware Platform Caterpillar 3500

Diesel

LNG (Liquefied Natural Gas)

High fuel efficiency

Start up on Diesel and then switch over to a mixture with LNG

Lowest possible emissions

NOx , SOx , CO2 and CH4 (methaan)

Easy to retrofit

Suitable for different qualities of LNG

Still 100% Diesel as a fall back

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 3

_

Customer Requirements cont

1

-

Focus on motor management control also called

54255**slide

ArenaRed Electronic Control Unit

Hardware Platform Caterpillar 3500

Diesel

LNG (Liquefied Natural Gas)

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 4

_

Engine Management System

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 5

_

Engine Management System

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 6

_

LNG Supply

Full controlled by the AR-ECU

A full fail-safe system

On-board diagnostics

Power and Temperature sensors

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 7

_

Sensors / Actuators

Combustion in each cylinder is monitored by a set of

cylinder pressure sensors

These allows the AR-ECU to optimize the combustion timing

and gas mixture

In the exhaust are UEGO λ-sensors and temperature sensors

to monitor the results of each combustion cycle

Turbo

Boost Wastegate

Inlet

Wastegate Manifold

Filter Compressor Intercooler Gas

P

P P T λ

P T Diesel

Turbine

P Pressure sensor

T Temperature sensor

λ Lambda (UEGO) sensor

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 8

_

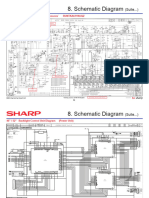

AR Electronic Control Unit

Connectors Connectors

[PWR] 16

Power Supply Units Injector P

16

Injector N

g

ia

ia

D

D

+24V Power Supply Units +24V Power Supply Units

for internal supplies for external supplies

8

8 x EMD 8 x EMD

+15V

+12V

-15V

+5V

+8V

[STOP]

Emergency stop

1

ESTOP OUT ISOLATED ISOLATED

+15V

+12V

-15V

[DL]

+5V

+8V

CAT data link

+24Vinj

+24Vinj

2 Kill / IRQ

2 Kill / IRQ

UART

UART

Fault

Fault

Fire

Fire

1 EMERGENCY Watchdog and health

ESTOP

Termination

STOP check uP

8

1

8

1

2

CAT Data Link

Internal

JTAG DDR3

8 x LED Expansion

Connector 2x 2Gb

Connectors

[DO_HC]

SPI Flash E-MMC

50 MHz Digital Output High Current

Diag

64Mb 32GB

+24V

43

32

20

16

5

2

1

2

1

General Purpose

Data Ctrl

+ Protection

I/O Controller

I/O Controller

Configuration

I/O Controller

I/O Controller

I/O Controller

I/O Controller

[CAN]

Controller

Controller

Controller

Controller

Controller

24V/5A

22

Interrupt

Interrupt

Interrupt

Memory

UART

UART

UART

JTAG

Clock

Out

SDIO

CAN interfaces 22

Digital out

4 Diag

Controller

SPIController

6 6

CAN

CAN CAN

CAN

12 14

CAN Phy

Phy Controller

Controller

MCP2551

MCP2551 MCP2515

MCP2515

[EMD]

SPI

Electromechanical Drivers [AO]

Analog Out 4-20mA

I/O Controller

Controller

4-20mA

CAN

Zynq SoC

driver

CAN

2 2 2 4

CAN Phy Analog out

MCP2551

[SHD] [POS] [AI_LS] [AI_HS] [DI] [ETH]

Remote Position interfaces Analog Input Low Speed Analog Input High Digital Input Ethernet interfaces

Shutdown Speed

Controller

+24V

CAN

CAN

2 2

CAN Phy

I/O Controller

Controller

SPI Controller

I/O Controller

I/O Controller

I/O Controller

I/O Controller

I/O Controller

I/O Controller

I/O Controller

Purpose Out

SPIController

+ Protection

24V/300mA

3

Controller

MCP2551

AR ECU x

AR ECU x

General

RGMII

3

MII

Digital out

1 Diag

SPI

SPI

1 6 3 3 6 10 1 32 2 2 15 12 [DO_LC]

10

Digital Output Low Current

Rst CA Pulse SWITCH

Synchroniser (3 ports)

2 3 3 2 4

[PWR] 6x 7

6 ADC

ADC

Power Supply Units RS422 HALL VRSensor

Sensor VR Sensor

ADS8363

Ch.ADC

HALL

6 Ch. ADC

VR RS485

MCP3903

ADS8363

RS422 4 4 4 4

6MCP3903

interrface Interface

Interface Interface

PHY

PHY interrface

Shutdown

PHY

Remote

22Ch.

Ch.

+24V

+24Vinj

Gbit Phy

42 8

Protection 40 x COND COND

0-10V

and 2x Magnetics Magnetics Magnetics

4-20mA

Vbatt

+5V

+12V

+8V

Gnd

Preamp

1 12 3 3 4 4 42 8 32 8 8 8

Shutdown

Encoder

HALL sensor

VR

ADC

OBD/Debug

RS485 RX

RS485 TX

Digital in

100Mb Link

Cascade

ADC

100Mb Link

Cascade

Connectors

PWR

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 9

_

AR Electronic Control Unit

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 10

_

AR Electronic Control Unit cont

General Interfaces

DDR3 memory

eMMC

SPI Flash

JTAG

RS485

CAN

Ethernet

…

Monitor Interfaces

16x 12 bits ADC

2x UARTs

1x CAN

10x PWM outputs

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 11

_

AR Electronic Control Unit cont

Electromechanical drivers

High Voltage IO

High Current IO

Digital Interfaces

High Current IO

Low Current IO

Sensor Inputs

Analog Interfaces

High Speed Inputs

Low Speed Inputs

Analog Outputs

Misc Interfaces

LED bank

Position Interface

Expansion Connector

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 12

_

Catepillar 3500 & AR-ECU

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 13

_

Zynq Architecture

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 14

_

Zynq Architecture cont

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 15

_

Zynq Architecture cont

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 16

_

Zynq Architecture cont

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 17

_

Zynq Architecture cont

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 18

_

Design Flow and Tools

Software FPGA hardware

Real-time OS ADC IP Interface

Drivers eMMC interface

APIs DDR3 memory

... IO

JTAG

...

Tools Tools

Vivado SDK Vivado

Matlab Matlab

... ModelSim

Altium

...

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 19

_

High-Speed ADC IP-block

High-Speed ADC to read

pressure sensors

AXI streaming interface for

transmitting ADC data

completed with timestamp and

crank angle

AXI slave interface for

configuration

Interface to 2 ADC channels

of the ADS8363

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 20

_

High-Speed ADC IP-block cont

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 21

_

High-Speed ADC IP-block cont

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 22

_

Software Partitioning and

Communication Channels

Zynq SoC heart of the system

Linux with Realtime

extension Xenomai

Licensed & custom IP

in FPGA PL

Microprocessor for

Watchdog & Health

Monitor

Software controlled

EMD Injector Drivers

Communication

cascading channel

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 23

_

Cascading Channels

Multiple AR-ECUs can be cascaded so the system can

control more than eight cyclinders.

AR-ECU

AR-ECU AR-ECU

AR-ECU AR-ECU

AR-ECU

#1 CA Pulse

Sync

#2 CA Pulse

Sync

#3 CA Pulse

Sync

Eth Eth Eth Eth Eth Eth Eth Eth Eth

100 Mb 1 Gb 100 Mb 100 Mb 1 Gb 100 Mb 100 Mb 1 Gb 100 Mb

Since Ethernet is non real-time by nature, crucial real-

time signals will be routed over the four dedicated wires.

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 24

_

Why Linux with Xenomai

Zynq All Programmable SoC dual core Cortex-A9

Xilinx offers a kernel build and Linux kernel distribution by 3rd

parties

Support Linux 3.14.17 with patches for real-time extension

Xenomai 2.6.4 within SDK, version choice is limited

Xenomai offers greater flexibility and consistency because the

real-time tasks can share the same drivers, synchronization

primitives and memory as other non real-time tasks

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 25

_

eMMC Configuration

Initial Programming Running Bitfile Selection

Set boot mode pins of Zynq to Set boot mode pins of Zynq to

JTAG (can be forced in initial QSPI (can be forced in running Start

programming U-boot) U-boot)

Download initial programming Download running U-boot using

U-boot using JTAG QSPI

Updated Yes

bitfile

present in

eMMC?

Start initial programming U-boot Start running U-boot Program Yes

FPGA

succesful?

Download initial programming Download golden or updated No

kernel, ramdisk image and DTB bitfile using eMMC

files using TFTP

Golden Yes

Start initial programming kernel Download running kernel ramdisk image

image and DTB files using eMMC present in

eMMC?

Program Yes

FPGA

Run initial programming shell succesful?

scripts using rcS to download Start running kernel

from TFTP and program: No

• Running U-boot + FSBL to QSP

• Running kernel to eMMC

• Running ramdisk to eMMC

• Running DTB to eMMC

• Golden bitfile to eMMC Stuck in U-boot, no valid FPGA Done, FPGA loaded succesfully

• Update bitfile to eMMC image found

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 26

_

Flash Image Generation

Flash Image

Zynq

Configuration BootHeader

Wizard FSBL

(Executable)

Boot & Configuration

FSBL

Information

PS Register PL

Initialization PL

Bitstream(s)

Bitstream(s)

Flash Image

Generator

FSBL OS and/or OS and/or

(source Code) Application Application

User Created Code & data Code & data

Golden Image Golden Image

(optional) (optional)

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 27

_

Core|Vision

Our competences

Core|Vision has more than 125 man years of design experience in hard-

and software development. Our competence areas are:

System Design

FPGA Design

Consultancy / Training

Digital Signal Processing

Embedded Real-time Software

App development, IOS Android

Data Acquisition, digital and analog

Modeling & Simulation

ASIC Conversion & Prototyping

PCB design & Layout

Doulos & Xilinx Training Partner

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 28

_

?

?

Cereslaan 10b

5384 VT Heesch

+31 (0)412 660088

www.core-vision.nl

Email : info@core-vision.nl

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 29

_

Visit our booth 28

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 30

_

Training Program

Essentials of FPGA Design 1 day

Designing for Performance 2 days

Advanced FPGA Implementation 2 days

Design Techniques for Lower Cost 1 day

Designing with Spartan-6 and Virtex-6 Family 3 days

Essential Design with the PlanAhead Analysis Tool 1 day

Advanced Design with the PlanAhead Analysis Tool 2 days

Xilinx Partial Reconfiguration Tools and Techniques 2 days

Designing with the 7 Series Families 2 days

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 31

_

Training Program

Vivado Essentials of FPGA Design 2 days

Vivado Design Suite Tool Flow 1 day

Vivado Design Suite for ISE Users 1 day

Vivado Avanced XDC and STA for ISE Users 2 days

Vivado Advanced Tools & Techniques 2 days

Vivado Static Timing Analysis and XDC 2 days

Debugging Techniques Using Vivado Logic Analyzer 1 day

Essential Tcl Scripting for Vivado Design Suite 1 day

Vivado FPGA Design Methodology 1 day

Designing with the UltraScale Architecture 2 days

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 32

_

Training Program

Designing with Multi Gigabit Serial IO 3 days

High Level Synthesis with Vivado 2 days

C-Based HLS Coding for Hardware Designers 1 day

C-Based HLS Coding for Software Designers 1 day

DSP Design Using System Generator 2 days

Essential DSP Implementation Techniques for

Xilinx FPGAs 2 days

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 33

_

Training Program

Embedded Systems Design 2 days

Embedded Systems Software Design 2 days

Advanced Features and Techniques of SDK 2 days

Advanced Features and Techniques of EDK 2 days

Zynq All Programmable SoC Systems Archicture 2 days

Zynq All Programmable SoC Accelerators 1 day

C Language Programming with SDK 2 days

Embedded Design with PetaLinux SDK 2 days

Embedded C/C++ SDSoC Development

Environment and Methodology 1 day

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 34

_

Training Program

VHDL Design for FPGA 3 days

Advanced VDHL 2 days

Comprehensive VHDL 5 days

Expert VHDL Verification 3 days

Expert VDHL Design 2 days

Expert VHDL 5 days

Essential Digital Design Techniques 2 days

BRINGING YOU THE NEXT LEVEL IN EMBEDDED DEVELOPMENT 35

_

You might also like

- Turbofan SpecificationsDocument5 pagesTurbofan SpecificationsRasoul gholinia kiviNo ratings yet

- Improve Engine Performance with Low-Sac NozzleDocument2 pagesImprove Engine Performance with Low-Sac NozzleNguyễn Đình ĐứcNo ratings yet

- D.C. Powered Timing Light Model 161.2158 for 12 Volt Ignition Systems Sears Owners ManualFrom EverandD.C. Powered Timing Light Model 161.2158 for 12 Volt Ignition Systems Sears Owners ManualNo ratings yet

- The Lube Oil Centrifugal Filter: A Retrofittable Cleaning SystemDocument2 pagesThe Lube Oil Centrifugal Filter: A Retrofittable Cleaning SystemAnonymous alQXB11EgQNo ratings yet

- Work Shop Manual: 15 LD 225 15 LD 315 15 LD 350 15 LD 400 15 LD 440Document6 pagesWork Shop Manual: 15 LD 225 15 LD 315 15 LD 350 15 LD 400 15 LD 440Ayane DejeneNo ratings yet

- Hazop Action Sheet: Project Title Yanbu Phase 3 Power & Desalination Plant Interfaces P&ID Drawing NoDocument4 pagesHazop Action Sheet: Project Title Yanbu Phase 3 Power & Desalination Plant Interfaces P&ID Drawing NoVijaya Seharan NairNo ratings yet

- Transmission Digest January 2011Document68 pagesTransmission Digest January 2011transtechoz100% (5)

- Ken R 15920001Document2 pagesKen R 15920001Percy Ccalla sefrNo ratings yet

- ECM PINOUT GUIDEDocument4 pagesECM PINOUT GUIDEjemaliz100% (8)

- Sharp Runtka611wjqz psd-0698 Psu SCHDocument2 pagesSharp Runtka611wjqz psd-0698 Psu SCHMarko VujinovićNo ratings yet

- AGN 035 - Protect alternators from overloads and faultsDocument10 pagesAGN 035 - Protect alternators from overloads and faultsariwibowoNo ratings yet

- Winone Elevator Connection DiagramDocument40 pagesWinone Elevator Connection DiagramMuhammad Rashid75% (4)

- 74HC HCT154Document20 pages74HC HCT154CRISTIAN SORACANo ratings yet

- +3000036EN carelDocument4 pages+3000036EN carelFRANCISCO BRITO DIASNo ratings yet

- Linde 393 Service Manual PDFDocument126 pagesLinde 393 Service Manual PDFnenad100% (7)

- F8eb7 Quanta BDBD PDFDocument45 pagesF8eb7 Quanta BDBD PDFtrutleptNo ratings yet

- Control Solenid Main Mod Control Circuit High P0963Document4 pagesControl Solenid Main Mod Control Circuit High P0963Christian Ramos Alarcon100% (1)

- Lambardini 340 Workshop ManualDocument44 pagesLambardini 340 Workshop Manualsagarkali100% (1)

- Hydr 725 & 730 Serie AltaDocument2 pagesHydr 725 & 730 Serie Altasebastian jaramillo trujilloNo ratings yet

- Maxxforce 7 Epa 10Document2 pagesMaxxforce 7 Epa 10Juan Martinez100% (4)

- Fluidics 5800Document1 pageFluidics 5800Héctor GarcíaNo ratings yet

- Test Signals for Debugging TI LPRF SoCsDocument7 pagesTest Signals for Debugging TI LPRF SoCsMiguel Angel RupNo ratings yet

- Connecting an engine control moduleDocument1 pageConnecting an engine control moduleOmar Hernández100% (1)

- Default Switch/Jumper SettingsDocument16 pagesDefault Switch/Jumper SettingsRafael Avella100% (1)

- C#56 - RTU Interface For CPF SubstationsDocument9 pagesC#56 - RTU Interface For CPF Substationsabudhabi.inbornNo ratings yet

- Guide to Electronics Fuel Dispenser SUNNY-XE Model SDA 2222Document4 pagesGuide to Electronics Fuel Dispenser SUNNY-XE Model SDA 2222Faizan Majid0% (1)

- B224-FCC-LT-PID-111-11011 TO 11047 - LEGEND P&IDsDocument33 pagesB224-FCC-LT-PID-111-11011 TO 11047 - LEGEND P&IDsSahadev SinghaNo ratings yet

- 4 HydraulicsDocument51 pages4 Hydraulicsalexis aguirre espejoNo ratings yet

- Panasonic tnp4g4572p Psu SCHDocument4 pagesPanasonic tnp4g4572p Psu SCHagesoporteNo ratings yet

- SYS-1019D-16C-RAN13TP+ Quick Reference GuideDocument1 pageSYS-1019D-16C-RAN13TP+ Quick Reference GuideSribller DribbleNo ratings yet

- 318C PDFDocument4 pages318C PDFTidjani SallNo ratings yet

- G3606 Electrical System: Advisor MidsDocument2 pagesG3606 Electrical System: Advisor Mids巴啦啦No ratings yet

- EVNHPC TRI AN Unit Cooling System ApprovalDocument1 pageEVNHPC TRI AN Unit Cooling System Approvalnguyen rinNo ratings yet

- LT Cable Sizing Calculation With TECTON Comments - NTPL-TEC-TA5-E-222-B - R1Document19 pagesLT Cable Sizing Calculation With TECTON Comments - NTPL-TEC-TA5-E-222-B - R1Purushothaman SeenuNo ratings yet

- C9 Generator Set With EMCP 3 Electrical System: Engine Top ViewDocument2 pagesC9 Generator Set With EMCP 3 Electrical System: Engine Top Viewjoelalejandrosuarez33% (3)

- KENR95370001Document4 pagesKENR95370001Danny MaciasNo ratings yet

- Nokia 6233 rm-145 6234 rm-123Document10 pagesNokia 6233 rm-145 6234 rm-123me academyNo ratings yet

- COPIER (B264/B265) Point To Point Diagram: Bicu PCB 1Document14 pagesCOPIER (B264/B265) Point To Point Diagram: Bicu PCB 1josdavisNo ratings yet

- Buje Bronce - 4256364-02-DDocument1 pageBuje Bronce - 4256364-02-Dcesar guerreroNo ratings yet

- demo2LabDocument5 pagesdemo2LabSergio FeitozaNo ratings yet

- D9T Track-Type Tractor Electrical System: Harness and Wire Electrical Schematic SymbolsDocument4 pagesD9T Track-Type Tractor Electrical System: Harness and Wire Electrical Schematic SymbolsfernandoNo ratings yet

- Q64AD GH UserManual Hardware IB 0800223 BDocument1 pageQ64AD GH UserManual Hardware IB 0800223 BSebastián LozadaNo ratings yet

- UntitledDocument20 pagesUntitledSteve RindNo ratings yet

- H50CTE BRAUN Protection Rev-01Document4 pagesH50CTE BRAUN Protection Rev-01oskeyNo ratings yet

- QB400Document2 pagesQB400Éverton KafskiNo ratings yet

- Bulletin11M12A01-01E 101Document13 pagesBulletin11M12A01-01E 101Manuel GallegosNo ratings yet

- Workshopmanual lombardiniLGWDocument94 pagesWorkshopmanual lombardiniLGWbiuro.cnp.tczewNo ratings yet

- InBIO280 Installation and Connection Guide V2.0Document2 pagesInBIO280 Installation and Connection Guide V2.0fmanriquezarceNo ratings yet

- 机型:KDL42XS715UN: Konka Dtv Sch DesignDocument14 pages机型:KDL42XS715UN: Konka Dtv Sch DesignAlexis FloresNo ratings yet

- iNUKE NU6000DSP: Service ManualDocument45 pagesiNUKE NU6000DSP: Service ManualHerberth BarriosNo ratings yet

- G3612 Schesematic RENR5911!01!01-ALLDocument2 pagesG3612 Schesematic RENR5911!01!01-ALLAnonymous eii2XsNo ratings yet

- 0206 MACH7-Regelung Engl PDFDocument1 page0206 MACH7-Regelung Engl PDFSyed Mohammed Hussain100% (1)

- C15 and C18 Electrical System Industrial and Petroleum EngineDocument2 pagesC15 and C18 Electrical System Industrial and Petroleum EngineOsvaldo UrbanoNo ratings yet

- Jet45 AAS Systems Modules V2.19Document97 pagesJet45 AAS Systems Modules V2.19Pedro Miguel LealNo ratings yet

- Cxa VVVF 220Document1 pageCxa VVVF 220Mohamed ArefNo ratings yet

- Features: Diesel and LPG Forklift Trucks Capacity 8000, 9000 and 10000 LB H40D/T, H45D/T, and H50D/TDocument4 pagesFeatures: Diesel and LPG Forklift Trucks Capacity 8000, 9000 and 10000 LB H40D/T, H45D/T, and H50D/TLuis Barrera RamirezNo ratings yet

- Electrical Schematic, NL1812 - 47594169 - ADocument3 pagesElectrical Schematic, NL1812 - 47594169 - AMiguel VanegasNo ratings yet

- Electrical Schematic, NL1812 - 47594169 - ADocument3 pagesElectrical Schematic, NL1812 - 47594169 - AMiguel VanegasNo ratings yet

- BC 700 PB ManualDocument60 pagesBC 700 PB ManualSaasiNo ratings yet

- VACON NX All in One Application Guide DPD00903H enDocument354 pagesVACON NX All in One Application Guide DPD00903H enSaasiNo ratings yet

- EDC7UC31 CodesDocument22 pagesEDC7UC31 CodesFastcross Honda93% (15)

- BC 600 PB ManualDocument44 pagesBC 600 PB ManualSaasiNo ratings yet

- PROFIBUS Diagnostics Suite: User ManualDocument48 pagesPROFIBUS Diagnostics Suite: User ManualFer NandoNo ratings yet

- Fisher GX Control Valve and Actuator System: Scope of ManualDocument44 pagesFisher GX Control Valve and Actuator System: Scope of ManualSaasiNo ratings yet

- DET+ & DET-1600/1620 Detonation Sensing Monitors: Detects Detonation and Avoids Consequential Engine DamageDocument2 pagesDET+ & DET-1600/1620 Detonation Sensing Monitors: Detects Detonation and Avoids Consequential Engine DamageSaasiNo ratings yet

- BP1-R - Reverse Power RelayDocument8 pagesBP1-R - Reverse Power RelaySaasiNo ratings yet

- Fisher GX Control Valve and Actuator System: Scope of ManualDocument44 pagesFisher GX Control Valve and Actuator System: Scope of ManualSaasiNo ratings yet

- RGPR30NS40: BV 400 30V I 30A V 1.6V E 300mJDocument11 pagesRGPR30NS40: BV 400 30V I 30A V 1.6V E 300mJSaasiNo ratings yet

- DET+ & DET-1600/1620 Detonation Sensing Monitors: Detects Detonation and Avoids Consequential Engine DamageDocument2 pagesDET+ & DET-1600/1620 Detonation Sensing Monitors: Detects Detonation and Avoids Consequential Engine DamageSaasiNo ratings yet

- Produktinformation: ELFA ArtikelnrDocument29 pagesProduktinformation: ELFA ArtikelnrSaasiNo ratings yet

- Vdocument - in Bosch Edc7u31 Iveco 1033Document3 pagesVdocument - in Bosch Edc7u31 Iveco 1033SaasiNo ratings yet

- MOTORTECH Manual MIC4Document158 pagesMOTORTECH Manual MIC4Luis Eduardo Laporte MontoyaNo ratings yet

- MPC563xM-based Cost Effective ECU Chipset: Operation of The Suitcase DemoDocument11 pagesMPC563xM-based Cost Effective ECU Chipset: Operation of The Suitcase DemoSaasiNo ratings yet

- ACC 2613B Crank Angle EncoderDocument4 pagesACC 2613B Crank Angle EncoderSaasiNo ratings yet

- Small Outline Integrated Circuit (SOIC) Package: Application NoteDocument28 pagesSmall Outline Integrated Circuit (SOIC) Package: Application NoteSaasiNo ratings yet

- Servo Motor Specification Table with Rated Outputs up to 7kWDocument1 pageServo Motor Specification Table with Rated Outputs up to 7kWSaasiNo ratings yet

- Common Rail Systems by LiebherrDocument24 pagesCommon Rail Systems by LiebherrHùng Phạm100% (2)

- NISTIR 6785 MatML Workshop Report Example 1 Silicon Nitride CeramicDocument13 pagesNISTIR 6785 MatML Workshop Report Example 1 Silicon Nitride CeramicSaasiNo ratings yet

- Profibus On The QUICC Engine Block: Application NoteDocument24 pagesProfibus On The QUICC Engine Block: Application NoteSaasiNo ratings yet

- Wartsila 14 Product GuideDocument70 pagesWartsila 14 Product GuideSaasiNo ratings yet

- Instrumentation and Automation: 23.1 Monitoring Equipment Mounted On The EngineDocument28 pagesInstrumentation and Automation: 23.1 Monitoring Equipment Mounted On The EngineSaasi100% (1)

- Zpduino ArduinoDocument55 pagesZpduino ArduinoSergio RobertoNo ratings yet

- Fuel feed pump parts list for Wärtsilä Vasa 32 engineDocument4 pagesFuel feed pump parts list for Wärtsilä Vasa 32 engineSaasiNo ratings yet

- DKX3 v3.0.1 0C EDocument192 pagesDKX3 v3.0.1 0C ESaasiNo ratings yet

- Liebherr d934 122 MM Diesel EngineDocument28 pagesLiebherr d934 122 MM Diesel EngineSaasiNo ratings yet

- Edh Ed HandbookDocument495 pagesEdh Ed HandbookUndibal Alejandro RivasNo ratings yet

- AN 370: Using The Intel FPGA Serial Flash Loader With The Intel Quartus Prime SoftwareDocument16 pagesAN 370: Using The Intel FPGA Serial Flash Loader With The Intel Quartus Prime SoftwareSaasiNo ratings yet

- Trends in Vehicle and Fuel Technologies Review of Past TrendsDocument247 pagesTrends in Vehicle and Fuel Technologies Review of Past TrendsAmit ShuklaNo ratings yet

- Fuel injection pump functions and typesDocument5 pagesFuel injection pump functions and typesanilNo ratings yet

- Fuel System With Bosch Fuel InjDocument4 pagesFuel System With Bosch Fuel InjreggissNo ratings yet

- Design & Thermal Analysis of I.C. Engine Poppet Valves Using Solidworks and FEADocument9 pagesDesign & Thermal Analysis of I.C. Engine Poppet Valves Using Solidworks and FEAAnonymous kw8Yrp0R5rNo ratings yet

- SV 5C 1Document3 pagesSV 5C 1FredNo ratings yet

- Bukh Marine Diesel EnginesDocument9 pagesBukh Marine Diesel EnginesDimas SaputroNo ratings yet

- Greaves 200 Kva Generator Set PDFDocument2 pagesGreaves 200 Kva Generator Set PDFZaw TunNo ratings yet

- Honda Lead NHX110 2009 Service ManualDocument431 pagesHonda Lead NHX110 2009 Service ManualDontAskTwice85% (34)

- BJ Cicada: Bore: Stroke: Displacement: 0.437" (11.10mm) 0.554" (14.07mm) 0.093 Cuin (1.362cc)Document5 pagesBJ Cicada: Bore: Stroke: Displacement: 0.437" (11.10mm) 0.554" (14.07mm) 0.093 Cuin (1.362cc)Vignesh WaranNo ratings yet

- A320 Sections To Printed 70%Document3 pagesA320 Sections To Printed 70%ptm78mgtd9No ratings yet

- 4B SeriesDocument59 pages4B SeriesalxsscabalNo ratings yet

- Porsche ECU Pins....Document4 pagesPorsche ECU Pins....José BenavidesNo ratings yet

- 1997 Mercury Villager Engine Controls Remove and InstallDocument13 pages1997 Mercury Villager Engine Controls Remove and InstallRubenNo ratings yet

- Quincy QRNG Spec SheetDocument4 pagesQuincy QRNG Spec SheetAlanNo ratings yet

- Mantenimiento 120C 160C LCDocument2 pagesMantenimiento 120C 160C LCGustavo Gonzalez100% (1)

- TM 9-2805-257-24PDocument110 pagesTM 9-2805-257-24PAdvocateNo ratings yet

- Cummins - ISL9 CM2350 (2013-17)Document18 pagesCummins - ISL9 CM2350 (2013-17)Melvin Zepeda100% (2)

- Bendix - TU-FLO 750 Air Compressor Service Data (SD-01-344)Document40 pagesBendix - TU-FLO 750 Air Compressor Service Data (SD-01-344)Carlos Rivera100% (1)

- Perkins Industrial EnginesDocument46 pagesPerkins Industrial EnginesCESAR NASCIMENTO100% (2)

- QSK60 G4 PDFDocument2 pagesQSK60 G4 PDFLuki100% (2)

- Technical Presentation on Common Rail Diesel Engine SystemsDocument57 pagesTechnical Presentation on Common Rail Diesel Engine Systemsempu pacolNo ratings yet

- 2003 Camry Diagnostic Trouble Code Chart DtcengDocument8 pages2003 Camry Diagnostic Trouble Code Chart DtcengMontrealPaulNo ratings yet

- Ads Fcu - Governor Capabilities List 2017Document16 pagesAds Fcu - Governor Capabilities List 2017luiz phillipNo ratings yet

- MWM Limit ValueDocument19 pagesMWM Limit ValueKhokon Kumer Saha100% (3)

- Acura TSX Sport Wagon L4-2.4L 2011 Timing Chain: Service and RepairDocument11 pagesAcura TSX Sport Wagon L4-2.4L 2011 Timing Chain: Service and RepairCarlos Gunter Tamayo MoralesNo ratings yet

- Lubricating Oil Pump Bearing inspection-WS18V005Document1 pageLubricating Oil Pump Bearing inspection-WS18V005tomiNo ratings yet

- 02 - Engine Operating CharateristicsDocument25 pages02 - Engine Operating CharateristicsFabio BosioNo ratings yet

- Automotive Pollution and Control PDFDocument69 pagesAutomotive Pollution and Control PDFSudhanshu Gupta100% (6)

- Mitsubishi 6DB1 Engine PartsDocument5 pagesMitsubishi 6DB1 Engine PartsEngineParts250% (6)

- Compressure Spares Requirement - 2020Document2 pagesCompressure Spares Requirement - 2020A2 BhaskarNo ratings yet