Professional Documents

Culture Documents

74AC245 FairchildSemiconductor

Uploaded by

Elyes MbarekOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74AC245 FairchildSemiconductor

Uploaded by

Elyes MbarekCopyright:

Available Formats

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

January 2008

74AC245, 74ACT245

Octal Bidirectional Transceiver with 3-STATE

Inputs/Outputs

Features General Description

■ ICC and IOZ reduced by 50% The AC/ACT245 contains eight non-inverting bidirec-

■ Non-inverting buffers tional buffers with 3-STATE outputs and is intended for

■ Bidirectional data path

bus-oriented applications. Current sinking capability is

24mA at both the A and B ports. The Transmit/Receive

■ A and B outputs source/sink 24mA

(T/R) input determines the direction of data flow through

■ ACT245 has TTL-compatible inputs the bidirectional transceiver. Transmit (active-HIGH)

enables data from A ports to B ports; Receive (active-

LOW) enables data from B ports to A ports. The Output

Enable input, when HIGH, disables both A and B ports

by placing them in a HIGH Z condition.

Ordering Information

Package

Order Number Number Package Description

74AC245SC M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

74AC245SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74AC245MTC MTC20 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153,

4.4mm Wide

74AC245PC N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

74ACT245SC M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

74ACT245SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74ACT245MSA MSA20 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide

74ACT245MTC MTC20 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153,

4.4mm Wide

74ACT245PC N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering number.

All packages are lead free per JEDEC: J-STD-020B standard.

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Connection Diagram Logic Symbol

IEEE/IEC

Pin Description

Pin

Names Description

OE Output Enable Input

T/R Transmit/Receive Input

A0–A7 Side A 3-STATE Inputs or 3-STATE

Outputs

B0–B7 Side B 3-STATE Inputs or 3-STATE

Outputs

Truth Table

Inputs

OE T/R Outputs

L L Bus B Data to Bus A

L H Bus A Data to Bus B

H X HIGH-Z State

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 2

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol Parameter Rating

VCC Supply Voltage −0.5V to +7.0V

IIK DC Input Diode Current

VI = −0.5V −20mA

VI = VCC + 0.5 +20mA

VI DC Input Voltage −0.5V to VCC + 0.5V

IOK DC Output Diode Current

VO = −0.5V −20mA

VO = VCC + 0.5V +20mA

VO DC Output Voltage −0.5V to VCC + 0.5V

IO DC Output Source or Sink Current ±50mA

ICC or IGND DC VCC or Ground Current per Output Pin ±50mA

TSTG Storage Temperature −65°C to +150°C

TJ Junction Temperature 140°C

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to absolute maximum ratings.

Symbol Parameter Rating

VCC Supply Voltage

AC 2.0V to 6.0V

ACT 4.5V to 5.5V

VI Input Voltage 0V to VCC

VO Output Voltage 0V to VCC

TA Operating Temperature −40°C to +85°C

∆V / ∆t Minimum Input Edge Rate, AC Devices: 125mV/ns

VIN from 30% to 70% of VCC, VCC @ 3.3V, 4.5V, 5.5V

∆V / ∆t Minimum Input Edge Rate, ACT Devices: 125mV/ns

VIN from 0.8V to 2.0V, VCC @ 4.5V, 5.5V

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 3

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

DC Electrical Characteristics for AC

TA = +25°C TA = −40°C to +85°C

Symbol Parameter VCC (V) Conditions Typ. Guaranteed Limits Units

VIH Minimum HIGH Level 3.0 VOUT = 0.1V or 1.5 2.1 2.1 V

Input Voltage 4.5 VCC – 0.1V 2.25 3.15 3.15

5.5 2.75 3.85 3.85

VIL Maximum LOW Level 3.0 VOUT = 0.1V or 1.5 0.9 0.9 V

Input Voltage 4.5 VCC – 0.1V 2.25 1.35 1.35

5.5 2.75 1.65 1.65

VOH Minimum HIGH Level 3.0 IOUT = –50µA 2.99 2.9 2.9 V

Output Voltage 4.5 4.49 4.4 4.4

5.5 5.49 5.4 5.4

3.0 VIN = VIL or VIH, 2.56 2.46

IOH = –12mA

4.5 VIN = VIL or VIH, 3.86 3.76

IOH = –24mA

5.5 VIN = VIL or VIH, 4.86 4.76

IOH = –24mA(1)

VOL Maximum LOW Level 3.0 IOUT = 50µA 0.002 0.1 0.1 V

Output Voltage 4.5 0.001 0.1 0.1

5.5 0.001 0.1 0.1

3.0 VIN = VIL or VIH, 0.36 0.44

IOL = 12mA

4.5 VIN = VIL or VIH, 0.36 0.44

IOL = 24mA

5.5 VIN = VIL or VIH, 0.36 0.44

IOL = 24mA(1)

IIN(2) Maximum Input 5.5 VI = VCC, GND ±0.1 ±1.0 µA

Leakage Current

IOLD Minimum Dynamic 5.5 VOLD = 1.65V Max. 75 mA

IOHD Output Current(3) 5.5 VOHD = 3.85V Min. −75 mA

ICC (2) Maximum Quiescent 5.5 VIN = VCC or GND 4.0 40.0 µA

Supply Current

IOZT Maximum I/O 5.5 VI (OE) = VIL, VIH; ±0.3 ±3.0 µA

Leakage Current VI = VCC, GND;

VO = VCC, GND

Notes:

1. All outputs loaded; thresholds on input associated with output under test.

2. IIN and ICC @ 3.0V are guaranteed to be less than or equal to the respective limit @ 5.5V VCC.

3. Maximum test duration 2.0ms, one output loaded at a time.

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 4

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

DC Electrical Characteristics for ACT

TA = +25°C TA = −40°C to +85°C

Symbol Parameter VCC (V) Conditions Typ. Guaranteed Limits Units

VIH Minimum HIGH Level 4.5 VOUT = 0.1V or 1.5 2.0 2.0 V

Input Voltage 5.5 VCC − 0.1V 1.5 2.0 2.0

VIL Maximum LOW 4.5 VOUT = 0.1V or 1.5 0.8 0.8 V

Level Input Voltage 5.5 VCC − 0.1V 1.5 0.8 0.8

VOH Minimum HIGH Level 4.5 IOUT = −50µA 4.49 4.4 4.4 V

Output Voltage 5.5 5.49 5.4 5.4

4.5 VIN = VIL or VIH, 3.86 3.76

IOH = −24mA

5.5 VIN = VIL or VIH, 4.86 4.76

IOH = −24mA(4)

VOL Maximum LOW 4.5 IOUT = 50µA 0.001 0.1 0.1 V

Level Output Voltage 5.5 0.001 0.1 0.1

4.5 VIN = VIL or VIH, 0.36 0.44

IOL = 24mA

5.5 VIN = VIL or VIH, 0.36 0.44

IOL = 24mA(4)

IIN Maximum Input 5.5 VI = VCC, GND ±0.1 ±1.0 µA

Leakage Current

ICCT Maximum ICC/Input 5.5 VI = VCC − 2.1V 0.6 1.5 mA

IOLD Minimum Dynamic 5.5 VOLD = 1.65V Max. 75 mA

IOHD Output Current(5) 5.5 VOHD = 3.85V Min. −75 mA

ICC Maximum Quiescent 5.5 VIN = VCC or GND 4.0 40.0 µA

Supply Current

IOZT Maximum I/O 5.5 VI (OE) = VIL, VIH; ±0.3 ±3.0 µA

Leakage Current VI = VCC, GND;

VO = VCC, GND

Notes:

4. All outputs loaded; thresholds on input associated with output under test.

5. Maximum test duration 2.0ms, one output loaded at a time.

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 5

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

AC Electrical Characteristics for AC

TA = +25°C, TA = −40°C to +85°C,

CL = 50pF CL = 50pF

Symbol Parameter VCC (V)(6) Min. Typ. Max. Min. Max. Units

tPLH Propagation Delay, 3.3 1.5 5.0 8.5 1.0 9.0 ns

An to Bn or Bn to An 5.0 1.5 3.5 6.5 1.0 7.0

tPHL Propagation Delay, 3.3 1.5 5.0 8.5 1.0 9.0 ns

An to Bn or Bn to An 5.0 1.5 3.5 6.0 1.0 7.0

tPZH Output Enable Time 3.3 2.5 7.0 11.5 2.0 12.5 ns

5.0 1.5 5.0 8.5 1.0 9.0

tPZL Output Enable Time 3.3 2.5 7.5 12.0 2.0 13.5 ns

5.0 1.5 5.5 9.0 1.0 9.5

tPHZ Output Disable Time 3.3 2.0 6.5 12.0 1.0 12.5 ns

5.0 1.5 5.5 9.0 1.0 10.0

tPLZ Output Disable Time 3.3 2.0 7.0 11.5 1.5 13.0 ns

5.0 1.5 5.5 9.0 1.0 10.0

Note:

6. Voltage range 3.3 is 3.3V ± 0.3V. Voltage range 5.0 is 5.0V ± 0.5V.

AC Electrical Characteristics for ACT

TA = +25°C, TA = −40°C to +85°C,

CL = 50pF CL = 50pF

Symbol Parameter VCC (V)(7) Min. Typ. Max. Min. Max. Units

tPLH Propagation Delay, 5.0 1.5 4.0 7.5 1.5 8.0 ns

An to Bn or Bn to An

tPHL Propagation Delay, 5.0 1.5 4.0 8.0 1.0 9.0 ns

An to Bn or Bn to An

tPZH Output Enable Time 5.0 1.5 5.0 10.0 1.5 11.0 ns

tPZL Output Enable Time 5.0 1.5 5.5 10.0 1.5 12.0 ns

tPHZ Output Disable Time 5.0 1.5 5.5 10.0 1.0 11.0 ns

tPLZ Output Disable Time 5.0 2.0 5.0 10.0 1.5 11.0 ns

Note:

7. Voltage range 5.0 is 5.0V ± 0.5V.

Capacitance

Symbol Parameter Conditions Typ. Units

CIN Input Capacitance VCC = OPEN 4.5 pF

CI/O Input/Output Capacitance VCC = 5.0V 15.0 pF

CPD Power Dissipation Capacitance VCC = 5.0V 45.0 pF

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 6

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Physical Dimensions

13.00

12.60 A

11.43

20 11

B

9.50

10.65 7.60

10.00 7.40

2.25

1 10 0.65

PIN ONE 0.51 1.27 1.27

INDICATOR 0.35

0.25 M C B A

LAND PATTERN RECOMMENDATION

2.65 MAX SEE DETAIL A

0.33

C 0.20

0.10 C

0.30

0.75 0.10 SEATING PLANE

X 45°

0.25

NOTES: UNLESS OTHERWISE SPECIFIED

(R0.10)

A) THIS PACKAGE CONFORMS TO JEDEC

GAGE PLANE

(R0.10) MS-013, VARIATION AC, ISSUE E

0.25 B) ALL DIMENSIONS ARE IN MILLIMETERS.

8°

0° C) DIMENSIONS DO NOT INCLUDE MOLD

FLASH OR BURRS.

1.27 D) CONFORMS TO ASME Y14.5M-1994

0.40 SEATING PLANE E) LANDPATTERN STANDARD: SOIC127P1030X265-20L

(1.40) DETAIL A F) DRAWING FILENAME: MKT-M20BREV3

SCALE: 2:1

Figure 1. 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 7

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Physical Dimensions (Continued)

Figure 2. 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 8

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Physical Dimensions (Continued)

Figure 3. 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 9

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Physical Dimensions (Continued)

26.92

24.89

PIN #1 7.11

6.09

3.43

(0.97) 1.78 3.17 7.87

7° TYP

5.33 MAX

1.14

7° TYP

2.54 3.55

0.36 3.17 7.62

0.56 0.38 MIN 10.92 MAX

0.20

0.35

.001[.025] C

NOTES:

Figure 4. 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 10

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Physical Dimensions (Continued)

Figure 5. 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 11

74AC245, 74ACT245 — Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global

subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

ACEx® FPS™ PDP-SPM™ SyncFET™

Build it Now™ FRFET® Power220® ®

®

CorePLUS™ Global Power ResourceSM Power247 The Power Franchise®

CROSSVOLT™ Green FPS™ POWEREDGE®

CTL™ Green FPS™ e-Series™ Power-SPM™

Current Transfer Logic™ GTO™ PowerTrench® TinyBoost™

EcoSPARK® i-Lo™ Programmable Active Droop™ TinyBuck™

®

EZSWITCH™ * IntelliMAX™ QFET TinyLogic®

™ ISOPLANAR™ QS™ TINYOPTO™

MegaBuck™ QT Optoelectronics™ TinyPower™

®

MICROCOUPLER™ Quiet Series™ TinyPWM™

Fairchild® MicroFET™ RapidConfigure™ TinyWire™

Fairchild Semiconductor® MicroPak™ SMART START™ µSerDes™

®

FACT Quiet Series™ MillerDrive™ SPM UHC®

FACT® Motion-SPM™ STEALTH™ Ultra FRFET™

FAST® OPTOLOGIC® SuperFET™ UniFET™

FastvCore™ OPTOPLANAR® SuperSOT™-3 VCX™

®* ®

FlashWriter SuperSOT™-6

SuperSOT™-8

* EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS

HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE

APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS

PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S

WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support,

which, (a) are intended for surgical implant into the body or device, or system whose failure to perform can be

(b) support or sustain life, and (c) whose failure to perform reasonably expected to cause the failure of the life support

when properly used in accordance with instructions for use device or system, or to affect its safety or effectiveness.

provided in the labeling, can be reasonably expected to

result in a significant injury of the user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

This datasheet contains the design specifications for product

Advance Information Formative or In Design development. Specifications may change in any manner without notice.

This datasheet contains preliminary data; supplementary data will be

Preliminary First Production published at a later date. Fairchild Semiconductor reserves the right to

make changes at any time without notice to improve design.

This datasheet contains final specifications. Fairchild Semiconductor

No Identification Needed Full Production reserves the right to make changes at any time without notice to improve

the design.

This datasheet contains specifications on a product that has been

Obsolete Not In Production discontinued by Fairchild Semiconductor. The datasheet is printed for

reference information only.

Rev. I32

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC245, 74ACT245 Rev. 1.5.0 12

You might also like

- 74F245 Octal Bidirectional Transceiver With 3-STATE Outputs: Features General DescriptionDocument12 pages74F245 Octal Bidirectional Transceiver With 3-STATE Outputs: Features General DescriptionedgarlibanioNo ratings yet

- 74F245 Octal Bidirectional Transceiver With 3-STATE Outputs: General Description FeaturesDocument9 pages74F245 Octal Bidirectional Transceiver With 3-STATE Outputs: General Description FeaturesabcdNo ratings yet

- 74VHC245 Octal Bidirectional Transceiver With 3-STATE OutputsDocument6 pages74VHC245 Octal Bidirectional Transceiver With 3-STATE OutputsLIFT LIFTNo ratings yet

- 74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionDocument9 pages74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General Descriptionkt2018No ratings yet

- 74LCX245 Low Voltage Bidirectional Transceiver With 5V Tolerant Inputs and OutputsDocument14 pages74LCX245 Low Voltage Bidirectional Transceiver With 5V Tolerant Inputs and OutputsozmeenNo ratings yet

- 74LVXC4245 8-Bit Dual Supply Configurable Voltage Interface Transceiver With 3-STATE OutputsDocument8 pages74LVXC4245 8-Bit Dual Supply Configurable Voltage Interface Transceiver With 3-STATE OutputsStuxnetNo ratings yet

- 74AC541, 74ACT541 Octal Buffer/Line Driver With 3-STATE OutputsDocument12 pages74AC541, 74ACT541 Octal Buffer/Line Driver With 3-STATE OutputsChugo LimaNo ratings yet

- 74LVX245 Low Voltage Octal Bidirectional Transceiver: General Description FeaturesDocument6 pages74LVX245 Low Voltage Octal Bidirectional Transceiver: General Description FeaturesStuxnetNo ratings yet

- Datasheet LVC4245Document8 pagesDatasheet LVC4245AdamTrisnoizeAgustianNo ratings yet

- 74VHC541 Octal Buffer/Line Driver With 3-STATE Outputs: General DescriptionDocument7 pages74VHC541 Octal Buffer/Line Driver With 3-STATE Outputs: General Descriptionprdp_666No ratings yet

- 74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesDocument8 pages74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesSero StivNo ratings yet

- 74VHC125 Quad Buffer With 3-STATE Outputs: Features General DescriptionDocument9 pages74VHC125 Quad Buffer With 3-STATE Outputs: Features General DescriptionWilmer Yesid Granados JaimesNo ratings yet

- 74ABT245 Octal Transceiver With Direction Pin (3-State) : Features DescriptionDocument6 pages74ABT245 Octal Transceiver With Direction Pin (3-State) : Features DescriptionBontha RajuNo ratings yet

- Datasheet Vhct245aDocument9 pagesDatasheet Vhct245aMang Asep BuhoyNo ratings yet

- 74AC374, 74ACT374 Octal D-Type Flip-Flop With 3-STATE OutputsDocument15 pages74AC374, 74ACT374 Octal D-Type Flip-Flop With 3-STATE OutputsshohratNo ratings yet

- 54F/74F545 Octal Bidirectional Transceiver With TRI-STATE OutputsDocument8 pages54F/74F545 Octal Bidirectional Transceiver With TRI-STATE OutputsnooorNo ratings yet

- 74ACQ657 - 74ACTQ657 Quiet Series Octal Bidirectional Transceiver With 8-Bit Parity Generator/Checker and 3-STATE OutputsDocument10 pages74ACQ657 - 74ACTQ657 Quiet Series Octal Bidirectional Transceiver With 8-Bit Parity Generator/Checker and 3-STATE OutputsStuxnetNo ratings yet

- 74AC573, 74ACT573 Rev 2008Document13 pages74AC573, 74ACT573 Rev 2008ly1328067No ratings yet

- 74AC125 - Quad Buffer With TRI-STATE OutputsDocument8 pages74AC125 - Quad Buffer With TRI-STATE OutputsGabriel RacovskyNo ratings yet

- MM74HC245A Octal 3-STATE Transceiver: General Description FeaturesDocument8 pagesMM74HC245A Octal 3-STATE Transceiver: General Description FeaturesjoelpalzaNo ratings yet

- 74ACQ244 - 74ACTQ244 Quiet Series Octal Buffer/Line Driver With 3-STATE OutputsDocument10 pages74ACQ244 - 74ACTQ244 Quiet Series Octal Buffer/Line Driver With 3-STATE OutputsStuxnetNo ratings yet

- 74ac541 TristateDocument9 pages74ac541 TristateershadsaabNo ratings yet

- Triple Schmitt Inverter: Order CodesDocument7 pagesTriple Schmitt Inverter: Order CodeselieNo ratings yet

- 74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesDocument8 pages74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesrzvNo ratings yet

- 74ACQ240 - 74ACTQ240 Quiet Series Octal Buffer/Line Driver With 3-STATE OutputsDocument10 pages74ACQ240 - 74ACTQ240 Quiet Series Octal Buffer/Line Driver With 3-STATE OutputsStuxnetNo ratings yet

- Octal Bus Transceiver (3-State) : PD CC oDocument9 pagesOctal Bus Transceiver (3-State) : PD CC oSero StivNo ratings yet

- SN74LS245 Octal Bus Transceiver: LOW Power SchottkyDocument4 pagesSN74LS245 Octal Bus Transceiver: LOW Power Schottky4909151No ratings yet

- Is Now Part ofDocument10 pagesIs Now Part ofAntonioNo ratings yet

- DM74ALS645A Octal Bus Transceivers: General Description FeaturesDocument4 pagesDM74ALS645A Octal Bus Transceivers: General Description FeaturesMaiyeumotnguoiNTNo ratings yet

- Quad 2-Input and Gate: Order CodesDocument9 pagesQuad 2-Input and Gate: Order CodesSero StivNo ratings yet

- Quad 2 Channel Multiplexer (3-State) : PD CC oDocument10 pagesQuad 2 Channel Multiplexer (3-State) : PD CC oSero StivNo ratings yet

- Quad 2-Input and Gate: Order CodesDocument8 pagesQuad 2-Input and Gate: Order Codeszoya shaNo ratings yet

- MC74AC245, MC74ACT245 Octal Bidirectional Transceiver With 3 State Inputs/OutputsDocument10 pagesMC74AC245, MC74ACT245 Octal Bidirectional Transceiver With 3 State Inputs/OutputsPanagiotis PanagosNo ratings yet

- 74VHC245FT Datasheet en 20170222Document9 pages74VHC245FT Datasheet en 20170222rfidguysNo ratings yet

- Quad 2 Channel Multiplexer (3-State) : Order CodesDocument12 pagesQuad 2 Channel Multiplexer (3-State) : Order CodesSero StivNo ratings yet

- VHC32Document7 pagesVHC32quangNo ratings yet

- 74 Ac 240 DatasheetDocument8 pages74 Ac 240 DatasheetKlarizze GanNo ratings yet

- Octal Bus Buffer With 3 State Outputs (Non Inverted) : PD CC oDocument9 pagesOctal Bus Buffer With 3 State Outputs (Non Inverted) : PD CC ocriman45No ratings yet

- Single Fet Bus Switch 2.5-V/3.3-V Low-Voltage Switch With 5-V-Tolerant Level ShifterDocument14 pagesSingle Fet Bus Switch 2.5-V/3.3-V Low-Voltage Switch With 5-V-Tolerant Level ShifterPablo LloveraNo ratings yet

- 74 Act 08Document7 pages74 Act 08ChrisNo ratings yet

- 74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionDocument9 pages74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionMalik Mian Manzer MithaNo ratings yet

- B A Y - B A Y + : Quadruple 2-Input and GatesDocument8 pagesB A Y - B A Y + : Quadruple 2-Input and GatesJosé AdelinoNo ratings yet

- M54HCT257 PDFDocument12 pagesM54HCT257 PDFRio CandrapurwitaNo ratings yet

- 54ACTQ08 NationalSemiconductorDocument8 pages54ACTQ08 NationalSemiconductorJuan PerezNo ratings yet

- 74VHCT139A: Dual 2 To 4 Decoder/DemultiplexerDocument8 pages74VHCT139A: Dual 2 To 4 Decoder/DemultiplexerCyro PereiraNo ratings yet

- 74VHC273 Octal D-Type Flip-Flop: General Description FeaturesDocument10 pages74VHC273 Octal D-Type Flip-Flop: General Description FeaturesSero StivNo ratings yet

- Hex Inverter (Open Drain) : PD CC oDocument8 pagesHex Inverter (Open Drain) : PD CC oSero StivNo ratings yet

- Hex Inverter (Open Drain) : Order CodesDocument9 pagesHex Inverter (Open Drain) : Order CodesSero StivNo ratings yet

- Dual 2-Input Nor Gate: Order CodesDocument7 pagesDual 2-Input Nor Gate: Order CodeselieNo ratings yet

- SN74AUP1T157 (Electrónica Digital)Document15 pagesSN74AUP1T157 (Electrónica Digital)OscarHoracioSernaPradoNo ratings yet

- DatasheetDocument7 pagesDatasheetStuxnetNo ratings yet

- 74LV08ADocument8 pages74LV08AEngin UzunNo ratings yet

- 74vhct245aft 74vhct245aft 74vhct245aft 74vhct245aftDocument9 pages74vhct245aft 74vhct245aft 74vhct245aft 74vhct245aftIvan PalominoNo ratings yet

- Octal Bus Buffer With 3 State Outputs (Inverted) : Order CodesDocument10 pagesOctal Bus Buffer With 3 State Outputs (Inverted) : Order CodesSero StivNo ratings yet

- Porta Lógica XORDocument7 pagesPorta Lógica XORLuiz BitencourtNo ratings yet

- Datasheet TC74HC153 - ToshibaDocument9 pagesDatasheet TC74HC153 - ToshibaM TAQYUDDIN FAWWASNo ratings yet

- DS011647Document10 pagesDS011647Paulo Henrique ValérioNo ratings yet

- Octal Bus Transceiver (3-State) : Order CodesDocument10 pagesOctal Bus Transceiver (3-State) : Order CodesSero StivNo ratings yet

- 74ACT00Document7 pages74ACT00Ahmed ElarbeNo ratings yet

- Fig. 1. Flyback Converter With Conventional Lossless LCD Snubber. Fig. 2. Flyback Converter With The Proposed Lossless LCD SnubberDocument1 pageFig. 1. Flyback Converter With Conventional Lossless LCD Snubber. Fig. 2. Flyback Converter With The Proposed Lossless LCD SnubberElyes MbarekNo ratings yet

- PSIM User Manual PDFDocument280 pagesPSIM User Manual PDFHelenio Salvador PizarroNo ratings yet

- PSIM User Manual PDFDocument280 pagesPSIM User Manual PDFHelenio Salvador PizarroNo ratings yet

- An1376 25w Quasiresonant Flyback Converter For Settop Box Application Using The l6565 StmicroelectronicsDocument35 pagesAn1376 25w Quasiresonant Flyback Converter For Settop Box Application Using The l6565 StmicroelectronicsElyes MbarekNo ratings yet

- PSIM User Manual PDFDocument280 pagesPSIM User Manual PDFHelenio Salvador PizarroNo ratings yet

- HCPL 316J 000eDocument34 pagesHCPL 316J 000eElyes MbarekNo ratings yet

- Robo RoverDocument40 pagesRobo RoverElyes MbarekNo ratings yet

- Diehl 3000H Manual PDFDocument90 pagesDiehl 3000H Manual PDFElyes MbarekNo ratings yet

- Queen Manual PDFDocument25 pagesQueen Manual PDFFrancisc OszNo ratings yet

- Diehl 3000H Manual PDFDocument90 pagesDiehl 3000H Manual PDFElyes MbarekNo ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- tms320f28069 PDFDocument182 pagestms320f28069 PDFElyes MbarekNo ratings yet

- LabVIEW Mostly Missed Question in CLADDocument39 pagesLabVIEW Mostly Missed Question in CLADprsaxenaNo ratings yet

- LabVIEW Mostly Missed Question in CLADDocument39 pagesLabVIEW Mostly Missed Question in CLADprsaxenaNo ratings yet

- UT206A 1000A Digital Clamp Meters - UT200 - UNI-TDocument5 pagesUT206A 1000A Digital Clamp Meters - UT200 - UNI-TElyes MbarekNo ratings yet

- En - stm32PMSMFOCSDK Getting StartedDocument82 pagesEn - stm32PMSMFOCSDK Getting StartedElyes MbarekNo ratings yet

- RDSO Specification For RelayDocument58 pagesRDSO Specification For RelayTarun Bhateja100% (2)

- Esp Troubleshooting Guide PDFDocument65 pagesEsp Troubleshooting Guide PDFkalpeshkdg100% (3)

- Especificações Gerais - LIQIDocument30 pagesEspecificações Gerais - LIQIJonathan Machado D. SouzaNo ratings yet

- Circuit Breaker FinalDocument56 pagesCircuit Breaker Finalmanikumar 143No ratings yet

- Caterpillar 3406 Engine Service Manual S N 92u1Document10 pagesCaterpillar 3406 Engine Service Manual S N 92u1سام سپه پورNo ratings yet

- Cat Lovato ATL20Document6 pagesCat Lovato ATL20Luis FloresNo ratings yet

- Actuators & Positioners Linear Pneumatic Actuators: Data SheetDocument10 pagesActuators & Positioners Linear Pneumatic Actuators: Data SheetTai Dang HuyNo ratings yet

- IKEA Kitchen Dreambook 2013Document35 pagesIKEA Kitchen Dreambook 2013Thomas Solis100% (3)

- Impassa scw9055 57 User Manual en 29007827r001 WebDocument28 pagesImpassa scw9055 57 User Manual en 29007827r001 Webapi-372539559No ratings yet

- Pro Stock Electronic Fuel Injection Technical DocumentationDocument20 pagesPro Stock Electronic Fuel Injection Technical DocumentationAnan AtamnaNo ratings yet

- Cable GlandsDocument14 pagesCable GlandsSACHINNo ratings yet

- Repair and Service Manual TXT 48V: Electric Powered Golf CarDocument192 pagesRepair and Service Manual TXT 48V: Electric Powered Golf Carmg victorNo ratings yet

- H61MXV/H67MXV Series Motherboard: Downloaded From Manuals Search EngineDocument112 pagesH61MXV/H67MXV Series Motherboard: Downloaded From Manuals Search EnginejaramillosterNo ratings yet

- Rs46 Series Technical GuideDocument16 pagesRs46 Series Technical Guideabdelhadi houssinNo ratings yet

- Analysis of The Indian Maintenance Center For WAG-9 Electric Locomotives and Improve For New Railways ServiceDocument45 pagesAnalysis of The Indian Maintenance Center For WAG-9 Electric Locomotives and Improve For New Railways Service2251 EE MANMAT BIRADARNo ratings yet

- Allison Transmission 30004000 Series Fault Code List - Download PDF Manual PDFDocument10 pagesAllison Transmission 30004000 Series Fault Code List - Download PDF Manual PDFasdrubal laraNo ratings yet

- Iveco Stralis Ebs2 Repair ManualDocument128 pagesIveco Stralis Ebs2 Repair ManualGoran Malisic100% (1)

- Chapter 2 - Fuel Supply SystemDocument14 pagesChapter 2 - Fuel Supply SystemLalith Koushik GanganapalliNo ratings yet

- Inductance and Capacitance Meter Adapter Using 74HC132Document6 pagesInductance and Capacitance Meter Adapter Using 74HC132Miguelangel Bravo MigoneNo ratings yet

- Electrical Safety EarthingDocument4 pagesElectrical Safety Earthingجلال محسنNo ratings yet

- Assignment 4 SuspensionDocument3 pagesAssignment 4 SuspensionAdam LuqmanNo ratings yet

- Review of The Newly Released ASME BPVC Section XIII Overpressure ProtectionDocument32 pagesReview of The Newly Released ASME BPVC Section XIII Overpressure ProtectionDan TompknsNo ratings yet

- As Flexible and Logical As You Want It. Make The Most Of: Your TimeDocument52 pagesAs Flexible and Logical As You Want It. Make The Most Of: Your TimeTomasPavlovicNo ratings yet

- Medium Voltage SubstationsDocument5 pagesMedium Voltage SubstationsAnh Tú NguyễnNo ratings yet

- Earthing System and Protection in LV Installations - Vol-1 - Basics of Earthing SystemDocument76 pagesEarthing System and Protection in LV Installations - Vol-1 - Basics of Earthing SystemGhhNo ratings yet

- Park Compact 16 13-6103-19Document2 pagesPark Compact 16 13-6103-19Oana OanaNo ratings yet

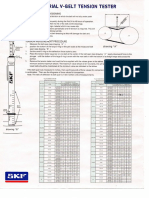

- Tabla de Fuerzas Medidor de Tensión de FajasDocument1 pageTabla de Fuerzas Medidor de Tensión de Fajasmatrix1x100% (1)

- 5PX Datasheet Low PDFDocument2 pages5PX Datasheet Low PDFJoe DoeNo ratings yet

- F932 Engine PDFDocument172 pagesF932 Engine PDFNick MontanoNo ratings yet

- To The Digital Storage Oscilloscope (Dso) : A Consulab PresentationDocument28 pagesTo The Digital Storage Oscilloscope (Dso) : A Consulab Presentationala100% (3)