Professional Documents

Culture Documents

Pa340u A

Uploaded by

AriNetoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Pa340u A

Uploaded by

AriNetoCopyright:

Available Formats

PA340 PA340

PA340

High Voltage Power Operational Amplifier

FEATURES DESCRIPTION

♦ RoHS COMPLIANT The PA340 is a high voltage monolithic MOSFET oper-

♦ MONOLITHIC MOS TECHNOLOGY ational amplifier achieving performance features previ-

♦ LOW COST ously found only in hybrid designs while increasing re-

liability. Inputs are protected from excessive common

♦ HIGH VOLTAGE OPERATION – 350V

mode and differential mode voltages. The safe operat-

♦ LOW QUIESCENT CURRENT TYP. – 2.2mA ing area (SOA) has no second breakdown limitations.

♦ NO SECOND BREAKDOWN External compensation provides the user flexibility in

♦ HIGH OUTPUT CURRENT – 120 mA PEAK choosing optimum gain and bandwidth for the applica-

tion.

APPLICATIONS The surface mount package of the PA340CC is an in-

♦ TELEPHONE RING GENERATOR dustry standard non-hermetic plastic 7-pin DDPAK.

♦ PIEZO ELECTRIC POSITIONING

♦ ELECTROSTATIC TRANSDUCER &

DEFLECTION

♦ DEFORMABLE MIRROR FOCUSING

♦ PACKAGING OPTIONS

7-pin DDPAK Surface Mount Package (PA340CC)

FIGURE 1: Equivalent Schematic

3

+VS

D1

Q1

Q2

Q3 I OUT

5

Q4 Q5

1 6 Q6

–IN COMP

D2 D3 D4 D5 COMP Q8

2 7

+IN

Q11 Q10

Q12 Q13

Q14

–VS

4

SUB

Copyright © Cirrus Logic, Inc. 2011 JUL 2011

PA340U (All Rights Reserved) 1

www.cirrus.com APEX - PA340UREVA

Downloaded from Arrow.com.

PA340

High voltage considerations should be taken when designing board layouts for the PA340. The PA340 may require a

derate in supply voltage depending on the spacing used for board layout. The 14-mil minimum spacing of the 7-pin

DDPAK is adequate to standoff the 350V rating of the PA340. However, a supply voltage derate to 250V is required

if the spacing of circuit board artwork is less than 11 mils.

The metal tab of the PA340CC package is directly tied to -Vs.

PA340CX

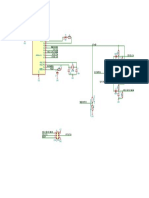

TYPICAL APPLICATION

PA340CC

A A

1 1

DDPAK

PKG. STYLE CC

-IN

+IN

+Vs

-Vs

OUT

COMP (Cc)

COMP (Cc)

For CC values, see graph on page 4.

-IN

+IN

+Vs

-Vs

OUT

COMP (Cc)

COMP (Cc)

Note: CC must be rated for full supply voltage.

FIGURE 2. External Connections.

Ref: APPLICATION NOTE 20: "Bridge Mode Operation of Power Amplifiers"

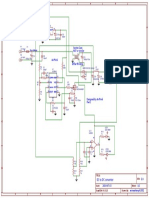

Two PA340 amplifiers operated as a bridge driver for a piezo transducer provides a low cost 660 volt total drive

capability. The RN CN network serves to raise the apparent gain of A2 at high frequencies. If RN is set equal to R the

amplifiers can be compensated identically and will have matching bandwidths.

R 20R 20R

20R

VIN

+175

+175

CC CC

10pF 10pF

A1 A2

PA340 PA340 RN

PIEZO

TRANSDUCER CN

LOW COST 660V p-p

PIEZO DRIVER

–175 –175

FIGURE 3. Low Cost 660VP-P Piezo Driver

2 PA340U

Downloaded from Arrow.com.

PA340

1. CHARACTERISTICS AND SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Min Max Units

SUPPLY VOLTAGE, +VS to -VS 350 V

OUTPUT CURRENT, continuous within SOA 60 mA

OUTPUT CURRENT, peak (Note 3) 120 mA

POWER DISSIPATION, continuous @ TC = 25°C 14 W

INPUT VOLTAGE, differential -16 +16 V

INPUT VOLTAGE, common mode -VS +VS V

TEMPERATURE, pin solder - 10 sec 220 °C

TEMPERATURE, junction (Note 2) 150 °C

TEMPERATURE, storage -65 150 °C

TEMPERATURE RANGE, powered (case) -40 125 °C

SPECIFICATIONS (PER AMPLIFIER)

Parameter Test Conditions (Note 1) Min Typ Max Units

INPUT

OFFSET VOLTAGE, initial 12 40 mV

OFFSET VOLTAGE, vs. temperature

25°C to 85°C 17 250 µV/°C

(Note 3)

OFFSET VOLTAGE, vs. temperature

-25°C to 25°C 18 500 µV/°C

(Note 3)

OFFSET VOLTAGE, vs. supply 4.5 µV/V

OFFSET VOLTAGE, vs. time 80 µV/kh

BIAS CURRENT, initial 50 200 pA

BIAS CURRENT, vs. supply 2 pA/V

OFFSET CURRENT, initial 50 200 pA

INPUT IMPEDANCE, DC 1011 Ω

INPUT CAPACITANCE 3 pF

COMMON MODE, voltage range +VS - 12 V

COMMON MODE, voltage range -VS + 12 V

COMMON MODE REJECTION, DC VCM = ±

90VDC 84 115 dB

NOISE, broad band 10kHz BW, RS = 1KΩ 337 µV RMS

GAIN

OPEN LOOP at 15Hz RL = 5KΩ 90 103 dB

GAIN BANDWIDTH PRODUCT @1MHz 10 MHz

POWER BANDWIDTH 280V p-p 35 kHz

PA340U 3

Downloaded from Arrow.com.

PA340

Parameter Test Conditions (Note 1) Min Typ Max Units

OUTPUT

VOLTAGE SWING IO = 40mA ±VS - 12 ±VS - 10 V

CURRENT, peak (Note 3) 120 mA

CURRENT, continuous 60 mA

SETTLING TIME to 0.1% 10V step, A V = -10 2 µs

SLEW RATE CC = 4.7pF 32 V/µS

RESISTANCE, 10mA (Note 4) RCL = 0Ω 91 Ω

RESISTANCE, 40mA (Note 4) RCL = 0Ω 65 Ω

POWER SUPPLY

VOLTAGE ±10 ±150 ±175 V

CURRENT, quiescent 2.2 2.5 mA

THERMAL

RESISTANCE, AC junction to case F > 60Hz 5.9 6.85 °C/W

RESISTANCE, DC junction to case F < 60Hz 7.7 8.9 °C/W

RESISTANCE, junction to air

Full temperature range 27 °C/W

(Note 5)

TEMPERATURE RANGE, case Meets full range specifications -25 25 +85 °C

NOTES:

1. Unless otherwise noted TC = 25°C, CC = 6.8pF. DC input specifications are ± value given. Power sup-

ply voltage is typical rating.

2. Long term operation at the maximum junction temperature will result in reduced product life. Derate

internal power dissipation to achieve high MTTF. For guidance, refer to heatsink data sheet.

3. Guaranteed but not tested.

4. Since the PA340 has no current limit, load impedance must be large enough to limit output current to

120mA.

5. Heat tab attached to 3/32" FR-4 board with 2oz. copper. Topside copper area (heat tab directly at-

tached) = 1000 sq. mm, backside copper area = 2500 sq. mm, board area = 2500 sq. mm.

CAUTION The PA340 is constructed from MOSFET transistors. ESD handling procedures must be observed.

4 PA340U

Downloaded from Arrow.com.

PA340

2. TYPICAL PERFORMANCE GRAPHS

POWER DERATING VBE for ILIMIT GAIN AND COMPENSATION

INTERNAL POWER DISSIPATION, P(W)

16 30 100

14 VDROP+@85°C 125°C

25 85°C

COMPENSATION, pF

VDROP FROM VS, (V)

12

20 10

10 VDROP-@85°C

25°C

8 15 55°C

6 VDROP-@27°C

10 1

4

5

2 VDROP+@27°C

0 0 0.1

0 25 50 75 100 125 0 20 40 60 80 100 120 0.1 1 10

TEMPERATURE, T (°C) OUTPUT CURRENT, IO (mA) GAIN

SMALL SIGNAL RESPONSE PHASE RESPONSE POWER RESPONSE

-80 1000

OUTPUT VOLTAGE, (VOUT) (p-p)

100 -90 68pF

OPEN LOOP GAIN, A (dB)

0.75pF -100 2.2pF

80 0.75pF

-110 6.8pF

PHASE, Φ (°)

60 2.2pF 2.2pF

-120 15pF

6.8pF -130 6.8pF 100

40 33pF

15pF -140 68pF

20 -150 15pF

68pF

-160

0

-170

-20 -180 10

10 100 1K 10K 100K 1M 10M 10K 100K 1M 10M 10K 100K 1M

FREQUENCY, F (Hz) FREQUENCY, F (Hz) FREQUENCY, F (Hz)

HARMONIC DISTORTION SLEW RATE QUIESCENT CURRENT

NORMALIZED QUIESCENT CURRENT, IQ (%)

10

30 102

DISTORTION, (%)

1

SLEW RATE, (V/µs)

30VP-P FALL

60VP-P 20 100 5°C

12

0.1 180V C

P-P

25°

RISE

10 98 °C

0.01 A V = 20 -40

C C = 15pF

R L = 2K

0.001 0 96

100 1K 10K 100K 5 15 25 35 45 55 65 75 85 20 60 100 140 180 220 260 300 340

FREQUENCY, F (Hz) COMPENSATION CAPACITANCE, CC (pF) TOTAL SUPPLY VOLTAGE, (V)

COMMON MODE REJECTION POWER SUPPLY REJECTION

120 100

COMMON MODE REJECTION, CMR (dB)

POWER SUPPLY REJECTION, PSR (dB)

100 90 POSITIVE

80 80

60 70 NEGATIVE

40 60

20 50

0 40

10 100 1K 10K 100K 10 100 1K 10K 100K

FREQUENCY, F (Hz) FREQUENCY, F (Hz)

PA340U 5

Downloaded from Arrow.com.

PA340

3. APPLICATION INFORMATION

Please read Application Note 1 "General Operating Considerations" which covers stability, power supplies, heat

sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit www.Cirrus.com for design

tools that help automate tasks such as calculations for stability, internal power dissipation, current limit, heat sink

selection, Apex Precision Power's complete Application Notes library, Technical Seminar Workbook and Evaluation

Kits.

3.1 PHASE COMPENSATION

Open loop gain and phase shift both increase with increasing temperature. The PHASE COMPENSATION typical

graph shows closed loop gain and phase compensation capacitor value relationships for four case temperatures.

The curves are based on achieving a phase margin of 50°. Calculate the highest case temperature for the applica-

tion (maximum ambient temperature and highest internal power dissipation) before choosing the compensation.

Keep in mind that when working with small values of compensation, parasitics may play a large role in performance

of the finished circuit. The compensation capacitor must be rated for at least the total voltage applied to the amplifier

and should be a temperature stable type such as NPO or COG.

3.2 OTHER STABILITY CONCERNS

There are two important concepts about closed loop gain when choosing compensation. They stem from the fact

that while "gain" is the most commonly used term, β (the feedback factor) is really what counts when designing for

stability.

1. Gain must be calculated as a non-inverting circuit (equal input and feedback resistors can provide a signal gain

of -1, but for calculating offset errors, noise, and stability, this is a gain of 2).

2. Including a feedback capacitor changes the feedback factor or gain of the circuit. Consider RIN = 4.7k, Rf = 47k

for a gain of 11. Compensation of 4.7 to 6.8pF would be reasonable. Adding 33pF parallel to the 47K rolls off the

circuit at 103kHz, and at 2MHz has reduced gain from 11 to roughly 1.5 and the circuit is likely to oscillate.

As a general rule the DC summing junction impedance (parallel combination of the feedback resistor and all input

resistors) should be limited to 5K ohms or less. The amplifier input capacitance of about 6pF, plus capacitance of

connecting traces or wires and (if used) a socket will cause undesirable circuit performance and even oscillation if

these resistances are too high. In circuits requiring high resistances, measure or estimate the total sum point ca-

pacitance, multiply by RIN /Rf, and parallel Rf with this value. Capacitors included for this purpose are usually in the

single digit pF range. This technique results in equal feedback factor calculations for AC and DC cases. It does not

produce a roll off, but merely keeps β constant over a wide frequency range. Paragraph 6 of Application Note 19

details suitable stability tests for the finished circuit.

3.3 SAFE OPERATING AREA SOA

The MOSFET output stage of the PA340 is not limited by second 1.0

breakdown considerations as in bipolar output stages. However

OUTPUT CURRENT FROM +VS OR –VS, (A)

0.5

there are still three distinct limitations: 0.3 200mS

0.2

1. Voltage withstand capability of the transistors. 300mS

2. Current handling capability of the die metallization. 0.1

3. Temperature of the output MOSFETS. 0.05

DC, TC = 25°C

0.03

These limitations can be seen in the SOA (see Safe Operating Area 0.02

graphs). Note that each pulse capability line shows a constant power DC, TC = 85°C

0.01

level (unlike second breakdown limitations where power varies with

voltage stress). These lines are shown for a case temperature of 0.005

25°C. Pulse stress levels for other case temperatures can be calcu- 0.003

0.002

lated in the same manner as DC power levels at different tempera-

tures. The output stage is protected against transient flyback by the 0.001

10 20 30 50 100 200 300 500 1K

parasitic diodes of the output stage MOSFET structure. However, SUPPLY TO OUTPUT DIFFERENTIAL, VS - VO, (V)

for protection against sustained high energy flyback external fast-

recovery diodes must be used. FIGURE 4. Safe Operating Area

6 PA340U

Downloaded from Arrow.com.

PA340

3.4 HEATSINKING

The PA340CC 7-pin DDPAK surface mountable package has a large exposed integrated copper heatslug to which

the monolithic amplifier is directly attached. The PA340CC requires surface mount techniques of heatsinking. A sol-

der connection to a copper foil area as defined in Note 5 of Page 3 is recommended for circuit board layouts. This

may be adequate heatsinking but the large number of variables suggests temperature measurements to be made

on the top of the package. Do not allow the temperature to exceed 85°C.

3.5 OVERVOLTAGE PROTECTION

Although the PA340 can withstand differential input voltages up to 16V, in +Vs Z1

some applications additional external protection may be needed. Differen-

tial inputs exceeding 16V will be clipped by the protection circuitry. How-

ever, if more than a few milliamps of current is available from the overload -IN +Vs

source, the protection circuitry could be destroyed. For differential sources

above 16V, adding series resistance limiting input current to 1mA will pre- Q1 OUT

Q2

vent damage. Alternatively, 1N4148 signal diodes connected anti-parallel

across the input pins is usually sufficient. In more demanding applications

+IN

where bias current is important, diode connected JFETs such as 2N4416 -Vs

will be required. See Q1 and Q2 in Figure 5. In either case the differential

input voltage will be clamped to 0.7V. This is sufficient overdrive to produce

the maximum power bandwidth. Z2

-Vs

In the case of inverting circuits where the +IN pin is grounded, the diodes

FIGURE 5. Overvoltage Protection

mentioned above will also afford protection from excessive common mode

voltage. In the case of non-inverting circuits, clamp diodes from each input to each supply will provide protection.

Note that these diodes will have substantial reverse bias voltage under normal operation and diode leakage will

produce errors.

Some applications will also need over-voltage protection devices connected to the power supply rails. Unidirectional

zener diode transient suppressors are recommended. The zeners clamp transients to voltages within the power

supply rating and also clamp power supply reversals to ground. Whether the zeners are used or not the system

power supply should be evaluated for transient performance including power-on overshoot and power-off polarity

reversals as well as line regulation. See Z1 and Z2 in Figure 5.

CONTACTING CIRRUS LOGIC SUPPORT

For all Apex Precision Power product questions and inquiries, call toll free 800-546-2739 in North America.

For inquiries via email, please contact apex.support@cirrus.com.

International customers can also request support by contacting their local Cirrus Logic Sales Representative.

To find the one nearest to you, go to www.cirrus.com

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject

to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant

information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale

supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus

for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third

parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights,

copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives con-

sent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent

does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROP-

ERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED TO BE

SUITABLE FOR USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PROD-

UCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUS-

TOMER’S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF

MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE

CUSTOMER OR CUSTOMER’S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES,

BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL

LIABILITY, INCLUDING ATTORNEYS’ FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs, Apex Precision Power, Apex and the Apex Precision Power logo designs are trademarks of Cirrus Logic, Inc.

All other brand and product names in this document may be trademarks or service marks of their respective owners.

PA340U 7

Downloaded from Arrow.com.

You might also like

- OPA350 OPA2350 OPA4350: Micro Applications FeaturesDocument11 pagesOPA350 OPA2350 OPA4350: Micro Applications FeaturesNuno FilipeNo ratings yet

- That - DN140 (Verschoben) 5Document1 pageThat - DN140 (Verschoben) 5sdtrnkNo ratings yet

- 25W + 25W Stereo Class-D Amplifier 50W Mono in BTL: DescriptionDocument10 pages25W + 25W Stereo Class-D Amplifier 50W Mono in BTL: DescriptionJULIONo ratings yet

- MP44010 - r1.2 PFC Fuente 50 Pulgadas Jhon JairoDocument14 pagesMP44010 - r1.2 PFC Fuente 50 Pulgadas Jhon JairoAndres AlegriaNo ratings yet

- TI Current Loop Tiduao7Document26 pagesTI Current Loop Tiduao7Parasaram SrinivasNo ratings yet

- TA4558Document3 pagesTA4558isaiasvaNo ratings yet

- Using Mosfets and A Relay, This Electronic Load Can Operate in Both Current-And Voltage-Regulation ModesDocument1 pageUsing Mosfets and A Relay, This Electronic Load Can Operate in Both Current-And Voltage-Regulation ModesRick JordanNo ratings yet

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyDocument13 pages120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyNo ratings yet

- 741 Datasheet PDFDocument6 pages741 Datasheet PDFsamsul hadiNo ratings yet

- 100V - 100W Audio Amp with Mute/StandbyDocument13 pages100V - 100W Audio Amp with Mute/StandbyFrancisco BelchiorNo ratings yet

- 2019 Comba Indoor AntennaDocument7 pages2019 Comba Indoor AntennaClaudio Calabrese100% (1)

- Features Description: D D D DDocument25 pagesFeatures Description: D D D DDavid O'NeillNo ratings yet

- AN-1349 LM34910 Evaluation Board: User's GuideDocument5 pagesAN-1349 LM34910 Evaluation Board: User's GuiderolandseNo ratings yet

- U741 PDFDocument6 pagesU741 PDFFilipe SilvaNo ratings yet

- FAN7390 High-Current, High & Low-Side, Gate-Drive IC: Features DescriptionDocument14 pagesFAN7390 High-Current, High & Low-Side, Gate-Drive IC: Features DescriptionjoelpalzaNo ratings yet

- Low Power Quad Operational Amplifiers As324/324ADocument13 pagesLow Power Quad Operational Amplifiers As324/324APaulo ManuelNo ratings yet

- C4570C Nec 2Document11 pagesC4570C Nec 2cdeeman azdiNo ratings yet

- LM2903 LM393 LM393A LM293A - FairchildDocument9 pagesLM2903 LM393 LM393A LM293A - FairchildElectronicos CaldasNo ratings yet

- TDA7293Document12 pagesTDA7293Radulescu LucianNo ratings yet

- That - DN140 (Verschoben) 2Document1 pageThat - DN140 (Verschoben) 2sdtrnkNo ratings yet

- 2A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterDocument18 pages2A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterCesarS100% (1)

- Bcd Semiconductor Manufacturing Limited As339a 245eb9e162Document11 pagesBcd Semiconductor Manufacturing Limited As339a 245eb9e162yannick audrey simeni youmessiNo ratings yet

- Diodes GP4504MTR G1Document15 pagesDiodes GP4504MTR G1Jose Luis ValduezaNo ratings yet

- TDA7295S: 80V - 80W Dmos Audio Amplifier With Mute/St-ByDocument13 pagesTDA7295S: 80V - 80W Dmos Audio Amplifier With Mute/St-ByLucio DeschiNo ratings yet

- 25W Mono Class-D Amplifier: DescriptionDocument6 pages25W Mono Class-D Amplifier: DescriptionGiovanni BiancaNo ratings yet

- General-Purpose Single Operational Amplifier: FeaturesDocument11 pagesGeneral-Purpose Single Operational Amplifier: FeaturesGabrielNo ratings yet

- STMicroelectronics UA741CN Datasheet PDFDocument11 pagesSTMicroelectronics UA741CN Datasheet PDFAlina ȘtefănesiNo ratings yet

- CA3450Document8 pagesCA3450MUHAMMAD SISWANTORONo ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: Features General DescriptionDocument5 pagesSynchronous-Rectified Buck MOSFET Drivers: Features General DescriptionTeles SilvaNo ratings yet

- VCC C3 D3 IC1 R9 330 1u Thermistor PowerDocument1 pageVCC C3 D3 IC1 R9 330 1u Thermistor PowermicNo ratings yet

- OPA340NA 250 Texas Instruments Datasheet 8442867Document21 pagesOPA340NA 250 Texas Instruments Datasheet 8442867Zakaria Al SharabiNo ratings yet

- High Efficiency 2A, 36V, Synchronous Step Down Converter: The Future of Analog IC TechnologyDocument20 pagesHigh Efficiency 2A, 36V, Synchronous Step Down Converter: The Future of Analog IC TechnologyAspire2222No ratings yet

- MP39 - MP39A: Power Operational AmplifierDocument14 pagesMP39 - MP39A: Power Operational AmplifierPtichkinNo ratings yet

- Features: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierDocument5 pagesFeatures: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierAlexandre Correa100% (1)

- DatasheetDocument20 pagesDatasheetDarya TelichkoNo ratings yet

- AS358P E1 BCD SemiconductorDocument15 pagesAS358P E1 BCD SemiconductorDesperado Manogaran MNo ratings yet

- Tonepad Tonebendermk2Document1 pageTonepad Tonebendermk2MiguelNo ratings yet

- Single Supply, Low Power Dual Comparators: Semiconductor Technical DataDocument6 pagesSingle Supply, Low Power Dual Comparators: Semiconductor Technical DataNick DNo ratings yet

- General Purpose Single Operational Amplifiers: DescriptionDocument9 pagesGeneral Purpose Single Operational Amplifiers: DescriptionDavid RiosNo ratings yet

- CDV700Pro Construction Tutorial PDFDocument33 pagesCDV700Pro Construction Tutorial PDFjuan9gonzalez_9No ratings yet

- TDA7293 Audio AMP - Data SheetDocument15 pagesTDA7293 Audio AMP - Data Sheetmilanbrkljaca.zdNo ratings yet

- 3A Ultra Low Dropout Linear Regulator: General Description FeaturesDocument11 pages3A Ultra Low Dropout Linear Regulator: General Description FeaturesdejanNo ratings yet

- Microphone Preamplifier Circuit DiagramDocument1 pageMicrophone Preamplifier Circuit DiagramSigg KeyoNo ratings yet

- Arduino Inverter230515Document3 pagesArduino Inverter230515Ibrahim Dalafika AbdullahiNo ratings yet

- Single Operational Amplifier: Features DescriptionDocument10 pagesSingle Operational Amplifier: Features DescriptionFranciscoNo ratings yet

- Single Operational Amplifier: Features DescriptionDocument10 pagesSingle Operational Amplifier: Features DescriptionChristianNo ratings yet

- Single Operational Amplifier: Features DescriptionDocument10 pagesSingle Operational Amplifier: Features DescriptionMiguel Angel Ariza HormecheaNo ratings yet

- LM358Document7 pagesLM358doni satriaNo ratings yet

- High Voltage Power Operational Amplifiers: FeaturesDocument13 pagesHigh Voltage Power Operational Amplifiers: FeaturesramswaruprewaniNo ratings yet

- Roland Funny Cat SchematicDocument4 pagesRoland Funny Cat SchematicGustavoTfLa100% (1)

- DC to DC converter circuitDocument1 pageDC to DC converter circuitHardik100% (1)

- MPPT Part 2 AviPrink PDFDocument1 pageMPPT Part 2 AviPrink PDFadmnrvNo ratings yet

- 3A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterDocument18 pages3A, 4.2V-16V Input, Fast Transient Synchronous Step-Down ConverterJuan C RiveraNo ratings yet

- BigmufpiDocument4 pagesBigmufpinene_guitarNo ratings yet

- Archive: DatasheetDocument11 pagesArchive: DatasheetSo Was RedNo ratings yet

- NCP1396A, NCP1396B Controller, High Performance Resonant Mode, With High and Low Side DriversDocument26 pagesNCP1396A, NCP1396B Controller, High Performance Resonant Mode, With High and Low Side DriversMaria VaccarielloNo ratings yet

- 74HCT9046A: 1. General DescriptionDocument43 pages74HCT9046A: 1. General DescriptionDanielNo ratings yet

- DB Ca04pa04Document2 pagesDB Ca04pa04AriNetoNo ratings yet

- DB Amplifier LinkDocument2 pagesDB Amplifier LinkAriNetoNo ratings yet

- DB - Ca03pa03 3Document2 pagesDB - Ca03pa03 3AriNetoNo ratings yet

- Vishay General Semiconductor: FeaturesDocument4 pagesVishay General Semiconductor: Featurestommy99No ratings yet

- TM Ca03Document17 pagesTM Ca03AriNetoNo ratings yet

- Unit 4: Microcontrollers (Arduino) Overview Digital I/ODocument60 pagesUnit 4: Microcontrollers (Arduino) Overview Digital I/OAriNetoNo ratings yet

- Sartorius LC / AC - Balances Service Manual: Sartorius AG, Weighing TechnologyDocument25 pagesSartorius LC / AC - Balances Service Manual: Sartorius AG, Weighing TechnologyAngelithox VargaxNo ratings yet

- Innovative Buck RegulatorDocument3 pagesInnovative Buck RegulatorAriNetoNo ratings yet

- Service Manual: CX501 CX501B CX501ADocument31 pagesService Manual: CX501 CX501B CX501AAriNetoNo ratings yet

- MOSFET Worksheet R2 PDFDocument2 pagesMOSFET Worksheet R2 PDFvladan.izbmNo ratings yet

- TTC5200 Datasheet en 20131101Document5 pagesTTC5200 Datasheet en 20131101Johnny Bances RiosNo ratings yet

- Education Manual: The Raspberry PiDocument137 pagesEducation Manual: The Raspberry Pidr7zyqNo ratings yet

- Education Manual: The Raspberry PiDocument137 pagesEducation Manual: The Raspberry Pidr7zyqNo ratings yet

- Service Manual: CX501 CX501B CX501ADocument31 pagesService Manual: CX501 CX501B CX501AAriNetoNo ratings yet

- Ucc 1801Document55 pagesUcc 1801AriNeto100% (1)

- Raspberry Pi Projects Book PDFDocument204 pagesRaspberry Pi Projects Book PDFstanchan82100% (1)

- KSB Hyamat VP LiteratureDocument48 pagesKSB Hyamat VP LiteratureMuhammad azeemNo ratings yet

- DC Inverter VRF Systems C VRFDocument50 pagesDC Inverter VRF Systems C VRFMd Saddam HossainNo ratings yet

- Kutai 75 Amp - AVR For Brush GeneratorsDocument1 pageKutai 75 Amp - AVR For Brush GeneratorsIbrahim Al-AssraNo ratings yet

- Conic Sections: Circles and Their EquationsDocument26 pagesConic Sections: Circles and Their EquationsJanet ComandanteNo ratings yet

- 1.9 Flyback Converter in DCM: Output PowerDocument4 pages1.9 Flyback Converter in DCM: Output PowerRakesh SutharNo ratings yet

- RFT Vs MDT Vs DSTDocument6 pagesRFT Vs MDT Vs DSTAbdullah IshaqNo ratings yet

- Tightening Torque of A Bolted Joint - MetricDocument2 pagesTightening Torque of A Bolted Joint - MetricgdwvcdNo ratings yet

- Explosive SC Penetration Into Tuff RockDocument69 pagesExplosive SC Penetration Into Tuff RockBAYE JBPNo ratings yet

- Reynolds Experiment PDFDocument8 pagesReynolds Experiment PDFali najatNo ratings yet

- Molecular Dynamics Simulations of Atomic Diffusion During The Al-Cu Ultrasonic Welding ProcessDocument11 pagesMolecular Dynamics Simulations of Atomic Diffusion During The Al-Cu Ultrasonic Welding ProcessftiraNo ratings yet

- Annex-04 Turbosan NORM End Suction Erection ProcedureDocument31 pagesAnnex-04 Turbosan NORM End Suction Erection ProcedureEngr.Muhammad ObaidullahNo ratings yet

- Zn-Mg-Al Corrosion analysis paperDocument12 pagesZn-Mg-Al Corrosion analysis paperrahul.meenaNo ratings yet

- Designing Forming Fabrics for Optimum Papermaking PerformanceDocument6 pagesDesigning Forming Fabrics for Optimum Papermaking PerformanceLev BNo ratings yet

- Special Relativity: 1 The Invariant IntervalDocument8 pagesSpecial Relativity: 1 The Invariant IntervalBrunoNo ratings yet

- Lectur2 SCDocument35 pagesLectur2 SCbouk omraNo ratings yet

- Spray Drying of Fruit and Vegetable Juices - A ReviewDocument66 pagesSpray Drying of Fruit and Vegetable Juices - A ReviewTantry Eko PutriNo ratings yet

- Heat Exchanger DesignDocument83 pagesHeat Exchanger DesignPhượng NguyễnNo ratings yet

- Kabelmetal NYYDocument1 pageKabelmetal NYYDudi MulyadiNo ratings yet

- How Trust Impacts Organizational Learning and InnovationDocument14 pagesHow Trust Impacts Organizational Learning and Innovationerika31123100% (1)

- Charpit's Method for Solving Nonlinear PDEsDocument23 pagesCharpit's Method for Solving Nonlinear PDEsManpreet Singh68% (31)

- Artists' Pastels: Standard Specification ForDocument5 pagesArtists' Pastels: Standard Specification ForPyone Ei ZinNo ratings yet

- Physics Investigatory Project - Safa Azeem Zaina 2Document18 pagesPhysics Investigatory Project - Safa Azeem Zaina 2Reshma Mahjabeen100% (3)

- Cellulose Nanocrystals Obtained From Office Waste PaperDocument41 pagesCellulose Nanocrystals Obtained From Office Waste PaperAlexander Estrada OrtizNo ratings yet

- MCQ in Differential Calculus (Limits and Derivatives) Part 1 - Math Board ExamDocument13 pagesMCQ in Differential Calculus (Limits and Derivatives) Part 1 - Math Board ExamAF Xal RoyNo ratings yet

- Concentration of SolutionsDocument42 pagesConcentration of SolutionsAien RonquilloNo ratings yet

- VSEPRDocument14 pagesVSEPRagraharirajiv33No ratings yet

- UN 5000 User's Manual: CommissioningDocument13 pagesUN 5000 User's Manual: CommissioningAmit BiswasNo ratings yet

- HMT Tutorial 1Document3 pagesHMT Tutorial 1mofoNo ratings yet

- Physics Multiple Choice QuestionsDocument8 pagesPhysics Multiple Choice QuestionsPranav AgrawalNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : Quad Smart Power Solid State Relay For Complete H-Bridge ConfigurationsDocument33 pagesObsolete Product(s) - Obsolete Product(s) : Quad Smart Power Solid State Relay For Complete H-Bridge Configurationsmarino246No ratings yet