Professional Documents

Culture Documents

U6264ADC Datasheet Download at Https

Uploaded by

Nadir CebiyevOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

U6264ADC Datasheet Download at Https

Uploaded by

Nadir CebiyevCopyright:

Available Formats

U6264A

Standard 8K x 8 SRAM

Features p ESD protection > 2000 V DQ0 - DQ7. After the address

(MIL STD 883C M3015.7) change, the data outputs go High-Z

p 8192 x 8 bit static CMOS RAM p Latch-up immunity > 100 mA until the new read information is

p 70 and 100 ns Access Times p Packages: PDIP28 (600 mil) available. The data outputs have no

p Common data inputs and SOP28 (300 mil) preferred state. If the memory is

outputs SOP28 (330 mil) driven by CMOS levels in the active

p Three-state outputs state, and if there is no change of

p Typ. operating supply current Description the address, data input and control

70 ns: 45 mA signals W or G, the operating cur-

100 ns: 37 mA The U6264A is a static RAM manu- rent (at IO = 0 mA) drops to the

p Data retention current factured using a CMOS process value of the operating current in the

at 3 V: < 10 µA (standard) technology with the following ope- Standby mode. The Read cycle is

p Standby current standard < 30 µA rating modes: finished by the falling edge of E2 or

p Standby current low power - Read - Standby W, or by the rising edge of E1,

(L) < 10 µA - Write - Data Retention respectively.

p Standby current very low power The memory array is based on a Data retention is guaranteed down

(LL) < 1 µA 6-transistor cell. to 2 V. With the exception of E2, all

p Standby current for LL-version The circuit is activated by the rising inputs consist of NOR gates, so that

at 25 °C and 5 V: typ. 50 nA edge of E2 (at E1 = L), or the falling no pull-up/pull-down resistors are

p TTL/CMOS-compatible edge of E1 (at E2 = H). The required. This gate circuit allows to

p Automatic reduction of power address and control inputs open achieve low power standby require-

dissipation in long Read or Write simultaneously. According to the ments by activation with TTL-levels

cycles information of W and G, the data too.

p Power supply voltage 5 V inputs, or outputs, are active. If the circuit is inactivated by

p Operating temperature ranges: During the active state (E1 = L and E2 = L, the standby current (TTL)

0 to 70 °C E2 = H), each address change drops to 150 µA typ.

-25 to 85 °C leads to a new Read or Write cycle.

-40 to 85 °C In a Read cycle, the data outputs

p Quality assessment according to are activated by the falling edge of

CECC 90000, CECC 90100 and G, afterwards the data word read

CECC 90111 will be available at the outputs

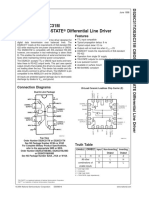

Pin Configuration Pin Description

n.c. 1 28 VCC

A12 2 27 W (WE)

A7 3 26 E2 (CE2)

A6 4 25 A8 Signal Name Signal Description

A5 5 24 A9 A0 - A12 Address Inputs

A4 6 23 A11 DQ0 - DQ7 Data In/Out

A3 7 PDIP 22 G (OE)

E1 Chip Enable 1

A2 8 SOP 21 A10

E2 Chip Enable 2

A1 9 20 E1 (CE1)

G Output Enable

A0 10 19 DQ7

W Write Enable

DQ0 11 18 DQ6

VCC Power Supply Voltage

DQ1 12 17 DQ5

DQ2 16 VSS Ground

13 DQ4

VSS 14 15 n.c. not connected

DQ3

Top View

December 12, 1997 1

This datasheet can be found on https://www.jotrin.com

U6264A

Block Diagram

A4

Row Decoder

Row Address

A5 Memory Cell

A6 Array

Inputs

A7

A8 256 Rows x

A9 256 Columns

A11

A12

Column Decoder

Column Address

A0

A1

Inputs

A2 DQ0

A3 Sense Amplifier/ DQ1

Common Data I/O

Write Control Logic

A10 DQ2

DQ3

DQ4

Address DQ5

Change Clock

Generator DQ6

Detector

DQ7

E2 VCC VSS W G

1

E1

Truth Table

Operating Mode E1 E2 W G DQ0 - DQ7

Standby/not * L * * High-Z

selected H * * * High-Z

Internal Read L H H H High-Z

Read L H H L Data Outputs Low-Z

Write L H L * Data Inputs High-Z

* H or L

Characteristics

All voltages are referenced to V SS = 0 V (ground).

All characteristics are valid in the power supply voltage range and in the operating temperature range specified.

Dynamic measurements are based on a rise and fall time of ≤ 5 ns, measured between 10 % and 90 % of V I, as well as

input levels of V IL = 0 V and VIH = 3 V. The timing reference level of all input and output signals is 1.5 V,

with the exception of the tdis -times, in which cases transition is measured ± 200 mV from steady-state voltage.

Maximum Ratings Symbol Min. Max. Unit

Power Supply Voltage V CC -0.3 7 V

Input Voltage VI -0.3 VCC + 0.5 V

Output Voltage VO -0.3 VCC + 0.5 V

Power Dissipation PD - 1 W

Operating Temperature C-Type Ta 0 70 °C

G-Type -25 85 °C

K-Type -40 85 °C

Storage Temperature Tstg -55 125 °C

2 December 12, 1997

U6264A

Recommended

Symbol Conditions Min. Max. Unit

Operating Conditions

Power Supply Voltage VCC 4.5 5.5 V

Data Retention Voltage V CC(DR) 2.0 V

Input Low Voltage* VIL -0.3 0.8 V

Input High Voltage VIH 2.2 VCC + 0.3 V

* -2 V at Pulse Width 10 ns

Electrical Characteristics Symbol Conditions Min. Max. Unit

Supply Current - Operating Mode ICC(OP) VCC = 5.5 V

VIL = 0.8 V

VIH = 2.2 V

Standard tcW = 70 ns 70 mA

tcW = 100 ns 60 mA

Low Power (L) tcW = 70 ns 70 mA

tcW = 100 ns 60 mA

Very Low Power (LL) tcW = 70 ns 55 mA

tcW = 100 ns 45 mA

Supply Current - Standby Mode ICC(SB) VCC = 5.5 V

(CMOS level) VE1 = VE2 = VCC - 0.2 V

or VE2 = 0.2 V

Standard 30 µA

Low Power (L) 10 µA

Very Low Power (LL) 1 µA

Supply Current - Standby Mode ICC(SB)1 VCC = 5.5 V

(TTL level) VE1 = VE2 = 2.2 V

or VE2 = 0.2 V

Standard 5 mA

Low Power (L) 5 mA

Very Low Power (LL) 3 mA

Supply Current - Data Retention ICC(DR) VCC(DR) = 3V

Mode VE1 = VE2 = VCC(DR) - 0.2 V

or VE2 = 0.2 V

Standard 10 µA

Low Power (L) 10 µA

Very Low Power (LL) 1 µA

December 12, 1997 3

U6264A

Electrical Characteristics Symbol Conditions Min. Max. Unit

Output High Voltage VOH VCC = 4.5 V 2.4 V

IOH = -1.0 mA

Output Low Voltage VOL VCC = 4.5 V 0.4 V

IOL = 3.2 mA

Input Leakage Current

Standard &

Low Power (L) High IIH VCC = 5.5 V 2 µA

VIH = 5.5 V

Low IIL VCC = 5.5 V -2 µA

VIL = 0V

Very Low Power (LL) High IIH VCC = 5.5 V 1 µA

VIH = 5.5 V

Low IIL VCC = 5.5 V -1 µA

VIL = 0V

Output High Current IOH VCC = 4.5 V -1 mA

VOH = 2.4 V

Output Low Current IOL VCC = 4.5 V 3.2 mA

VOL = 0.4 V

Output Leakage Current

Standard &

Low Power (L)

High at Three-State Outputs IOHZ VCC = 5.5 V 2 µA

VOH = 5.5 V

Low at Three-State Outputs IOLZ VCC = 5.5 V -2 µA

VOL = 0V

Very Low Power (LL)

High at Three-State Outputs IOHZ VCC = 5.5 V 1 µA

VOH = 5.5 V

Low at Three-State Outputs IOLZ VCC = 5.5 V -1 - µA

VOL = 0V

4 December 12, 1997

U6264A

Symbol Min. Max. Unit

Switching Characteristics

Alt. IEC 07 10 07 10

Time to Output in Low-Z t LZ tt(QX) 5 5 10 10 ns

Cycle Time

Write Cycle Time tWC tcW 70 100 ns

Read Cycle Time tRC tcR 70 100 ns

Access Time

E1 LOW or E2 HIGH to Data Valid tACE ta(E) - - 70 100 ns

G LOW to Data Valid tOE ta(G) - - 40 50 ns

Address to Data Valid tAA ta(A) - - 70 100 ns

Pulse Widths

Write Pulse Width tWP tw(W) 50 70 ns

Chip Enable to End of Write tCW tw(E) 65 90 ns

Setup Times

Address Setup Time tAS tsu(A) 0 0 ns

Chip Enable to End of Write tCW tsu(E) 65 90 ns

Write Pulse Width tWP tsu(W) 50 70 ns

Data Setup Time tDS tsu(D) 35 40 ns

Data Hold Time tDH th(D) 0 0 ns

Address Hold from End of Write tAH th(A) 0 0 ns

Output Hold Time from Address tOH tv(A) 5 5 ns

Change

E1 HIGH or E2 LOW to Output in tHZCE tdis(E) 0 0 25 35 ns

High-Z

W LOW to Output in High-Z tHZWE tdis(W) 0 0 30 35 ns

G HIGH to Output in High-Z tHZOE tdis(G) 0 0 25 35 ns

Data Retention Mode E1-Controlled Data Retention Mode E2-Controlled

VCC VCC

4.5 V 4.5 V

VCC(DR) ≥ 2 V VCC(DR) ≥ 2 V

E2

2.2 V 2.2 V tDR Data Retention trec

tDR Data Retention trec E1

0.8 V VE2(DR) ≤ 0.2 V 0.8 V

0V 0

VE2(DR) ≥ VCC(DR) - 0.2 V or VE2(DR) ≤ 0.2 V

V CC(DR) - 0.2 V ≤ VE1(DR) ≤ VCC(DR) + 0.3 V

Chip Deselect to Data Retention Time tDR: min 0 ns

Operating Recovery Time trec: min tcR

December 12, 1997 5

U6264A

Test Configuration for Functional Check

5V

A0 VCC

A1

A2

A3 DQ0

A4

Input level according to the

relevant test measurement

DQ1 960

ment of all 8 output pins

Simultaneous measure-

VIH A5 DQ2

A6 DQ3

A7 DQ4

A8 DQ5

A9 DQ6

VIL A10 DQ7

A11 VO

A12

E1 30 pF1)

E2

W 510

G VSS

1) In measurement of tdis(E), tdis(W), tdis(G) the capacitance is 5 pF.

Capacitance Conditions Symbol Min. Max. Unit

VCC = 5.0 V

Input Capacitance CI 8 pF

VI = VSS

f = 1 MHz

Output Capacitance CO 10 pF

Ta = 25 °C

All pins not under test must be connected with ground by capacitors.

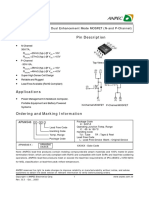

IC Code Numbers

Example

U6264A D G 07 L

Type

Package Internal Code

D = PDIP

S = SOP (330 mil)

S1 = SOP (300 mil)

Operating Temperature Range Power Consumption

C = 0 to 70 °C = Standard

G = -25 to 85 °C L = Low Power

K = -40 to 85 °C Access Time LL = Very Low Power

07 = 70 ns

10 = 100 ns

The date of manufacture is given by the last 4 digits of the mark, the first 2 digits indicating the year, and the last 2

digits the calendar week.

6 December 12, 1997

U6264A

Read Cycle 1 (during Read cycle: E1 = G = VIL, E2 = W = VIH)

tcR

Ai Addresses Valid

ta(A )

AAAAAAAAAAA AAAAAAA

DQi Previous

Data Valid

AAAA

AAAAAAAA

AAAAAAA

AAA

Output Data

Valid

AAAA

AAAAAAA

AAA

Output

tv(A ) AAAAAAAAAAA AAAAAAA

Read Cycle 2 (during Read cycle: W = VIH)

tcR

Ai Addresses Valid

tsu(A) ta(E)

tt(QX )

E1 tdis(E)

ta(E)

tsu(A)

tdis(E)

E2 tt(QX)

ta(G)

G tdis(G)

tt(QX)

DQi High-Z AAAA

AAAAAAAA

AAAAAAA

AAA Output Data

Output AAAA

AAAAAAAA

AAAAAAA

AAA Valid

Write Cycle 1 (W-controlled)

tcW

Ai Addresses Valid

tsu(E) th(A)

AAAA

AAAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAA

AA AAAA

AAAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA

AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAA

AAAA

E1 AA AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA

tsu(E)

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAA AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA

E2 AAAA

AAAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAA

AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA

tsu(A) tw(W)

W

tsu(D) th(D)

DQi Input Data

Input Valid

tdis(W)

tt(QX )

AAAA AAAA

DQi High-Z AAAA AAAAAAA

AAA

AAAA

Output AAAAAAAA

AAAAAAA

AAA

AAAA

AAAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA

G AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA

December 12, 1997 7

U6264A

Write Cycle 2 (E1-controlled)

tcW

Ai Addresses Valid

tsu(A) tw(E) th(A )

E1

tsu(E)

AAAAAAAAAAA AAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA

E2 AAAA

AAAAAAAA

AAAAAAA

AAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA

AAAAAAAAAAA AAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA

tsu(W)

AAAAAAAAAAAAAAAAAAA AAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA

W AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA

AAAAAAAAAAAAAAAAAAA tsu(D)

AAAAAAAAAAAA

t

AAAAAAAAAAAAAAAAAAAA

h(D)

DQi Input Data

Input tdis(W) Valid

tt(QX )

DQi High-Z

Output

AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA

G AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA

Write Cycle 3 (E2-controlled)

tcW

Ai Addresses Valid

tsu(E) th(A )

AAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA

E1 AAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA

tsu(A) tw(E)

E2

tsu(W)

AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA

W AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAA

tsu(D) th(D)

DQi Input Data

Input tdis(W) Valid

tt(QX )

DQi High-Z

Output

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA

G AAAA

AAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAAA

AAAAAAA

AAA

AAAA AAAA AAAA AA AAAA AAAA AAAA AA

AAAA

AAAA AAAA

AAAA AAAA

AAAA A AAAA

AAAA AAAA

AAAA AAAA

AAAA A

AAAA L- or H-level

AAAAAAAAAAAAAA

AAAA AAAA AAAA

AAAAAAAAAAAAAA

undefined AAAA AAAA

8 December 12, 1997

Memory Products 1998

Standard 8K x 8 SRAM U6264A

LIFE SUPPORT POLICY

ZMD products are not designed, intended, or authorized for use as components in

systems intend for surgical implant into the body, or other applications intended to

support or sustain life, or for any other application in which the failure of the ZMD

product could create a situation where personal injury or death may occur.

Components used in life-support devices or systems must be expressly authorized

by ZMD for such purpose.

The information describes the type of component and shall not be considered as

assured characteristics.

Terms of delivery and rights to change design reserved.

Zentrum Mikroelektronik Dresden GmbH

Grenzstraße 28 • D-01109 Dresden • P. O. B. 80 01 34 • D-01101 Dresden • Germany

Phone: +49 351 88 22-3 06 • Fax: +49 351 88 22-3 37 • Email: sales@zmd.de

Internet Web Site: http://www.zmd.de

You might also like

- U62H64SA: Automotive Fast 8K X 8 SRAMDocument8 pagesU62H64SA: Automotive Fast 8K X 8 SRAMAhmed Sherif CupoNo ratings yet

- U 6264 AsaDocument8 pagesU 6264 AsaJoil LeandroNo ratings yet

- UL62H256AS2ADocument11 pagesUL62H256AS2AJesus Maria LizarzabalNo ratings yet

- DS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentDocument9 pagesDS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentJoel PalzaNo ratings yet

- DS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentDocument9 pagesDS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentDiego SerranoNo ratings yet

- D D D D D D D: Description/ordering InformationDocument19 pagesD D D D D D D: Description/ordering InformationkarimNo ratings yet

- Ds1225ab Ds1225adDocument9 pagesDs1225ab Ds1225adMuhammad Jalal AldeenNo ratings yet

- sn74hc365 Ic PDFDocument18 pagessn74hc365 Ic PDFDanuu Goligat DhokaNo ratings yet

- Memoria Dallas DS1658Y-100Document11 pagesMemoria Dallas DS1658Y-100wilmer1973No ratings yet

- DS1245Y/AB 1024k Nonvolatile SRAM: Features Pin AssignmentDocument10 pagesDS1245Y/AB 1024k Nonvolatile SRAM: Features Pin Assignmentاحمد زغارىNo ratings yet

- DS1245Y/AB 1024k Nonvolatile SRAM: Features Pin AssignmentDocument3 pagesDS1245Y/AB 1024k Nonvolatile SRAM: Features Pin AssignmentDel ValleNo ratings yet

- 256K X 16 4Mb Asynchronous SRAMDocument14 pages256K X 16 4Mb Asynchronous SRAMThein Htoon lwinNo ratings yet

- DS 1225adDocument10 pagesDS 1225adJosé AdelinoNo ratings yet

- D D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsDocument25 pagesD D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsДрагиша Небитни ТрифуновићNo ratings yet

- Microcomputers, Inc.: RN ( FfirnwDocument4 pagesMicrocomputers, Inc.: RN ( FfirnwPrzemysław WójcikNo ratings yet

- MT 8816 AeDocument6 pagesMT 8816 AecubareNo ratings yet

- SN 74 LVTH 541Document11 pagesSN 74 LVTH 541api-3825669No ratings yet

- D D D D D D D D: Description/ordering InformationDocument19 pagesD D D D D D D D: Description/ordering InformationEzequiel AriasNo ratings yet

- Cat28f020p 12Document16 pagesCat28f020p 12Carlos MarquesNo ratings yet

- M5M51008CFP MitsubishiElectricSemiconductorDocument7 pagesM5M51008CFP MitsubishiElectricSemiconductorErasmo FrancoNo ratings yet

- 64-Bit TTL Bipolar RAM, Inverting (3-State) : Integrated CircuitsDocument10 pages64-Bit TTL Bipolar RAM, Inverting (3-State) : Integrated CircuitsEdher Hugo Morales EscobedoNo ratings yet

- EEPROM 24C256 - Atmel PDFDocument20 pagesEEPROM 24C256 - Atmel PDFValdir DerlannNo ratings yet

- Memory Interface Circuits 80x86 Processors: Ref: Online Course On EE-390, KFUPMDocument15 pagesMemory Interface Circuits 80x86 Processors: Ref: Online Course On EE-390, KFUPMMarcus QeqqrqrrqNo ratings yet

- DS1230Y/AB 256k Nonvolatile SRAM: Features Pin AssignmentDocument11 pagesDS1230Y/AB 256k Nonvolatile SRAM: Features Pin AssignmentCairineLopesNo ratings yet

- Discontinued Product: For Reference OnlyDocument5 pagesDiscontinued Product: For Reference OnlyahmedNo ratings yet

- U6264ASADocument8 pagesU6264ASAThong ChanNo ratings yet

- 96Khz 24bit Adc With Single-Ended Input: General DescriptionDocument17 pages96Khz 24bit Adc With Single-Ended Input: General Description邓建福No ratings yet

- W27C512Document16 pagesW27C512algnben1746No ratings yet

- D D D D: SN54ACT374, SN74ACT374 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsDocument22 pagesD D D D: SN54ACT374, SN74ACT374 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsMarta_d_eNo ratings yet

- TRM3 Com ARDETEM EN 1Document2 pagesTRM3 Com ARDETEM EN 1willvinNo ratings yet

- I C-Compatible Serial E Prom: General DescriptionDocument20 pagesI C-Compatible Serial E Prom: General Descriptionsajjad_pirzadaNo ratings yet

- DS26C31T/DS26C31M Cmos Quad Tri-State Differential Line DriverDocument14 pagesDS26C31T/DS26C31M Cmos Quad Tri-State Differential Line DriverdiegoNo ratings yet

- SC1531 Semtech CorporationDocument11 pagesSC1531 Semtech Corporation94430s19684No ratings yet

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument21 pagesTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64Anordio2No ratings yet

- CMOS Static RAM 16K (2K X 8-Bit) : Features DescriptionDocument13 pagesCMOS Static RAM 16K (2K X 8-Bit) : Features DescriptionTấn Long Đoàn NguyễnNo ratings yet

- SN 74 HCT 573Document20 pagesSN 74 HCT 573bvNo ratings yet

- 256 Kbit (32Kb x8) Parallel EEPROM With Software Data ProtectionDocument21 pages256 Kbit (32Kb x8) Parallel EEPROM With Software Data ProtectionvanmarteNo ratings yet

- Features Description: 1996 Burr-Brown Corporation PDS-1304B Printed in U.S.A. October, 1997Document16 pagesFeatures Description: 1996 Burr-Brown Corporation PDS-1304B Printed in U.S.A. October, 1997Hector Jose Murillo CordobaNo ratings yet

- Str-A6251 Str-A6252 PDFDocument7 pagesStr-A6251 Str-A6252 PDFrafalero1No ratings yet

- 3 V/5 V, 450 16-Bit, Sigma-Delta ADC AD7715 : A Max at 3 V SuppliesDocument31 pages3 V/5 V, 450 16-Bit, Sigma-Delta ADC AD7715 : A Max at 3 V SupplieshfalanizNo ratings yet

- Microprocessor: Based, Multipurpose, ProgrammableDocument61 pagesMicroprocessor: Based, Multipurpose, ProgrammableSiddhant MittalNo ratings yet

- UCN5810 DatasheetDocument7 pagesUCN5810 DatasheetkarimNo ratings yet

- Ds1245ab Ds1245yDocument11 pagesDs1245ab Ds1245yakeem alturkiNo ratings yet

- Atmel 8766 Seeprom At24cs04 08 Datasheet ATMLH236Document23 pagesAtmel 8766 Seeprom At24cs04 08 Datasheet ATMLH236berrumeNo ratings yet

- Write Protect Pin For Hardware Data ProtectionDocument16 pagesWrite Protect Pin For Hardware Data Protectionisc44242100% (2)

- Ka8603 Universal Speech Network: 16-DIP-300ADocument6 pagesKa8603 Universal Speech Network: 16-DIP-300AAdnanDeğerliyurtNo ratings yet

- DatasheetDocument12 pagesDatasheetKlan ZangoNo ratings yet

- At24c02a 04a 08aDocument16 pagesAt24c02a 04a 08aretno.endah ekowatiNo ratings yet

- ths5661 PDFDocument29 pagesths5661 PDFIqbal AchmadiNo ratings yet

- CAT28F010: Licensed Intel Second SourceDocument14 pagesCAT28F010: Licensed Intel Second SourceMorteza BaratzadehNo ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument19 pages2-Wire Serial EEPROM: FeaturesAgustin AndrokaitesNo ratings yet

- INTERFACINGDocument18 pagesINTERFACINGRajni GoelNo ratings yet

- 8-/10-Channel, Low Voltage, Low Power,: - AdcsDocument44 pages8-/10-Channel, Low Voltage, Low Power,: - AdcsjuenkkinNo ratings yet

- 256 Kilobit (32 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsDocument12 pages256 Kilobit (32 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsAmine EmineNo ratings yet

- Overview Data Sheets: F 8653: Central ModuleDocument2 pagesOverview Data Sheets: F 8653: Central ModulemohamadziNo ratings yet

- APM4546Document13 pagesAPM4546Ridho MawardiNo ratings yet

- CMOS Static RAM 16K (2K X 8-Bit) : Features DescriptionDocument11 pagesCMOS Static RAM 16K (2K X 8-Bit) : Features DescriptionTung DuongNo ratings yet

- 128 Kilobit (16 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsDocument12 pages128 Kilobit (16 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsMarcus SilvaNo ratings yet

- AT24C16BDocument20 pagesAT24C16Blucio perezNo ratings yet

- Simone's ResumeDocument4 pagesSimone's ResumeMorrisa AlexanderNo ratings yet

- AT-2plus 6-Channel ECG Unit: MemoryDocument98 pagesAT-2plus 6-Channel ECG Unit: MemoryOle CheNo ratings yet

- Summary of Lesson 4 - Preparing DataDocument4 pagesSummary of Lesson 4 - Preparing DatasergioNo ratings yet

- Database Programming Section 9 QuizDocument17 pagesDatabase Programming Section 9 QuizJosé Obeniel LópezNo ratings yet

- DriverEasy PCInfoDocument3 pagesDriverEasy PCInfoDiego GómezNo ratings yet

- Advantages of Proposed SystemDocument3 pagesAdvantages of Proposed System4JN19CS408 Shreelakshmi cNo ratings yet

- Integrating Lync Server and CUCMDocument37 pagesIntegrating Lync Server and CUCMrakgautam1980No ratings yet

- A Practical Approach To Software Quality PDFDocument297 pagesA Practical Approach To Software Quality PDFTrendkill Trendkill TrendkillNo ratings yet

- Lenovo Watch 9 User Guide EnglishDocument2 pagesLenovo Watch 9 User Guide EnglishKhairulAshraafNo ratings yet

- Multi-Dimensional Information-Driven Many-Objective Software Remodularization ApproachDocument18 pagesMulti-Dimensional Information-Driven Many-Objective Software Remodularization ApproachIoana SoraNo ratings yet

- HelloFresh OnboardingTeardownDocument10 pagesHelloFresh OnboardingTeardownShashank GuptaNo ratings yet

- Release Strategy PO With FioriDocument11 pagesRelease Strategy PO With FioriAymen AddouiNo ratings yet

- CEA User Manual (NASA RP-1311) PDFDocument184 pagesCEA User Manual (NASA RP-1311) PDFAmer SmajkićNo ratings yet

- AWS EC2 - Full ConfigDocument2 pagesAWS EC2 - Full Configcatalin pirnogNo ratings yet

- Internal Attachment ReportDocument12 pagesInternal Attachment ReportDaniel50% (2)

- Dsa Cheatsheet: Code LibraryDocument4 pagesDsa Cheatsheet: Code Library20I307 - AKSHAYA BNo ratings yet

- Tieng Anh 10 Friends Global - Unit 8 - Test 2Document8 pagesTieng Anh 10 Friends Global - Unit 8 - Test 2haminhpham1708No ratings yet

- Telugu IME ReadmeDocument5 pagesTelugu IME Readmesravannkumar2626ramNo ratings yet

- Logcat 1702664817732Document13 pagesLogcat 1702664817732fabiandejesuscentenoNo ratings yet

- What Are Escape Rooms - (PDFDrive)Document22 pagesWhat Are Escape Rooms - (PDFDrive)João Paulo da MataNo ratings yet

- Dip Computer Science 2023Document8 pagesDip Computer Science 2023DripNo ratings yet

- Lab Guide 6Document12 pagesLab Guide 6Eric MartinezNo ratings yet

- Examen, 03 ED, 2020A - ECUACIONES DIFERENCIALES (2020A), Spring 2020 - WebAssign PDFDocument4 pagesExamen, 03 ED, 2020A - ECUACIONES DIFERENCIALES (2020A), Spring 2020 - WebAssign PDFMarcos ArtolaNo ratings yet

- Dynamic Econometric Models: Autoregressive and Distributed-Lag ModelsDocument11 pagesDynamic Econometric Models: Autoregressive and Distributed-Lag Modelsمؤمن عثمان علي محمدNo ratings yet

- SHELL RECORD FullDocument23 pagesSHELL RECORD FullananthalaxmiNo ratings yet

- Explain System and User Status in Production OrderDocument204 pagesExplain System and User Status in Production Orderapi-3733587100% (4)

- Warning: Asm170 Murphymatic Micro-Controller Installation and Operation InstructionsDocument4 pagesWarning: Asm170 Murphymatic Micro-Controller Installation and Operation InstructionsSuryadiNo ratings yet

- CNAi Import Export InstructionsDocument12 pagesCNAi Import Export InstructionsSokratesNo ratings yet

- IBC100-e IntDocument2 pagesIBC100-e IntavryoneNo ratings yet

- New Literacies Across The CurriculumDocument13 pagesNew Literacies Across The CurriculumPECHERA, DARYLENE F.No ratings yet