Professional Documents

Culture Documents

UL62H256AS2A

Uploaded by

Jesus Maria LizarzabalCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UL62H256AS2A

Uploaded by

Jesus Maria LizarzabalCopyright:

Available Formats

U62H256A

Automotive Fast 32K x 8 SRAM

Features Description

! 32768 x 8 bit static CMOS RAM The U62H256A is a static RAM go High-Z until the new information

! 35 and 55 ns Access Time manufactured using a CMOS pro- is available. The data outputs have

! Common data inputs and cess technology with the following no preferred state. The Read cycle

data outputs operating modes: is finished by the falling edge of W,

! Three-state outputs - Read - Standby or by the rising edge of E, respec-

! Typ. operating supply current - Write - Data Retention tively.

35 ns: 45 mA The memory array is based on a Data retention is guaranteed down

55 ns: 30 mA 6-transistor cell. to 2 V. With the exception of E, all

! Standby current < 50 µA at 125 °C The circuit is activated by the fal- inputs consist of NOR gates, so

! TTL/CMOS-compatible ling edge of E. The address and that no pull-up/pull-down resistors

! Power supply voltage 5 V control inputs open simultaneously. are required.

! Operating temperature range According to the information of W

-40 °C to 85 °C and G, the data inputs, or outputs,

-40 °C to 125 °C are active. In a Read cycle, the

! QS 9000 Quality Standard data outputs are activated by the

! ESD protection > 2000 V falling edge of G, afterwards the

(MIL STD 883C M3015.7) data word will be available at the

! Latch-up immunity >100 mA outputs DQ0-DQ7. After the

! Package: SOP28 (300/330 mil) address change, the data outputs

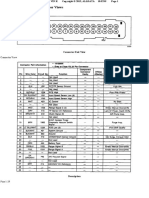

Pin Configuration Pin Description

A14 1 28 VCC

A12 2 27 W

A7 3 26 A13

A6 4 25 A8 Signal Name Signal Description

A5 5 24 A9 A0 - A14 Address Inputs

A4 6 23 A11 DQ0 - DQ7 Data In/Out

A3 7 22 G E Chip Enable

SOP

A2 8 21 A10 G Output Enable

A1 9 20 W Write Enable

E

VCC Power Supply Voltage

A0 10 19 DQ7

VSS Ground

DQ0 11 18 DQ6

DQ1 12 17 DQ5

DQ2 13 16 DQ4

VSS 14 15 DQ3

Top View

April 20, 2004 1

U62H256A

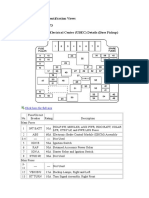

Block Diagram

A6

A7

Row Address Memory Cell

Row Decoder

A8 Array

Inputs

A9

A10

A11 512 Rows x

64 x 8 Columns

A12

A13

A14

Column Decoder

Column Address

A0

A1

DQ0

Inputs

A2

A3 Sense Amplifier/ DQ1

Write Control Logic

Common Data I/O

A4

DQ2

A5

DQ3

DQ4

DQ5

Address

Change Clock DQ6

Detector Generator

DQ7

VCC VSS E W G

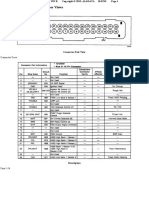

Truth Table

Operating Mode E W G DQ0 - DQ7

Standby/not selected H * * High-Z

Internal Read L H H High-Z

Read L H L Data Outputs Low-Z

Write L L * Data Inputs High-Z

* H or L

2 April 20, 2004

U62H256A

Characteristics

All voltages are referenced to V SS = 0 V (ground).

All characteristics are valid in the power supply voltage range and in the operating temperature range specified.

Dynamic measurements are based on a rise and fall time of ≤ 5 ns, measured between 10 % and 90 % of V I, as well as

input levels of VIL = 0 V and VIH = 3 V. The timing reference level of all input and output signals is 1.5 V,

with the exception of the tdis-times and ten-times, in which cases transition is measured ±200 mV from steady-state voltage.

Absolute Maximum Ratings a Symbol Min. Max. Unit

Power Supply Voltage VCC -0.5 7 V

Input Voltage VI -0.5 VCC + 0.5 b V

Output Voltage VO -0.5 VCC + 0.5 b V

Power Dissipation PD - 1 W

Operating Temperature K-Type Ta -40 85 °C

A-Type -40 125

Storage Temperature Tstg -65 150 °C

Output Short-Circuit Current

| IOS | 200 mA

at VCC = 5 V and VO = 0 V c

a

Stresses greater than those listed under „Absolute Maximum Ratings“ may cause permanent damage to the device. This is a stress rating only,

and functional operation of the device at condition above those indicated in the operational sections of this specification is not implied. Exposure

to absolute maximum rating conditions for extended periods may affect reliability

b

Maximum voltage is 7 V

c

Not more than 1 output should be shorted at the same time. Duration of the short circuit should not exceed 30 s.

Recommended

Symbol Conditions Min. Max. Unit

Operating Conditions

Power Supply Voltage VCC 4.5 5.5 V

Input Low Voltage d VIL -0.3 0.8 V

Input High Voltage VIH 2.2 VCC + 0.3 V

d

-2 V at Pulse Width 10 ns

April 20, 2004 3

U62H256A

Electrical Characteristics Symbol Conditions Min. Max. Unit

Supply Current - Operating Mode ICC(OP) VCC = 5.5 V

VIL = 0.8 V

VIH = 2.2 V

tcW = 35 ns 90 mA

tcW = 55 ns 70 mA

Supply Current - Standby Mode ICC(SB) VCC = 5.5 V

(CMOS level) VE = VCC - 0.2 V

K-Type 10 µA

A-Type 50 µA

Supply Current - Standby Mode ICC(SB)1 VCC = 5.5 V 1 mA

(TTL level) VE = 2.2 V

Output High Voltage VOH VCC = 4.5 V 2.4 V

IOH = -4.0 mA

Output Low Voltage VOL VCC = 4.5 V 0.4 V

IOL = 8.0 mA

Input High Leakage Current IIH VCC = 5.5 V 2 µA

VIH = 5.5 V

Input Low Leakage Current IIL VCC = 5.5 V -2 µA

VIL = 0V

Output High Current IOH VCC = 4.5 V -4 mA

VOH = 2.4 V

Output Low Current IOL VCC = 4.5 V 8 mA

VOL = 0.4 V

Output Leakage Current

High at Three-State Outputs IOHZ VCC = 5.5 V 2 µA

VOH = 5.5 V

Low at Three-State Outputs IOLZ VCC = 5.5 V -2 µA

VOL = 0V

4 April 20, 2004

U62H256A

Symbol 35 55

Switching Characteristics

Unit

Read Cycle

Alt. IEC Min. Max. Min. Max.

Read Cycle Time tRC tcR 35 55 ns

Address Access Time to Data Valid tAA ta(A) 35 55 ns

Chip Enable Access Time to Data Valid tACE ta(E) 35 55 ns

G LOW to Data Valid tOE ta(G) 15 25 ns

E HIGH to Output in High-Z tHZCE tdis(E) 15 20 ns

G HIGH to Output in High-Z tHZOE tdis(G) 12 15 ns

E LOW to Output in Low-Z tLZCE ten(E) 3 3 ns

G LOW to Output in Low-Z tLZOE ten(G) 0 0 ns

Output Hold Time from Address Change tOH tv(A) 3 3 ns

E LOW to Power-Up Time tPU 0 0 ns

E HIGH to Power-Down Time tPD 35 55 ns

Symbol 35 55

Switching Characteristics Unit

Write Cycle

Alt. IEC Min. Max. Min. Max.

Write Cycle Time tWC tcW 35 55 ns

Write Pulse Width tWP tw(W) 20 35 ns

Write Setup Time tWP tsu(W) 20 35 ns

Address Setup Time tAS tsu(A) 0 0 ns

Address Valid to End of Write tAW tsu(A-WH) 25 40 ns

Chip Enable Setup Time tCW tsu(E) 25 40 ns

Pulse Width Chip Enable to End of Write tCW tw(E) 25 40 ns

Data Setup Time tDS tsu(D) 15 25 ns

Data Hold Time tDH th(D) 0 0 ns

Address Hold from End of Write tAH th(A) 0 0 ns

W LOW to Output in High-Z tHZWE tdis(W) 15 20 ns

G HIGH to Output in High-Z tHZOE tdis(G) 12 15 ns

W HIGH to Output in Low-Z tLZWE ten(W) 0 0 ns

G LOW to Output in Low-Z tLZOE ten(G) 0 0 ns

April 20, 2004 5

U62H256A

Data Retention Mode

E - controlled

VCC

4.5 V

VCC(DR) ≥ 2 V

2.2 V 2.2 V

tsu(DR) Data Retention trec E

0V

VCC(DR) - 0.2 V ≤ VE(DR) ≤ VCC(DR) + 0.3 V

Data Retention Symbol

Characteristics Conditions Min. Typ. Max. Unit

Alt. IEC

Data Retention Supply Voltage VCC(DR) 2 5.5 V

Data Retention Supply Current ICC(DR) VCC(DR) = 3 V

VE = VCC(DR) - 0.2 V

K-Type 6 µA

A-Type 30 µA

Data Retention Setup Time tCDR tsu(DR) See Data Retention 0 ns

Waveforms (above)

Operating Recovery Time tR trec tcR ns

Test Configuration for Functional Check

5V

A0 VCC

A1

A2

A3

A4 DQ0

A5 DQ1 481

ment of all 8 output pins

Simultaneous measure-

relevant test measurement

Input level according to the

VIH A6 DQ2

A7

A8 DQ3

A9 DQ4

A10 DQ5

VIL A11

A12 DQ6

A13 DQ7 VO

A14

30 pF e

E

W

255

G VSS

e

In measurement of tdis(E),tdis(W), ten(E), ten(W), ten(G) the capacitance is 5 pF.

6 April 20, 2004

U62H256A

Capacitance Conditions Symbol Min. Max. Unit

Input Capacitance VCC = 5.0 V CI 7 pF

VI = VSS

Output Capacitance f = 1 MHz

Ta = 25 °C Co 7 pF

All pins not under test must be connected with ground by capacitors.

Ordering Code

Example U62H256A S K 35 LL

Type Leadfree Option

blank = Standard Package

Package G1 = Leadfree Green Package f

S = SOP28 (300 mil)

S2 = SOP28 (330 mil) Type 2 Power Consumption

blank = Standard (only A-Type)

Operating Temperature Range LL = Very Low Power (only K-Type)

K = -40 to 85 °C

A = -40 to 125 °C Access Time

35 = 35 ns

55 = 55 ns

f

on special request

Device Marking (example)

Product specification ZMD Date of manufacture

U62H256ASK (The first 2 digits indicating

Assembly location and 35LL C 0425 the year, and the last 2

trace code 1 ZZ G1 digits the calendar week.)

Internal Code Leadfree Green Package

April 20, 2004 7

U62H256A

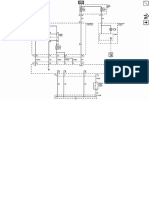

Read Cycle 1: Ai-controlled (during Read Cycle : E = G = V IL, W = VIH)

tcR

Ai Address Valid

ta(A)

DQi Previous Data Valid Output Data Valid

Output

tv(A)

Read Cycle 2: G-, E-controlled (during Read Cycle: W = V IH)

tcR

Ai Address Valid

tsu(A) ta(E) tdis(E)

E ten(E)

ta(G) tdis(G)

G ten(G)

DQi High-Z

Output Output Data Valid

tPU

tPD

ICC(OP) 50 %

50 %

ICC(SB)

8 April 20, 2004

U62H256A

Write Cycle1: W-controlled

tcW

Ai Address Valid

tsu(E) th(A)

E

tsu(A-WH)

W tw(W)

tsu(A)

tsu(D) th(D)

DQi

Input Data Valid

Input

tdis(W) ten(W)

DQi High-Z

Output

Write Cycle 2: E-controlled

tcW

Ai Address Valid

tsu(A) th(A)

E tw(E)

tsu(W)

W

tsu(D) th(D)

DQi Input Data Valid

Input ten(E) tdis(W)

DQi High-Z

Output tdis(G)

undefined L- to H-level H- to L-level

The information describes the type of component and shall not be considered as assured characteristics.Terms of

delivery and rights to change design reserved.

April 20, 2004 9

U62H256A

LIFE SUPPORT POLICY

ZMD products are not designed, intended, or authorized for use as components in systems intended for surgical

implant into the body, or other applications intended to support or sustain life, or for any other application in which

the failure of the ZMD product could create a situation where personal injury or death may occur.

Components used in life-support devices or systems must be expressly authorized by ZMD for such purpose.

LIMITED WARRANTY

The information in this document has been carefully checked and is believed to be reliable. However Zentrum

Mikroelektronik Dresden AG (ZMD) makes no guarantee or warranty concerning the accuracy of said information

and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon it.

The information in this document describes the type of component and shall not be considered as assured charac-

teristics.

ZMD does not guarantee that the use of any information contained herein will not infringe upon the patent, trade-

mark, copyright, mask work right or other rights of third parties, and no patent or licence is implied hereby. This

document does not in any way extent ZMD’s warranty on any product beyond that set forth in its standard terms and

conditions of sale.

ZMD reserves terms of delivery and reserves the right to make changes in the products or specifications, or both,

presented in this publication at any time and without notice.

April 20, 2004 Zentrum Mikroelektronik Dresden AG

Grenzstraße 28 • D-01109 Dresden • P. O. B. 80 01 34 • D-01101 Dresden • Germany

Phone: +49 351 8822 306 • Fax: +49 351 8822 337 • Email: memory@zmd.de • http://www.zmd.de

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

You might also like

- U6264ADC Datasheet Download at HttpsDocument9 pagesU6264ADC Datasheet Download at HttpsNadir CebiyevNo ratings yet

- U 6264 AsaDocument8 pagesU 6264 AsaJoil LeandroNo ratings yet

- U62H64SA: Automotive Fast 8K X 8 SRAMDocument8 pagesU62H64SA: Automotive Fast 8K X 8 SRAMAhmed Sherif CupoNo ratings yet

- 256K X 16 4Mb Asynchronous SRAMDocument14 pages256K X 16 4Mb Asynchronous SRAMThein Htoon lwinNo ratings yet

- Memoria Dallas DS1658Y-100Document11 pagesMemoria Dallas DS1658Y-100wilmer1973No ratings yet

- DS1245Y/AB 1024k Nonvolatile SRAM: Features Pin AssignmentDocument3 pagesDS1245Y/AB 1024k Nonvolatile SRAM: Features Pin AssignmentDel ValleNo ratings yet

- DS1245Y/AB 1024k Nonvolatile SRAM: Features Pin AssignmentDocument10 pagesDS1245Y/AB 1024k Nonvolatile SRAM: Features Pin Assignmentاحمد زغارىNo ratings yet

- DS1230Y/AB 256k Nonvolatile SRAM: Features Pin AssignmentDocument11 pagesDS1230Y/AB 256k Nonvolatile SRAM: Features Pin AssignmentCairineLopesNo ratings yet

- Winbond - 29c020 - 90 (Memoria FlashStreetBasket PDFDocument22 pagesWinbond - 29c020 - 90 (Memoria FlashStreetBasket PDFrullitoNo ratings yet

- RMLV0816BGSB - 4S2Document14 pagesRMLV0816BGSB - 4S2Mohamed SuhailNo ratings yet

- MCM6208C DatasheetDocument8 pagesMCM6208C DatasheetGregory PinoNo ratings yet

- 256 Kilobit (32 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsDocument12 pages256 Kilobit (32 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsAmine EmineNo ratings yet

- D D D D: SN54ACT374, SN74ACT374 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsDocument22 pagesD D D D: SN54ACT374, SN74ACT374 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsMarta_d_eNo ratings yet

- D D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsDocument25 pagesD D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsДрагиша Небитни ТрифуновићNo ratings yet

- Am27c256 AmdDocument12 pagesAm27c256 AmdRafaelNo ratings yet

- DS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentDocument9 pagesDS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentJoel PalzaNo ratings yet

- sn74hc365 Ic PDFDocument18 pagessn74hc365 Ic PDFDanuu Goligat DhokaNo ratings yet

- A-Data: Synchronous DRAM 1M X 16 Bit X 4 Banks General Description FeaturesDocument9 pagesA-Data: Synchronous DRAM 1M X 16 Bit X 4 Banks General Description FeaturesJim LiebNo ratings yet

- SED1530 Series: Dot Matrix LCD Driver-ControllerDocument20 pagesSED1530 Series: Dot Matrix LCD Driver-ControllerJuan Carlos BarandicaNo ratings yet

- Item 11 X24C16PDocument15 pagesItem 11 X24C16Pdifa20061168No ratings yet

- D D D D D D D: Description/ordering InformationDocument19 pagesD D D D D D D: Description/ordering InformationkarimNo ratings yet

- DS1501/DS1511: Y2K-Compliant Watchdog Real-Time ClocksDocument20 pagesDS1501/DS1511: Y2K-Compliant Watchdog Real-Time Clocksfulk1989No ratings yet

- DS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentDocument9 pagesDS1220AB/AD 16k Nonvolatile SRAM: Features Pin AssignmentDiego SerranoNo ratings yet

- W27C512Document16 pagesW27C512algnben1746No ratings yet

- SN 74 HCT 573Document20 pagesSN 74 HCT 573bvNo ratings yet

- CS8411 CS8412: Digital Audio Interface ReceiverDocument36 pagesCS8411 CS8412: Digital Audio Interface Receivertinears02No ratings yet

- 64-Bit TTL Bipolar RAM, Inverting (3-State) : Integrated CircuitsDocument10 pages64-Bit TTL Bipolar RAM, Inverting (3-State) : Integrated CircuitsEdher Hugo Morales EscobedoNo ratings yet

- D D D D D D D D: Description/ordering InformationDocument19 pagesD D D D D D D D: Description/ordering InformationEzequiel AriasNo ratings yet

- DS1245Y/AB 1024k Nonvolatile SRAM: Features Pin AssignmentDocument12 pagesDS1245Y/AB 1024k Nonvolatile SRAM: Features Pin Assignmentprairote pengCNo ratings yet

- WBNDS00693 1Document22 pagesWBNDS00693 1ANDREA SIFFREDI NIETONo ratings yet

- Chapter 3Document39 pagesChapter 3belihuNo ratings yet

- TLV1543 ADC SPI 10bits 11 VoiesDocument30 pagesTLV1543 ADC SPI 10bits 11 Voiesloic.savorninNo ratings yet

- 256 Kbit (32Kb x8) Parallel EEPROM With Software Data ProtectionDocument21 pages256 Kbit (32Kb x8) Parallel EEPROM With Software Data ProtectionvanmarteNo ratings yet

- 28 C 64Document19 pages28 C 64thetkhinechoNo ratings yet

- 4 Mbit (512Kb x8, Uniform Block) Single Supply Flash Memory: M29F040 Is Replaced by The M29F040BDocument31 pages4 Mbit (512Kb x8, Uniform Block) Single Supply Flash Memory: M29F040 Is Replaced by The M29F040BYacine AlgersNo ratings yet

- 1-Of-16 Decoder/demultiplexer: Integrated CircuitsDocument8 pages1-Of-16 Decoder/demultiplexer: Integrated CircuitsCyro PereiraNo ratings yet

- 96 KHZ Digital Audio Receiver: Cs8413 Cs8414Document38 pages96 KHZ Digital Audio Receiver: Cs8413 Cs8414moocomNo ratings yet

- Ds1225ab Ds1225adDocument9 pagesDs1225ab Ds1225adMuhammad Jalal AldeenNo ratings yet

- CS8412Document38 pagesCS8412ricardosdiotiNo ratings yet

- Cat28f020p 12Document16 pagesCat28f020p 12Carlos MarquesNo ratings yet

- Ds1245ab Ds1245yDocument11 pagesDs1245ab Ds1245yakeem alturkiNo ratings yet

- SN 74 LVTH 541Document11 pagesSN 74 LVTH 541api-3825669No ratings yet

- M5M51008CFP MitsubishiElectricSemiconductorDocument7 pagesM5M51008CFP MitsubishiElectricSemiconductorErasmo FrancoNo ratings yet

- CAT28C256: 32K-Bit Parallel E PromDocument10 pagesCAT28C256: 32K-Bit Parallel E PromAhmed AlsheikhNo ratings yet

- 1 Mbit (128K X 8) Parallel EEPROM With Software Data ProtectionDocument22 pages1 Mbit (128K X 8) Parallel EEPROM With Software Data ProtectionvanmarteNo ratings yet

- Memory Interface Circuits 80x86 Processors: Ref: Online Course On EE-390, KFUPMDocument15 pagesMemory Interface Circuits 80x86 Processors: Ref: Online Course On EE-390, KFUPMMarcus QeqqrqrrqNo ratings yet

- 96Khz 24bit Adc With Single-Ended Input: General DescriptionDocument17 pages96Khz 24bit Adc With Single-Ended Input: General Description邓建福No ratings yet

- DS34Document14 pagesDS34akeem alturkiNo ratings yet

- CAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromDocument11 pagesCAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromAdnen GuedriaNo ratings yet

- X24C04 4K 512 X 8 Bit: 3839 FHD F01Document19 pagesX24C04 4K 512 X 8 Bit: 3839 FHD F01Legna80No ratings yet

- 74LS164Document4 pages74LS164jaja558No ratings yet

- Chapter 3Document43 pagesChapter 3salitemhiretNo ratings yet

- 27c210a 15Document29 pages27c210a 15Abraham GutierrezNo ratings yet

- 1 MB (128K X 8, Chip Erase) FLASH MEMORY: DescriptionDocument25 pages1 MB (128K X 8, Chip Erase) FLASH MEMORY: DescriptionWill ?No ratings yet

- 128 Kilobit (16 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsDocument12 pages128 Kilobit (16 K X 8-Bit) CMOS EPROM: Distinctive CharacteristicsMarcus SilvaNo ratings yet

- 74LS374Document24 pages74LS374aasadad100% (1)

- SN 74 Ls 374Document32 pagesSN 74 Ls 374Ajish joNo ratings yet

- SN54LS373, SN54LS374, SN54S373, SN54S374, SN74LS373, SN74LS374, SN74S373, SN74S374 Octal D-Type Transparent Latches and Edge-Triggered Flip-FlopsDocument32 pagesSN54LS373, SN54LS374, SN54S373, SN54S374, SN74LS373, SN74LS374, SN74S373, SN74S374 Octal D-Type Transparent Latches and Edge-Triggered Flip-FlopsMladen VujicicNo ratings yet

- SN54ACT574, SN74ACT574 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsDocument6 pagesSN54ACT574, SN74ACT574 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsYenco Barliza DiazNo ratings yet

- Tle 7209-2R para Motor Paso A Paso PDFDocument32 pagesTle 7209-2R para Motor Paso A Paso PDFabrahamrojasNo ratings yet

- SIR System o Bolsas de AireDocument17 pagesSIR System o Bolsas de AireJesus Maria LizarzabalNo ratings yet

- Tabla de ConversionDocument30 pagesTabla de ConversionJesus Maria LizarzabalNo ratings yet

- Chery Orinoco 1.8 2017 M-TDocument2 pagesChery Orinoco 1.8 2017 M-TJesus Maria Lizarzabal100% (1)

- Chevrolet - Manual Procedimientos BLAZER 1998 5.7 Pinout 4Document2 pagesChevrolet - Manual Procedimientos BLAZER 1998 5.7 Pinout 4Jesus Maria LizarzabalNo ratings yet

- Transmision Automatica 4L60Document109 pagesTransmision Automatica 4L60Jesus Maria LizarzabalNo ratings yet

- Chevrolet - Manual Procedimientos BLAZER 1998 5.7 Pinout 3Document2 pagesChevrolet - Manual Procedimientos BLAZER 1998 5.7 Pinout 3Jesus Maria LizarzabalNo ratings yet

- Chevrolet - Manual Procedimientos BLAZER 1998 5.7 Pinout 2Document2 pagesChevrolet - Manual Procedimientos BLAZER 1998 5.7 Pinout 2Jesus Maria LizarzabalNo ratings yet

- Chevrolet - Manual Procedimientos BLAZER 1998 5.7 Pinout 1Document2 pagesChevrolet - Manual Procedimientos BLAZER 1998 5.7 Pinout 1Jesus Maria LizarzabalNo ratings yet

- Ronco 5.8Document13 pagesRonco 5.8jemalizNo ratings yet

- Captiva 3.2L 2008Document13 pagesCaptiva 3.2L 2008Jesus Maria LizarzabalNo ratings yet

- DaVinci Resolve 17 Colorist GuideDocument345 pagesDaVinci Resolve 17 Colorist GuideOusmane Traoré100% (1)

- International Journal of Computational Science, Information Technology and Control Engineering (IJCSITCE)Document3 pagesInternational Journal of Computational Science, Information Technology and Control Engineering (IJCSITCE)Anonymous BI4sNIkiNwNo ratings yet

- CS1100 LabManual Jan-April 2011 For StudentsDocument23 pagesCS1100 LabManual Jan-April 2011 For Studentsabhinav_ksskNo ratings yet

- Recording With AudacityDocument5 pagesRecording With AudacityMilokulaKatoNo ratings yet

- SSIS Integration Toolkit For Marketo Help ManualDocument28 pagesSSIS Integration Toolkit For Marketo Help ManualGanesh KamtheNo ratings yet

- 6.0.1.2 Broadband Varieties InstructionsDocument2 pages6.0.1.2 Broadband Varieties InstructionsCloyd Romeo Villafuerte0% (1)

- 221Document2 pages221Abhishek RanjanNo ratings yet

- Cek Rekomendasi TokopediaDocument1 pageCek Rekomendasi TokopediaAhmad DediNo ratings yet

- LCM Shipments ReceivingDocument64 pagesLCM Shipments ReceivingskumaaranNo ratings yet

- CartconvDocument3 pagesCartconvoldmangoyaNo ratings yet

- WAMP Server and PHP ZeroMQ Extension InstallationDocument2 pagesWAMP Server and PHP ZeroMQ Extension InstallationGautambuddha AirportNo ratings yet

- Supporting Mobile Objects in Corba: Ec/Acts Climate ClusterDocument32 pagesSupporting Mobile Objects in Corba: Ec/Acts Climate ClusterLuitaNo ratings yet

- HIS Operation Centum VPDocument99 pagesHIS Operation Centum VPatif010100% (3)

- Customising Quick Access ToolbarDocument4 pagesCustomising Quick Access ToolbarsonamNo ratings yet

- Advance Computing TechnologyDocument2 pagesAdvance Computing TechnologySanjay PatelNo ratings yet

- Optical Transport Solutions: MRV Empowers The Optical Edge. We Deliver Packet and Optical SolutionsDocument6 pagesOptical Transport Solutions: MRV Empowers The Optical Edge. We Deliver Packet and Optical SolutionsmoneyminderNo ratings yet

- C++ Basic SyntaxDocument8 pagesC++ Basic SyntaxMohamed K MarahNo ratings yet

- Manual Radwin 5000Document525 pagesManual Radwin 5000Victor Jesús Sánchez JuárezNo ratings yet

- GSM Security NewDocument6 pagesGSM Security NewDinesh TaragiNo ratings yet

- Business Analytics NotesDocument5 pagesBusiness Analytics NotesSARGAM JAINNo ratings yet

- Informatica - Historical Catch-Up Load in Informatica Using UNIX ScriptDocument6 pagesInformatica - Historical Catch-Up Load in Informatica Using UNIX ScriptKapilNo ratings yet

- Implementation Guide For Parcel Interchange With IEC CDDDocument22 pagesImplementation Guide For Parcel Interchange With IEC CDDVjetar TepenskiNo ratings yet

- Configuring Zig-Bee Modules For Point-to-Point Communication Using XCTUDocument16 pagesConfiguring Zig-Bee Modules For Point-to-Point Communication Using XCTUGurudatta PalankarNo ratings yet

- When Does UE Need To Perform Random Access ProcedureDocument8 pagesWhen Does UE Need To Perform Random Access ProcedureAngela BarrNo ratings yet

- Ecdl Manual Module 4Document107 pagesEcdl Manual Module 4doaabdelfatah100% (1)

- Bently Nevada Monitor Specification: Cooling Gas CompressorDocument2 pagesBently Nevada Monitor Specification: Cooling Gas CompressorHaitham AbdEl-TawabNo ratings yet

- Development of A Distributed Systems Simulator For Event Based Middle WareDocument22 pagesDevelopment of A Distributed Systems Simulator For Event Based Middle Wareapi-3728449100% (1)

- Presentation On BALSAHARADocument36 pagesPresentation On BALSAHARAradhika_kambhamNo ratings yet

- Computational Astrophysics and Cosmology PDFDocument26 pagesComputational Astrophysics and Cosmology PDFRiddhijit ChattopadhyayNo ratings yet

- 8DG42094BAAA - V1 - Alcatel-Lucent 1350 OMS EML 9.1.1 User Guide (Maint-2)Document534 pages8DG42094BAAA - V1 - Alcatel-Lucent 1350 OMS EML 9.1.1 User Guide (Maint-2)balla aubinNo ratings yet