Professional Documents

Culture Documents

SEMIKRON Application-Note Gate Driver Basics EN 2021-07-22 Rev-01

Uploaded by

erode els erodeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SEMIKRON Application-Note Gate Driver Basics EN 2021-07-22 Rev-01

Uploaded by

erode els erodeCopyright:

Available Formats

Application Note Revision: 01

AN 21-002 Issue date:

Prepared by:

2021-07-22

Paul Drexhage

Approved by: Arendt Wintrich

Keyword: driver, gate, IGBT, MOSFET, replaces AN-7002, AN-

7003, AN-7004

Gate Driver Basics

1. Introduction .............................................................................................................................1

2. Topology ..................................................................................................................................2

2.1 Voltage rating......................................................................................................................3

3. Driver Output Capability .............................................................................................................4

3.1 Drive voltage.......................................................................................................................4

3.2 Gate charge ........................................................................................................................6

3.2.1 Qout and additional boost capacitance................................................................................9

3.3 Average gate current ............................................................................................................9

3.4 Peak gate current.................................................................................................................9

4. Gate Resistor ..........................................................................................................................10

4.1 Minimum gate resistance.....................................................................................................10

4.2 Internal gate resistor ..........................................................................................................11

4.3 Soft turn-off resistor ...........................................................................................................11

4.4 Power dissipation ...............................................................................................................11

4.5 Resistor type .....................................................................................................................12

4.6 Switching behaviour of the free-wheeling diode ......................................................................12

4.7 Influence on switching losses ...............................................................................................13

5. Physical Implementation...........................................................................................................14

5.1 Connections between controller and driver.............................................................................15

5.2 Connections between driver and module................................................................................16

5.2.1 Lead dress ..................................................................................................................16

5.2.2 Component location ......................................................................................................16

5.2.3 Additional components ..................................................................................................17

5.3 PCB layout ........................................................................................................................18

5.3.1 Insulation coordination..................................................................................................18

6. Conclusion..............................................................................................................................19

1. Introduction

This application note is intended to assist in the selection and implementation of an off-the-shelf driver core

or plug-and-play gate driver. This application note replaces AN-7002, AN-7003, and AN-7004.

In power electronics systems, the term “gate driver” is generally used to describe the circuit connecting the

low-voltage controller (containing software and system logic) to the high-voltage power modules (containing

IGBTs, MOSFETs, etc.).

Commercial IGBT/MOSFET drivers are available in three basic classes:

Driver ICs: This term covers the broad category of integrated circuits from basic level shifters (e.g.

3.3V logic input, high current bipolar output) to complete driver circuits integrating logic and isolation

into one transfer-moulded package. In the former case, these components require the design of

© by SEMIKRON / 2021-07-22 / Application Note Page 1/20

PROMGT.1023/ Rev.7/ Template Application Note

additional isolation and/or power supply circuits to achieve full functionality. In the latter case, due

to the physical constraints of the package, these devices are generally limited to lower power

applications.

Driver cores: For medium to high power applications, a driver core (Figure 1L) provides all of the

functional blocks of a complete driver IC, but on a larger scale. Isolation is usually achieved with

large optocouplers or pulse transformers that allow for higher operating voltages and greater

creepage/clearance distances. The entire circuit is fabricated on a PCB that can be plugged/soldered

into a larger PCB. This design allows flexibility to adjust gate resistance and trip levels for specific

modules.

Plug-and-play: For industry-standard modules (e.g. SEMITRANS10, SEMiX3p) complete driver

boards (Figure 1R) containing all the features of a driver core plus the requisite gate resistors and

configuration components for a specific module type are already installed. The PCBs are designed to

directly press, solder, or plug into a certain module housing.

Figure 1: SKYPER 12 PV driver core (L) and SKYPER 12 press-fit plug-and-play driver for

SEMiX3p module (R)

2. Topology

A modern two-channel driver circuit is generally constructed as in Figure 2 with the critical feature for safety

being a clear delineation between primary (low voltage) and secondary (high voltage) sides. The controller

is interfaced to the primary side, where logic (perhaps in the form of an ASIC) provides short pulse

suppression, interlock and/or dead time, and generally conditions the gating signals so that they can be

transmitted across an isolation barrier. Additionally, an isolated power supply is needed to provide the

positive and negative voltage rails that are used to turn the power devices on and off. Secondary side

components include this as well as fast-acting protection features (e.g. DSCP) that avoid the delay of sending

an error and the ensuing turn-off signal across the isolation barrier.

© by SEMIKRON / 2021-07-22 / Application Note Page 2/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 2: SEMIKRON two-channel driver block diagram

Primary side Isolation Secondary side

barrier

Error Processing

VCE monitoring Passive

Components

RG_ON

Signal

Gate RG_OFF

Processing

Drive RG_SOFT_OFF

Interlock

CGE

Deadtime

Soft TVS

Short pulse

Turn-off Clamp

suppression

Power Undervoltage

Supply Protection

DC/DC

converter

control

Power Undervoltage

Supply Protection

Error Processing

Soft Passive

Undervoltage

Turn-off Components

protection

RG_ON

Halt mode

Gate RG_OFF

Power-on

Drive RG_SOFT_OFF

reset

CGE

TVS

Error Processing Clamp

VCE monitoring

Driver core

Plug-and-play

2.1 Voltage rating

Most driver cores and plug-and-play drivers are categorized according to the maximum blocking voltage of

the devices they are designed to drive (e.g. 1200V, 1700V). This rating, in turn, translates to the voltage

used for type testing of the driver (Visol) which is mainly determined by the isolation barrier between primary

and secondary. Transformer-based isolation barriers, as used in most SEMIKRON driver products, are

particularly robust in this regard with a typical isolation voltage rating of 4kVACrms. Relevant standards and

methods for testing voltage isolation are given in [7].

© by SEMIKRON / 2021-07-22 / Application Note Page 3/20

PROMGT.1023/ Rev.7/ Template Application Note

3. Driver Output Capability

3.1 Drive voltage

While there are a variety of different techniques for turning a transistor gate on and off [2], by far the most

common is the resistance-controlled voltage-source type. In this method, fixed turn-on and turn-off voltages

are applied to the gate and the rate of rise of current is controlled with a resistor (Figure 3, Figure 4).

Particularly for larger devices, separate turn-on and turn-off gate resistors are used and this will be assumed

for most of the explanations given in this application note.

Figure 3: Turn-on of IGBT using a bipolar power supply for the gate driver

VGG(on)

IG

+

RGon VGE

-

© by SEMIKRON / 2021-07-22 / Application Note Page 4/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 4: Turn-off of IGBT using a bipolar power supply for the gate driver

IG

R Goff +

V GE

-

V GG(off)

These turn-on and turn-off voltages are generally uniform for a given semiconductor technology and selected

as a compromise between:

Cost/complexity (bipolar vs. unipolar secondary-side voltage supplies)

Switching speed

Immunity to parasitic turn-on (see [3])

Conduction losses (reducing RDS(on))

Protecting the gate oxide (not exceeding VGES)

Silicon IGBTs are generally driven with a 15V turn-on voltage and a -5V…-15V turn-off voltage for larger

(higher current) devices or 0V turn-off voltage for smaller (lower current devices). In the case of IGBT7 [6],

it is possible to safely turn off even large devices using a 0V turn-off voltage due to the gate capacitance (i.e.

CGE is large relative to CGC).

Silicon MOSFETs are generally driven with a 10V…15V turn-on voltage and a 0V turn-off voltage.

Silicon carbide MOSFETs are still evolving at the time of this writing but generally are driven with a high

(15V…20V) turn-on voltage to reduce on-state losses. A slightly negative turn-off voltage (-3V…-5V) is

recommended.

In most cases, these turn-on/turn-off voltages are fixed for off-the-shelf driver solutions so it is only

necessary to be aware of the used voltages when looking at other datasheet values (e.g. QG).

© by SEMIKRON / 2021-07-22 / Application Note Page 5/20

PROMGT.1023/ Rev.7/ Template Application Note

3.2 Gate charge

The fabrication of any insulated gate transistor (IGBT, MOSFET) yields three main intrinsic capacitances (CGE,

CCE, CGC). These capacitances can be combined to form general “small signal capacitances” (Cies, Cres, Coes)

and vary with voltage applied across the transistor.

Figure 5: Intrinsic and small-signal capacitances

Intrinsic capacitances Small-signal capacitances

Cies = CGE + CGC

Coes = CGC + CCE

Cres = CGC

For gate driver sizing, the most important of these capacitances are CGE (“gate capacitance”) and CGC (“Miller

capacitance”) as they most strongly determine the gate voltage and current characteristics. Figure 6 shows

the idealized waveforms at the gate including which capacitances are being charged by the gate current.

© by SEMIKRON / 2021-07-22 / Application Note Page 6/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 6: Idealized gate turn-on waveforms

VGE(on)

Miller plateau

VGE(pl)

Gate VGE(th)

Voltage

t

VGE(off)

IG(pk)

Gate

Current

CGE CGC CGE

t

VCC IRR

Collector

Voltage/

Current VCEsat

IC t

t0 t1 t2 t3 t4 t5

The main intervals of interest are (terms given for an IGBT):

t0…t1: The gate current IG charges the input capacitance CGE and the gate-emitter voltage VGE rises to the

threshold voltage VGE(th). Depending on the gate resistor, several amperes may be running in this

state. As VGE is still below VGE(th), no collector current flows during this period and VCE remains at VCC.

t1…t2: As soon as VGE exceeds VGE(th), the main device turn-on process starts. IC begins to increase but since

the free-wheeling diode is still conducting current at the beginning of this interval (for most

topologies), the collector-emitter voltage VCE will not yet drop. The reverse recovery behaviour of the

free-wheeling diode causes overshoot in the collector current (IRR). While the device is in the active

mode, the gate voltage is directly linked to the collector current so the overshoot is reflected in the

gate waveforms.

t2…t3: When the free-wheeling diode is finally off, VCE starts to drop rapidly and dVCE/dt is high. VGE is held

to VGE(pl) as CGC charges, resulting in the characteristic “Miller plateau”.

t3…t4: VCE decreases at a slower rate (with increasing CGC and constant gate current) towards the on-state

value (VCEsat) as CGC continues to charge. VGE remains at VGE(pl).

t4…t5: At the beginning of this interval, the device is fully turned-on. With CGC finally charged, CGE is now

able to completely charge, resulting in VGE reaching its steady state value, VGE(on). VCE reaches the

on-state value, VCEsat.

Turn-off of the device gate involves discharging the capacitances in a very similar manner. Idealized turn-off

waveforms (valid for the larger gate resistances typically used in applications) are given in Figure 7.

© by SEMIKRON / 2021-07-22 / Application Note Page 7/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 7: Idealized gate turn-off waveforms

VGE(on)

VGE(pl)

Gate VGE(th)

Voltage

t

VGE(off)

t

Gate

Current

Collector IC

Voltage/

Current VCC VCEsat

t

t0 t1 t2 t3 t4

While the capacitances described in Figure 5 influence the switching characteristics of the device, they are

not used directly to size the driver. For that, the gate charge characteristic is used. This characteristic is

given in the module datasheet in the form of a graph showing how the gate voltage changes with accumulated

charge (Figure 8L). The effective gate charge is then measured from the turn-off voltage, VGE(off), to the turn-

on voltage, VGE(on). As this voltage can vary between drivers, this should be checked before reading the

effective gate charge, QG.

In some cases, the datasheet graph may not extend far enough to account for the implemented gate voltages.

In this case, the gate charge characteristic should be extrapolated to determine the higher effective gate

charge (Figure 8R).

© by SEMIKRON / 2021-07-22 / Application Note Page 8/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 8: Example gate charge characteristic from SKM400GB12E4 datasheet (L) and

extrapolation method (R)

VGE(on) VGE(on)

-4

VGE

VGE(off) -8 -8

0 -1000 0

-12

QGE’ QGC QGE’’

VGE(off) -15

QG (+15/-8V) = 2260nC

QG (±15V) ≈3010nC

3.2.1 Qout and additional boost capacitance

The gate driver must be able to source or sink the gate charge every switching event without a significant

drop of the voltage at the secondary-side power supply (e.g. +15V, -8V). A drop in this voltage during

switching can lead to increased switching losses. Because of this, gate driver datasheets give a value for

maximum output charge per pulse, Qout, which must be above the value of QG determined above. However,

the datasheet Qout is often given with the caveat that some additional boost capacitance must be added to

the by the user. The method for calculating this capacitance is given in the respective Technical Explanations

for the driver (e.g. SKYPER 42 LJ). Capacitors are placed on the secondary side in parallel with both the TOP

(e.g. 15V) and BOT (e.g. -8V) connections and should be close to the driver power supply pins. It is strongly

recommended that these be ceramic type and electrolytic or tantalum types are to be avoided. Additionally,

drivers may require that the additional secondary-side capacitance be duplicated on the primary side as well.

3.3 Average gate current

With the gate charge for a given device determined, the required average current can be calculated as:

𝐼𝐺(𝑎𝑣𝑔) = 𝑓𝑠𝑤 ∙ 𝑄𝐺 (1)

Where:

IG(avg): Required average gate current in Amperes

fsw: IGBT/MOSFET switching frequency in Herz

QG: IGBT/MOSFET gate charge in Coulombs (for a given voltage change)

The driver datasheet gives the value Iout(avg), the average output current capability per channel. Therefore,

the calculated value IG(avg) must be smaller than Iout(avg), which may be derated with temperature.

Similarly, the average output power required can be calculated by factoring in the total available gate voltage:

𝑃𝐺(𝑎𝑣𝑔) = 𝐼𝐺(𝑎𝑣𝑔) ∙ (𝑉𝐺𝐸(𝑜𝑛) ‒ 𝑉𝐺𝐸(𝑜𝑓𝑓)) (2)

3.4 Peak gate current

The peak current that occurs in the gate circuit during every turn-on or turn-off event can be roughly

calculated using the driving voltage and the total resistance in the gate circuit. In reality, the inductance in

© by SEMIKRON / 2021-07-22 / Application Note Page 9/20

PROMGT.1023/ Rev.7/ Template Application Note

the gate circuit further limits the current but since it may not be known during the initial design stages, the

absolute worst-case peak current can be estimated as:

𝑉𝐺𝐸(𝑜𝑛) ‒ 𝑉𝐺𝐸(𝑜𝑓𝑓)

𝐼𝐺(𝑝𝑘) = 𝑅𝐺 + 𝑅𝐸 + 𝑅𝐺𝑖𝑛𝑡 (3)

Where:

RG: Externally applied turn-on (or turn-off) gate resistor

RE: Externally applied emitter resistor, if present

RGint: Gate resistor internal to module

The driver datasheet gives the value Iout(peak), the peak output current capability per channel. Therefore, the

calculated value IG(pk) should be below Iout(peak), though due to the worst-case nature of the calculated current

(mentioned previously) this should only be considered for rough selection of the driver.

4. Gate Resistor

As explained above, on a basic level the gate resistor controls the charging and discharging of a (gate)

capacitance. This, in turn, affects a number of critical parameters:

Device switching time

Switching losses

Reverse bias safe operating area (RBSOA)

Short-circuit safe operating area (SCSOA)

Electromagnetic (high-frequency) emissions

Rate of change of collector-emitter (drain-source) voltage, dv/dt

Rate of change of collector (drain) current, di/dt

Reverse recovery of free-wheeling diode

This behaviour can vary between technologies (IGBT/MOSFET “generations”), but in general an increased

gate resistance will lead to slower switching speed and increased switching losses. Gate resistance selection

is a trade-off between maximum allowed voltage slopes (dv/dt), EMI, and switching losses.

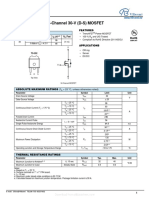

4.1 Minimum gate resistance

When an IGBT (MOSFET) module is qualified by a manufacturer, switching tests are performed to determine

the turn-on and turn-off resistors that will minimize switching losses while also maintaining stable behaviour

across the safe operating area for the device. This is done in a controlled environment with standardized

equipment and a low-inductance DC-link structure. The resulting minimum recommended resistor values

(and corresponding switching speeds and losses) are given in the “Characteristics” section of the device

datasheet (Figure 9). While these values can be taken as a starting point, the optimal gate resistor for a

given application can only be found through double-pulse testing [4].

Figure 9: Location of minimum turn-on and turn-off resistors in datasheet (SKM400GB12E4)

© by SEMIKRON / 2021-07-22 / Application Note Page 10/20

PROMGT.1023/ Rev.7/ Template Application Note

Maximum gate resistance is not defined, but cannot be so large as to keep the device from reaching saturation

during each switching period (i.e. linear operation is prohibited).

4.2 Internal gate resistor

Many power modules have an internal gate resistance, RGint, for each switch installed inside the module or,

more often, fabricated directly onto the IGBT/MOSFET die. This resistor is added by the manufacturer to

stabilize the switching behaviour of the device and cannot be removed or changed. Furthermore, all datasheet

values for switching losses, switching speeds, etc. already account for this resistance. Therefore, all “RG”

values give on the datasheet are for external, user-applied gate resistors. The internal gate resistor is only

used for calculating peak gate current (3.4) and estimating gate current pulse width (4.3).

4.3 Soft turn-off resistor

Many drivers offer dynamic short-circuit protection (DSCP, VCE-monitoring, DESAT) where the secondary side

of the driver can detect a rise in the on-state voltage of a device due to a short circuit and immediately switch

off the device. However, turn-off at high current with the “normal” gate resistor can lead to overvoltage

across the device. Therefore, many DSCP circuits incorporate an additional soft turn-off resistor that is put

in series with the normal RGoff in the event of a DESAT event (Figure 10). This increased turn-off resistance

is intended to slow the turn-off of the device, thereby reducing the rate of change of current and hence the

induced overvoltage.

Figure 10: Soft turn-off resistor during DESAT event

DRIVER

VGG(on)

RGon

RGoff ISC

RGsoft-off

VGG(off)

A typical starting value for RGsoft-off is 10 times RGoff. However, the proper value has to be very carefully

evaluated in the system in accordance with the individual application parameters. The setup is a balance

between staying within the maximum permitted short circuit time of the device (tpsc) while also not exceeding

the voltage limit (VCES or VDSS).

4.4 Power dissipation

A high peak gate current (3.4) passes through the gate resistor during each switching transition at a

frequency typically in the kHz range. This results in a large amount of power dissipated in a small (typically

surface mounted PCB) resistor. Figure 11 illustrates the shape of the current at the gate, with positive pulses

flowing through the turn-on resistor and negative pulses flowing through the turn-off resistor.

© by SEMIKRON / 2021-07-22 / Application Note Page 11/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 11: Gate current waveform

IG(pk)_ON

tp(off)

tp(on)

IG(pk)_OFF

If the shape of the current pulses is assumed triangular, the RMS value and hence, the average power

dissipation in either the turn-on or the turn-off resistor can be calculated:

𝑡𝑝 ∙ 𝑓𝑠𝑤 2

(

𝑃𝑅_𝐺_𝑎𝑣𝑔 = 𝐼𝐺(𝑝𝑘) ∙ 3 ) ∙𝑅 𝐺 (4)

Where:

IG(pk): Either turn-on or turn-off peak current

fsw: Switching frequency in Hz

RG: Either turn-on or turn-off gate resistor

tp: Either turn-on or turn-off current base width (as defined in Figure 11), which can be estimated

as:

2 ∙ 𝑄𝑔

𝑡𝑝 ≈ 𝐼𝐺(𝑝𝑘) (4b)

As the peak currents can be quite high, it is also critical to consider the peak power dissipated in each resistor:

2

𝑃𝑅_𝐺_𝑝𝑘 = 𝐼𝐺(𝑝𝑘) ∙ 𝑅𝐺 (5)

Resistors manufacturers should provide a graph of repetitive pulse load capability (in W) versus pulse

duration (in s).

4.5 Resistor type

The high power dissipated in the gate resistors requires consideration of the resistor’s power rating,

particularly for modern surface mount types. Furthermore, the relatively low resistance values, high operating

temperature, and high pulse current capability are generally found in metal film resistors, and in particular,

the cylindrical Metal Electrode Leadless Face (MELF) type.

Lastly, the high power requirements, coupled with the fact that failure (opening) of a gate resistor could

cause the IGBT or MOSFET to remain on, means that most high power converter designs utilize multiple

resistors in parallel to achieve the effective RGon or RGoff value. In this way the heat can be spread across a

PCB and the failure of a single gate resistor does not necessarily mean control of the converter is immediately

lost.

4.6 Switching behaviour of the free-wheeling diode

The switching behaviour of the free-wheeling diode is also affected by the gate resistor and limits the

minimum value of the gate resistance. This means that the turn-on switching speed of the IGBT can be only

increased up to a level compatible with the reverse recovery behaviour of the free-wheeling diode being

used. Figure 12 depicts the typical dependency of the free-wheeling diode reverse recovery current IRRM on

© by SEMIKRON / 2021-07-22 / Application Note Page 12/20

PROMGT.1023/ Rev.7/ Template Application Note

diF/dt, determined by the control of the given gate resistor RGon of the IGBT. The reverse recovery current

increases with the commutation speed, diF/dt. An increase in IRRM will also cause higher turn-off power

dissipation in the free-wheeling diode. Using a turn-on resistor above the minimum recommended value (4.1)

will reduce such behaviour.

Figure 12: Diode peak reverse recovery current vs. di/dt and RGon (L) and soft recovery (R)

(SKM400GB12E4)

V,I I

trr

ts tf

0

0.2IRRM

dI/dt dIr/dt

RGon=

IRRM IRRM

V

VM

t

4.7 Influence on switching losses

While it is generally safe to assume that higher gate resistor values lead to slower switching speeds and

higher switching losses, the actual effect of gate resistance on switching loss is defined more clearly using a

graph on the device datasheet (Figure 13). The slope and shape of these curves can vary dramatically

between device generations.

The example figure also illustrates the consideration for differing turn-on and turn-off resistor values. The

turn-on resistor (RGon) determines the turn-on energy of the IGBT/MOSFET as well as the turn-off (reverse

recovery) energy of the corresponding freewheeling diode. The turn-off resistor (RGoff) determines only the

turn-off energy of the IGBT/MOSFET.

© by SEMIKRON / 2021-07-22 / Application Note Page 13/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 13: Effect of gate resistors on switching energies (SKM400GB12E4)

70mJ

57mJ

33mJ

RGon = 3Ω

RGoff = 5Ω

5. Physical Implementation

Equally important to individual component values is the physical layout of the driver. In the case of a driver

core, the user is responsible for constructing an adaptor board which contains the application specific

components (e.g. gate resistors), configuration components for the driver (e.g. for selecting dead time,

DESAT protection levels), and connections to the power module (e.g. solder, spring, plug, wire). This

combination of driver core plus adaptor board(s) then becomes the “gate driver” circuit. An example is given

in Figure 14 where a SKiM93 module is being driven by a SKYPER 42 driver core. A “Board 93 GB SKYPER 42

R” is used for the adaptor board and provides connections to the driver, turn-on and turn off gate resistors,

and a connector for connection to the PWM controller. In this case, the board also serves to parallel each

set of three IGBTs in the module, allowing a “6-pack” (three individual half-bridges) to operate as a “2-pack”

(single large half-bridge).

In certain instances (smaller power applications), the controller may be integrated into the same circuit board

as the driver, however, physical separation of some sort must be still maintained, at least for the sake of

voltage isolation.

© by SEMIKRON / 2021-07-22 / Application Note Page 14/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 14: Example of SKiM93 module with SKYPER 42 driver core and adaptor board

Driver core Connection to

(2-channel) controller

Adaptor board

Module

(configured as

half-bridge)

5.1 Connections between controller and driver

Control signals for the gate driver cannot be compromised by interference. Electrical interference can come

from a number of sources such as high di/dt and dv/dt due to IGBT/MOSFET switching. The primary goal is

then to minimize coupling between the control signals and these noise sources. A few design tips for gate

driver / controller connection are given below:

Traces on the printed circuit board should be kept as short as possible. Loops (large areas between

a signal and its return) should be avoided.

Cables from the controller should not exceed three meters. Twisted pair cable should be used.

Control signals should not be grouped with control power supply lines. Signal grounds and power

supply grounds should be separate. Both grounds should be tied at a single point to avoid ground

loops.

Signal cables should be placed as far away as possible from power terminals, power cables, ground

cables, DC-link capacitors and all other noise sources.

Control signal cable should not run parallel to power cable. The minimum distance between control

signal cable and power cable should be 30cm and the cables should only cross perpendicularly.

It is recommended that all cables be kept close to ground (e.g. heat sink or similar).

In noise intensive applications, it is recommended that shielded cables or fibre optic interfaces be

used to improve noise immunity.

Use a low value capacitor (1nF) between signal and power supply ground of the gate driver for

differential mode noise suppression. With current limited line drives, this capacitor can cause a small

delay of a few ns.

The use of an open-collector driver from the controller for the gate signals is not recommended.

© by SEMIKRON / 2021-07-22 / Application Note Page 15/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 15: Connections between controller and gate driver

< 3m

Power supply positive

Twisted

pair

Control signal ground

Gate

Controller

Control signal Driver

(e.g. TOP, BOT) ~1nF

Power supply ground

5.2 Connections between driver and module

The gate driver must be located very close to the module to minimize stray inductance. An advantageous

solution, even for high-power modules, is to mount the gate driver onto the IGBT module directly. Where

this is not possible, at least the components shown in Figure 16 should be mounted at the module (e.g. on

a small auxiliary circuit board) with cabling run up to the driver board. A few design tips on gate driver/IGBT

connection for systems where wire connections are used are given in the following sections.

5.2.1 Lead dress

The connections between gate driver and module must be kept as short as possible. Gate and emitter

wiring should be twisted pair.

Gate wiring for top and bottom IGBTs or other phases must not be bundled together.

The VCE-monitoring (DESAT protection) wiring must not be bundled together with the gate and

emitter wiring.

Voltage is induced across LE (Figure 16) due to the high di/dt of the load current. If the ground

(emitter connection) of the driver circuit is connected to this power terminal (instead of the auxiliary

emitter), the voltage across LE decreases the gate turn-on voltage. In addition, voltage is added to

the gate turn-off voltage to slow down turn-on/turn-off. Use auxiliary emitter contacts to minimize

the negative feedback effect on gate-emitter voltage.

The total stray inductance in the gate-emitter circuit (combination of LG values in Figure 16) forms

an LC circuit with the gate input capacitance Cies. The resonation of this LC circuit could cause voltage

peaks exceeding the rating of the device. In order to damp these oscillations, it is suggested that the

gate resistor be no smaller than:

𝐿𝐺_𝑡𝑜𝑡𝑎𝑙

𝑅𝐺(𝑚𝑖𝑛) ≥ 2 ∙ 𝐶𝑖𝑒𝑠 (6)

A high gate inductance can also inadvertently accelerate switching speed which may cause a device

to operate outside its safe operating area (i.e. collector-emitter overvoltage).

5.2.2 Component location

Place the gate resistances for turn-on and turn-off close together.

If external boost capacitors are used, the capacitors must be placed as close to the gate driver as

possible in order to minimize parasitic inductance.

© by SEMIKRON / 2021-07-22 / Application Note Page 16/20

PROMGT.1023/ Rev.7/ Template Application Note

5.2.3 Additional components

In order to ensure an IGBT remains off when the driver supply voltage is removed and voltage is

applied to the power circuit it is recommended that a 10kΩ resistor (RGE) be placed between the gate

and emitter. If a wire connection is used, do not place RGE between printed circuit board and IGBT

module. RGE has to be placed very close to the module.

Use a transient voltage suppressor (DTVS) between gate and emitter. The suppressor diode must be

placed very close to the IGBT module and can protect the IGBT gate in overvoltage conditions as well

as limit the short circuit current should a short circuit occur. During short circuit, the gate emitter

voltage may increase due to the Miller capacitance between collector and gate. High dv/dt during

short circuit causes a current to flow through the Miller capacitor, in doing so increasing the gate

emitter voltage. The suppressor diode will clamp this voltage. Furthermore, the suppressor diode can

protect the gate driver from consequential damage should the IGBT module malfunction.

The use of a capacitor (CGE) between gate and emitter can be advantageous, even for high-power

IGBT modules and parallel operation (see [5]). The gate emitter capacitor CGE is used as a smoothing

capacitor, especially in the event of a short circuit, in order to reduce oscillation at the IGBT gate.

CGE should be approximately 10…50% of the intrinsic CGE of the IGBT. The CGE has to be placed very

close to the IGBT module.

Driver circuits (such as the SKYPER series) that incorporate VCE-monitoring (DESAT protection)

monitor the collector-emitter voltage when the device is in an on state. When the device is off, a

diode (DVCE) is necessary to block high voltage from damaging the driver. This diode must be capable

of blocking at least the same voltage as that of the main device. Additionally, the diode must have a

reverse recovery time faster than the VCE rise time of the main device. These requirements, coupled

with the necessary voltage spacing, limit the selection to specialized diodes such as the BY203 series.

For higher voltage operation (e.g. with 1700V devices), an additional resistor (RVCE) is used to further

reduce the voltage. The voltage drops of these additional components need to be considered when

selecting the trip point for the VCE-monitoring circuit.

The trip point (VCEStat) for the VCE-monitoring is typically set through a resistor (RCFG) that forms the

lower half of a voltage divider. A capacitor (CCFG) in parallel determines the blanking time (tbl) for the

detection circuit.

Further details for selecting component values are given in the respective Technical Explanations

document for the driver core.

Figure 16: Connections between gate driver and module (one channel shown)

RVCE DVCE

Collector

CCFG RCFG

LG RGon

Main gate

driver

circuit/ LG’ RGoff

driver core

CGE RGE DTVS

LG’’

Auxiliary

emitter

LE

Power

emitter

© by SEMIKRON / 2021-07-22 / Application Note Page 17/20

PROMGT.1023/ Rev.7/ Template Application Note

5.3 PCB layout

The thermal requirements for the gate resistors described in 4.3 and 4.5, coupled with the bullet points in

5.2, dictate the layout of the PCB. The primary guiding point is the use of a large emitter plane at least

beneath the gate resistors. This technique reduces stray inductance and provides some heatsinking.

Figure 17 shows a layout for turn-on and turn-off resistors with an emitter plane. The left side of the figure

shows the complete layout with RGon (R251//R252//R253) and RGoff (R254//R255//R256) in the centre. The

centre of Figure 17 shows the topside connection for the resistors with large areas of copper providing

heatsinking (note that the pads extend beneath the resistors). The right of Figure 17 shows the large emitter

plane on the copper layer below the topside layer, extending below the resistors and reducing any loop area

that would cause parasitic inductance in the gate-emitter circuit.

Figure 17: Example PCB layout for gate resistors

Complete Top layer Bottom layer

5.3.1 Insulation coordination

When designing a PCB for a driver core, it is important not to compromise the isolation voltage rating of the

system by reducing creepage and clearance distances below those defined by the driver core itself. For

example, most two-channel SKYPER driver cores are divided into “islands” of isolated circuits, each with their

own connectors down to the main PCB (Figure 18). These driver cores may also include slots to increase

creepage distance; these notches do not necessarily need to be duplicated on the PCB if care is taken to

separate circuits.

© by SEMIKRON / 2021-07-22 / Application Note Page 18/20

PROMGT.1023/ Rev.7/ Template Application Note

Figure 18: Isolation concept on SKYPER 12 PV driver core

Primary Secondary

(BOT)

Isolationprim-sec

Isolationsec-sec

Isolation Secondary

slots (TOP)

Further information regarding standards and methods for determining insulation coordination can be found

in [8].

6. Conclusion

Gate driver design is a complex topic but driver products are commercially available that allow a user to

focus on tuning the operation of the power module. Initial sizing of such a driver can be quickly performed

as shown here but no closed-form formulae can give the perfect component values for a particular application.

Thorough lab testing (e.g. double-pulse testing, [4]) is required to arrive at final gate resistor values.

Figure 1: SKYPER 12 PV driver core (L) and SKYPER 12 press-fit plug-and-play driver for SEMiX3p module

(R) ...............................................................................................................................................2

Figure 2: SEMIKRON two-channel driver block diagram .......................................................................3

Figure 3: Turn-on of IGBT using a bipolar voltage source .....................................................................4

Figure 4: Turn-off of IGBT using a bipolar voltage source .....................................................................5

Figure 5: Intrinsic and small-signal capacitances.................................................................................6

Figure 6: Idealized gate turn-on waveforms .......................................................................................7

Figure 7: Idealized gate turn-off waveforms .......................................................................................8

Figure 8: Example gate charge characteristic from SKM400GB12E4 datasheet (L) and extrapolation method

(R) ...............................................................................................................................................9

Figure 9: Location of minimum turn-on and turn-off resistors in datasheet (SKM400GB12E4)..................10

Figure 10: Soft turn-off resistor during DESAT event .........................................................................11

Figure 11: Gate current waveform ..................................................................................................12

Figure 12: Diode peak reverse recovery current vs. di/dt and RGon (L) and soft recovery (R)

(SKM400GB12E4) .........................................................................................................................13

Figure 13: Effect of gate resistors on switching energies (SKM400GB12E4)...........................................14

Figure 14: Example of SKiM93 module with SKYPER 42 driver core and adaptor board ...........................15

Figure 15: Connections between controller and gate driver .................................................................16

Figure 16: Connections between gate driver and module (one channel shown)......................................17

Figure 17: Example PCB layout for gate resistors ..............................................................................18

Figure 18: Isolation concept on SKYPER 12 PV driver core ..................................................................19

© by SEMIKRON / 2021-07-22 / Application Note Page 19/20

PROMGT.1023/ Rev.7/ Template Application Note

References

[1] www.SEMIKRON.com

[2] A. Wintrich, U. Nicolai, W. Tursky, T. Reimann, “Application Manual Power Semiconductors”, 2nd

edition, ISLE Verlag 2015, ISBN 978-3-938843-83-3

[3] N. Hofstötter, “Limits and hints how to turn off IGBTs with unipolar supply”, AN 1401, Rev. 02,

SEMIKRON International GmbH 2015

[4] J. Lamp, “IGBT Peak Voltage Measurement and Snubber Capacitor Specification”, AN 7006, Rev. 00,

SEMIKRON International GmbH 2008

[5] N. Hofstötter, “IGBT Modules in Parallel Operation with Central and Individual Driver Board”, AN 17-

001 , Rev. 00, SEMIKRON International GmbH 2017

[6] A. Wintrich, P. Beckedahl, “Introduction of new IGBT Generation 7”, AN 19-002, Rev. 01, SEMIKRON

International GmbH 2019

[7] R. Weiss, “High voltage testing”, AN 16-002, Rev. 02, SEMIKRON International GmbH 2019

[8] R. Weiss, “Coordination of insulation”, AN 1405, Rev. 03, SEMIKRON International GmbH 2017

IMPORTANT INFORMATION AND WARNINGS

The information in this document may not be considered as guarantee or assurance of product characteristics

("Beschaffenheitsgarantie"). This document describes only the usual characteristics of products to be expected in typical

applications, which may still vary depending on the specific application. Therefore, products must be tested for the

respective application in advance. Application adjustments may be necessary. The user of SEMIKRON products is

responsible for the safety of their applications embedding SEMIKRON products and must take adequate safety measures

to prevent the applications from causing a physical injury, fire or other problem if any of SEMIKRON products become

faulty. The user is responsible to make sure that the application design is compliant with all applicable laws, regulations,

norms and standards. Except as otherwise explicitly approved by SEMIKRON in a written document signed by authorized

representatives of SEMIKRON, SEMIKRON products may not be used in any applications where a failure of the product or

any consequences of the use thereof can reasonably be expected to result in personal injury. No representation or warranty

is given and no liability is assumed with respect to the accuracy, completeness and/or use of any information herein,

including without limitation, warranties of non-infringement of intellectual property rights of any third party. SEMIKRON

does not assume any liability arising out of the applications or use of any product; neither does it convey any license under

its patent rights, copyrights, trade secrets or other intellectual property rights, nor the rights of others. SEMIKRON makes

no representation or warranty of non-infringement or alleged non-infringement of intellectual property rights of any third

party which may arise from applications. This document supersedes and replaces all information previously supplied and

may be superseded by updates. SEMIKRON reserves the right to make changes.

SEMIKRON INTERNATIONAL GmbH

Sigmundstrasse 200, 90431 Nuremberg, Germany

Tel: +49 911 6559 6663, Fax: +49 911 6559 262

sales@semikron.com, www.semikron.com

© by SEMIKRON / 2021-07-22 / Application Note Page 20/20

PROMGT.1023/ Rev.7/ Template Application Note

You might also like

- Electronics One-Seven PDFDocument1,038 pagesElectronics One-Seven PDFray davis100% (2)

- Install-Config Guide - SureSigns VS4 Rel A.07Document96 pagesInstall-Config Guide - SureSigns VS4 Rel A.07CHRISTOPHER BURLESON100% (1)

- Secure, intuitive CXDI Control Software optimizes digital radiography workflowDocument3 pagesSecure, intuitive CXDI Control Software optimizes digital radiography workflowzoir qodirovNo ratings yet

- Sirona Orthophos 3 Dental X-Ray - Maintenance ManualDocument24 pagesSirona Orthophos 3 Dental X-Ray - Maintenance ManualAhmed Mohamed Abd Elsalam100% (1)

- System On / Off / Login: Icon Name DescriptionDocument2 pagesSystem On / Off / Login: Icon Name DescriptionCristian Eduardo Caro Ubilla100% (1)

- M700 M701 User GuideDocument58 pagesM700 M701 User GuideAndrei DanaiataNo ratings yet

- Pts000052-Dicom Conformance Statement Mylab X4XX F060XXX-F065XXX 01.1 PDFDocument393 pagesPts000052-Dicom Conformance Statement Mylab X4XX F060XXX-F065XXX 01.1 PDFRadiologos Del MundoNo ratings yet

- ENG - 6984924503 - Rev2 (Service Manual)Document440 pagesENG - 6984924503 - Rev2 (Service Manual)l.n.a.92100% (1)

- Elecs RefresherDocument46 pagesElecs Refreshermario sanchezNo ratings yet

- Analog Layout TechniquesDocument29 pagesAnalog Layout Techniquesarammart100% (1)

- Technical Instruction for CSA-71A Compressor UnitDocument36 pagesTechnical Instruction for CSA-71A Compressor Unitjesusweiss6No ratings yet

- ENG - 6916000203 - Rev11 (Technical Manual)Document102 pagesENG - 6916000203 - Rev11 (Technical Manual)l.n.a.92No ratings yet

- Siemens Mammomat Balance Maintenance InstructionDocument22 pagesSiemens Mammomat Balance Maintenance InstructionMarlon DeteraNo ratings yet

- Starters For Centrifugal Chillers: Installation, Operation and Maintenance ManualDocument56 pagesStarters For Centrifugal Chillers: Installation, Operation and Maintenance ManualMuhammad Javed BhattiNo ratings yet

- EN - ZiehmPortfolio - Brochure 28438 - 2023 - 03 - 16Document15 pagesEN - ZiehmPortfolio - Brochure 28438 - 2023 - 03 - 16Anh Kiệt ChiêuNo ratings yet

- Spare Parts CMS RevADocument26 pagesSpare Parts CMS RevAnader0123No ratings yet

- Project Report FinalDocument36 pagesProject Report FinalNiranjan ThimmappaNo ratings yet

- 86504C4A Diamond D32 Spare Part Catalog Nov04 PDFDocument108 pages86504C4A Diamond D32 Spare Part Catalog Nov04 PDFJavier AltamiranoNo ratings yet

- Instal OPERA T20c 20s T90s T90eDocument121 pagesInstal OPERA T20c 20s T90s T90eOlmedo MedinaNo ratings yet

- Radbook 2018 PDFDocument164 pagesRadbook 2018 PDFvietventNo ratings yet

- Enclosure - CR 30-X 2nd CR30-Xm - Input TrayDocument20 pagesEnclosure - CR 30-X 2nd CR30-Xm - Input TrayCarlos SolanoNo ratings yet

- DICOM Conformance Statement IE33 R5.1.x.x and IU22 R5.1.x.xDocument145 pagesDICOM Conformance Statement IE33 R5.1.x.x and IU22 R5.1.x.xGOMEDICAGSNo ratings yet

- Professional Washer Extractor Service ManualDocument34 pagesProfessional Washer Extractor Service Manualjack jansenNo ratings yet

- SPIDriver User Guide: Setup, APIs & ExamplesDocument22 pagesSPIDriver User Guide: Setup, APIs & ExamplesluizmataNo ratings yet

- Cardiosoft V6.71 Service Manual - SM - 2060290-150 - ADocument128 pagesCardiosoft V6.71 Service Manual - SM - 2060290-150 - AEmanuel Naskosi Santiz AguilarNo ratings yet

- Pike Intel Cresent Bay ULT Platform Block DiagramDocument33 pagesPike Intel Cresent Bay ULT Platform Block DiagramBausiniNo ratings yet

- Artis Zee EP Suite Final PDFDocument20 pagesArtis Zee EP Suite Final PDFTòng Tiêu ThanhNo ratings yet

- Schematic Diagram t240Document6 pagesSchematic Diagram t240dany weinfeldNo ratings yet

- CMMT-AS - S1 Manual 2021-04d 8153824g1Document44 pagesCMMT-AS - S1 Manual 2021-04d 8153824g1Emanuel CazanNo ratings yet

- Adc Solo enDocument2 pagesAdc Solo enNikolay PenevNo ratings yet

- PB2 800CSL Service Manual Pb2smDocument36 pagesPB2 800CSL Service Manual Pb2smde etenNo ratings yet

- Rev0 (System Integration Guide)Document52 pagesRev0 (System Integration Guide)Eth3r lok1No ratings yet

- Rotor Drive TheoryDocument6 pagesRotor Drive TheoryАлександрNo ratings yet

- 【SIEMENS】Cios Select-with-FD-BrochureDocument8 pages【SIEMENS】Cios Select-with-FD-BrochureAshleyNo ratings yet

- Olympus CV-160 Maintenance ManualDocument40 pagesOlympus CV-160 Maintenance ManualjansensouzaNo ratings yet

- Achieva User's Guide (NA) (English)Document76 pagesAchieva User's Guide (NA) (English)DENIS DAINo ratings yet

- Mercedes e Class 2009 Saloon 212 Owners ManualDocument373 pagesMercedes e Class 2009 Saloon 212 Owners ManualcatalinNo ratings yet

- Neusoft NeuViz64Document12 pagesNeusoft NeuViz64Mohamed ECH CHARFAOUYNo ratings yet

- x10 350ie User 221024 085929Document118 pagesx10 350ie User 221024 085929Manuel Albano Aguiar ArnaezNo ratings yet

- Maintenance Instructions System: From Serial No. 20.000Document43 pagesMaintenance Instructions System: From Serial No. 20.000Simon DelgusteNo ratings yet

- DataPro 5000DN English Guide RevFDocument14 pagesDataPro 5000DN English Guide RevFDanilo CarvalhoNo ratings yet

- (XENO-360) Quick ManualDocument2 pages(XENO-360) Quick ManualYousef SyNo ratings yet

- User Manual: VFD500M Series High Performance Smart InverterDocument102 pagesUser Manual: VFD500M Series High Performance Smart InvertervascoeeNo ratings yet

- Samsung GT-i9082 Galaxy Grand 07 Level 2 Repair - Assembly, DisassemblyDocument6 pagesSamsung GT-i9082 Galaxy Grand 07 Level 2 Repair - Assembly, Disassemblyahmad riza virsNo ratings yet

- Aa-2u Chassis (Kv-34fv16 Kv-34fv16c Kv-34fx260 Kv34fx260c)Document72 pagesAa-2u Chassis (Kv-34fv16 Kv-34fv16c Kv-34fx260 Kv34fx260c)David Argote BellidoNo ratings yet

- Amulet Quick Ref v1 6 1Document14 pagesAmulet Quick Ref v1 6 1ddubokaNo ratings yet

- Drawing Software & Shim ToolDocument5 pagesDrawing Software & Shim ToolTihomir Drenovski100% (1)

- ADV-Series Manual ENDocument406 pagesADV-Series Manual ENderbalijalel100% (1)

- Power System OverviewDocument23 pagesPower System OverviewHarold MartinezNo ratings yet

- Aloka Prosound F75 BrochureDocument10 pagesAloka Prosound F75 BrochureSUNGDUK HEONo ratings yet

- Fs-Aqura Essentials r1.0 - enDocument44 pagesFs-Aqura Essentials r1.0 - enJe PongNo ratings yet

- Philips Mcd183Document29 pagesPhilips Mcd183tavo litasNo ratings yet

- Wärtsilä JOVYSTAR HP 200-800kVA: Operating ManualDocument58 pagesWärtsilä JOVYSTAR HP 200-800kVA: Operating ManualAbdelwhab ElsaftyNo ratings yet

- GE Definium 8000 Operator ManualDocument381 pagesGE Definium 8000 Operator ManualAbdelraouf MohammadNo ratings yet

- Service Manual for Daewoo Mini Component Sound SystemsDocument46 pagesService Manual for Daewoo Mini Component Sound SystemsDaifred GutiérrezNo ratings yet

- All Products BrochureDocument14 pagesAll Products BrochureholysaatanNo ratings yet

- Sony Sa Wm20Document10 pagesSony Sa Wm20ronal starsNo ratings yet

- Dynamitron - October 2016 - WebDocument12 pagesDynamitron - October 2016 - WebChilmy Coklat SusuNo ratings yet

- ResMed AirCurve 10 User GuideDocument23 pagesResMed AirCurve 10 User GuideMedSparkNo ratings yet

- Engineering Change Notice (Field Change Notice) : Releasing The Information of DR-ID300CL Application Software V8.1Document65 pagesEngineering Change Notice (Field Change Notice) : Releasing The Information of DR-ID300CL Application Software V8.1Tayo AjakaiyeNo ratings yet

- RXi Box IPC - Training - RevADocument13 pagesRXi Box IPC - Training - RevAEzzNadiNo ratings yet

- Datex Capnomac Ultima Monitor - Service Manual PDFDocument232 pagesDatex Capnomac Ultima Monitor - Service Manual PDFFernandoNo ratings yet

- hIG 1800 240211Document35 pageshIG 1800 240211Manolo BalboaNo ratings yet

- Starters For Centrifugal Chillers: Installation, Operation and Maintenance ManualDocument84 pagesStarters For Centrifugal Chillers: Installation, Operation and Maintenance ManualJorge CotzomiNo ratings yet

- Republic Day Celebration-1Document1 pageRepublic Day Celebration-1erode els erodeNo ratings yet

- MS 486 PDFDocument9 pagesMS 486 PDFerode els erodeNo ratings yet

- MS 420 PDFDocument3 pagesMS 420 PDFerode els erodeNo ratings yet

- Erode DC DC Converter LetterDocument1 pageErode DC DC Converter Lettererode els erodeNo ratings yet

- Hog Daily e Loco 17 00 HRSDocument2 pagesHog Daily e Loco 17 00 HRSerode els erodeNo ratings yet

- MS - 434 - Rev - 0 PDFDocument6 pagesMS - 434 - Rev - 0 PDFerode els erodeNo ratings yet

- MS 415 PDFDocument7 pagesMS 415 PDFerode els erodeNo ratings yet

- SEMIKRON Technical Explanation Thermal Interface Materials EN 2019-09-25 Rev-03Document19 pagesSEMIKRON Technical Explanation Thermal Interface Materials EN 2019-09-25 Rev-03erode els erodeNo ratings yet

- Improving Fault Isolation in DC/DC Converters Based With Bayesian Belief NetworksDocument7 pagesImproving Fault Isolation in DC/DC Converters Based With Bayesian Belief Networkserode els erodeNo ratings yet

- Programmable Controllers DC-Output Module Telecommunication: TOSHIBA Photocoupler IRED & Photo-TransistorDocument8 pagesProgrammable Controllers DC-Output Module Telecommunication: TOSHIBA Photocoupler IRED & Photo-TransistorDraKo BaracunataNo ratings yet

- Influence of Traction Motor Components On ThermalDocument14 pagesInfluence of Traction Motor Components On Thermalerode els erodeNo ratings yet

- Research of Intelligent Lead-Acid Batteries ChargeDocument8 pagesResearch of Intelligent Lead-Acid Batteries Chargeerode els erodeNo ratings yet

- MS 490 To Avoid SPM OFF ON During VCU Reset PDFDocument7 pagesMS 490 To Avoid SPM OFF ON During VCU Reset PDFerode els erodeNo ratings yet

- FDocument1 pageFExer CelimaNo ratings yet

- Analysis of High Power IGBT Short Circuit Failures: IEEE Transactions On Plasma Science June 2004Document9 pagesAnalysis of High Power IGBT Short Circuit Failures: IEEE Transactions On Plasma Science June 2004erode els erodeNo ratings yet

- SEMIKRON Material Content Data Sheet SEMITRANS® 2 EN 2019-07-13 Rev-05Document2 pagesSEMIKRON Material Content Data Sheet SEMITRANS® 2 EN 2019-07-13 Rev-05erode els erodeNo ratings yet

- IGBT and diode failures in electronic power transformersDocument9 pagesIGBT and diode failures in electronic power transformerserode els erodeNo ratings yet

- 01 ArnoDocument4 pages01 Arnoerode els erodeNo ratings yet

- Stability and Dynamic Characteristics Analysis of DC-DC Buck Converter Via Mathematical Modelling"Document7 pagesStability and Dynamic Characteristics Analysis of DC-DC Buck Converter Via Mathematical Modelling"erode els erodeNo ratings yet

- A Three Windings Full Bridge Converter With A Lossless Clamp CircuitDocument9 pagesA Three Windings Full Bridge Converter With A Lossless Clamp Circuiterode els erodeNo ratings yet

- Syste Generalize MachDocument19 pagesSyste Generalize MachZobida AlazragNo ratings yet

- SLGN OdesDocument1 pageSLGN Odeserode els erodeNo ratings yet

- Turbine component list and diagramDocument2 pagesTurbine component list and diagramerode els erodeNo ratings yet

- Tidu578 PDFDocument48 pagesTidu578 PDFsuriantoNo ratings yet

- Harmonic Control of PWM Inverter For Traction: Translated From Denki Gakkai Ronbunshi, Vol. PPDocument8 pagesHarmonic Control of PWM Inverter For Traction: Translated From Denki Gakkai Ronbunshi, Vol. PPerode els erodeNo ratings yet

- Igbt Gate Driver Reference Design For Parallel Igbts With Short-Circuit Protection and External BJT BufferDocument33 pagesIgbt Gate Driver Reference Design For Parallel Igbts With Short-Circuit Protection and External BJT BufferVasil StoyanovNo ratings yet

- Modelingof Buck Converterwith Input FilterDocument13 pagesModelingof Buck Converterwith Input Filtererode els erodeNo ratings yet

- LICENSEDocument8 pagesLICENSEerode els erodeNo ratings yet

- Knoppix CheatcodesDocument3 pagesKnoppix CheatcodesdasboogiemanNo ratings yet

- What Is An SCR - Thyristor, Silicon Controlled Rectifier - Radio-ElectronicsDocument9 pagesWhat Is An SCR - Thyristor, Silicon Controlled Rectifier - Radio-ElectronicsKhin Aung ShweNo ratings yet

- Datasheet 5Document3 pagesDatasheet 5Nhat TruongNo ratings yet

- Introduction To HVDC VSC AlstomDocument30 pagesIntroduction To HVDC VSC AlstompongpumNo ratings yet

- Nano Transistors PDFDocument334 pagesNano Transistors PDFAlok KumarNo ratings yet

- 17 FinFETDocument47 pages17 FinFETVani YamaniNo ratings yet

- Matsuki-Me4435 C145078Document5 pagesMatsuki-Me4435 C145078Nguyễn Nhật MinhNo ratings yet

- Ae El Bh6dl4wDocument11 pagesAe El Bh6dl4wbasavarajNo ratings yet

- Features Description: Low-Cost, Green-Mode PWM Controller For Flyback Converters SG6858Document13 pagesFeatures Description: Low-Cost, Green-Mode PWM Controller For Flyback Converters SG6858Dusmantha AnandaratneNo ratings yet

- Characterization and Modeling of SiC MOSFET Body DiodeDocument9 pagesCharacterization and Modeling of SiC MOSFET Body DiodeAnonymous okeik4iSNo ratings yet

- Chapter 7 - FET BiasingDocument10 pagesChapter 7 - FET BiasingEliaquim RomanNo ratings yet

- B.SC ElectronicsDocument74 pagesB.SC ElectronicsLucifer DevilNo ratings yet

- SG6848 SGDocument13 pagesSG6848 SGjabbmfNo ratings yet

- Spice Computation of MOSDocument10 pagesSpice Computation of MOSJaymee LalbhaiNo ratings yet

- Time-Of-Flight (ToF) Measurement Using Pulse LasersDocument22 pagesTime-Of-Flight (ToF) Measurement Using Pulse Lasersengin kavakNo ratings yet

- An Improved Matlab/Simulink Model of Sic Power Mosfets: Gang Li Qiang GaoDocument6 pagesAn Improved Matlab/Simulink Model of Sic Power Mosfets: Gang Li Qiang Gaovenktesh22No ratings yet

- High-power N-channel MOSFET for switching regulators and DC-DC convertersDocument2 pagesHigh-power N-channel MOSFET for switching regulators and DC-DC convertershectorsevillaNo ratings yet

- The RF Mosfet Line N-Channel Enhancement-Mode MOSFET: Semiconductor Technical DataDocument7 pagesThe RF Mosfet Line N-Channel Enhancement-Mode MOSFET: Semiconductor Technical DataschokbrekerNo ratings yet

- Sony KDL-22BX300,32BX300 Chassis AZ1-FK PDFDocument33 pagesSony KDL-22BX300,32BX300 Chassis AZ1-FK PDFciro_svNo ratings yet

- Mosfet'S: From Microelectronic Circuits Text by Sedra and Smith Oxford PublishingDocument29 pagesMosfet'S: From Microelectronic Circuits Text by Sedra and Smith Oxford PublishingKomay Abo ShakraNo ratings yet

- PHD78NQ03LT: N-Channel 30-V (D-S) MOSFETDocument8 pagesPHD78NQ03LT: N-Channel 30-V (D-S) MOSFETNikolay ShkolkinNo ratings yet

- IRF 460 and 1N4007 DatasheetDocument10 pagesIRF 460 and 1N4007 DatasheetRadif AghnadiinNo ratings yet

- U4Document173 pagesU4Virthish DKNo ratings yet

- 2018 Ee 69Document19 pages2018 Ee 69Ali MohsinNo ratings yet

- Lecture 080 - Latchup and Esd: CMOS Analog Circuit Design, 2Document16 pagesLecture 080 - Latchup and Esd: CMOS Analog Circuit Design, 2Milan DubeyNo ratings yet

- Ece-Research Work 1Document10 pagesEce-Research Work 1Peale ObiedoNo ratings yet

- 161 20551 0 FS7M0880Document16 pages161 20551 0 FS7M0880Edwin Vitovis TorresNo ratings yet