Professional Documents

Culture Documents

VLSI Model qp2

Uploaded by

M. Thirumala Reddy100%(1)100% found this document useful (1 vote)

20 views1 pageA full adder has three inputs (a, b, cin) and two outputs (s, cout) where s is the sum and cout is the carry-out. The formulae for s and cout can be expressed in disjunctive normal form. There are three approaches for handling carry in n-bit word adders: (1) ripple carry which has a delay that increases linearly with word size, (2) carry-skip with fixed-size blocks which can reduce delay but requires multiple blocks, and (3) carry-skip with variable-size blocks which can further reduce delay but is more complex to implement. The document estimates and compares the delays of implementing a 48-bit adder using each

Original Description:

Original Title

VLSI model qp2

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentA full adder has three inputs (a, b, cin) and two outputs (s, cout) where s is the sum and cout is the carry-out. The formulae for s and cout can be expressed in disjunctive normal form. There are three approaches for handling carry in n-bit word adders: (1) ripple carry which has a delay that increases linearly with word size, (2) carry-skip with fixed-size blocks which can reduce delay but requires multiple blocks, and (3) carry-skip with variable-size blocks which can further reduce delay but is more complex to implement. The document estimates and compares the delays of implementing a 48-bit adder using each

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

100%(1)100% found this document useful (1 vote)

20 views1 pageVLSI Model qp2

Uploaded by

M. Thirumala ReddyA full adder has three inputs (a, b, cin) and two outputs (s, cout) where s is the sum and cout is the carry-out. The formulae for s and cout can be expressed in disjunctive normal form. There are three approaches for handling carry in n-bit word adders: (1) ripple carry which has a delay that increases linearly with word size, (2) carry-skip with fixed-size blocks which can reduce delay but requires multiple blocks, and (3) carry-skip with variable-size blocks which can further reduce delay but is more complex to implement. The document estimates and compares the delays of implementing a 48-bit adder using each

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

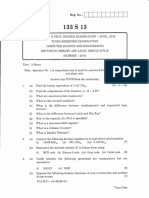

2008 Paper 9 Question 2

VLSI Design

(a) A full adder for a single bit has three inputs, a, b and cin , and two outputs,

s and cout for the sum and carry-out. State the formulae for s and cout in

disjunctive normal form. [2 marks]

(b) Explain the operation of the following three approaches for handling carry in

n-bit word adders, deriving formulae for the signals involved and explaining

the limiting factors on their speed:

(i ) ripple carry, [2 marks]

(ii ) carry-skip with fixed-size blocks, and [6 marks]

(iii ) carry-skip with variable-size blocks. [4 marks]

(c) Assuming a delay of τ for a round of combinational logic consisting of negation,

conjunction and disjunction, estimate the delays for the three designs applied

to a 48-bit adder. [3 × 2 marks]

You might also like

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsFrom EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikNo ratings yet

- ME 308 Online Series 1 DescriptiveDocument1 pageME 308 Online Series 1 DescriptiveimnithinNo ratings yet

- 07a50503 ComputergraphicsDocument5 pages07a50503 Computergraphics02871a0536No ratings yet

- A G1010 Pages: 2: Answer All Questions, Each Carries 4 MarksDocument2 pagesA G1010 Pages: 2: Answer All Questions, Each Carries 4 MarksMILAN K JAIN B.Tech CSE B 2018-2022No ratings yet

- Computer - Graphics 2005 SDocument5 pagesComputer - Graphics 2005 SVardhani DhulipudiNo ratings yet

- r05221201 Computer GraphicsDocument5 pagesr05221201 Computer Graphicslibrarian_abitNo ratings yet

- B.E - (2008 Patt.) - 1-5Document5 pagesB.E - (2008 Patt.) - 1-5Ravikiran JadhavNo ratings yet

- rr221402 Computer GraphicsDocument6 pagesrr221402 Computer GraphicsSRINIVASA RAO GANTANo ratings yet

- RT 41033112016Document8 pagesRT 41033112016varmaNo ratings yet

- Nov Dec 2016Document3 pagesNov Dec 2016pecoxor808No ratings yet

- A G192010 Pages:3: Answer All Questions, Each Carries 4 MarksDocument3 pagesA G192010 Pages:3: Answer All Questions, Each Carries 4 MarksMILAN K JAIN B.Tech CSE B 2018-2022No ratings yet

- CADA QP-Ktunotes - in PDFDocument3 pagesCADA QP-Ktunotes - in PDFsachinNo ratings yet

- r7310503 Computer GraphicsDocument1 pager7310503 Computer GraphicsRadhaKrishnamNo ratings yet

- Lab Session 3 - v3Document1 pageLab Session 3 - v3Jessica JapNo ratings yet

- (4660) - 1286 M.E. (Computer Networks) System Operations and Maintenance (2013 Credit Pattern) (Semester - III) (610202)Document127 pages(4660) - 1286 M.E. (Computer Networks) System Operations and Maintenance (2013 Credit Pattern) (Semester - III) (610202)PrathameshNo ratings yet

- Computer GraphicsDocument6 pagesComputer GraphicsPradeep KumarNo ratings yet

- Bit2102 Bit3101a Bbit106 Data Structures and AlgorithmsDocument3 pagesBit2102 Bit3101a Bbit106 Data Structures and AlgorithmsFact HubNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)rajkumarsac100% (1)

- CG 2020Document3 pagesCG 2020Kashish DhingraNo ratings yet

- Computer Graphics (ECS-504) 2011-12-2Document4 pagesComputer Graphics (ECS-504) 2011-12-2Ajay YadavNo ratings yet

- B. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ADocument3 pagesB. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ARajeev GairolaNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityKetan PatelNo ratings yet

- Computer Science Tripos Part IDocument10 pagesComputer Science Tripos Part IHuxNo ratings yet

- Nov Dec 2014Document4 pagesNov Dec 2014abdnazar2003No ratings yet

- Rr210203 Switching Theory and Logic DesignDocument9 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao GNo ratings yet

- Assignment On Development CylDocument10 pagesAssignment On Development Cyljay SinghNo ratings yet

- rr420306 Computer GraphicsDocument5 pagesrr420306 Computer GraphicsSRINIVASA RAO GANTANo ratings yet

- FemmDocument8 pagesFemmtyagaraju batchalaNo ratings yet

- Bbit 106 Data Structures and Algorithims - Distance LearningDocument3 pagesBbit 106 Data Structures and Algorithims - Distance Learningjames kilonzoNo ratings yet

- Question Paper Sep 2009Document3 pagesQuestion Paper Sep 2009Vignesh MuruganNo ratings yet

- Seemester Exam 2017-18 - 2521Document2 pagesSeemester Exam 2017-18 - 2521Arjun SinghNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Iyyappan SubramanianNo ratings yet

- Gujarat Technological University: Subject Code: 2151603 Date: Subject Name: Computer Graphics Time: Total Marks: 70Document2 pagesGujarat Technological University: Subject Code: 2151603 Date: Subject Name: Computer Graphics Time: Total Marks: 70Vrunda HingrajiyaNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityKetan PatelNo ratings yet

- COMP 420 Computer Graphics ExamDocument3 pagesCOMP 420 Computer Graphics ExamAlex KirimiNo ratings yet

- L-2/T-Licse Date: 08/08/2017: - 'Ds (Jia)Document22 pagesL-2/T-Licse Date: 08/08/2017: - 'Ds (Jia)Na ThakaNo ratings yet

- 08ab303 - Digital Logic CircuitsDocument3 pages08ab303 - Digital Logic CircuitsChandru RamaswamyNo ratings yet

- RT41033102019Document2 pagesRT41033102019Mahesh BabuNo ratings yet

- B4 (1) .4-R3 Chapter WiseDocument20 pagesB4 (1) .4-R3 Chapter Wisetabishkhan12345No ratings yet

- STLDDocument2 pagesSTLDANUPAMA PonnuNo ratings yet

- WWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic DesignDocument4 pagesWWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic Designbadiganti tejakrishnaNo ratings yet

- Btech Cs 3 Sem Computer Organization and Architecture kcs302 2022Document2 pagesBtech Cs 3 Sem Computer Organization and Architecture kcs302 2022Harshit dubeyNo ratings yet

- Course Code: MET 406 Azby/Ms - 18 / 4656 Eighth Semester B. E. (Mechanical Engineering) ExaminationDocument23 pagesCourse Code: MET 406 Azby/Ms - 18 / 4656 Eighth Semester B. E. (Mechanical Engineering) ExaminationMubarika SabirNo ratings yet

- Set No. 1: Digital Control Systems RT42021Document8 pagesSet No. 1: Digital Control Systems RT42021Akhil ChinnaNo ratings yet

- QP April2011 42 Mec IcgDocument4 pagesQP April2011 42 Mec IcgMohammedshafeeq Ahmed0% (1)

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universityfeyayel990No ratings yet

- Btech Cs 3 Sem Computer Organization and Architecture rcs302 2020Document2 pagesBtech Cs 3 Sem Computer Organization and Architecture rcs302 2020Vishal Kumar SharmaNo ratings yet

- GTU DOM Paper 2Document2 pagesGTU DOM Paper 2ManavNo ratings yet

- 2020-10-19SupplementaryEC370EC370-K - Ktu QbankDocument2 pages2020-10-19SupplementaryEC370EC370-K - Ktu QbankSharmin SathiNo ratings yet

- MCS-053 4Document3 pagesMCS-053 4Sumit Waitforit RanaNo ratings yet

- MCA105Document1 pageMCA105Abhi MittalNo ratings yet

- BCS 054 June2010 June2023Document116 pagesBCS 054 June2010 June2023giyori6960No ratings yet

- The Open University of Sri Lanka Faculty of Engineering Technology Department of Electrical and Computer EngineeringDocument4 pagesThe Open University of Sri Lanka Faculty of Engineering Technology Department of Electrical and Computer EngineeringYasith Ishara PereraNo ratings yet

- 07a4ec09 STLDDocument6 pages07a4ec09 STLDSRINIVASA RAO GANTANo ratings yet

- Apj Abdul Kalam Technological University Apj Abdul Kalam Technological UniversityDocument2 pagesApj Abdul Kalam Technological University Apj Abdul Kalam Technological UniversityMILAN K JAIN B.Tech CSE B 2018-2022No ratings yet

- RT41033082021Document3 pagesRT41033082021AB GamingNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universityeishaagrawal015No ratings yet

- Attainable Region Theory: An Introduction to Choosing an Optimal ReactorFrom EverandAttainable Region Theory: An Introduction to Choosing an Optimal ReactorNo ratings yet

- From Microstructure Investigations to Multiscale Modeling: Bridging the GapFrom EverandFrom Microstructure Investigations to Multiscale Modeling: Bridging the GapDelphine BrancherieNo ratings yet

- Transport Layer SecurityDocument45 pagesTransport Layer SecurityM. Thirumala ReddyNo ratings yet

- Structured Query Language (SQL) : DatabaseDocument72 pagesStructured Query Language (SQL) : DatabaseM. Thirumala ReddyNo ratings yet

- Data StructuresDocument35 pagesData StructuresM. Thirumala ReddyNo ratings yet

- Vlsi QP11Document1 pageVlsi QP11M. Thirumala ReddyNo ratings yet

- VLSI Designer Model PaperDocument1 pageVLSI Designer Model PaperM. Thirumala ReddyNo ratings yet

- Tree Planting ProjectDocument3 pagesTree Planting ProjectM. Thirumala ReddyNo ratings yet