Professional Documents

Culture Documents

Vlsi QP11

Uploaded by

M. Thirumala Reddy0 ratings0% found this document useful (0 votes)

9 views1 pageThe document discusses different designs for an n-input NAND gate in CMOS technology, including static CMOS, dynamic CMOS, and pseudo-nMOS. It asks the reader to sketch each design, annotate with suitable transistor widths considering resistance differences between p-channel and n-channel transistors, and calculate logical effort and parasitic delay for each. It then asks which design would be fastest for an n=4 input NAND gate when resistance of p-channel is 3 times n-channel, and how the answer might change if driving a large capacitive load.

Original Description:

Original Title

VLSI QP11

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document discusses different designs for an n-input NAND gate in CMOS technology, including static CMOS, dynamic CMOS, and pseudo-nMOS. It asks the reader to sketch each design, annotate with suitable transistor widths considering resistance differences between p-channel and n-channel transistors, and calculate logical effort and parasitic delay for each. It then asks which design would be fastest for an n=4 input NAND gate when resistance of p-channel is 3 times n-channel, and how the answer might change if driving a large capacitive load.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

9 views1 pageVlsi QP11

Uploaded by

M. Thirumala ReddyThe document discusses different designs for an n-input NAND gate in CMOS technology, including static CMOS, dynamic CMOS, and pseudo-nMOS. It asks the reader to sketch each design, annotate with suitable transistor widths considering resistance differences between p-channel and n-channel transistors, and calculate logical effort and parasitic delay for each. It then asks which design would be fastest for an n=4 input NAND gate when resistance of p-channel is 3 times n-channel, and how the answer might change if driving a large capacitive load.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

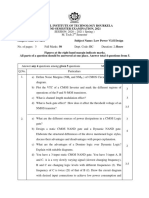

2004 Paper 9 Question 2

VLSI Design

(a) Sketch designs for an n-input NAND gate in CMOS using

(i ) static CMOS;

(ii ) dynamic CMOS;

(iii ) pseudo-nMOS. [2 marks each]

(b) Assuming that a conducting p-channel has a resistance γ times that of a

similarly sized n-channel, annotate each of your circuit diagrams with suitable

widths for the transistors, and explain the reasons for their values.

[2 marks each]

(c) For each design, calculate the logical effort and the parasitic delay.

[2 marks each]

(d ) Which is likely to be fastest for the case when n = 4 and γ = 3? What

difference would it make if the circuit were driving a large capacitative load?

[2 marks]

You might also like

- Digital Vlsi Design (Ecen 3201)Document2 pagesDigital Vlsi Design (Ecen 3201)Shovan GhoshalNo ratings yet

- Digital Vlsi Design (Ecen 3201) - 2017Document2 pagesDigital Vlsi Design (Ecen 3201) - 2017gaurav kumarNo ratings yet

- CMOS Ternary Logic CircuitsDocument7 pagesCMOS Ternary Logic CircuitsSubhasis BiswasNo ratings yet

- Week5 VLSI Subsystems Assignment AnswersDocument5 pagesWeek5 VLSI Subsystems Assignment AnswersGPS INNOVATIVESNo ratings yet

- AVD2Document2 pagesAVD2ankushwreNo ratings yet

- VLSI Designer Model PaperDocument1 pageVLSI Designer Model PaperM. Thirumala ReddyNo ratings yet

- Solutions MidtermDocument10 pagesSolutions MidtermVineet RawatNo ratings yet

- Sub: VLSI Design 4-1 ECE Descriptive Questions: Ds DsDocument3 pagesSub: VLSI Design 4-1 ECE Descriptive Questions: Ds DsMohan DasNo ratings yet

- SMPLXDocument5 pagesSMPLXVikas DewanganNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument2 pages3 Hours / 70 Marks: Seat No58 EX Ramawat PankajNo ratings yet

- Ecen 3103Document2 pagesEcen 3103gaurav kumarNo ratings yet

- EGB424 Assig23Document3 pagesEGB424 Assig23fgh fghfghfNo ratings yet

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- Electronic Design Automation (Ecen 2106) 2020Document4 pagesElectronic Design Automation (Ecen 2106) 2020abhishekkumarjhafbgNo ratings yet

- 2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Document7 pages2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Avik MitraNo ratings yet

- DC Dec 17Document3 pagesDC Dec 17SAURABH BHISENo ratings yet

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- Time: 3 Hours Total Marks: 70: PD PLDocument1 pageTime: 3 Hours Total Marks: 70: PD PLDeepanshi RuhelaNo ratings yet

- PN Sequence Generation From 2-D Array of Shift RegistersDocument7 pagesPN Sequence Generation From 2-D Array of Shift RegistersR InduNo ratings yet

- EXAM Phys Elec II 2016 SolutionsDocument10 pagesEXAM Phys Elec II 2016 SolutionsThulasizwe PhethaNo ratings yet

- Answer All Questions, Each Carries 4 MarksDocument3 pagesAnswer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- Cryptography and Network Security 2010Document4 pagesCryptography and Network Security 2010fitoj akaNo ratings yet

- ME 1998 Unsolved PDFDocument14 pagesME 1998 Unsolved PDFSathya ThyaguNo ratings yet

- Introduction To Internet 2012 PDFDocument2 pagesIntroduction To Internet 2012 PDFPratap Kumar MahatoNo ratings yet

- Digital Communications: B o B oDocument12 pagesDigital Communications: B o B oLion LionNo ratings yet

- EEC802Document2 pagesEEC802khayrul islamNo ratings yet

- DCMDocument2 pagesDCMapi-279049687No ratings yet

- ME 2003 Unsolved PDFDocument18 pagesME 2003 Unsolved PDFSathya ThyaguNo ratings yet

- National Institute of Technology Rourkela End Semester Examination, 2021Document3 pagesNational Institute of Technology Rourkela End Semester Examination, 2021ajay vermaNo ratings yet

- Advanced Digital VLSI Design (ECE 521) (Makeup) PDFDocument2 pagesAdvanced Digital VLSI Design (ECE 521) (Makeup) PDFRahul PinnamaneniNo ratings yet

- Cs 307 Data CommunicationDocument4 pagesCs 307 Data CommunicationNithin vNo ratings yet

- Question PaperDocument10 pagesQuestion PapersivaNo ratings yet

- XII PhysicsDocument60 pagesXII PhysicsBhavana ShindeNo ratings yet

- Capacitance and Power Modeling at Logic-Level: C V F PowerDocument7 pagesCapacitance and Power Modeling at Logic-Level: C V F PowerAnala MNo ratings yet

- Mid Semester Exam-March21Document1 pageMid Semester Exam-March21GOURAV MAHORENo ratings yet

- Course Code: PHT 101 Itsj/Rw - 17 / 1007 First / Second Semester Bachelor of Engineering ExaminationDocument3 pagesCourse Code: PHT 101 Itsj/Rw - 17 / 1007 First / Second Semester Bachelor of Engineering ExaminationFightingNo ratings yet

- HT TP: //qpa Pe R.W But .Ac .In: 2010-11 Parallel ProgrammingDocument4 pagesHT TP: //qpa Pe R.W But .Ac .In: 2010-11 Parallel ProgrammingarabindoNo ratings yet

- Sunversit: Enrollment No... LI.A3aa3..Document3 pagesSunversit: Enrollment No... LI.A3aa3..Pranjal BajajNo ratings yet

- MJ12 PDFDocument6 pagesMJ12 PDFSarika VadivelanNo ratings yet

- Complete Materials and Electrical E1 2021Document7 pagesComplete Materials and Electrical E1 2021Brody CrossNo ratings yet

- Research On 3D Wireless Sensor Networks ISC-EAR Routing AlgorithmDocument6 pagesResearch On 3D Wireless Sensor Networks ISC-EAR Routing AlgorithmAshagre MekuriaNo ratings yet

- Imc Oe PrevpapsDocument4 pagesImc Oe PrevpapsAbd 17No ratings yet

- Cassandra Availability VirtualDocument23 pagesCassandra Availability VirtualRaghavendar PNo ratings yet

- IES CONV Electrical Engineering 2000Document9 pagesIES CONV Electrical Engineering 2000jitenNo ratings yet

- Crosstalk Aware Bandwidth Modelling For VLSI RC Global Interconnects Using 2Document8 pagesCrosstalk Aware Bandwidth Modelling For VLSI RC Global Interconnects Using 2maheshwarivikas1982No ratings yet

- C C1115 Pages 2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesC C1115 Pages 2: Answer Any Two Full Questions, Each Carries 15 MarksFayaz aliNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Computer Networks Test 2Document18 pagesComputer Networks Test 2Nelson RajaNo ratings yet

- Logical EffortDocument108 pagesLogical EffortPranav DarganNo ratings yet

- Introduction To Rock Mechanics (CE-425) : Submission Date: 6 May 2021 (Thursday)Document1 pageIntroduction To Rock Mechanics (CE-425) : Submission Date: 6 May 2021 (Thursday)Shahzad AslamNo ratings yet

- DC QuestionDocument5 pagesDC QuestionVaishnavi BavalekarNo ratings yet

- 18EI56Document6 pages18EI56Rocky BhaiNo ratings yet

- Kec 072 2023Document2 pagesKec 072 20232000520310061No ratings yet

- Answer All Questions, Each Carries 3 Marks: Reg No.: - NameDocument2 pagesAnswer All Questions, Each Carries 3 Marks: Reg No.: - Nameanon_914773339No ratings yet

- Introduction To Parallel Computing CS4355/5325 Assignment 1: Due Date: September 17, 2009Document1 pageIntroduction To Parallel Computing CS4355/5325 Assignment 1: Due Date: September 17, 2009Riyanny 'Wiwied' PratiwiNo ratings yet

- Information Theory Year QSTNDocument9 pagesInformation Theory Year QSTNsagarNo ratings yet

- HT TP: //qpa Pe R.W But .Ac .In: 2011 Solid State DevicesDocument4 pagesHT TP: //qpa Pe R.W But .Ac .In: 2011 Solid State DevicesSoumitra BhowmickNo ratings yet

- Fast Technique For Computing Syndromes of B.C.H. and Reed-Solomon CodesDocument2 pagesFast Technique For Computing Syndromes of B.C.H. and Reed-Solomon CodesRAJKUMAR SAMIKKANNUNo ratings yet

- SANDISKDocument3 pagesSANDISKrAM100% (3)

- Transport Layer SecurityDocument45 pagesTransport Layer SecurityM. Thirumala ReddyNo ratings yet

- Structured Query Language (SQL) : DatabaseDocument72 pagesStructured Query Language (SQL) : DatabaseM. Thirumala ReddyNo ratings yet

- VLSI Model qp2Document1 pageVLSI Model qp2M. Thirumala Reddy100% (1)

- VLSI Designer Model PaperDocument1 pageVLSI Designer Model PaperM. Thirumala ReddyNo ratings yet

- Tree Planting ProjectDocument3 pagesTree Planting ProjectM. Thirumala ReddyNo ratings yet