Professional Documents

Culture Documents

TC554161FTL 70L

Uploaded by

Técnico 04 LógicaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TC554161FTL 70L

Uploaded by

Técnico 04 LógicaCopyright:

Available Formats

TOSHIBA

1l:554161F1nLJ1]{L-70L/85L/I0L

SILICON GATE CMOS PRELIMINARY

262,144 WORD x 16 BIT STATIC RAM

Description

The TC554161 FTUfRL is a 4,194,304 bit CMOS static random access memory organized as 262,144 words by 16 bits and

operated from a single 5V power supply. Advanced circuit techniques provide both high speed and low power features with an

operating current of 10mNMHz (typ.) and a minimum cycle time of 70ns. When CE is a logical high, the device is placed in a low

power standby mode in which the standby current is 601-!A (max.). The TC554161 FTUfRL has two control inputs. A chip enable

input (CE) allows for device selection and data retention control, while an output enable input (OE) provides fast memory access.

Byte access is supported by upper and lower byte controls. The TC554161 FTUfRL is suitable for use in microprocessor systems

where high speed, low power, and battery backup are required. The TC554161 FTUfRL is offered in a 54-pin thin small outline

plastic package (forward type, reverse type).

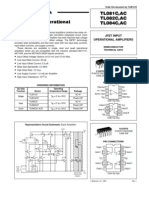

Features Pin Connection (Top View)

• Low power dissipation: 55mW/MHz (typ.)

• Standby current: 81-!A (max.) at Ta = 25°C NC A4 NC

A3 AS A3

• Single 5V power supply A2 A6 A2

• Access time (max.) Al A7 Al

AO NC AO

TC554161FTL/TRL 1/016 1/01 1/016

1/015 1/02 1/015

-70L -85L -10L

Vee Vee Vee

Access Time 70ns 85ns 100ns GND GND GND

11014 1/03 1/014

CE Access Time 70ns 85ns 100ns 11013 1/04 1/013

OE Access Time 35ns 45ns 50ns US LS US

CE OE CE

• Power down feature: CE NC NC NC

• Data retention supply voltage: 2.0 - 5.5V

RNV NC R/W

11012 1105 1/012

• Inputs and outputs TIL compatible 1/011 1/06 1/011

• Package TC554161 FTL : TSOP54-P-400 GND GND GND

Vee Vee Vee

TC554161TRL : TSOP54-P-400A 1/010 1/07 1/010

Pin Names 1/09 1108 1/09

NC AS NC

AO - A17 Address Inputs A17 A9 A17

Data Input/Output

A16 Al0 A16

1/01 - 1/016

AIS All Als

CE Chip Enable Input A14 A12 A14

RIW ReadIWrite Control Input

Al3 NC A13

OE Output Enable Input

LB, UB Data Byte Control Input

Voo Power (+5V)

GND Ground

NC No Connection

TOSHIBA AMERICA ELECTRONIC COMPDNENTS, INC. A .. 149

TC554161FTLfTRL-70U85U10L Static RAM

Block Diagram

a: ~ VOO

~~

ero

MEMORY

CELL ARRAY

1,024x256x 16

~ GNO

(4,194,304)

1101

1102

1103

1/04

1105

1106

~~~¥::7;~~=ZI

1108

1109

1107

1/010

1/011

1/012

1/013

1/014

11015

1/016

Operating Mode

~

MODE

CE OE R/W Lii

L

UB

L

1/01 -1/08

Output

1/09 -1/016

Output

POWER

1000

Read L L H H L High Impedance Output 1000

L H Output High Impedance .1

000

L L Input Input 1000

Write L * L H L High Impedance Input 1000

L H Input High Impedance 1000

L H H * *

Output Deselect High Impedance High Impedance 1000

L * * H H

Standby H * * * * High Impedance High Impedance loos

*HorL

Maximum Ratings

SYMBOL ITEM RATING UNIT

Voo Power Supply Voltage -0.3 - 7.0 V

VIN Input Voltage -0.3* - 7.0 V

VI/O Input and Output Voltage -0.5* - V DO + 0.5 V

Po Power Dissipation 0.6 W

TSOLOER Soldering Temperature - Time 260 -10 °C - sec

T STRG Storage Temperature -55 - 150 °C

TOPR Operating Temperature 0-70 °C

* -3.0V with a pulse width of 30ns

A:;'150 TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC. PRELIMINARY

Static RAM TC554161FTLlTRL-70U85U10L

DC Recommended Operating Conditions

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

Voo Power Supply Voltage 4.5 5.0 5.5

V IH Input High Voltage 2.2 - Voo + 0.3

V

V IL Input Low Voltage -0.3* - 0.8

V OH Data Retention Supply Voltage 2.0 - 5.5

* -3.0V with a pulse width of 30ns

DC Characteristics (Ta = 0 - 70°C, Voo = 5V±10%)

SYMBOL PARAMETER TEST CONDITION MIN. TYP. MAX. UNIT

III Input Leakage Current V IN = 0 - Voo - - ±1.0 ~

CE = V IH or RIW = V IL or OE = V IH

ILO Output Leakage Current - - ±1.0 ~

VOUT= 0 - Voo

10H Output High Current V OH = 2.4V -1.0 - - rnA

10L Output Low Current VOL = O.4V 2.1 - - rnA

CE = V IL , lOUT = OrnA Min. - - 100

10001 tcycle

Operating Current

Other Inputs = VIHN IL 11ls - 15 - rnA

CE = 0.2V, lOUT = OrnA Min. - - 90

10002 tcycle

Other Inputs = VIHN IL 11ls - 10 -

100S1 CE = V IH , Other Inputs = VIHN IL - - 3 rnA

Standby Current CE = Voo - 0.2V Ta = 0 - 70°C - - 60

100S2 Voo = 2.0V - 5.5V IlA

Ta = 25°C - 4 8

Capacitance* (Ta = 25°C, f = 1.0MHz)

SYMBOL PARAMETER TEST CONDITION MAX. UNIT

C IN Input Capacitance V IN = GND 10

pF

C OUT Output Capacitance V OUT = GND 10

*This parameter is periodically sampled and is not 100% tested.

PREJ,.IMINARY TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC. A-151

TC554161 FTLlTRL-70U85U1 OL Static RAM

AC Characteristics (Ta =0 - 70°C, Voo =5V±10%)

Read Cycle

TC554161FTL/TRL

SYMBOL PARAMETER -70L -85L -10L UNIT

MIN. MAX. MIN. MAX. MIN. MAX.

tRc Read Cycle Time 70 - 85 - 100 -

tAcc Address Access Time - 70 - 85 - 100

tco CE Access Time - 70 - 85 - 100

tOE OE Access Time - 35 - 45 - 50

tSA UB, LB Access Time - 35 - 45 - 50

tOH Output Data Hold Time from Address Change 10 - 10 - 10 -

ns

tCOE Output Enable Time from CE 10 - 10 - 10 -

tOEE Output Enable Time from OE 5 - 5 - 5 -

tSE Output Enable Time from UB, LB 5 - 5 - 5 -

too Output Disable Time from CE - 25 - 30 - 35

to DO Output Disable Time from OE - 25 - 30 - 35

tso Output Disable Time from UB, LB - 25 - 30 - 35

Write Cycle

TC554161 FTL/TRL

SYMBOL PARAMETER -70L -85L -10L UNIT

MIN. MAX. MIN. MAX. MIN. MAX.

twc Write Cycle Time 70 - 85 - 100 -

twp Write Pulse Width 50 - 55 - 60 -

tcw Chip Enable to End of Write 60 - 70 - 80 -

tsw UB, LB Enable to End of Write 50 - 55 - 60 -

tAs Address Setup Time 0 - 0 - 0 - ns

tWR Write Recovery Time 0 - 0 - 0 -

tos Data Setup Time 30 - 35 - 40 -

tOH Data Hold Time 0 - 0 - 0 -

tOEw Output Enable Time from RIW 5 - 5 - 5 -

toow Output Disable Time from RIW - 25 - 30 - 35

AC Test Conditions

Input Pulse Levels 2.4V/0.6V

Input Pulse Rise and Fall Time 5ns

Input Timing Measurement Reference Levels 1.5V

Output Timing Measurement Reference Levels 1.5V

Output Load 1 TTL Gate and C L = 100pF

A-152 TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC. PRELIMINARY

Static RAM TC554161 FTLfTRL-70U85U10L

Timing Waveforms

Read Cycle (1)

ADDRESSES

UB,LB

Dout--------------~----------~~

Write Cycle 1 (4) (R/W Controlled Write)

ADDRESSES

twp tWR

RNV

UB, LB

Hrgh Impedance

Dout

Din (5) Data Stable (5)

PRELIMINARY TOSHIBA AMERICA ELECTRONIC COMPONENTS. INC. A-153

TC554161 FTlJTRL-70U85U10L Static RAM

Write Cycle 2 (4) (CE Controlled Write)

ADDRESSES

RIW

US, LS

High Impedance

Dout------------------------~

Din (5) (5)

Write Cycle 3 (4) (UB, LB Controlled Write)

ADDRESSES

US. LB

ance

Dout------------------------~

Din (5) (5)

A--154 TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

PRELIMINARY

Static RAM TC554161 FTLJTRL-70U85U1 OL

Notes:

1. RNJ is high for read cycles.

2. If the CE low transition occurs coincident with or after the RN.J low transition, outputs remain in

a high impedance state.

3. If the CE high transition occurs coincident with or prior to the RN.J high transition, outputs remain

in a high impedance state.

4. If OE is high during a write cycle, the outputs are in a high impedance state during this period.

5. The I/O may be in the output state during this time; therefore input signals of opposite phase must not be applied.

PRELIMINARY TOSHISA AMERICA ELECTRONIC COMPONENTS. INC. A-155

TC554161FTUTRL,.70U85U1 OL Static RAM

Data Retention Characteristics {Ta = 0 - 70°C}

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V OH Data Retention Supply Voltage 2.0 - 5.5 V

IOOS2 Standby Current

IV OH =3.0V - - 30*

JlA

I V OH = 5.5V - - 60

tCOR Chip Deselect to Data Retention Mode 0 - - ns

tR Recovery Time 5 - - ms

*6J.lA (max.) Ta = 0 - 40°C

CE Controlled Data Retention Mode

Voo DATA RETENTION MODE

4.SV

Voo-O.2V

GND

Note:

1. If the V1H of CE is 2.2V in operation, during the period that the Voo voltage is going down from 4.5V to 2.4V, IOOS1

current flows.

A-156 TDSHIBA,AMERICA ELECTRONICCOMPC!JNENTS, INC. PRELIMINARY

You might also like

- TC554161FTL 70Document8 pagesTC554161FTL 70Técnico 04 LógicaNo ratings yet

- TC551001BPL 70L ToshibaDocument8 pagesTC551001BPL 70L ToshibaKalees WaranNo ratings yet

- IS61LV2568L: 256K X 8 High-Speed Cmos Static RamDocument14 pagesIS61LV2568L: 256K X 8 High-Speed Cmos Static RamTan Hung LuuNo ratings yet

- TC58NVG0S3ETA00Document65 pagesTC58NVG0S3ETA00Freddy AmayaNo ratings yet

- FlashMemory-DataSheets Atmel Elenota - PLDocument13 pagesFlashMemory-DataSheets Atmel Elenota - PLriegerautoNo ratings yet

- Description: 2 GBIT (256M × 8 Bit) Cmos Nand E PromDocument65 pagesDescription: 2 GBIT (256M × 8 Bit) Cmos Nand E PromLuis SantosNo ratings yet

- Description: 1G BIT (128M 8 Bit) Cmos Nand E PromDocument52 pagesDescription: 1G BIT (128M 8 Bit) Cmos Nand E PromLuis SantosNo ratings yet

- TC58NVG2S3ETA00Document70 pagesTC58NVG2S3ETA00Freddy AmayaNo ratings yet

- 3A Ultra Low Dropout Linear Regulator: General DescriptionDocument12 pages3A Ultra Low Dropout Linear Regulator: General DescriptionLoengrin MontillaNo ratings yet

- Hy628100alg 70Document9 pagesHy628100alg 70Claudiney BricksNo ratings yet

- EOL Product: HM5216165 SeriesDocument52 pagesEOL Product: HM5216165 SeriesfurqanhamidNo ratings yet

- TC58NVG3S0FTA00Document73 pagesTC58NVG3S0FTA00varimasrNo ratings yet

- Description: 1 GBIT (128M × 8 Bits) Cmos Nand EepromDocument34 pagesDescription: 1 GBIT (128M × 8 Bits) Cmos Nand Eeprommiloud1911No ratings yet

- EL5166, EL5167: FeaturesDocument16 pagesEL5166, EL5167: FeaturesЕвгений ИвановNo ratings yet

- Microcomputers, Inc.: RN ( FfirnwDocument4 pagesMicrocomputers, Inc.: RN ( FfirnwPrzemysław WójcikNo ratings yet

- Description: 2 GBIT (256M × 8 Bit) Cmos Nand E PromDocument65 pagesDescription: 2 GBIT (256M × 8 Bit) Cmos Nand E Promsuan kwang Tan100% (1)

- Toshiba 8GB NAND TC58NVG3S0FTAI0 PDFDocument73 pagesToshiba 8GB NAND TC58NVG3S0FTAI0 PDFMilan MilenovicNo ratings yet

- Toshiba-Tc58bvg0s3hta00 C113406Document44 pagesToshiba-Tc58bvg0s3hta00 C113406ivan lopezNo ratings yet

- Description: 1G BIT (128M 8 Bit) Cmos Nand E PromDocument52 pagesDescription: 1G BIT (128M 8 Bit) Cmos Nand E PromLademir FerreiraNo ratings yet

- Cy7c1019cv33 12zcDocument8 pagesCy7c1019cv33 12zcTuhin KarakNo ratings yet

- TL 084 CNDocument8 pagesTL 084 CNNiranjan kumarNo ratings yet

- Single-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington OptocouplersDocument15 pagesSingle-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington Optocouplersdevrim.kosalNo ratings yet

- TLP551 Datasheet en 20190624Document7 pagesTLP551 Datasheet en 20190624jose antonio iglesias infantesNo ratings yet

- AT28HC256Document16 pagesAT28HC256Harris RaoNo ratings yet

- As7c256a 10TCNTR PDFDocument51 pagesAs7c256a 10TCNTR PDFjan ZielinskiNo ratings yet

- 128K X 8 Low Power Cmos Static Ram: Description FeaturesDocument11 pages128K X 8 Low Power Cmos Static Ram: Description Featuresvanhuong87No ratings yet

- 7SJ64 13.8kV Busbar ProtectionDocument2 pages7SJ64 13.8kV Busbar ProtectionBalajiNo ratings yet

- Description: 2 Gbit (256M × 8 Bit) Cmos Nand E PromDocument53 pagesDescription: 2 Gbit (256M × 8 Bit) Cmos Nand E PromMiguel CastilloNo ratings yet

- Features General Description: High Input Voltage, Low Quiescent Current, 150ma LDO RegulatorDocument20 pagesFeatures General Description: High Input Voltage, Low Quiescent Current, 150ma LDO RegulatorRoxanaDelcampoNo ratings yet

- 16K (2Kx8) Parallel Eeproms AT28C16: FeaturesDocument12 pages16K (2Kx8) Parallel Eeproms AT28C16: FeaturesWilmer OscoNo ratings yet

- 256K X 4 Static RAM: PreliminaryDocument10 pages256K X 4 Static RAM: PreliminaryedgarlibanioNo ratings yet

- Tc58dvm92a5ta00 ToshibaDocument38 pagesTc58dvm92a5ta00 ToshibaLorenzo TorresNo ratings yet

- cd74hc4051 q1Document18 pagescd74hc4051 q1richardleonn2No ratings yet

- 64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesDocument12 pages64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesbacagratisNo ratings yet

- HY628400 HynixSemiconductorDocument9 pagesHY628400 HynixSemiconductorHamidNo ratings yet

- Eeprom At28c64Document14 pagesEeprom At28c64Manuel FonsecaNo ratings yet

- TC58NVG2S0FTA00 ToshibaDocument71 pagesTC58NVG2S0FTA00 ToshibaMang Asep BuhoyNo ratings yet

- Features: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifierDocument13 pagesFeatures: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifiersdasfaNo ratings yet

- CAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionDocument11 pagesCAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionLaboratorio GTO Perú S.A.C.No ratings yet

- Toshiba Confidential Tc58Nvg5D2Fta00: DescriptionDocument65 pagesToshiba Confidential Tc58Nvg5D2Fta00: DescriptionNoel Alejandro Cordova RangelNo ratings yet

- AT28C16Document12 pagesAT28C16Mike EsquivelNo ratings yet

- HCPL 061aDocument19 pagesHCPL 061aMaria TzagarakiNo ratings yet

- LF411Document13 pagesLF411intan nur indahNo ratings yet

- Datasheet AP7175Document14 pagesDatasheet AP7175Edwin SorianoNo ratings yet

- IS41LV16100B: 1M X 16 (16-Mbit) Dynamic Ram With Edo Page ModeDocument23 pagesIS41LV16100B: 1M X 16 (16-Mbit) Dynamic Ram With Edo Page ModeIldevan JoséNo ratings yet

- TCL Chassis M113 SINGER SCT-29128 - Service - ManualDocument90 pagesTCL Chassis M113 SINGER SCT-29128 - Service - ManualAjith Priyalal75% (4)

- TVL ST23 04 Ad0Document9 pagesTVL ST23 04 Ad0coulsonpfilNo ratings yet

- Industrial Inverter Inverter For Air Conditioner IGBT/Power MOSFET Gate Drive IH (Induction Heating)Document9 pagesIndustrial Inverter Inverter For Air Conditioner IGBT/Power MOSFET Gate Drive IH (Induction Heating)El Riz El SammyNo ratings yet

- TC58NVG1S3BFT00 - TC58NVG1S8BFT00Document37 pagesTC58NVG1S3BFT00 - TC58NVG1S8BFT00Freddy AmayaNo ratings yet

- INPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Document8 pagesINPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Isaac CostaNo ratings yet

- Decodificadorde1para8 DemultiplexadorDocument8 pagesDecodificadorde1para8 DemultiplexadorAndré Luís KirstenNo ratings yet

- Features: High Performance Pin DriverDocument11 pagesFeatures: High Performance Pin DriverЕвгений ИвановNo ratings yet

- Bro Avag - HCPL 314jDocument14 pagesBro Avag - HCPL 314jRomusNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Lm2674 Simple Switcher Power Converter High Efficiency 500-Ma Step-Down Voltage RegulatorDocument35 pagesLm2674 Simple Switcher Power Converter High Efficiency 500-Ma Step-Down Voltage RegulatorTécnico 04 LógicaNo ratings yet

- UntitledDocument39 pagesUntitledTécnico 04 LógicaNo ratings yet

- 74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesDocument8 pages74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesrzvNo ratings yet

- Sn74ahc1g125 SN74LVC1G125Document24 pagesSn74ahc1g125 SN74LVC1G125Técnico 04 LógicaNo ratings yet

- IV2412Document2 pagesIV2412Técnico 04 LógicaNo ratings yet

- Design of Electrical Apparatus Solved ProblemsDocument15 pagesDesign of Electrical Apparatus Solved ProblemsnandhakumarmeNo ratings yet

- EDEPRO0146 0116 1 en Prospekt Multicond Data SheetDocument10 pagesEDEPRO0146 0116 1 en Prospekt Multicond Data SheetMartín LópezNo ratings yet

- Capacitor ValueDocument6 pagesCapacitor ValueP.Rajan GuruNo ratings yet

- Ti Ldo PresentationDocument22 pagesTi Ldo PresentationDebolina GhoshNo ratings yet

- GC-1F DRH 4189340472 UkDocument122 pagesGC-1F DRH 4189340472 UkYONNATHANNo ratings yet

- Mechanical Electromechanical Switches and Relay and Other Interfacing DevicesDocument21 pagesMechanical Electromechanical Switches and Relay and Other Interfacing DevicesRose Anne Delos SantosNo ratings yet

- First Issue 13/1/2021 0: A.Fathy A.AbdelrazikDocument7 pagesFirst Issue 13/1/2021 0: A.Fathy A.AbdelrazikAhmed El HadidyNo ratings yet

- Metallwarenfabrik Gemmingen GMBH: We Welcome You To The Presentation of "Civil Genset Control Unit"Document23 pagesMetallwarenfabrik Gemmingen GMBH: We Welcome You To The Presentation of "Civil Genset Control Unit"abathunNo ratings yet

- Permanent Magnet Synchronous GeneratorDocument5 pagesPermanent Magnet Synchronous GeneratorSanela BeganovicNo ratings yet

- Clap SwitchDocument24 pagesClap Switchbalvendra0350% (2)

- Chapter 2Document16 pagesChapter 2Aly AshrafNo ratings yet

- Lec 6 & 7 - Transmission Line ProtectionDocument34 pagesLec 6 & 7 - Transmission Line ProtectionAwil MohamedNo ratings yet

- Safety Precautions in Handling Elecrical AppliancesDocument2 pagesSafety Precautions in Handling Elecrical AppliancesKunal MehraNo ratings yet

- P.E.S. College of Engineering, Mandya - 571 401Document2 pagesP.E.S. College of Engineering, Mandya - 571 401manoharaNo ratings yet

- The Capacitor of CapacitanceDocument2 pagesThe Capacitor of CapacitanceFarid AhmedNo ratings yet

- Defect Management Guidelines - DraftDocument18 pagesDefect Management Guidelines - DraftqianghoNo ratings yet

- Super Trex VFD Shielded Power CableDocument1 pageSuper Trex VFD Shielded Power CableAmr EidNo ratings yet

- HVT CatalogDocument2 pagesHVT CatalogGerardo Roman RomanNo ratings yet

- Eee-Viii-electrical Design, Estimation and Costing (10ee81) - Question PaperDocument6 pagesEee-Viii-electrical Design, Estimation and Costing (10ee81) - Question PapersriramNo ratings yet

- 2032-10 - E Gazette SLDocument3 pages2032-10 - E Gazette SLhimaliNo ratings yet

- SIE DS TPS411 ExternalDocument4 pagesSIE DS TPS411 ExternalCarlos HernándezNo ratings yet

- 742RDocument19 pages742Rj31ocNo ratings yet

- Hubbel ATS PDFDocument16 pagesHubbel ATS PDFalexiuteodorNo ratings yet

- Hidraulico 416e CaterpillarDocument12 pagesHidraulico 416e CaterpillarFabian Ignacio Cifuentes Alcaide100% (2)

- C5440 PanasonicSemiconductorDocument2 pagesC5440 PanasonicSemiconductorteniNo ratings yet

- Danfoss Pressure Switch KP34, KP35, KP36, KP37Document8 pagesDanfoss Pressure Switch KP34, KP35, KP36, KP37Parinpa Ketar100% (1)

- Customer Manual 1Document36 pagesCustomer Manual 1AliNo ratings yet

- 20039-11 B11R D11C UniverseDocument225 pages20039-11 B11R D11C UniverseDaniel Alex SánchezNo ratings yet

- Mge Ups Systems Ex 7 RT 3 1 Manuel D UtilisationDocument38 pagesMge Ups Systems Ex 7 RT 3 1 Manuel D Utilisationali azigNo ratings yet

- N2XRYDocument5 pagesN2XRYicalcalNo ratings yet