Professional Documents

Culture Documents

Microprocessor Module 2 Part1

Microprocessor Module 2 Part1

Uploaded by

Jyothika0 ratings0% found this document useful (0 votes)

5 views7 pagesmicroprocessor

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentmicroprocessor

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

5 views7 pagesMicroprocessor Module 2 Part1

Microprocessor Module 2 Part1

Uploaded by

Jyothikamicroprocessor

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 7

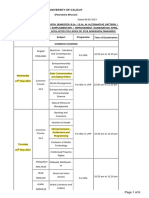

te Micronrocesson Communication

To understand function of various signals of 8085, it is necessary to examine the

process of communication between the microprocessor and memory and the timings of

these signals in relation to system clock.

+ Figure 7.1 shows how the microprocessor fetches or gets a machine code from memory.

> Step 1: PC places 16-bit address 200SH of the memory location on the address

bus

> Step 2: The control unit sends the Memory Read control signal (MEMR, active

low) to enable the output buffer of the memory chip.

> Step 3: The instruction (4FH) stored in the memory location is placed on the data

bus and transferred to instruction decoder of the microprocessor.

> Step 4: The instruction is decoded and executed according to the binary pattern

of the instruction.

Figure 7.1: Microprocessor Communication with Memory

Microprocessor Operation

¢ The microprocessor external communication functions can be divided into three

categories:

1) Memory Read and Write

2) 1/0 Read and Write

3) Request Acknowledge

« These functions are further divided into various machine cycles - Opcode Fetch,

Memory Read, Memory Write, 1/0 Read, 1/0 Write

* In this section, we will study basic machine cycles -Read, Opcode Fetch, Memory

Memory Write, 1/0 Read, 1/0 Write

Opcode Fetch Machine Cycle

© The first operation in any instruction is Opcode Fetch

© Opcode fetch cycle is called the M1 cycle and has four T-states.

* 8085 uses the first three states T1-T3 to fetch the code and T4 to decode and

execute the opcode.

* There are some instructions which have six T-states

For eg. MOV C, Ais one-byte instruction and has 1 machine cycle i.e. Opcode Fetch

© Figure 7.2 (a) & (b) shows the timing diagram of Opcode Fetch Machine Cycle with 4

& 6 T-states resp.

Here [PC]H & [PC]L stands for higher order byte of PC & lower order byte of PC resp.

Figure 7.2: (b) Opcode Fetch Machine Cycle with 6 T-states

Memory Read Machine Cycle

‘The memory read machine cycle is executed by the processor to read a data byte

from memory.

The processor takes 3T states to execute this cycle.

The instructions which have more than one byte word size will use the machine

cycle after the opcode fetch machine cycle.

Figure 7.3 shows the timing diagram of Memory Read Machine Cycle

Figure 7.3 Memory Read Machine Cycle

Memory Write Machine Cycle

¢ The memory write machine cycle is executed by the processor to write a data

byte in a memory location.

© The processor takes 3T states to execute this machine cycle.

Figure 7.4: Memory Write Machine Cycle

1/0 Read Machine Cycle

* The 1/0 Read cycle is executed by the processor to read a data byte from 1/0 port or

from the peripheral, which is 1/0, mapped in the system.

«The processor takes 3T states to execute this machine cycle.

« The IN instruction uses this machine cycle during the execution.

Figure 7.5: 1/0 Read Machine Cycle

1/0 Write Machine Cycle

«© The 1/0 write machine cycle is executed by the processor to write a data byte in the

1/0 port or to a peripheral, which is 1/0, mapped in the system.

«The processor takes 3T states to execute this machine cycle.

* The OUT instruction uses this machine cycle during the execution.

|S

C7

f

pt

4

Figure 7.6: 1/0 Write Machine Cycle

Instruction Format

* An instruction is a command to the microprocessor to perform a given task on a

specified data.

* Each instruction has two parts: one is task to be performed, called the operation

code(opcode), and the second is the data to be operated on, called the operand,

© The operand (or data) can be specified in various ways. It may include 8-bit (or 16-

bit ) data, an internal register, a memory location, or 8-bit (or 16-bit) address. In

some instructions, the operand is implicit.

Instruction Word Size:

© 8085 Instruction set is classified into the following three groups according to word

size or byte size.

1. One Byte Instructions:

« A 1-byte instruction includes the opcode and the operand in the same byte. For

example:

Task Opcode | Operand | Hex Code

Copy the contents of the accumulator in register C_| MOV GA AFH

Add the contents of register B to the contents of

the accumulator ADD 7 ae

Invert (Complement) each bitin the accumulator _[|_CMA 2FH

* These instructions are 1-byte instructions performing three different tasks.

© Inthe first instruction, both operand registers are specified.

to

In the second instruction, the operand B is specified and the accumulator is

assumed,

* In third instruction, the accumulator is assumed to be the implicit operand.

«These instructions are stored in 8-bit binary format in memory; each requires one

memory location.

. Two Byte Instructions:

© Ina 2-byte instruction, the first byte specifies the operation code and the second

byte specifies the operand. For example:

Task Opcode | Operand eas

Toad an 8-bit data byte in 3EH | First Byte (Opcode)

the accumulator MVE | A32H | 32H _| Second Byte

Load an 8-bit data byte in 06H | First Byte (Opcode)

register B MVI | B.F2H | 2H | Second Byte

© These instructions would require two memory locations each to store the binary

codes,

Three Byte Instructions:

* Ina 3-byte instruction, the first byte specifies the opcode, and the following two

bytes specify the 16-bit address. The second byte is the low-order address and the

third byte is the high-order address. For example:

Task Opcode | Operand | (He

, BAH _| First Byte (Opcode)

Lois contenis‘otaneincry LDA | 2050H | SoH | Second Byte

2050H into A Sarees

Transfer the program C3H_| First Byte (Opcode)

sequence to memory location | jMP | 2085H | 85H | Second Byte

2085H_ 20H __| Third Byte

© These instructions would require three memory locations each to store the binary

codes,

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 2023-05-08 16 - 13 - 33 - Time7840Document6 pages2023-05-08 16 - 13 - 33 - Time7840JyothikaNo ratings yet

- Microprocessor16 2Document2 pagesMicroprocessor16 2JyothikaNo ratings yet

- Rdbms IV Bca Nov 2019Document3 pagesRdbms IV Bca Nov 2019JyothikaNo ratings yet

- RDBMS Bca IvDocument2 pagesRDBMS Bca IvJyothikaNo ratings yet