Professional Documents

Culture Documents

Signetics

Signetics

Uploaded by

Erasmo Franco0 ratings0% found this document useful (0 votes)

33 views68 pagesOriginal Title

68000_Signetics

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

33 views68 pagesSignetics

Signetics

Uploaded by

Erasmo FrancoCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 68

Signetics 68000

16-/32-Bit Microprocessor

Product Specification

miary

Customer Specie Products

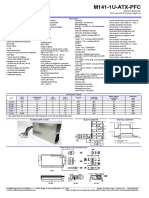

DESCRIPTION PIN CONFIGURATION PIN CONFIGURATION

“Tho 68000 is the fet imlamentaton of

the 68000 182 bit microprocessor ach

tecture Th 68000 has a 16-0 data bus

ard24 bt address bus, whthotularch-

tecture provides for 82°08 adose and

databvses, tis completely code-compat- “ Em

‘ible with the 68008 8-bit data bus Lal je) 0

implementation of the 68000 and is down- oe je 7

ward todo-compaile wily the. 68010 Si fe

Virval extension andthe 68020 32:58 in- = ia»

plomonttion of the architecture, Ary : EB

Geormode programs wittn using tho | woe Be

{8000 instruction sot wil un unchanged

fon the 68008, 69010, and 68020, Tiss om [al

possible because the user programming a 3) ow

‘model is identical for all four processors oucK jj ow

and the instruction sets are proper a ja os

‘sub-sels of the complete architecture. ‘waxcx f3) ono ee ee

‘The 68000 possesses an asynchronous m a= 2 & Sa

bus structure wih « 24-08 aderose Bos ve Fa a 32 ae

anda 16> data bus, es fa an i8 38

“The resources available to the 68000 user x0 fa) vee 1 a

onsst othe folowing: wc Fa a ie g

+17 32-bit data and address rege rr Fa ee §

Bex 3

‘= 16MB dlrect adressing registers vx fa aw ae 2

+56 powertl instruction types : fs ae oe £

+ Operations on five main data types iad Bae ne 2

+ Memory-mapped VO = Fa) aw a #

#14 addressing modes wr fay ass eal ie

As showninto programming modelFigg | IS a ger :

tre 1), the 66000 ofers ston 32-31 fo Bala a ee

rogisters and a 32-bit program counter. ret fal a0 2 ie eau

Thott ight egistore (00-07) ae used ro FA a BS 2

25 data ogists for byte (6-2), word e fp ae ie 5

(16-bit), and long-word (32-bit) opera- " Fa ar BR 5

Hons, Tho second sot of saven registers - a

(A0- AS} and house stackpontr (USP) : fa

tay be wed as software stack pointers 7 Bs

and base adéressroisters. fh adaton,

tho rogitrs may be used for word and

fong-word operations, All of the 16

repitors may bo vsed a8 ndex roiters

oly 25, 1986 353 853-0866 84748

‘Signotcs Matary Customer Spectc Products

Product Speciation

16-/32-Bit Microprocessor

68000

ORDERING INFORMATION inpanisront bvgpa om ces

ae a Proererabemriaeeee

PTION “A CODE = (SSP) are also available to the programmer.

enoaatn sins | Thearopases shen

stem cumisosininie | — earn ia eee | ever

0 ron | natn tigen ree

cece ct ee

Ce 3 Lead ‘Zero (2), overflow (V), and camy (C). Adkition-

serncanetce eran snc] Stamnes,

ose ote _| Sihemsaaneatan

f qe Ebeessoesswessneteeeereseese] ooo] acetal

E 2s Sn Ha

is aoe Rcate sn stamsncasten

Le Figure 2. Supervisor Programming Model Supplement

lelemes faroren aeeriomar

bE qs TRE RW DT PTT Te

2, tenener || cleo sro]

ree eee re ae —

ee

Figure 1, User Programming Medat

Figure 3, Status Register

oly 25, 1986

‘Signetcs Miltary Customer Specie Products Product Specification

16-/32-Bit Microprocessor 68000

Table 1. Addressing Modes Data Types and Addressing

"ADDRESSING MODES ‘SYNTAX

Register direct addressing

Data rogistr direct Da

‘Acsiross rogistor crock an

‘Absolute data eddressing

Absokie short sow

‘Absolut long mo

‘Program counter relative addressing

Folatve with otsot 644°C)

Platve with index and ofsat &4(PCXn)

Register indirect addressing

Register indroct an)

Postineromont rogistriniroct (anys

Prodocromentrogiserindiroct (an)

Fogistor indirect wit offset (AN)

Indoxod rgisiorindroct with offeot efAnX0)

‘immediate data addressing

Immediate too

Quick immediate ne

implied addressing

Implied register SRIUSPISPIPC

NOTES:

Dn = Datarogistor

[An = Address rogisior

Xn = Addross or data register used as index

rogstor

SR ~ Slats rogistr Ste

PC = Program countor

July 25, 1986

‘Stack pointer

User stack pointer

Etecive Adcross

‘bit offset (deplacoment)

= Te2itotistispiacomen)

985

Modes

Five basic data types aro supported. Thoso

ata types ar

he

‘© BCD digits (4 bits)

1 Bytes (8 bit)

© Words (16 bite)

© Long words (32 bite)

In adcton, operations on other data types

suchasmemory addossos, statis word data,

tc, 79 povided inthe instruction sat.

‘The 14 addroes modes, shown in Table n=

‘clude ic basie ypes:

= Register direct

Rogier indirect

(© Absolute

‘* Program counter relative

‘+ immediate

© implied

Included in the roistr indioet addressing

‘modes the capably to do preincremonting,

predecrementing, ofsttng, and indexing.

"The program counter relatvo modo can also

be modified via Indexing and olsottng

Signetes Mitary Customer Specie Products

Product Specification

16-/32-Bit Microprocessor

68000

Table 2. Instruction Set Summary

MNEMONIC DESCRIPTION

"BOD ad decimal wih extend

‘400 Ad

AND Logieal AND

asl ‘Avitymote shitiot

ASA, ‘Avitumate shttright

oe Branch conditionally

CHG Bittost and change,

BOLA Bittst and clear

BRA Branch aways

eseT Bittost and cot

BSA Branch to eubeoutine

eTsT, Bitest

HK ‘Gheck egislor agains baunde

oun Clear operand |

cue Compare

Bcc Test condlion, decrement and branch

pis. Signed vide

oy, Unsigned civ

EOR Exclusive OR

exc Exchange registers

ext Sign exiona

MP Jump

usr Jump © subroutina

CEA. Load etoctve accross

NK Unk stack

tt Logica sitet

ey Logical shit ight

MOVE Move source 1 dastnaton

MULS Signed multip'y

Mutu Unsigned multiply

BCD ‘Negato decimal with xtand

NEG. Negate

NOP, No operation

Nor. ‘One's comploment

OR Logical OR

PEA Push etlocive across

RESET Rosot extemal cavices

ROL Rotate lot without excond

FOR Fotato right witoutextond

ROXL Fotato lot wih extend

ROXR, tate right wih extond

RTE. Return rom exception

RTR Rot and retore

RTS. Rotun rom subroutine

‘S800 “Subtract decimal with extnd

Sco ‘Setcondtonal

stop Stop

SUB Subtract

SWAP. ‘Swap data register halves

TAS Test and set operanc

TRAP Trap

TRAPV ‘Trap on overtiow

18T Test

UN Tain

Jy 28, 1988

366

Instruction Set Overview

‘The 68000 instruction sets shown in Table 2,

‘Some addtionalinstucions ae vaiaons, of

subs0ts of theso, and they appear in Tabo 3,

‘Special omphasis has boon givon tothe in

struction set's supporto stucturedhighevel

languages to tacitate ease of programming.

Each instucton, with few excoptons, ope:

ates on bytes, words, and long words and

‘most instructions can use any ofthe 14 ad-

crossing modes. Combing instruction ypes,

‘ata ypes, and addressing medes, over 1000,

useful instructions are provided. These in-

structions include signed and unsigned, mut

iy and divide, “quick” arithmetic operations,

BCD artimat, and expanded operations

(trough waps)

Sighotics Miltary Customor Specie Products

Product Specification

16-/32-Bit Microprocessor

68000

Table 3. Variations of Instruction Types

INSTRUCTION

By VARIATION DESCRIPTION

‘ADD ADD a

‘ADA. Aad access

‘4000 Add quick

‘ADO Ad immodiate

‘AD0x ‘Add with extond

"AND ‘AND Logical AND

‘ANDI [AND inmodato

‘ANDI 1 CCR [AND immaciate to condtion codes

ANDI to SR. AND immociato to ropstor status

one one ‘Compare

cMPA Compare adeeoss

‘MPM ‘Compare memory

cM Compare immodiato

OR OR ExciusivoOR

ORI Exclusiv OR immediats

EOAl con Exclsivo-OR immeciats to condition codes

EORI to SAL Exclsive-OR inmaciats to status regstor

MOVE WOVE ‘Wovo source to destination

MOVEA Move address

NOVEM Move multiple resistors

Mover Move peripheral data

Move Move quick

MOVE tom SR | Move from status register

MOVE CCR | Movoto concition codes

MOVE USP Movo usor stack pointer

NEG NEG ‘Negate

NEGX Negate with extond

on oR Logical OR

onl OF immediate

‘OF to COR ‘OF immediate to condition codes

OAIw SR OR immediate to status register

SUB SUB Subvact

SUBA Subvact addeess

suai Subract immediate

suBo Subvact quick

SUBK Subvact with extond

July 25, 1986

ser

Signotcs Miltary Customor Specie Products

Product Speciation

16-/32-Bit Microprocessor

68000

DATA ORGANIZATION AND

ADDRESSING CAPABILITIES

“This section contains a description ofthe ragis-

tors andthe data organization af tho 68000,

Operand Size

Sparano a owe: a

foquals 8 bits, a word equals 16 bits, an

werd equals 2bits. Th oporandsize for ach

instuctonis eithor explicit encodedin the in-

struction or imply defined bythe intrsction

poraton, Implicit inskuetions support some

subset ofall roo sizes.

Data Organization In Registers

The eight data ristors support data operands

of1,8, 16, 0°32 its. The seven address regis.

ters logether withthe stackpointerssuppertad-

ross operands of 32 bits

Data Registers

Each data ropstris 32 bits wide. Byte oper:

ands occupy the low-order 8 its, word oper

ands the low ordor 16 bts, andlong. word oper-

ands the ontre 32 bats, Tho loast significant bt

Isaddossed.as bit 2or0:the most signiicantbt

is addrossod as 31

Won a dataregistoris usod as ethora source

‘destination operand, only the appropriate

low-order porton is changed; the remaining

high-order portonis nether usodnor changed.

‘Address Registers

Each address registor and tho stack pointe is

‘32bis wide and holds a M32 bt adress. Ad.

(ress rogisars do not suppor the sized oper-

lands. Theretore, whon an adcross rogistor fs

used as a source operand, ether the low-order

Word oF the entre long: word operand is vsod

\depencing on tho operation size, When an ad

ress rgistoris used as the destination oper

and, ha entre registor's affected regardless of

the operation size. the operation size is word,

any otheroperands aro sign extended 32bits

belors the operation is performed,

aly 25,1986

a Ze

Figure 4, Word Organization In Memory

Data Organization in Memory

Bytos are individually addressable wit the

high-order byte having an even address the

‘same as tho word, as shown in Figure 4. The

low-ordor byte has an odd adress that i one

Count highor than the word adcress,Instruc-

tions and muttbyie data are accessod only on

‘word oven bys} boundaries. along-wordda-

{ums located at aderessn (a even), than tho

socondwordol hatdatumislocatedatadcross

nae

‘The datatypes supported by the 62000 are: bt

data, ntoger data of 8, 16, of 32 bits, 32-bit ad-

srossos and binary-coded decimal data, Each

‘ofthese datatypes is putin momory, as shown

in Figure 5. The numbers inccato the ordor in

Which the data wouldbe accosted rom tha pro-

Addressing

Instructions forth 68000 contin two Kinds of

informaton: the ‘ype of function to be pet-

formed and the locaton of tha operands) on

hich to pertorm that function, The methods

‘Usedtoloeate address) the oporandks) aro

plained inthe folowing paragraphs,

Instructions specty an operand location in one

ofthroe ways:

Register spociicaton the umber of he rogie-

tors given inthe rogister Fld of the instruc-

tion,

Efiocive addr — uso theciterontefocsve

addressing modes.

Implicit rotoronce th dafaon of contain in-

structions impbos the us of spoctc regis

Instruction Format

Instuetions are from oneto five wordsinfongth

2s shown i Figure 6, Tho length ofthe inetve-

tion and the operation tbe performedis spect

fied by he frst word o he intructon which is

caled tho operation word. Theremainngwords

further spect the operands. These words are

‘iherimmodiate operands or extensions tothe

‘fective accross mode spocfiod in the opera:

ton word

Program/Data References

‘The 68000 separates mamory references into

‘wo classes: program references and data ret

‘erences. Program reforoncas as the nam

plies, ar references i that section of momory

thatcontans the program being executed. Data

relerences refer to that secion of memory that

contains data Oporand reads ar from te data

space excoptinthecase ofthe rogram counter

Felative addressing mode. All operand writs

‘aro tothe data space,

Register Specification

‘Tho ogistrfild within an nsbucton specifies

the register to bo used. Other fel within tho

instruction specily whethor the regisior so-

lected is an adress or data register and how

the register i tobe used.

‘Signetice Miltary Customer Specie Products

16-/32-Bit Microprocessor

Product Speciation

68000

Or OATA-sorrE-s 8

roe eee

WEOER OATA-s TE =a m8

wow oe ee eee

eres ise erres

eve eves

---— sooness 2

TSB = OST SGHACANT RT — Us «LEAST SGHACANT BT

count oan

a

= ° aco co eco3

= sso

eco4 2005 coe ‘ec07

WD OST SGIERCANT GT 5D LEAST HGMRCANT OT

Figure 5. Memory Data Organization

sly 25, 1986

369

‘Signotics Miltary Customer Specife Products

Product Speciation

16-/32-Bit Microprocessor

68000

wow

{RST WORD SECCIEE OPERATION AND MODES)

OF A EME ORTHO ORES)

SF ANY One OR TWO WORD,

‘DESTINATION EFFEGTVE ADDRESS ETENBION

‘tran one Ot Pwo WORD

Figure 6, Instruction Operation Word General Format

woot |

FFECHVE ADDRESS

7, Single-Etfective- Address Instruction Operation Word

Effective Address.

‘Moctinsructons spect tho locaton of an op

rand by using the efacivo address feldin the

‘peration word. For example, Figur 7 shows

the general format ofthe single-ofoctvo-ad-

{ress instruction operation word. The effective

adiress is composed of two 3-bit folds the

mode feld and the register fold, The valu in

the mode fold selects the citfront adcross

modes. The regstr fold contains the number

of a rogistr.

“Tho efoctive address eld may require adc

$nal information to uly speci the oporand

‘This additonal information, caled the elective

adress xtonsion, is contanedin the folowing

word or words ands considored part ofthe in

stuaton, as shown in Figute 6. The etlective

address modes are groupodinte tree catego:

Fes ogisor deact, memory addeossing, and

special

Register Direct Modoe

Tote otfoctve adcressing modes spect hat

tho operands in ono of 16 mulslunctionregis-

Data Register Direct — The operands inthe

data ogistorspeciiog by the allactve adress

r9gistor foe

‘Address Register Direct —Tho operandis in

the adctess rogistor specif by the atlactve

across register fle.

Memory Adéross Modes

‘Those otfectve adcrossing modes speci that

tho operands in memary and provide be sp-

‘ic adoss ofthe operand.

Address Register Indirect — Tho adds of

‘he operandisin the adéross register specified

aly 25, 1988

by he rogister fils. Tho roferonce is classed

‘asa data telerence withthe exception ofthe

jump and jump toroutine instuctons

‘Address Reglstor Indirect with Postincre-

‘ment — Tho addrass of the operand isin tho

address register specie by the register fad.

Alter the operand address is uso, itis incrom-

‘ntod by one, to, four depending on wheth-

for the siza of the operand is byt, word, oF

long.werd, tthe address rogistar ie tho stack

pointer and the operand size Is byto, tho ad

ress is incremented by two rather than one 1

oop te sack pointaronaword boundary. The

releronceis claseliod as a data relerence,

‘Address Register Indirect with Predocre-

ment — Tho address of the operandi in tho

address register speciid bythe rogsior fl.

Botore the operand adéross it uted itis e-

‘romantedby one, two, orfaur depending upon

whether the operand size it byte, word. ot

fong-word. I the address rogisor i te stack

pointer and tho operand sizo is byte, the ad-

‘ress is decremontod by two rather than one to

oop the stack pinta on awordboundsay. The

references claeied as a data reference,

Address Register Indirect with Diaplace-

ment — This addressing mode roquiras ono

word extension, Tho adsross of ho operand

isthe sum oftheaddiessin teaddress register

and tho sign-oxtonded 16-bit dlsplacemont in

tog in te extension word, Tho rtorence ls

classified as a data rtoronce with the excop-

‘on oftejumpandjump-to-subroutnginstruc-

tons,

‘Address Reglstor Indirect with Index — This

‘edressing modo roquires one word of exten-

370

sion, The across of he operand is tho sum of

theaddrossin headdress rogistr, the sign-ox-

tended displacement intager in the low-otdar

‘ightbits fhe extension word, and conto of

‘heindox registar. The reeroncels lasses

‘data oferonce withthe excnpton of the jump

and jumpto-subroutine instructions,

Special Address Modes

‘The special addross modos use the offociva

‘address register feld to spect tho spacial ad-

‘ossing mode instoad of a register number.

[Absolute Short Address — This adirassing

mode requires one word of extension. The ad-

‘tess ofthe oporandis the extonsion word, Tho

16-bit address is sign extonded befor i i

used. Thereferancoisclassiod aga datafoe

‘once with tho excoption of the jump and

jump-o-subroutre instructions,

‘Absolute Long Address — This addressing

‘made requires tuo words of extonson. The ad-

‘ess of the operand is dovolopod by tho con-

catonaton ofthe extonsion words, The high-o-

or par ofthe adetoss is tho fast oxtanson

‘word the low-order pat of tho adcress is tho

econdextonsion word. Theoferenceis class

fod as a data roforonce with the excopton Of

the jump an jump-to-subroutine instructions.

rogram Counter with Diaplacemont — This

adrssing mode roquires one word of exton

sion. Tho address of he operands the eum of

the address in tho program eounior and the

sign-extondad 16 bit splacoment intoger in

{he word, The value in tho program count is

the adcrass of to extonsion word, The role

‘once i classifodas a program reference

‘Signetics Miltary Customer Specific Products

Product Speciation

16-/32-Bit Microprocessor

68000

Table 4, Effective Address Encoding Summary

"ADDRESSING MODE MODE | REGISTER

Data vogistr direct (000 | Register number

‘Adsress rogistor direct 001 | Rogier umber

‘adress rgisior indirect (010 | _Registor umber

‘Aderoes rogisiorindat with postineromont O17 | Register number

"Adios register inact with prodoorment 100_ | Register number

[Adeross rogisarindroct wih displacement 101 | Register numbor

‘Adsross rglstor ineroct wih index 110 [_ Register number

‘Absolute short 1 (000

‘Absolut ong a oor

Program count with dlplacemant or 010

Program counter with index i on

Immediate it 109)

Table 5. Data Movement Operations

INSTRUCTION | OPERAND SIZE OPERATION

XG, we ROR,

LEA. 3 FAA

‘AN SP)

NK - SP An

SP « displacement > SP

MOVE 16,32 | «(EAM

EA) hn, Dn

oven 16,32 ‘

Da —» (EA)

Mover 16,92 ea

Dn —> (EA)

MOVEQ 8 ox On)

PEA 3 EA» 48°)

‘SWAP % DejS¥16] €9 Daf159}

UNLK E an SP

($?)+— An

NOTES:

Ss = source bitrumbor (0) ¢ =e with postdecrement

6 = destination

slay 25, 1986 on

Indoctwith predecrement # = immodiate data

‘Signtic Mitary Customer Spocic Products

16-/32-|

Microprocessor

Counter with index — This address

‘ing mode requires one word of extnsion. The

‘adress is the sum of tho addkees in th pro-

‘gram counter, the sign-extended dsplacoment

Intogor in the lower sight bts of ho extonsion

word, andthe contantsalthe indoxrogistor. The

‘value inte program countor isthe across of

‘he extonsion word. This relerence is lassifed

2 a program reference,

Immediate Data — This adrassing mode r0-

ures ther one or wo words of extansion do

ending on the size a the operation

By operation ~ operand is low-order byte of

‘extonsion word

‘Word operation -oporand is extonsion word.

\Long-wordoperation -operandisintho two ox

tension words, high-order 16 bis arein the frst

‘extension werd low-order 16biteare inthe sec

‘nd extonsion word

ImplicitRoterence —Somoinstuctions make

implcitreterence othe program countor (PC),

the system stack point (SP), tho supenisor

stack pointar (SSP), tha user stack pointot

(USP), or the stats register (SA). A eolacted

Setotinstuctions may roference ha statsrog-

istor by moans of the afactve adds fold

‘These are:

[ANDI oR Oni SA

‘ANDI SR MOVE to cor

EORI w CCR MOVE 1 SR

EORI © SR. MOVE tromSR

ORI CCR

uly 25, 1986

Effective Address Encoding

Summary

Table disasunmay ol he otectvesdtessing

modes discussedin he provious paragraph

System Stack

“The systom stackis used implicit by many in-

structions; user stacks and queues may bo

‘croatadand maintinedttrough the addressing

‘modes. Address register soven (A7) ste sy

{tam stack pontor (SP), The eystom stack point

isthe te supordsor stack pointor SSP) or

the user stack pointer (USP), dopencing onthe

stat ofthe Sbhinthe status rogistr. ibe Sb

Indicates supervisor stato, SSP is the active

‘stom stack pointer and the USP cannot bo

‘oferencedas an adcrossropstor llth Sbitin-

cates user stato, the USP isthe active system

‘stack pointor and the SSP cannot bo roor

fenced. Each systom stack fils from high

‘momory to low memory,

INSTRUCTION SET SUMMARY

‘This section contains an overview ofthe form

‘and sructura of the 62000 instructon set, The

instuctons form a set of tols that incase all

the machine functions perform the following

operations

a7

Product Speciation

68000

Datamovement Bit Manipulation

Integer avthmatic Binary coded decimal

Logical Program coawol

Shiftand route System control

‘Tho complatorango of instucton capabiites

‘combined withthe fexbie adcrossing modes.

‘described proviousy provide a very flexible

bate fr program development

Data Movement Operations.

Tho basic method of dala acauisiton (vanster

‘and storage) i provided by to move (MOVE)

insiucton, The moveinsiricon andthe elec:

|e adcressing modes alow both adeross and

ata manipulation. Data move nsrucions al

tow byto, word, and long word operands to be

‘ranslrrd ftom memory io memory, memory

to register, ogistr to memory, and register

registor Adkoss move instuctons allow word

‘and long-word operand ranslers and ensure

‘hat only logal address manipulations are ex-

‘cuted. In adtion othe general move insbuc-

ton tore are several spoctal data moveront

instructions: move multiple registars (MO-

‘VEM), movo porphoral data (MOVEP), ex:

changoregstors (EX), ad elective aoss

(LEA) pushefectve address (PEA) bok lack

(NK, unink stack (UNLK), and move auick

(MOVE), Table 5is a summary of tho cata

‘movement operators.

‘Signoti Miitary Customer Speci Products

Product Specification

16-/32-Bit Microprocessor

68000

Table 6. Integer Arithmetic Operations

wwsTaucrion | OPERAND ‘OPERATION

8, 16, 32 ‘Dn + (EA}—> Dr

(EA) + Dn —> (EA),

a0

(Asma OA)

se | Reviearcoan

fon 8, 16,32 Dx Dy+X—> Dx

‘ “sy eyo X91

aR ee [ Oe

382] ote

en

Co (Ax) + Ay

se | meen

ows Bere [or Oe

aM S516 | or eA OF

om TI] One Ore

te22_| (Onin Ome

WS exe OnE

WOT [Te x16 | OnXCEA)> On

TE Tes [On (eA TEA

TE Tie | OE

a

(EA) (eA)

sue

(Ano)

tee | dareerrmoo sn

De by-X> Ox

SUK 3.16.32

(Ax) ~ (AY) ~ X 9 (Ax)

TAS S (EA)-0, 1 > EAT]

TST 8,16, 32 (€A)-0

Nore:

ATT sarunber 1), = bedrectni prcoment

DT eee aes {}. 2 Beech sere

Table 7. Logical Operations

WwSTAUGTION | OPERAND SE OPERATION

Baa tER Bo

avo ase | (aon ed)

Aa roa> A)

Orv EA) On

oa a.i.se | (env one

(EA) V fxxx > (EA)

wa Tee} AS Oy > A)

(EA) ® xxx — (EA)

wor Tee] eye

NOTES

FS nme ¥ = geaton

+ Line © = leat excuvo oF

1. Sage AND

uly 25,1986

a

Integer Arithmetic Operations

‘The arithmetic operations indude the four

basic operations of add (ADD), subtract

(SUB), mutiply (MUL), and divido (DIV), as

woll as afttmmotic compare (CMP), clear

(CLR), and negate (NEG), The add and sub-

tract inetuctons are available for both

address and data operations, wit data opera

tions accepting all operand sizes, Adcress

‘operations are limited to legal adress size

‘porands (16 or 82 bis). Data, address, and

momory compare oporations ar also avai-

‘bo, The clear and negate instructions may

be sued onal sizes of data operands,

Te multiply and divide operations are aval-

able for signed and unsigned oporands using

word multiply to produce along word product,

land a long-word dividend with word dvisoro

produce a word quotiont with a word remain

er

Mutprecision and mixed size arithmetic can

be accomplished using a sat of extndod i

‘structions. Those instructions aro: add ox

tended (ADDX), subiract extended (SUBX),

‘ign oxtona (EXT), and negate binary with ox

tend (NEG)

‘A wst operand (TST) instruction that wil sot

the conditon codes asaracultofacompare of

‘he oporand with 2070 is also availabl. Tost

and ot (TAS) i a synchronization instruction

Lsofulin muliprocassorsystoms, Table isa

‘summary ofthe inter arithmetic operations

Logical Operations

LLogialoporatoninsbuctions AND, OR, EOR,

‘and NOT ara available fr al sizes of ntogor

data oporands. A similar st ol immociatein-

ssructons (ANDI, ORI, and EORI) provide

‘hasological oporatons with alsizos ofimme-

date data. Tabla isa summary ofthe logical

‘operations,

‘Signotics Mitary Customer Specie Products

Product Specification

16-/32-Bit Microprocessor

68000

Table 8. Shitt and Rotate Operations

OPERATION

wetmuction | openaNo size

Ast 816,22 Cx.

ASR 16, 32 —S— Xe

ts. aie | CRE} °

sr ne

ROL 8, 16,32 c i }

roa ase | OE _

ron a

ox ats.s2 oe

Table 9. Bit Manipulation Operations

TWSTRUCTION | OPERAND Sze OPERATION

oreT a | eae

pear aa | ier eA>z

ty ttetea

a oy | cen

O->btefEA

mona aa | ae >z

Htot (EA) beat

NOTE: ssa

sy 25, 1986

37a

Shift and Rotate Operations

Shit oporations in both rections are pro-

\idod by the aries instructions ASA and

ASL and logical shit Instucione LSA and

USL. The rotat instructions (wth and witout

‘xtond) avalable are ROXR, ROXL, ROR,

land ROL. All shit and rotate operations can

be portormad in ether rogistors oF memory.

gitar shifts androtaes support all operand

sizes andallowa shiftcount speciiedina data

rogistor.

Momory shits and rotates are for word oper:

ands only and alow only sngl-bit shits or

rotates,

‘ablo Bis a summary of tho shit and rotate

operations.

Bit Manipulation Operations

Bit manipulation operations areaccomelichod

using the folowing insbuctons: it test

(TSM), bit test and sot (BSEN), bt wet and

lear (BCLA), and bit test and change

{BCHG), Table 9ie a summary of tho bit ma:

ripulaton operations. (2 is bit 2 ofthe status

register)

Signetce Mitary Customer Specie Products Product Speciation

16-/32-Bit Microprocessor 68000

‘Table 10. Binary Coded Decimal Operations Binary Coded Decimal

INSTRUCTION | OPERAND SIZE OPERATION Operations

nen Matron ritmotcoperabonson boary

ABCD 8 10 + Dyes X—? Ox coded decimal numbers are accomplished us-

= (Axi0+ = Ayia +X —> (AX) ing the following instructions: adddecimal with

as 7 Dawg Dre—X> Ox erton ABCD) eubeact aca wih eons

{S8C0). and ogate ne

tARV0~ (AVIA X= (AN) (NBCD). Table 10 is a summary of the binary.

NCD a O=EAya= XEN) oxo Ssinaloperatons

NOTE!{) = indvoct wit predocroment.

Table 11. Program Control Operations Program Control Operations

INSTRUCTION ‘OPERATION Program contoloperations are accomplished

Usinga series of concitonal and uncontional

‘Conditional branch inswuctons and retum insbuctons,

Bee Branch conatonaly (14 condtons) Those instructs are summaizedin

Brand te. depiadoment lett

Dice ‘Test corction, decrement, ans branch

$6 bitdsplacement ‘The condtonal insbucions provide sating

See Sotto condtionay (16 condons) ane branching fo th following condions

Uncondlilonel

nea pao (60 ~ cay doar 1S -fow or same

B-and 16-bit displacement Sera ha

es Branch o subroutine Foomerive NE not eral

Brand 16-btdeplacoment oe) eae

sump GT-gresterthan | T—always rue

‘lump to subroutine Hing Yo =no overfow

LE-lessorequal VS ovorfow

Return and restore conton codes

Retutn fom subroutine

Table 12. System Control Operations ‘System Control Operations,

INSTRUCTION. ‘OPERATION Systom contol operations ae accomplished

by using privloged instructons, wap generat:

Privileged ing instuctons, and insbucsons that Use oF

ANOITOSR Logical AND to stats gitar modi the stats register. These instuctons

EORIw SA Logical EOR to status rgistor fare summarized Tabo 12

MOVE EA SR Load now status ogisior

MOVE USP Move usor stack pointr

oAltasR Local OR to sats rogistar

RESET Reset extemal devices

ATE Return rom exception

STOP Stop program exacuton

Trap Generating

hk Chock ata register agsinst upper bounds

TRAP Tap

TRAPV Trap onovertow

‘Siatus Rogleter

‘ANDI 19 COR Logical AND to condition codos

EORI® oR Logical EOR oeondton codes

MOVE EA ® OCR Load new conston codes

MOVE SAio EA Store stats register

Al COR Logical OR to condton codes

July 25, 1986 a8

Signotcs Miltary Customer Specie Products

Product Speciation

16-/32-Bit Microprocessor

68000

‘Table 13. Data Strobe Control of Data Bus

wos | oS | Rw Do-Dis 0-07

igh | Pion [= To vi eta Noval dala

tow | tow | High Val cata ite Vela

High | Low | High (No valid data ae

tow | on | Hon se No valid data

tow | tow | tow Vale aia bis Weiser

High | Low Low ae bits oe bits

Low | High low ane Coo

NOTE:

"Those conditons ar a result of current implementaton and may not appear on tutte devices,

SIGNAL AND BUS OPERATION

DESCRIPTION

This socton contains a bio Sascription of he

ingut and ouput signals. A discussion of bus

‘operation during the various machine cycles

and operations is also give.

note

‘Thetoms assertion andnegstion wilbe veed

extensively. This i¢ done t2 avoid contusion

when dealing witha mixture of-activoow” and

“active high signals. The arm assert or assor-

tion is used to inceate that a signal is active ot

tt, independent of whether thatlovolis rope

sented by ahigh or ow votage. Tho term no.

gatoornegatonisusedto indicate thata signal

is inacvo or tle,

aly 26,1986

Signal Description

‘Theinputand output signals canbe functionally

corganzed into the groups shown in Figure 8.

‘The following paragraphs provide @ bret do-

scription ofthe signals and a refrence ({apps-

cable) to other paragraphs that contain more

-————[___wireomn 7

[__Tetwaure curaurtaassren_—i4+____]

SOR OAT ON Do or As.

FOR ox on eons oss

‘9 ASSERT DATA TRANSFER ACRNOWLEDGE

enc

pagar wos anos

BASE Re

SSeY aw eo nelD

5) REVOVE Gata rpoM 00-07 on 06-018

TERRATETE OE

wpeaare OTE

Figure 14, Byte Write Cycle Flowchart

Sue ous evens nene ewe

bx woro wars fae — coo ore wre —aefag— sven arse ware oe}

Figure 15. Word and Byte Write Cycle Timing Diagram

July 25, 1986

302

‘Signotics Mit Customer Specife Products

Product Speciation

16-/32-Bit Microprocessor

68000

Rosd-Modly-Wilte Cycle — Tho road:

modiy-wrte cycle performs a read, modes

tha data in the arthmotclogie uit, and wrtos

the data back 16 the samo address. In the

{68000, this eyo is indivisible in thatthe ad

‘ess tobe is assorted treughout the entre

cyde, The test and sot (TAS) insructon uses

{tis ole to providamoaningtul communication

‘between procestorsinamultplaprocessoren-

‘Yeonment. Tis instruction is the onl instruc.

tion that uses tho read modfy-wrte cytes and

since the tat and satinsbucton only operates

fon bys, al raad-modly-writa cytes are byte

‘peratons, Aread modify writs cycle flowchart

{is givonin Figure 16 anda bing Gagramisgi-

‘nin Figure 17.

vs ssen one

ree

EATEN

BEIT coe urcose

‘assent Aaoness sraoee

TEETER mon

Sees

src ons

SEAR

Bis

Tae —

nuns

BES ons

HER REoe

| res

1) Rewowe ara rnou 00-07 on De-O18

heaaTe OER

19 ser qm 10 ware

53 aaeenr Goren ONT Sac

Ge oxTastROse GOS)

BSE att Subs o7 on 98.01,

‘@8)0n

|}___——-["wurneomm |

1) gr08e ona on 0-07 08 DB.on

BRIBE o TNR

eran

TERUNATE OUTPUT TRANSFER ——

‘yheoare oos on DE

3 Reuove cata cpow 00-07 on os-ovs

Ser ReaD

ft TERINATETE OE

)Necare Ta

F

igure 16, Read-Modlly-Wrlte Cycle Flowchart

uty 25, 1986

383

‘Signotis Military Customer Specific Products

16-/32-Bit Microprocessor

Product Specification

68000

Users onsen ase w

[x vrnsiocgevers —______—»

Figure 17. Resd-Modity-Write Cycle Timing Diagram

Bus Arbitration

‘us atiraton is a technique usod by mas-

ter-ype devices to requost, be granted andac

knowledge bus mastership. nits simplest form,

itconsies ofthe folowing

1 assonting a bus mastorshiproquest,

2. receiving a grant thatthe buss avaliable at

tho ond of he curont cycle, and

8. acknowledging thatmastershiphas boon as-

‘sumed!

Figure 18 6 @ fowchar showing the deta in-

volvedin arequosttrom a single doves, Figure

sly 25, 1986

191s a timing diagram for ho same operation,

This tochrique alows processing of bus re

uosts during data vanstercyces.

‘Tho tming iagram chows thatthe bus request

is negatod at ho ime that an acknowledge ie

_assorod, This type of operation wauid be tre

fora systom consisting of tha processor and

‘one device capable o bus mastrshp, in sys-

tems having a number of dovioes capable of

bus mastership, the bus roquest ine rom ach

]

PL LS LPL

Bie

><

Figure 22. Bus Arbitration Timing Diagram—Processor Active

><

‘As shown in Figure 20, input signals labeled R

and Aareintemaly synchronizedon the bus e-

{questand bus grant acknowledge pins, e=pee

‘vol. The bus grant outputs laboled Gand the

intemal 3-Staa contol signal TI Tis tuo, the

‘adress cata, andcontolbuses ar placedina,

high impedance stato whan AS is negated. All

signals are shown in positive logic (active high)

‘ogardess of thoir tue active voltage love.

‘State changes (valid cutpus) occur onthe next

ising edge aftr the inernal signal is vai.

‘A timing diagram of tho bus arbivation so.

‘quonce during a processor bus eyo ie shown,

inFigure22.thebus arbitration soquence while

oly 25, 1986

the busis nactve (Lo, excouting intemal oper-

ons suchas amultiplynsructon) is shown in

Figure 23,

Wabusroquestis made ata ime when the MPU

has aroady begun a bus cycle but AS has not

bonassoried but state $0), EGwillnotbe as-

sorted on tbo noxt rising edge nstoad, BC wil

be dolayed unl the second sing ed follow:

ing its intemal assorion. This sequence is

shown in Figur 26

Bus Error and Halt Operation

Inabus architecture thatroques ahandshako

from an external device, the passibily exists

that the handshake might aot occur. Since dit

forontsystoms wilroque adiforent maximum

responsetime, abus errrinputis provided. Ex

tomal creuity must be used to dotermina tho

uration botweon address svobo and data

transteracknowledgebotoreissuingabuseror

signal, When a bus oor signals received, th

processor has two options: ato a bus oror

‘exception sequence or ty runing the bus oyde

‘gain,

Signatics Miltary Customer Specie Products Product Speciation

16-/32-Bit Microprocessor 68000

=———] | —— |

FS LL LL

mx rrocesson —pefae— susinactve —pefag—— auromure pus uasten ef Processon De

Figure 29. Bus Arbitration Timing Diagrem—Bus Inactive

ly 25,1986 389

‘Signotics Miltary Customer Spocifi Products

Product Specification

16-/32-Bit Microprocessor

68000

Poocesson sTARTeneKTaUSCTELE

‘BOREK SAMPLED

=F

CULL ey

Bus Error Operation — When the bus error

‘sigalis assorted, the curoatbuscycleistermi.

nated. BERR is asserted before te fling

edge of $2, AS willbe nogatedin S7in either a

‘ead or wit cyte. As long as BERR remains

‘asserted, the data and adéress buses wil bo in

‘he high-impedance stale. When BERR is no

{Gatod, th processor wil begin stacking lor ox

czption processing. Figure 25 is timing dia-

7am for the exception sequence, The s2-

‘quonceis composed the folowing elements

1. stacking the program countorandstatusreg-

ister,

2, stacking the err information,

5. roading the bus oror vector table ent, and

4. executing the bus oror hander routine

‘Tho stacking of te program counter andthe

status registris the samo a fanintorupthad

‘ccured. Saverl adtitinaltoms ara stacked

hon a bus error occurs. Those toms are used

{o determina the nature ofthe nor and corect

{if possible. The bus error vector is vector

‘number two located at addross $000008, The

processor loads the now program cauntr rom

sly 26, 1986

ah

Figure 24. Bus Arbitration Timing Diagram—Special Case,

ALTERNATE US MASTER

this locaton. A software bus ortor han rou

tine is then executed bythe processor. Rater to

Exception Processing fr acdtonal informa:

tin,

Re-Run Operation — When, during a bus

‘oyde, te processor raceives bus err signal

‘ane tha halt pin is boing oven by an extemal

sevice, the processor entors the rerun se-

‘quence, Figure 25 ig a Sing chagram for

re-running the bus eye

“The processor trminatos tho bus cycle, thon

puts tho address and data output limos fa the

high impedance stato. The procossor remains

‘alta’, and wllnotrun another bus eye unt

tho halt signal is removed by external logic.

‘Then the processor will rerun the previous

«yc using the samo funeton codes, tho samo

i

made to guarantee that tho ent cyde runs

‘ommctly and that the write oporation of @

testand-set operation is porformed without

‘ever leasing AS, # BERR and FACT are as-

sertod during a ead melt write bus cyclo, a

bus eror operation resus,

Halt Operation — The halt input signal tothe

{58000 performs a alirunisingle-stop function

ina similar fashion tothe synchronous device

halfunction. Taehaltand run modes are some-

hat so explanatory in that when th halt sig-

nal is constanty actve the processor “halts”

(oes nothing) and when the halt signal i con-

Stanly inactive the processor "runs" (does

something)

‘This single-step mode is derived from conecty

timed tansiions on the halt signal input

foreas the processor to exocua a single bus

‘cle by entaring the un med une proces-

s0F stats a bus cycle thon changing tothe hat

‘mode. thus, the single-step mode allows the

User to proceed trough (and therefore dabut)

Processor operations one bus oyle ata me,

‘Signotics Miltary Customer Spoctc Products Product Specification

16-/32-Bit Microprocessor 68000

rene X_ NO

[BEE fae neste ature —fag—— ove enon oerecnon pba sR

Figute 25. Bus Error Timing Diagram

ox FLELS LS LLLP

reorce X xX x

fx 10 fx str >} — reson

Figure 26. Re-Run Bus Cycle Timing Diagram

July 25, 1986 sat

‘Signotics Mitary Customer Specie Products

Product Speciation

16-/32-Bit Microprocessor

68000

Figuro27 deta the timing required for coract

single-step operations. Some caro must be ax

‘tcsed to avoid harmiulintoractons between

the bus errr signal and the halt pin when Using

{he singl-cycle made asa debugging tol, This

is also tue ofintaracione between the halt and

reset ines sinco those can reset the machine,

ion the processor complots a bus cyclo

tor recognizing that tho halt signal is active

‘most 9-State signals are put in tho high:

‘impedance stat, these include:

1. adrass nes, and

2, data ines.

‘This is required for coroct performance ol the

re-run bus cyce aporation.

Wile tho processor is honoring the halt re

quest, bus arbiation performs a8 usual

“Thats, hang has ne etlocton bus abitraton,

ttisthobus abivation funcbon tatremaves the

contol signals om the bus.

‘The altfuncton and the hardware Wace capa:

billy alow the hardware debugger to trace

inglebuscyclsoringleinstuctons ata ime.

These processor capabilties, along wih a soft

ware debugging package, give total debugging

foxy.

Double Bus Fautts—Whonabus errorexcep-

tion oeurs, te processor wal attompt io sack

‘several words containing information about the

Stataat he machino.labus err exception oe-

curs during the stacking oporaion, here have

boon wo bus errors in arow. This commonly

relerredtoasadovble bus auit Whenado\blo

bus taultoceus, tho processor wilhalt Onca a

busertorexcoptonhas occured, anybus eror

‘xcopton occuring botore he oxoaution ol he

next instucion constitutes a double bus faut,

Note that a bus cycio whichis re-run doos not

‘constiute a bus err exception and doos not

‘contribute to a double bus faut Not aso that

this means that as long as th extemal hard-

Ware requests it the procossor wil continue to

rerun the same bus eyde.

‘Tho bus error pn also hasan fect on procos-

50% oporation aftr the procastor receives an

‘extemal raset input Tha procassor reads the

oct table afar a reset lo determine the ad-

‘ross to star program execution fa bus enor

‘occurs whilo reading the voctor table (or at any

{imebelorethefirstinstuctonis execuied), te

‘rocessorreactsasila double bus aulthas oo-

curred andi alts, Only an extemal reset will

sar a halted processor

be 880 foe —— sr ——— pq near >

Figure 27, Halt Processor Timing Diagram

ly 25,1986 382

Signetcs Miltary Customer Specie Products

16-/32-Bit Microprocessor

Product Specification

68000

Reset Operation

“Therese eignalisabidroctiona signal hat

lows oithor the processor or an extorna signal

to rat the systom. Figure 28 isa Siming dia-

{gram forthe rasa operation Both the hal and

{esol inee must bo asserted to ensure total e-

sot of the processor.

Wan the resot and halttines are driven by an

‘ternal davies, it ie recognized as an entre

‘ystemrasat, including the procassor. The pro-

‘cessor responds by reading the reset voctor

table entry (vector number zero, address

'$000000) andloadsitnto te supervisor stack

pointer (SSP), Voctr lable antynumberoneat

feddress $000004 is road next and loaded into

the program counter, The processor inializos

the statis rogistorto an inoruptlevelot seven.

Nother rogetre are affoctod bythe resats0-

quence.

‘When a rete inetuction is oxecuted, he pro

‘coseor ives the rat infor 124 clock peri

‘ode. Inthis case be processorisbyingtresat

tbe restoltesystom. Thoretore, herein of

{ecton the intoral stato of he processor. Alt

the processor sintemalregistorsandihe stats

regisior aro unaffected by the execution of are,

‘etinstucton. All external devices connected

‘etheresotine wilbe resetatthe completion of

the resot instruction

[Aseoring the retat and halt nos for ten clock

‘oles wil cause a processor reset, excapt

‘whan Voc intl eppliadto the processor. n

this case, an extomal rosat must be at last

100m.

vores:

sree

EES

= TNL

= et» wo mLLsEcoNDs ey

Slowrencinrere,

‘vnatunton hare sect acie

Figure 28, Reset Operation Timing Diagram

AULT.

ervemctnom —— XXXK

iy 25, 1986

‘Signetics Mitary Customer Spocife Products

Product Specification

16-/32-Bit Microprocessor

68000

‘Table 16. DTACK, BERR, and HALT Assertion Results

X-dontoare

Nethe numberof tho curent avon bus st

‘signal asserted inthis bus stato

NA-signal isnot assorted inthis stato

'S-signalwas assorted in provious stato

Table 17. BERR and HALT Negation Results

"ASSERTED ON

case | conTROL RISING

No. | SIGNAL” | EDGE OF STATE RESULT

wa

DTACK - ‘S| Normal eye terminate and

' ‘BERR NA X | continue

aT NA. x

DIACK a ‘S| Normal cycle terminate andhalt

2 ‘BERR NA. X | Continue when FACT removed,

RAT A s

DIACK WA ‘| Normal eyclo terminate and halt.

3 ‘BERR NA NA | Contrue when FCT removed

ACT A 8

TACK x X | Terminate and take bus ero Wap.

4 ‘BERR a s

AT NA NA

DIAC A | Torminateandiro-nn,

5 ‘BERR a s

FACT NA A

DTACK x [Terminate and o-run when FACT

6 ‘SEAR A S| removed,

RT A 8

‘DTACK NA X | Torminate and ro-run when FALT

7 ‘BERR NA A | removed

FACT A s

NOTES:

ato (0.9, $4, $8, ote)

and remains asserted inti stato

NEGATED OW

conomons or | conor | Remeeee

Temmaton | “Sonat” | "orStare™ | resucre-wexrovete

ar

ror BEAR co 16 bus error

Bus Er FAUT oor | Tort wee.

= wm |= er + Tioga sequen uomiy

Fo. ‘HALT © of — @ _| taps to vector number 0.

Row BE T+ Trownsnomngae

Normal Far Sow [Maylengton noxt yee

=e © | tment wand

ee FAT | gor none {bo terminated as a bus error.

ROWE

‘= Signalis nogatodin this bus state,

July 25, 1986

306

The Relationship of DYACK,

BERR, and HALT

In order to property contottaminaton ofabus

cycle for @ rerun or a bus error condtion,

[DTACK, BERR, and HALT shoulsbo assorted

_and negated on the rising @dge ofthe 68000

lock. This will assur that when wo signals

areasserted simultaneously theroqulod set

Uptime (#47) or both of tham willbe met or

ing the same bus sta

This, or ome equivalent precaution, should

bedosignodextsmalt te 68000, Paramotr

#48 (s0e AC Eloctical Charactoratis fr #

‘feroncas) ie intended o ansuce this opera-

tion in a totaly asynchronous system, and

‘may be ignored if the above conditions ae

‘mat

‘Tho profered bus cyclo terminations may bo

summarizedas olows (case numbers rterto

Table 16)

‘Normal Termination:

DTACK occurs fst (Case 1),

ermine

ALT assonodattho same tine orbo-

{oro DTACK and BEA remains negated

(Cates 2and 3}:

Bus Error Termination:

[BERR is assorodin lou of, at ho same

time, or botore DTACK (Case 4); BERR

| nogatod at tho same time or ator

TACK.

Re-Run Termination:

[RATT and BER aro assertad in fou ot,

at the same timo, or belore DTACR

(Cases 6 and 7); HALT must be held at

leastone oyde ator BER, Case Sind-

ates BERR may procede FACT.

Tablo 16 details tho resulting bus cyto termi-

‘nation undor various combinations of contol

‘signal sequences. The nogaton of these

‘same contol signals under soveral condibane

is shownin able 17(OTACKis assumediobe

negated normally inallcases; forbest resus,

both DTACK and BERR should be nogatod

when address strobo is nogatd)

Example A:

‘Asystom uses a waich-dog timer totarminate

‘accesses tounpopuiated adress space. The

timer assons DTACK and BERR simuta-

neously ahr ime out (Case 4),

Example B:

‘A syslom uses oer dotacton on RAM con-

tents. Designer may (a) delay OTACK vn

ata verifed and retum BER and HALT si-

‘multaneouslyto re-run oror le (Case 6), or

it vakd, retum DTACK (Case 1); (0) delay

TACK unti data voriied androtum BERR at

same tine as DTACR data in error (Case 4),

Hat

Signotcs Military Customer Specie Products

Product Specification

16-/32-Bit Microprocessor

68000

Asynchronous Versus

‘Synchronous Operation

[Asynchronous Operation

Te achiave clock trequency independence ata

systom lovel, the 68000 can bo used in an

‘asynchronous manner, This entails usiog only

the bus handshake ines (XS, UDS, LDS,

[DTACK, BERR, FALT, and VPA) to control his

data ransler. Using thie method, AS signals the

‘sia of bus cydle and the data stobos aro

Used as a condliion for vad data on a write

‘yc. The slave dave (memory or parighoral)

thon responds by placing therequestedta on

the data bus for aroad cycle oatching data on

awrite cyce and asserting the data transtorac-

kKrowiodge signal (OTACK) to termina he bus

cycle, I no slave responds ortho access i in

‘ald, external conto! logie assorts the BERR,

(or BER and HALT signal to abort or rerun the

bus cycle.

‘The DTECK signalis alowodtoboasseriodbe-

foro the data om a slave device is valid on a

rad oyle. ho longth of timo that DTACK may

precode data is givon as paramotor #21 andit

‘must be matin any asynchronous systam toin-

sure that valid datalslatchodinto the processor

tio thatthore i no maximum time spociied

from the assorton of RS to the assorion of

TACK. This is bocavse the MPU wil insert

wait eyeles of one clock pariod each unti

[DTACK is rcognized.

‘Synchronous Operation

Teaow for tose systoms which uso sys

tem cock asa signa to goneato DTACR and

other asynctrenous inputs, fe asynchronaus

Input sop ti ie givon as parameter #47.

tis sonpf mat onan input such as OTACR,

the processors guarannod to recognize Hat

‘signal on tho not fling ogo ofthe systom

ack However the converse snot tu0~i the

Input signal doos not mot th setup tne iis

not quaranized net obo recognized. In a>

toni DTRCR i acognizd on atling edo,

‘ali data wi latchadino ho processor (on

‘read eyele) on tho nox fling 6099 provided

‘hatte data ects the sotup ime given as pa

rameter #27 Given tis, parame #1 may bo

‘gnored. Noto that f DYACK is assoriog, with

Torequred soup sino, belo ang 0092

‘o1S4,nowaitsates wif beincuredandtho bus

cele ilun tits maximum spoodatfour clock

pores

NOTE: During an acto bus cycle, VFR and

[BERR sampled on every fling ego ofthe

clock stating with $2. DTCK is sampled on

‘ry Taling ode ofthe clock starting with S¢

‘anddatais latched on te faling edge ofS dr

ingaread, The bus cyciewilthon bo terminated

in'S7 except whon BERRs assertdin th ab-

shy 25, 1986

sence ol DTACK.inwhich case twiltorminata

fone cock cycle ltarinS9, VPAis samplod only

‘onthe thi faling edge of tho systom clock bo-

fore the rising o0ge ofthe E cock

PROCESSING STATES

This eveton dosribs the actions ofthe 62000

which are utzde tha normal processing asso-

Catod wih the execuion of instucions. Tho

fonctions ofthe Bits inthe supervisor portion of

the status register are covered; the suparvisor!

user bit, the trace enable it andthe processor

interrupt peocty mask. Finally, the soquence of

rmomory references and actions takon by tho

procestar on exception conltons ae detailed.

‘The 62000is alwaysin one of hreo processing

sats: narmal, exception, or halted. The nor

‘mal processing stato that associated with in-

ftrutionexecuton;the memory oferences are

tofetch instucions and operands, adie store

results A special caze of ho normal sates tho

‘lopped state which the processor ontors when

fa stop Insruction it executed. In is state, oo

former references are mado.

The excoption processing stato is associated

with intorupts, wap Instuctons, racing, and

‘ther excaptonal condions. The exception

‘maybeinteraly eneratodby an instrucionor

by an unueualcondtion arising during tho ox

‘tution ofan instruction, Extrnaly, exception

proaossing ean bo forcod by an interrupt, by &

bus error, or by aresot. Exception processing is

signed to provide an ecient context switch

so tha the procossor may handle unusual coo-

sions.

“Tho haltod processing state isan inciation of

calastophic hardware fale, For example, i

uring tha exception processing of a bus enor

fanother bus ertor occurs, the processor as-

sumes thatthe systom ie unusable and hal

(Only an oxtoral reset can restart halted pro

cessor, Note thal a processor in the stopped

‘at0 is notin tho halted stato, nor vice versa.

Privilege States

“The processor operates in one of two states of

priviege: the “supervisor stale oF the "uso

Stato. The privilege sate detarmines which op-

tations ae legal, are used ta choose between

the superisr stack pointor snd the user sack

pointer ininstructon rterencet, and may ba

‘sed by an oxtrnal memory managomont do

‘oe to contre and translate accesses.

‘Theprivilege state samechanismfor provicing

socuriy ina computer system, Programs

should access ony thar own code and data

areas, and ought tobe resvictec trom access:

ing information which they do not need and

must nat mostly

395

The privioge mechanism provides socuriy by

‘lowing most programe to exocule in user

satan this eal, th accesses are controle,

“andthe efecs on obor pars of te systom aro

limited. The operating systom execules in ho

supervisor sata, has access to all resources,

and performs the ovorhoad tasks forthe user

state programs.

‘Supervisor State

“Tho supervisor stale ie the ighor stato of piv

Jee. For instuction executon, the supervisor

statoisdotormined by tho Sbitot he stats eq:

istr:ithe Sbitis assorted (igh, tho procossor

isinthe supervisor stata, Alinstuctons canbe

exccuted in the supervisor stata, The bus

‘oycles generated by instuctons oxocuted in

{he supervisor state are classfodas suporvisor

toecencas. While the procossorisin he super-

‘sor prvloge stato, thoso instructions which

Uso ater the systom stack pointr imply or

‘aderossrogistorsovon oxpicity accass the su-

pervisor stack pointer

‘Allexception processing is dane in he supers

tor sate, regards of ho eating of the S bit

‘Tnebus cytes generated during exception pro-

‘esting araclaselBodas suporvisorrofarencos.

[Al stacking operations during excoption pro-

cessing use the supervisor stack pointer,

User State

‘TheUser states the fowor stato of pivloge. For

Instvtion execution, the user stato ie dot

tminodby the Sitot the eats rgisor tho

bitis negatod (ow), th processor is executing

Instructons inthe user stato

‘Most instructions exocuto the same in user

sate asin fe supervisor stato, However, some

instructons which have important systom of

fects aro mado privieged. User programs are

net permitted exoouta the stop instruction or

the resetinsmucton. To ensure that ausorpro-

‘ram cannot entor the supervisor stay except

in a contoted manner, the insctions which

modty the whol stato register aro privloged.

‘To aid in debugging programs which are to be

sed as oporaing systoms, the move to user

stack pointer (MOVE to USP) and move from

User slack pointor (MOVE from USP) instrve-

tons ar also privileged,

‘Tnebus cycles gonoratodby an instruction ox

ecutod in the user stato ar cassied as usor

ate teforoncos, This allows an extemal

‘memory management dovice to transite te

‘address anda control access ip protected por-

‘onsatthe adress space. While te processor

‘iin tho user privloge stata, thosa instructions

\which uso er the systom stack pointer im-

Piety or adekoss rogistor soven explicit, ac-

‘cate the usor stack pointe:

‘Signotics Miltary Customer Specie Products

Product Specification

16-/32-Bit Microprocessor

68000

Table 18. Bus Cycle Classification

FUNCTION CODE OUTPUT

Foz Fer Foo

REFERENCE CLASS

(Wrassigned)

User data

User prooram

(Weassignedy

‘rassigned

‘Supenicr data

‘Sopenicer program

o

7

T

T

o

o

7

7

Tnierupt ecknowiedge

wore Nw PROGRAM COUNTER aH)

won ew PROGRAM COUNTER Om

Figure 28, Format of Vector Table Entries

vononeD ww

wfu fw

Figure 20. Vector Number Format

a ae

AL 2EH08

Figure 31. Exception Vector Address Celevlation

ly 25, 1986

396

Privilege State Changes

‘Once the processorisin the user stato andex-

‘ecuting inetuctons, only exceptional pro-

‘cessing can chango he prvioge state, Dring

‘exception processing, the curent seting of

‘ho bitol the stausropsioris saved andthe

'Sitia assorted, puting the processor inthe

supervisor stato. Thorafore, when Instruction

‘exocutonresumes atthe access spociiod to

‘process the exception, the processoris inthe

supervisor privoge

Reference Classification

When the processor makes a reforonc, it

classifies the kind of reterence being made,

{he encoding on the roe function code output

lines. This allows extemal translation of ad-

‘rossos, conta of acoess, and derontiaion

‘of speci processor state, such as intaruptac-

knowledge. Table 18 lists the classification of

ralerences.

Exception Processing

Botore discussing the dotals of inorups,

‘aps, and racing, a general description of ox

‘ception processing iin order. The processing

‘ofan exception occurs in our stops, wit varie

{ons for diferent exception causes. During the

{eststap, a temporary copy of te stats ogi:

teris made and te status rogiso is sot for ox

‘ception processing. in tho second tap the ox:

option vectors determined and th third top

isthe saving ofthe cotontprocussor context In

the fourth stop a now context is obtained and

the processor “swichos 10. insbucton

processing

Exception Vectors

Excoption votors are memory locations om

wich the processor feichos the addoss of a

routine wich wil handle that excopion. Alex:

caption vectors aro two words in ongth (Figure

23), excopt forthe reset voctor which is four

words All excopton voctrs be in the superd-

01 data space, except forthe reset voctor

‘hich isin the supervisor program space. A

vector numbers an it umber which, when

‘mutipid by four, gives the addross ofan ox-

option vectnr. Vectar numbers are generates

internal or exioraly dopending onthe cauto

‘ofthe excoption. Inthe case of intorupts, dr-

ing tho intorupt acknowlodge bus cycle, a po-

ripheral provides an 8-bi vactor number (Fig-

ure 20) othe procossor on data bus ines DO

through 07. The procossor wanelatos tha voo-

tornumber into a full 24-bit adkoss, shown in

Figure 21. The mamary layout for excopton

vectors is given in Table 19.

Signatics Miltary Customer Specie Products Product Spocifcation

16-/32-Bit Microprocessor 68000

Table 19. Exception Vector Table

VECTOR ‘ADDRESS

NUMBER(S) Dee Hex Space [ASSIGNMENT

° 2 000. ‘SP Rosa intal SSP

= * 004 SP Reset inal PC

z 2 008 30. Bus oro

3 1% 006 50 Aatross ror

“ 16 010) $0 egal instrcton

3 20 on 30 Zoro dvi

3 2a oo 80 CHK instruction

7 8 ac 30 "TRAPV insirvcton

® 2 020) 30 Privilege wollion

° 3% 02 30 “Trace

0 @ 028) 30 Tine 1010 emulator

1 a 026. 50 Tine 1111 emulator

Te e 030 30 Tnassigned sore

7 5 034 30, (Unassigned, resored)

1 oe 038 30, (Gnaszignod. reserved)

5 © 02¢ 30 Taiiiaizedntorupt vector

16-25 a 046 30 (Unassigned reserved)

8 O5F =

2 % 060 50 Spurous monet

25 09 054 30 Tovelntoruptavtovertr

2 104 058 30 over mtorptautovecior

2 108 08 30 Lovet itorupt autovecor

2 12 O70) 30 ‘evel itoruptautovecior

a 6 O74 30, Laval intruptautovecior

E 120 078, $0 Lavol 6 ntoruptautovecor

3 124 oe 30 Level itorryptautovecior

aea7 128 080) 30 "TRAP insrucion vectors

191 O8F 5

oe 192 060) 0 Unassigned, oserved)

255 OFF, =

ee 256) 10 = User interupi vectors

1025, OFF, =

NOTE:

Vector numbers 12,19, 14,16 through 23, and 48 tough 63 are reserved for futuro enhance-

‘mants by Signates, No ser pericheral devices shoul be assigned these numbers.

‘As shown in Tablo19, the memory layoutis $12

words long (1024 bys). It stars at address 0

‘and proceeds through addross 1023. This pro:

vidos 255 unique vectors; someof these arero-

served lor TRAPe and other systom functions.

‘Of he 255, there are 192 reserved for user in-

tomuptvectors. Howover there's no protecton

onthe fret 64 ents, 0 user intrupt voctors

‘may ovorapatthedisceion of hesystomsde-

signer

July 25, 1986

Kinds of Exceptions

Exceptions can be goneated by ether internal

‘of extemal causes. The externally generated

‘exceptions aro tho interupts and the bus eror

landrasstrequests. Theinterupis arerequests

trom pariphoral devices for processor action

whilethebus orror and esetintorupts ae used

focacoess contl and procossorresta. Thein-

texnally gonerated exceptions come from in-

stuctions, or from address errors or wacing

7

‘The wap (TRAP). rap on overtiow (TRAPY),

chock data register against uppor bounds

{CHK and dvido (DIV) instuctons all can

‘enerate excoptions as pat oftheir instruction

‘execution, Inaddon, egal insbuctons, word

{etches from odd addrossos, and prvoge vo-

lations cause exceptions. Tracing bohaves ke

_avory high-priority intorally-gonoratod inter.

rept ater each inttucton oxecuton.

‘Signotice Mitwy Customer Specife Products

Product Specification

16-/32-Bit Microprocessor

68000

oohcs

Figure 32. Excepilon Stack Order (Groups 1 and 2)

Table 20, Exception Grouping and Priority

‘GROUP EXCEPTION PROCESSING

° Resot ‘Exception procossing bonis

adress oor within wo Bock eyelet

bis enor

7 Trace Excepion processing boving

intropt before the nen instruction

egal

prvloge

2 TRAP, TRAPY, xcepiio processing

uk, stared by normal nstuction

200 ide ‘exoeuton

Exception Processing Sequence

Exception processing occurs in fouridentifabio

stops. In tho fist stop, an inom copy is mado

‘ofthe status registar Atartho copyie made, the

Shits asserted, puting the processor ini tho

supervisor prvloge stato. Also, the T bit sn

‘ato which wil alow the excoption handle to

‘execute unhindered by tracing. For the roeot

{and interrupt exceptions, the interrupt prioity

‘masks also updatod,

Inthe second stop the vector numberof the ox

‘ceptions determined. Forintorups, the vector

‘number is obtained by a processor fetch and

lassie as an intompt acknowledge. For all

‘other excoptons,intoral logic provides the

vectornumber Tis vector numbers thon used

to goneratethe addross oth exception veto,

‘Tho tid stop ist save the curent processor

status, exceptior he rosat excoption. The ou

Fentprogram counter value andthe saved copy

‘ofthe sta rogistor are stacked usig th tu

porvisor stack pointar as shown in Figure 92.

The program counter value stacked usually

‘oints tothe next unexecutedinsucen; how

‘v0 for bus ror and address eco, te valve

stacked for the program counter is unpredic

able, andmaybeincremontod kom the adcress

‘ofthe instruction which caused the error Adc

‘ionainformation dafining the curentcontextis

stacked oc he bus eror and address eorex

ceptions,

‘Tholaststopisthe same or allexceptons. The

‘new program counter values fetched Kom tho

‘2xcoption vector. The processor thon resumes

inswuction execution. The instucton atthe ad-

{ress given inthe exception vectors fetched,

July 25, 1986,

and noralinstrction decoding andexceuon

ie stared,

Multiple Exceptions

“Theso paragraphs describe the processing

which occurs when multiple exceptions arse st

mmuttaneousl,. Exceptons can be grouped ac-

cording 1 ther occurence and prio. The

Group Oexceptionsarorosot, bus error andad-

tess error. Those exceptions cause the in-

‘stuctioncurronty beingexocutedtobeaberted

{and the exception processing to commence

within two clock cycles

‘Tho Group 1 excoptions aretrace andinterupt,

‘as well as th priviege violations andilogal

stuctions. These exceptions allow the current

Instuetion to execute to completion, but pre

‘empl the exccuton ofthe next instruction by

forcing exception processing tooccur(priviege

Volaons and legal instructions are detacted

hon they are the nest instruction to bo ex:

‘ecuted). The Group 2 exceptions cccur as part

‘of tho normal processing of insbuctons. The

TRAP, TRAPV, CHK. and 2ero divide excap-

tionsareinthis group For heseexceptions, tho

normal execution ofan instruction may load to

‘exception processing.

‘Group Oexcoptions have highest priory, while

Group 2exceptions have lowest priory. Wain

Group 0, reset has highest prery, lowed by

us oro’ and then address errr. Within Group

1, trace has pricniy over extra inorupts,

vihich in tum takes priority ver iogal instruc

tion and priviego violation. Since only one i

stucton can 0 oxecuted.at aime, there sno

Prot relation within Group 2.

398

Tho priority rolation between two excoptions

determines whichis akon, or akon frat ifthe

Cconditons for both ari simutanooush.

Thorelore,abus ero occurs during a TRAP

instructor, the bus eror takes precedence,

‘and tho TRAP instucton processing

‘aborted In another example, faninteruptre-

‘quast occurs during the exacuton of an in-

struction while the T bits assorted, the aco

‘exception has priory, andis processed fit.

Bojora instruction processing resumes, how.

fever, the intomupt exception is also pro:

cessed, and insruction processing com-

‘ances finaly in the intsrupt handlor rout,

‘Asummary of excoption grouping and prosty

's given in Table 20,

Exception Processing Detalled

Discussion

Exceptons have @ number of sources and

‘eschexceptionhas processing whichispecul-

iar to it The folowing paragraphs dota the

sources of exceptions, how each arises, and

how each is processed,

Reset

‘The eset input provides the highest excoption

lovel. Tho procosting ofthe reset signal do-

‘signed for systom initiation and recovery fom

catastrophictalure. Any processing in progress

atthe time of tho resotis aborted andcannotbe

recovered. The processor's forced into the su-

ervisor state and the aca sta i forced of

‘The processor inorupt priority maskis sat at

lovel seven. The vector number is intoally

{eneratedto reference the resatexcoptionvec-

tor at locaton 0 in the supervisor program

space. Bocause no assumptions can be mado

aboutthe vat ofropstor contons,nparty-

lar the supervisor stack pointer, nother the pro-

{am counter north status roistor is saved.

Thoadkress contained the frst wo words of

the reset exception veto i otched athe ia

‘ial supervisor stack pointer, and he address in

thelast wo words ofthe reset excapton vector

{stetchodas the inital program countor Finaly,

Instectonexecutonis staradal the adress in

the program count The power-uptestat

‘code shouldbe pointed toby the inital program

‘counter.

‘Thoresotinstnction does not cause loading of

thereset vector, butdoos assertthoresatine >

resetextornaldovioos, This allows the sofware

to rset the systam toa known sale and thon

contin processing wih the nox instruction.

Intecrupte

Seveniovelsofintrupt prices are provided.

Devices may ba chained oxtomaly witinintr-

‘upt prority levels, lowing an unkimitod num

ber of peripheral devices to inerupt tho

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Relay de ReemplazoDocument3 pagesRelay de ReemplazoErasmo FrancoNo ratings yet

- Treadmill DC Motor MC-60 Control - CTM ProjectsDocument1 pageTreadmill DC Motor MC-60 Control - CTM ProjectsErasmo FrancoNo ratings yet

- MT! Service ManualDocument60 pagesMT! Service ManualErasmo FrancoNo ratings yet

- Operation Manual E-Series ET Analog 551890 enDocument33 pagesOperation Manual E-Series ET Analog 551890 enErasmo FrancoNo ratings yet

- Data Sheet Preliminary Jun83Document40 pagesData Sheet Preliminary Jun83Erasmo FrancoNo ratings yet

- SN75115Document11 pagesSN75115Erasmo FrancoNo ratings yet

- SBC 186-410Document12 pagesSBC 186-410Erasmo FrancoNo ratings yet

- MAX696 MaximDocument16 pagesMAX696 MaximErasmo FrancoNo ratings yet

- M5K4164AP 12 MitsubishiDocument11 pagesM5K4164AP 12 MitsubishiErasmo FrancoNo ratings yet

- Tma Datasheet 3049640Document5 pagesTma Datasheet 3049640Erasmo FrancoNo ratings yet

- SK70WT SemikronInternationalDocument2 pagesSK70WT SemikronInternationalErasmo FrancoNo ratings yet

- Semikron Sk70gar063Document4 pagesSemikron Sk70gar063Erasmo FrancoNo ratings yet

- Pcm5820 SeriesDocument120 pagesPcm5820 SeriesErasmo FrancoNo ratings yet

- AS3711 Datasheet EN v1-1214616Document104 pagesAS3711 Datasheet EN v1-1214616Erasmo FrancoNo ratings yet

- M5M51008CFP MitsubishiElectricSemiconductorDocument7 pagesM5M51008CFP MitsubishiElectricSemiconductorErasmo FrancoNo ratings yet