Professional Documents

Culture Documents

GDP 2265-Spec-Sheet

Uploaded by

pranavCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

GDP 2265-Spec-Sheet

Uploaded by

pranavCopyright:

Available Formats

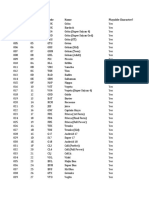

SINGLE/DUAL/QUAD

PCM BIT SYNCHRONIZER

Model 2265

Features General Description

The GDP Model 2265 Multi-

Up to 4 Channels in 2U Box Channel PCM Bit Synchronizer

Bit Rates houses up to 4 high-

5 bps to 20 Mbps performance bit synchronizer

5 bps to 40 Mbps (Opt) channels in a 2U chassis. The optimized digital design of this unit affords

Performance within 1 dB of the highest performance characteristics currently available.

theory The Model 2265 is capable of maintaining synchronization with the signal

Advanced Lock Detection of interest down to –3 dB Eb/No at a signal level as low as 100 mVpp.

Loop Bandwidth Settings When searching for the signal, acquisition is attainable in less than 50 bits.

from 0.01% to 1.6% The unit can maintain synchronization for a period of at least 256 bit

periods without a transition.

Extended LBW (Opt)

Accepts NRZ-L/M/S, BiØ-L/ The standard IRIG randomizer/derandomizer for both forward and reverse

M/S, DM-M/S; MDM-M/S sequences is provided. (Other randomizer/derandomizers are available.)

CCITT V.35 and V.36 scrambling/descrambling is also provided. A

Bit Rate Deviation Indication variety of Viterbi decoders are available including R1/2 K7 (Std), R3/4

Randomizer/Derandomizer K7 and R1/3 k7 (please inquire for other FEC options).

Scrambler/Descrambler To assure synchronization to the intended data stream, the Frame Pattern

CCITT V.35 / V.36 Detector may be invoked. Up to a 64-bit long pattern is detected.

Convolution Encoder Maintaining synchronization with this pattern at the programmed

Viterbi Decoder repetition rate and synchronization strategy produces a lock signal. An

Frame Pattern Detector Automatic Polarity Correction (APC) mode is also provided for inverted

data.

Input Signal Status

Sync and Signal Loss Each of the channels includes up to four Analog inputs. Additional inputs

are optionally available for RS-422 and TTL levels. Each channel

Measured Input Bit Rate provides a variety of outputs that include; three independent

Measured Signal Level programmable TTL Coded PCM outputs and one TTL Auxiliary Coded

Input Data Polarity output (4 total), two independently programmable (0, 90, 180 and 270

Signal/Data Quality Status degree) TTL Clock outputs and one TTL Auxiliary Clock output (3 total),

Eb/No Measurement two RS-422 Coded PCM and two RS-422 Clock outputs. Front Panel

Monitor BNCs are provided for each channel that include one Selected

BER / CER Measurement

Input Monitor, one PCM Data Out and one Clock Out

BERT PRN

Signal Level Measurement The MD2265 includes several unique features to determine the quality of

the data. The first is an Eb/No (Signal Quality) measurement. From this

Date Generator/Simulator

measurement the error rate of the data can be determined. The MD2265

Serial and QPSK(Opt) also measures errors in the frame synchronizer pattern as well as errors in

Auto Bit-Rate Scan (Opt) the Viterbi stream when these modes are enabled. A bit-error-rate

OPSK/OQPSK/SOQPSK (BERT) function is also provided. This allows link tests in a short loop-

Resequencer (opt) back to verify proper operation of the module, or long loop-back to

Remote Control via. measure performance of the link. An advanced lock detector ensures a

RS-232 (Std) solid lock indication for the bit synchronizer.

Ethernet (Opt) An Auto Scan feature is available that scans the input for up to 8

IEEE-488 (Opt) combinations of bit rates, input codes FEC and frame patterns (per Bit

Sync). When the signal criteria is present, the Bit Sync automatically

locks and recovers the data and clock.

300 Welsh Road · Building 3 · Horsham, PA 19044-2273 URL: http://www.gdpspace.com

Phone: 215-657-5242 Fax: 215-657-5273 E-mail: gdpinfo@gdpspace.com

SINGLE/DUAL/QUAD

PCM BIT SYNCHRONIZER

Model 2265

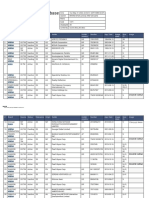

SPECIFICATIONS

Inputs, each Bit Sync

Analog Inputs Up to 4 Inputs per Bit Sync- 50 ohms (optional 75) or High Z

Digital Inputs Differential RS-422 and TTL (Optional)

Performance

Bit Rate Range 5 bps to 20 Mbps (40 Mbps Optional)

Tuning Resolution X.XXXEN (1≤N≤7)

Input Levels 0.1 Vp-p Min., +/- 12 V Max.. (others available)

DC Offsets DC Offset + peak input signal without exceeding Level limits.

AC Offset No degradation up to 100% of input signal amplitude at 0.1% of the bit rate.

Loop Bandwidths 0.01% to 1.6% (Extended LBW Range Optional)

Acquisition Range 2x LBW

Sync Acquisition Threshold SNR 0 dB

Sync Maintenance SNR –3 dB

Sync Acquisition < 50 bits

Sync Retention 256 bits without transitions

Bit Error Rate < 1 dB from theory to 40 Mbps

Features

Input/Output PCM Codes NRZ-L/M/S, BIǾ-L/M/S, DBIǾ-M/S, DM-M/S; MDM-M/S

Randomizer/Derandomizer IRIG 106 forward and reverse (Others Available)

Descrambler CCITT V.35/V.36

Viterbi Decoder R 1/2, K 7 with G1/G2 Swap and G2 Invert, (others available)

Resequencer QPSK/OQPSK/SOQPSK (Optional)

Frame Pattern Detector Up to 64 bits with programmable strategy and APC

Auto Scan (Optional) Searches up to 8 Bit Rate, Code, Frame pattern, FEC sets per Bit Sync

Output Data Polarity Same as Input polarity / inverted.

Output Clock Phase 0, 90, 180 & 270 degrees to 20 Mbps; 0 & 180 degrees 20 Mbps to 40 Mbps

BERT Function Bit-Error-Rate Generator/Error Detector (PRN 11/15) (Optional)

Outputs, each Bit Sync Channel

TTL (Each Channel)- Coded PCM and Clocks (Programmable 0, 90, 180, 270 degrees)

RS422 (Each Channel)- Coded PCM and Clock (Programmable 0, 90, 180, 270 degrees)

Bipolar Tape Output (Each Channel)- +/-1V - Coded PCM

Front Panel Monitor (Each Channel)- Selected Input Monitor, PCM Data Out, Clock Out

Composite Lock Status - Bit Synchronization, Frame Pattern and Viterbi

Signal Quality Status: Presented on Front Panel and Remote Port: Bit Sync Lock, Eb/No, Bit Rate Deviation,

Signal Presence, Signal Level, Bit Sync Lock-Loss-Count, and PRN BER/CER

Ordering Information

MD2265-02 Basic Dual Channel Unit (20 Mbps) OP2265-22 Ethernet Remote Control

MD2265-04 Basic Quad Channel Unit (20 Mbps) OP2265-40 Special Rear I/O

MD2265-01 Basic Single Channel Unit (20 Mbps) OP2265-41 Recirculate (NRZ-L & Clk In/ RNRZ Out)

OP2265-01 Operation to 40 Mbps OP2265-43 BERT Option

OP2265-05 QPSK & OQPSK Support OP2265-45 Auto Scan Option

OP2265-06 SOQPSK Support OP2265-70 75 Ohm option

OP2265-07 QPSK & OQPSK & SOQPSK OP2265-91 Extended Loop Bandwidth Range

OP2265-21 IEEE-488 Remote Control OP2265-92 Reed Solomon Option

Recognizing that no standard product can meet all the needs of all The statements in this data sheet are not intended to create any warranty,

users, GDP stands ready to provide units tailored to unique expressed or implied. Equipment specifications are subject to change without

applications. notice.

R101110

300 Welsh Road · Building 3 · Horsham, PA 19044-2273 URL: http://www.gdpspace.com

Phone: 215-657-5242 Fax: 215-657-5273 E-mail: gdpinfo@gdpspace.com

You might also like

- Satellite ModemDocument2 pagesSatellite ModemalifshahNo ratings yet

- Bit SyncDocument2 pagesBit SyncbansipmNo ratings yet

- Datum PSM 500LT Satellite TerminalDocument2 pagesDatum PSM 500LT Satellite TerminalrazfanmnNo ratings yet

- Modem Psm-500: Product Presentation SheetDocument2 pagesModem Psm-500: Product Presentation SheetgoodgranitNo ratings yet

- AMT 75 Broadcast Modem High-Performance DVB-S2Document3 pagesAMT 75 Broadcast Modem High-Performance DVB-S2Anonymous LU6nvFNo ratings yet

- Paradise Datacom PD20 Satellite ModemDocument5 pagesParadise Datacom PD20 Satellite ModemarzeszutNo ratings yet

- BX11 ManualDocument2 pagesBX11 ManualzakirfNo ratings yet

- OSM-300 Series: New Fea Tures FOR 2009Document2 pagesOSM-300 Series: New Fea Tures FOR 2009francescoli80No ratings yet

- Description Features: ENC6800+ENS6800+Document2 pagesDescription Features: ENC6800+ENS6800+David ToroNo ratings yet

- SM6615 Satellite Modulator: Product Overview Base Unit FeaturesDocument2 pagesSM6615 Satellite Modulator: Product Overview Base Unit FeaturesJose RivasNo ratings yet

- Product Photo: 27mm×13mm×2mmDocument11 pagesProduct Photo: 27mm×13mm×2mmUchija Darck KhronosNo ratings yet

- MT9M032: 1/4.5-Inch 1.6Mp CMOS Digital Image Sensor FeaturesDocument19 pagesMT9M032: 1/4.5-Inch 1.6Mp CMOS Digital Image Sensor FeaturesVenu Gopal Reddy BonthaNo ratings yet

- Dvb-T-T2-C ReceiverDocument2 pagesDvb-T-T2-C Receiverthagha mohamedNo ratings yet

- Product Data Sheet0900aecd806ced61Document5 pagesProduct Data Sheet0900aecd806ced61Mary V. LopezNo ratings yet

- Datum PSM-500 DatasheetDocument2 pagesDatum PSM-500 DatasheetThanh LeNo ratings yet

- Adc A4bcdDocument3 pagesAdc A4bcdDavid ToroNo ratings yet

- USB DTV Modulator: TVB595CDocument2 pagesUSB DTV Modulator: TVB595CArifBP - DTBDNo ratings yet

- MICRO DISTRIBUTED Catalog Rev GDocument4 pagesMICRO DISTRIBUTED Catalog Rev GMilorad PavlovicNo ratings yet

- Jdsu SmartclassDocument4 pagesJdsu SmartclassEfrain CahuanaNo ratings yet

- TELECOM Training LabDocument20 pagesTELECOM Training LabLuis BatistaNo ratings yet

- DEC 1003.datasheet - enDocument2 pagesDEC 1003.datasheet - enPrabheesh Nalukandathil MeethalNo ratings yet

- Vsat ViasatDocument2 pagesVsat Viasatvsharma26No ratings yet

- Chip Philips Toucam ProII Saa8116hlDocument20 pagesChip Philips Toucam ProII Saa8116hlEduardo AlamillaNo ratings yet

- Cisco D9854Document8 pagesCisco D9854denismoraes.toNo ratings yet

- AZ110 DatasheetDocument2 pagesAZ110 DatasheetJuana SosaNo ratings yet

- IDR CwIDU LC Presentation Edition2Document142 pagesIDR CwIDU LC Presentation Edition2nion83No ratings yet

- Codico E-1510 DSNG Exciter: GeneralDocument2 pagesCodico E-1510 DSNG Exciter: GeneralMladenovic SlobodanNo ratings yet

- CXD2854ER: Combined DVB-T2/DVB-T/DVB-C2/DVB-C/DVB-S2/DVB-S/ISDB-T/SBTVD-T/ISDB-S DemodulatorDocument39 pagesCXD2854ER: Combined DVB-T2/DVB-T/DVB-C2/DVB-C/DVB-S2/DVB-S/ISDB-T/SBTVD-T/ISDB-S DemodulatorJuan MatiasNo ratings yet

- Eurostar ManualDocument2 pagesEurostar ManualSarvesh Parmanand Seebundhun50% (2)

- JDSU SmartClass E1 Data Ds Acc TM AeDocument4 pagesJDSU SmartClass E1 Data Ds Acc TM AeAghil Ghiasvand MkhNo ratings yet

- Radyne QAM256Document2 pagesRadyne QAM256timmylau23No ratings yet

- Pasolink Training in VietnamDocument332 pagesPasolink Training in Vietnamtuannv191177100% (1)

- 73K324L CCITT V.22bis, V.22, V.21, V.23, Bell 212A Single-Chip ModemDocument32 pages73K324L CCITT V.22bis, V.22, V.21, V.23, Bell 212A Single-Chip ModemRicardo MercadoNo ratings yet

- 4 Channel HD Video Encoder RF Modulator, 4 Video Inputs, 1-4 Channel Output, With IP Video Ouput and ASI Output, Support AC3 AudioDocument1 page4 Channel HD Video Encoder RF Modulator, 4 Video Inputs, 1-4 Channel Output, With IP Video Ouput and ASI Output, Support AC3 AudiothorbroadcastNo ratings yet

- pcm1716 PDFDocument19 pagespcm1716 PDFRosa CruzNo ratings yet

- Catalog GQ-3670B PDFDocument2 pagesCatalog GQ-3670B PDFAndres Alberto ParraNo ratings yet

- Encoder 9034Document5 pagesEncoder 9034Ady AndyyNo ratings yet

- Satcom Technologies Volume 2 v125Document28 pagesSatcom Technologies Volume 2 v125ธนวรรณ โภคาอนนต์No ratings yet

- High-quality signal generator for broadcast testingDocument7 pagesHigh-quality signal generator for broadcast testingjsrt234956No ratings yet

- D9154 H.264 Encoder - Prelim Data Sheet - 7005029 PreA3.1Document3 pagesD9154 H.264 Encoder - Prelim Data Sheet - 7005029 PreA3.1juhi993No ratings yet

- HDX6803+D: Auto-Sensing 3G/HD/SD Demultiplexer With Up To 8 AES OutputsDocument5 pagesHDX6803+D: Auto-Sensing 3G/HD/SD Demultiplexer With Up To 8 AES OutputsRamez AbdulsalamNo ratings yet

- Q-Flex Data Sheet 210058 RevCDocument5 pagesQ-Flex Data Sheet 210058 RevCarzeszutNo ratings yet

- Curso de TV Plasma Part - 2Document40 pagesCurso de TV Plasma Part - 2s0nytechNo ratings yet

- Powervu Model D9852 Dual Decrypt Program Receiver: DescriptionDocument4 pagesPowervu Model D9852 Dual Decrypt Program Receiver: DescriptionDAVID RodríguezNo ratings yet

- Wireless Communications SolutionsDocument4 pagesWireless Communications SolutionsVan DUng VuNo ratings yet

- PCIUT3100Document2 pagesPCIUT3100Enrique ContrerasNo ratings yet

- IC CXD3068Q DatasheetDocument134 pagesIC CXD3068Q Datasheetnaupas007No ratings yet

- 4 Digit 7 Segment DisplayDocument3 pages4 Digit 7 Segment DisplayPraveen ChaudharyNo ratings yet

- Uda1334 - Audio DacDocument23 pagesUda1334 - Audio DacRegis DantasNo ratings yet

- 1st OptmDocument57 pages1st OptmMaximo Eduardo Santiago NairaNo ratings yet

- RN-171 802.11 B/G Wireless LANDocument16 pagesRN-171 802.11 B/G Wireless LANAnonymous 60esBJZIjNo ratings yet

- WDH-1500P Single Channel MPEG-2 SD IRDDocument2 pagesWDH-1500P Single Channel MPEG-2 SD IRDGoran BogdanovskiNo ratings yet

- Modicon M241 - TM241CEC24TDocument15 pagesModicon M241 - TM241CEC24TFuad JahićNo ratings yet

- SL 2048Document2 pagesSL 2048Eason NohNo ratings yet

- Communications and Data HandlingDocument57 pagesCommunications and Data HandlingpranavNo ratings yet

- MIL STD 1553 Seminar CondensedDocument35 pagesMIL STD 1553 Seminar CondensedrohitvanNo ratings yet

- Computing The Julian Day & TimeDocument10 pagesComputing The Julian Day & TimepranavNo ratings yet

- Material Property Charts Lecture Unit 2 Pptchaen23Document22 pagesMaterial Property Charts Lecture Unit 2 Pptchaen23pranavNo ratings yet

- Design High-Accuracy Attitude Stabilization System for Marine Satellite AntennaDocument19 pagesDesign High-Accuracy Attitude Stabilization System for Marine Satellite AntennaDouglas LimaNo ratings yet

- 96 ProcDocument1,073 pages96 ProcpranavNo ratings yet

- 90 ProcDocument1,104 pages90 ProcpranavNo ratings yet

- Network DevicesDocument21 pagesNetwork DevicesKishan KumarNo ratings yet

- 4270 Vlan TutorialDocument21 pages4270 Vlan TutorialAsma Lata LataNo ratings yet

- Maturity ModelsDocument28 pagesMaturity Modelsalakh400No ratings yet

- Datasheet UK Isolation TransformerDocument2 pagesDatasheet UK Isolation TransformerraveensanjeewaNo ratings yet

- V and Roogen Broeck 2012 SatelliteDocument70 pagesV and Roogen Broeck 2012 SatelliteCandidoMolanesNo ratings yet

- Dunya Report - 2Document46 pagesDunya Report - 2fsq82No ratings yet

- Mayoornews Letter July Edition - DocumentDocument1 pageMayoornews Letter July Edition - DocumentRaunaq Raj GuptaNo ratings yet

- Mosi DebatDocument8 pagesMosi DebatNurulNo ratings yet

- Best '80s Movies StreamingDocument2 pagesBest '80s Movies Streamingmakmare93No ratings yet

- Kristiana Britanik Resumé-2021Document1 pageKristiana Britanik Resumé-2021Kristiana BritanikNo ratings yet

- X200by Best Combo CloudDocument11 pagesX200by Best Combo CloudEcho VespertilioNo ratings yet

- karadio_playlistDocument7 pageskaradio_playlistmipNo ratings yet

- Elderly Widower's AdventureDocument1 pageElderly Widower's AdventureNadine PantiNo ratings yet

- Anti-Drugs Short FIlm Competition Terms and ConditionsDocument1 pageAnti-Drugs Short FIlm Competition Terms and ConditionsMemei PachuauNo ratings yet

- Oxford Reading Tree: at The ParkDocument12 pagesOxford Reading Tree: at The ParkKanjaNo ratings yet

- Instructive FunctionDocument2 pagesInstructive FunctionMJ ColumbresNo ratings yet

- How to make a welcome videoDocument11 pagesHow to make a welcome videoAdrià Caus CañellasNo ratings yet

- Muhammadu Irkoy Diya Bortaray Kaŋ Cine Ga GaabuDocument210 pagesMuhammadu Irkoy Diya Bortaray Kaŋ Cine Ga GaabuIslamic Books for E-Readers and TTS AppsNo ratings yet

- (DAILY CALLER OBTAINED) -- Banks 175 XMLDocument2 pages(DAILY CALLER OBTAINED) -- Banks 175 XMLHenry RodgersNo ratings yet

- General Info: Pre-Production Planning Document (PODCAST)Document6 pagesGeneral Info: Pre-Production Planning Document (PODCAST)ricky pateal100% (1)

- WIPO Global Brand Database search results for "Party arena" AND "GameDocument3 pagesWIPO Global Brand Database search results for "Party arena" AND "Game诺伊No ratings yet

- Incubus - Wish You Were Here Sheet Music For Bass (Tablature) (Bass Guitar)Document1 pageIncubus - Wish You Were Here Sheet Music For Bass (Tablature) (Bass Guitar)Star0fthesh0wNo ratings yet

- Vitti Chettiar Meyappa Chettiar: (Founder of Ar.L.Firm&Trust) / (Ar.L Begins With 3 Sons)Document9 pagesVitti Chettiar Meyappa Chettiar: (Founder of Ar.L.Firm&Trust) / (Ar.L Begins With 3 Sons)sundar20071989No ratings yet

- Rembrandt Paintings: A Corpus ofDocument814 pagesRembrandt Paintings: A Corpus ofEVIP1No ratings yet

- PR Methods & ToolsDocument4 pagesPR Methods & ToolsKomal VaityNo ratings yet

- Gingerbread FreebieDocument13 pagesGingerbread Freebiemiguel_carina7684No ratings yet

- Routenote Style Guide - Jan2020Document14 pagesRoutenote Style Guide - Jan2020Mostafa SrNo ratings yet

- Wizard Magazine 004 (1991) (No Guide)Document43 pagesWizard Magazine 004 (1991) (No Guide)Teddy Ray CarianNo ratings yet

- Dhabannahays-garanuug.comDocument288 pagesDhabannahays-garanuug.comYoonis Cumar100% (1)

- Contact list with names, emails, and mobile numbersDocument366 pagesContact list with names, emails, and mobile numbersDarshan S AcharyaNo ratings yet

- Dimpy Chandbhan Google SearchDocument1 pageDimpy Chandbhan Google SearchMulayam KhanguraNo ratings yet

- Hero Hindi Bryne RhondaDocument165 pagesHero Hindi Bryne RhondaSwathi PriyaNo ratings yet

- Demons Xenoverse ID ListDocument86 pagesDemons Xenoverse ID ListGonzalo Cardozo100% (1)

- Acknowledgments B1+Document7 pagesAcknowledgments B1+Houssayen BenouhibaNo ratings yet

- Charizard - Google SearchDocument1 pageCharizard - Google Searchrrgqbj8t9bNo ratings yet