Professional Documents

Culture Documents

Sine Rom

Uploaded by

Mestr Said Chouchf0 ratings0% found this document useful (0 votes)

0 views1 pageThis document defines a ROM entity that stores pre-calculated sine wave values. The ROM takes in an address and outputs the corresponding sine value stored at that address. It initializes the ROM by calculating sine values for each possible address and storing them in the ROM array during compilation. On each clock cycle, it outputs the value stored at the input address.

Original Description:

Original Title

sine_rom

Copyright

© © All Rights Reserved

Available Formats

TXT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document defines a ROM entity that stores pre-calculated sine wave values. The ROM takes in an address and outputs the corresponding sine value stored at that address. It initializes the ROM by calculating sine values for each possible address and storing them in the ROM array during compilation. On each clock cycle, it outputs the value stored at the input address.

Copyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

0 views1 pageSine Rom

Uploaded by

Mestr Said ChouchfThis document defines a ROM entity that stores pre-calculated sine wave values. The ROM takes in an address and outputs the corresponding sine value stored at that address. It initializes the ROM by calculating sine values for each possible address and storing them in the ROM array during compilation. On each clock cycle, it outputs the value stored at the input address.

Copyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

You are on page 1of 1

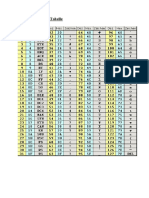

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use ieee.math_real.all;

entity sine_rom is

generic (

addr_bits : integer range 1 to 30;

data_bits : integer range 1 to 31

);

port (

clk : in std_logic;

addr : in unsigned(addr_bits - 1 downto 0);

data : out unsigned(data_bits - 1 downto 0)

);

end sine_rom;

architecture rtl of sine_rom is

subtype addr_range is integer range 0 to 2**addr_bits - 1;

type rom_type is array (addr_range) of unsigned(data_bits - 1 downto 0);

-- Fill the ROM with sine values

function init_rom return rom_type is

variable rom_v : rom_type;

variable angle : real;

variable sin_scaled : real;

begin

for i in addr_range loop

angle := real(i) * ((2.0 * MATH_PI) / 2.0**addr_bits);

sin_scaled := (1.0 + sin(angle)) * (2.0**data_bits - 1.0) / 2.0;

rom_v(i) := to_unsigned(integer(round(sin_scaled)), data_bits);

end loop;

return rom_v;

end init_rom;

constant rom : rom_type := init_rom;

begin

ROM_PROC : process(clk)

begin

if rising_edge(clk) then

data <= rom(to_integer(addr));

end if;

end process;

end architecture;

You might also like

- VHDL Code For Half Adder by Data Flow ModellingDocument14 pagesVHDL Code For Half Adder by Data Flow ModellingPrateekKumar96% (24)

- VHDL Quick Reference CardDocument2 pagesVHDL Quick Reference CardAndrés Sebastián MorenoNo ratings yet

- Digital Design With HDLDocument29 pagesDigital Design With HDLw.nNo ratings yet

- Ram 1Document1 pageRam 1bhslegion1498No ratings yet

- VHDL 4 RTL ModelsDocument33 pagesVHDL 4 RTL ModelsNguyễn Minh NghĩaNo ratings yet

- Microprocessor Exam PaperDocument11 pagesMicroprocessor Exam PaperTomas MacsweeneyNo ratings yet

- VHDL 5 Memory ModelsDocument14 pagesVHDL 5 Memory Modelsganga_ch1No ratings yet

- Codigo C#: Using Using Using Namespace Public Partial Class New PublicDocument2 pagesCodigo C#: Using Using Using Namespace Public Partial Class New PublicLuis Enrique GarcíaNo ratings yet

- C Standard LibraryDocument17 pagesC Standard LibraryKondamahesh100% (1)

- VHDLDocument73 pagesVHDLuninorsasta100% (1)

- Cad of Electronics LabDocument4 pagesCad of Electronics LabVaibhav PandeyNo ratings yet

- VHDL Revaluation ReportDocument5 pagesVHDL Revaluation Reportapophysis6No ratings yet

- V HDL SampleDocument5 pagesV HDL Sampleppat2006No ratings yet

- Organized InformatikDocument10 pagesOrganized InformatikChedy AbdNo ratings yet

- VHDL Packages, Coding Styles For Arithmetic Operations and VHDL-200x Additions - Presentation TranscriptDocument9 pagesVHDL Packages, Coding Styles For Arithmetic Operations and VHDL-200x Additions - Presentation TranscriptPrasad L. PanditNo ratings yet

- Data Type and Type Conversion in CDocument10 pagesData Type and Type Conversion in CcarlosptelefonicaNo ratings yet

- C# NotesDocument40 pagesC# NotesSuman DmNo ratings yet

- Cadence Nclaunch LabDocument86 pagesCadence Nclaunch Labsweety987No ratings yet

- Array MultiplierDocument2 pagesArray MultiplierNitesh Chilakala50% (2)

- VhdlfileDocument7 pagesVhdlfileNaveen NegiNo ratings yet

- Digital Signals and DesignDocument27 pagesDigital Signals and DesignkannNo ratings yet

- Vsem EEE 18EE52 MC Module-3Document31 pagesVsem EEE 18EE52 MC Module-3SuprithaNo ratings yet

- C Standard Library: Tullio Facchinetti 8 Maggio 2012Document19 pagesC Standard Library: Tullio Facchinetti 8 Maggio 2012FilippoNo ratings yet

- Computer - Hardware: Arithmetic and Logic Unit Micro ProcessorDocument25 pagesComputer - Hardware: Arithmetic and Logic Unit Micro ProcessorHarsha NaiduNo ratings yet

- Computer - Hardware: Arithmetic and Logic Unit Micro ProcessorDocument25 pagesComputer - Hardware: Arithmetic and Logic Unit Micro ProcessorMaheshpbk BmNo ratings yet

- Computer - Hardware: Arithmetic and Logic Unit Micro ProcessorDocument25 pagesComputer - Hardware: Arithmetic and Logic Unit Micro Processor7killers4uNo ratings yet

- 3 Unit 3-Arduino Programming - 11march2022Document35 pages3 Unit 3-Arduino Programming - 11march2022patilamrutak2003No ratings yet

- Java Quiz SheetDocument2 pagesJava Quiz SheetMark CrossNo ratings yet

- Rogram No: 1 AIM: Write HDL Code To Realize All The Logic GatesDocument32 pagesRogram No: 1 AIM: Write HDL Code To Realize All The Logic GatesPranav LatkarNo ratings yet

- Using SystemDocument3 pagesUsing Systemtiensktdk1No ratings yet

- 4x1 MUXDocument6 pages4x1 MUXYash GuptaNo ratings yet

- Function DllCallDocument4 pagesFunction DllCallFabian ToroNo ratings yet

- Vlsi Lab NewDocument28 pagesVlsi Lab NewVinoth KumarNo ratings yet

- Date: 28 September, 2015: VHDL Assighment 2Document15 pagesDate: 28 September, 2015: VHDL Assighment 2Ishan DarwhekarNo ratings yet

- Lab 7 PPDocument2 pagesLab 7 PPMuhammad AliNo ratings yet

- Papr MDocument7 pagesPapr MasfsfsadsaNo ratings yet

- 02 Essential C Security 101Document76 pages02 Essential C Security 101ksmaheshkumarNo ratings yet

- Visual C# ProgrammingDocument47 pagesVisual C# ProgrammingAung Ko Ko ZawNo ratings yet

- VHDL Lab FileDocument48 pagesVHDL Lab FileAnkit Gupta100% (1)

- 8x8 FIFO Buffer VHDL DesignDocument2 pages8x8 FIFO Buffer VHDL DesignIgnacioMartíNo ratings yet

- Lecture05 Data TypesDocument59 pagesLecture05 Data TypesSwifty SpotNo ratings yet

- New Microprocessor 1-RecDocument14 pagesNew Microprocessor 1-RecAgnus S Swarna LakshmiNo ratings yet

- VHDL ProgramsDocument30 pagesVHDL ProgramsVijay Singh100% (1)

- Arithmetic Using Numeric STD: 1 Operators in VHDLDocument8 pagesArithmetic Using Numeric STD: 1 Operators in VHDLlitoduterNo ratings yet

- Practical 2: Aim: Implementation of Basic Logic Gates and Its TestingDocument19 pagesPractical 2: Aim: Implementation of Basic Logic Gates and Its TestingVarun PatelNo ratings yet

- 7 C Prgramming v21Document31 pages7 C Prgramming v21Pipat NakasenoNo ratings yet

- Writing VHDL For RTL Synthesis: 1 StructureDocument9 pagesWriting VHDL For RTL Synthesis: 1 StructuremmalgiNo ratings yet

- Verilog: Hardware Description LanguageDocument53 pagesVerilog: Hardware Description LanguageTejaswi ChoppaNo ratings yet

- Lab3 - Achmad Mauludin H. - 165060301111002Document4 pagesLab3 - Achmad Mauludin H. - 165060301111002Mauudin BRgNo ratings yet

- A Structured VHDL Design Method-Jiri GaislerDocument28 pagesA Structured VHDL Design Method-Jiri GaislerTho RaNo ratings yet

- Digital Circuits and Systems - IIDocument41 pagesDigital Circuits and Systems - IIAman ShroffNo ratings yet

- CombinedDocument70 pagesCombinedchirag yadavNo ratings yet

- Cse AssignmentDocument9 pagesCse AssignmentSai sasindhar MalapatiNo ratings yet

- 02a. Data Types-2Document35 pages02a. Data Types-2Tszkin WongNo ratings yet

- System Verilog ClassesDocument105 pagesSystem Verilog ClassesLikhithmohan VNo ratings yet

- VHDL Bram BromDocument9 pagesVHDL Bram BromGmit MandyaNo ratings yet