Professional Documents

Culture Documents

HPC Lesson Plan

HPC Lesson Plan

Uploaded by

rajshreed2014Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HPC Lesson Plan

HPC Lesson Plan

Uploaded by

rajshreed2014Copyright:

Available Formats

SCHOOL OF COMPUTER ENGINEERING

KALINGA INSTITUTE OF INDUSTRIAL TECHNOLOGY

DEEMED TO BE UNIVERSITY

BHUBANESWAR

LESSON – PLAN

School : School of Computer Engineering

Program : B. Tech. CSE

Academic Session : Autumn Semester 2023 (July. - November)

Subject : High Performance Computing (HPC) (CS 3010)

Course Cridit : 4 (L-T-P) (3-1-0) (Weekly 4 Hours)

Semester : 5th Semester

Course Faculty : Dr.Manoj Kumar Mishra

Mail_id : (manojfcs@kiit.ac.in)

Course Outcomes/Learning Objectives:

1. Understand different quantitative techniques used to measure the performance of the

system with various criteria like CPI, CPU time, speed up, throughput, efficiency, etc.

2. Understand the concept of different types of hazards along with their structural

implementation and applications.

3. Identify the criteria to enhance the performance of pipelined processors.

4. Understand ILP and the techniques to exploit ILP in scalar, super-scalar, super pipelined

processor, and the VLIW processor.

5. Understand memory hierarchy and to analyze various Cache optimization techniques.

6. Classify various parallel architecture like centralized and distributed memory architecture

Prerequisite: Computer Architecture (CS-2006)

Teaching Pedagogy: Whiteboard/Marker, PowerPoint Presentations, Web Resources

Assessment Methodology: Mid Term: 20; End Term: 50

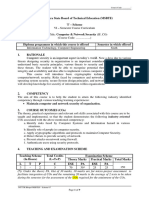

Distribution of Internal Marks:- Total 50 Marks

Mid Semester Examination = 20 Marks

Activity-based assessment=30 Marks

Activity-based assessment includes Problem Solving, Critical

Thinking, Creation along with Quiz.

LESSON – PLAN

Module No. & name / Topics/ Coverage Lecture serial COUrse No of

Section no. Name Number outcome classes

Introduction To High Lecture-1 CO 1

performance

Module-1

Computer

Architecture

Review of basic Lecture-2 CO-1

computer

architectures

Overview of

Computer

Architecture Introduction to Lecture -3 CO-1

09

instruction Set

architecture (ISA)

CISC & RISC

processor with

examples

Measuring and Lecture 4 CO-1

Reporting

Performance

Processor

performance

equation (with

numerical)

Performance

measurement with

respect to execution

time, CPU

time(concept with lecture 5

numerical)

Performance Lecture -6 CO-1

Measurement with

respect to the basic

performance

equation (concept Lecture -7

with numerical)

Amdahl’s law

(concept with

Exercises on

speedup and overall

speedup calculation) Lecture 8

Tutorial(Doubt Lecture 9 CO-1

clearing)

Activity -1

Problem

Solving/Critical

Thinking/Quiz

Module-2 Basic concepts to Lecture -10 CO-2 10

parallel processing &

pipelining pipelining Concept.

Introduction to Lecture-11 CO-2

MIPS Architecture

with its data path

Registers in MIPS

MIPS Instruction

Format(R type,I Lecture-12

Type and J type)

MIPS Instruction Lecture -13 CO-2

set with examples

MIPS Data-path and

Control

A brief introduction Lecture-14 CO-2

to Hazard and Types

of Hazards

(Concepts and

exercises) Lecture 15

Structural Hazard

Data Hazard (Inter-

instruction

dependency with

suitable examples:) Lecture-16

Control Hazard

Pipeline Stall Cycles Lecture-17

and its possible

effects on

performance

(Concepts and

exercises)

A technique for CO-2

overcoming or

reducing the

effects of Various

hazards (Solutions

to different

Lecture-18

Hazards) (concepts

and numericals)

Operand forwarding

and Instruction

Lecture -19

scheduling

Flush pipeline,

Branch Prediction,

Delay Slot

Lecture -20

Tutorial (doubt CO-2

clearing) Problem

Solving/Critical

Activity -2 Thinking/Quiz CO-2

Module-3 Concepts of Lecture-21 CO-3

instruction-level

Instruction

parallelism (ILP)

Level Techniques for Lecture-22 CO-3

increasing ILP

Parallelism 09

Dynamic branch

(ILP)

prediction

Loop Lecture-23 CO-3

unrolling(concepts

with Numerical)

Static scheduling Lecture-24 CO-4

With example

Dynamic scheduling Lecture-25 CO-4

Dynamic scheduling

approach

1.Scoreboard

approach (With

Numerical)

Lecture-29

2.Tomasulo’s

approach (With

Numerical)

Lecture-26

Super-scalar & Super Lecture-27 CO-4

pipelined

VLIW processor Lecture-28 CO-4

architecture

Tutorial (DOUBT CO-4

clearing)

Problem

Solving/Critical

Activity-3 CO-4

Thinking/Quiz

Mid sem exam

Module-4 Memory hierarchy Lecture-29 CO-5 09

(Inclusion, Coherence

Hierarchical

and locality

Memory properties)

Technology

Cache memory Lecture-30 CO-5

organization

Block Placement

Block Identification

Block Replacement

Write Strategy

Lecture-31

Cache Memory Lecture-32 CO-5

Performance

evaluation (concepts

and numerical

examples)

Cache Memory Lecture-33 CO-5

Optimization

Techniques (concepts

and numerical

examples)

Reduce miss rate. Lecture-34 CO-5

Larger block size

Larger cache size

Higher associativity

Lecture-35

Reduce miss penalty. Lecture-36 CO-5

Multilevel caches

Priority to Read

Misses over Writes

Reduce hit time. Lecture-37 CO-5

Avoiding address

translation

Tutorial(Doubt CO-5

clearinf)

Activity-4 CO-5

Problem

Solving/Critical

Thinking/Quiz

Module-5 Taxonomy of Parallel Lecture-38 CO-6 9

Architecture

Multiprocessor

Architecture

Multiprocessor Lecture-39 CO-6

Systems

Centralized Shared-

memory architecture

(Tightly coupled

multiprocessor like

UMA)

Distributed Shared Lecture-40 CO-6

memory architecture

(Loosely coupled

multiprocessor like

NUMA)

Lecture-41

Cache coherence Lecture-42 CO-6

Mechanism

Snooping Lecture-43 CO-6

protocol(Concepts

and numerical

examples)

Directory-based Lecture-44 CO-6

protocol(Concepts

and numerical

examples)

Tutorial(Doubt Lecture-45 CO-6

clearing)

Activity 5 and CO-6

Activity 6

Problem

Solving/Critical

Thinking/Quiz

Previous year Q and Lecture-46

answer discussion

Text Book :

1. John L. Hennessy and David A. Patterson, Computer Architecture: A Quantitative

Approach, Morgan Kaufmann.

References Books :

1. John Paul Shen and Mikko H. Lipasti, Modern Processor Design: Fundamentals of

Superscalar Processors, Tata McGraw-Hill.

2. M. J. Flynn, Computer Architecture: Pipelined and Parallel Processor Design, Narosa

Publishing House.

3. Kai Hwang, Advanced Computer Architecture: Parallelism, Scalability,

Programmability, McGraw- Hill.

Dr. Manoj Kumar Mishra

Signature

You might also like

- Fundamentals of Computer ScienceDocument105 pagesFundamentals of Computer ScienceBlackyNo ratings yet

- Creative Computing v09 n10 1983 OctoberDocument340 pagesCreative Computing v09 n10 1983 OctoberAthalberth Athalberth MarqezNo ratings yet

- Introduction To C Programming Notes PDFDocument425 pagesIntroduction To C Programming Notes PDFPremavathiDamodharan100% (2)

- Unit1 - Programming - Scheme of Work - TungdtDocument4 pagesUnit1 - Programming - Scheme of Work - Tungdtl1111c1anh-5No ratings yet

- Eglobe User Manual V 1.4 2012-08-07Document191 pagesEglobe User Manual V 1.4 2012-08-07ajshsu568267% (12)

- MCS 012 SolvedDocument21 pagesMCS 012 SolvedPayal MashruNo ratings yet

- TRIA - 6000 Manual PainelDocument11 pagesTRIA - 6000 Manual PainelIsaac Azevedo67% (3)

- 21CS32Document5 pages21CS32sharath.aiNo ratings yet

- Nptel: Parallel Computing - Video CourseDocument3 pagesNptel: Parallel Computing - Video CourseAnu PriyaNo ratings yet

- Final Lesson Plan Cs TheoryDocument16 pagesFinal Lesson Plan Cs TheoryKrushnasamy SuramaniyanNo ratings yet

- 01 - Introduction To Computer and AlgorithmDocument44 pages01 - Introduction To Computer and AlgorithmCt Kamariah Md SaatNo ratings yet

- DPCO Syllabus (Theory Cum Practical)Document2 pagesDPCO Syllabus (Theory Cum Practical)yogeshwaran.r2022lcseNo ratings yet

- COA HANDOUT - ModifiedDocument20 pagesCOA HANDOUT - ModifiedVani telluriNo ratings yet

- Handout From ERPDocument22 pagesHandout From ERPsowmya kambhampatiNo ratings yet

- SyllabusDocument17 pagesSyllabusShanmuk ReddyNo ratings yet

- Ballari Institute of Technology & Management, Ballari Department of Computer Science and Engg. Course Outcomes 2014-2018Document5 pagesBallari Institute of Technology & Management, Ballari Department of Computer Science and Engg. Course Outcomes 2014-2018suryakiranaNo ratings yet

- M-CO VISemProgrammingWithPython L (CO, IF) 141220181911Document10 pagesM-CO VISemProgrammingWithPython L (CO, IF) 141220181911Vishal WankhedeNo ratings yet

- Course Outline - CSE 211 - Computer Architecture - 193 DCDocument5 pagesCourse Outline - CSE 211 - Computer Architecture - 193 DCgtgtdfgfdgNo ratings yet

- Introduction To Computing-TheoryDocument9 pagesIntroduction To Computing-Theorykashiijaam008No ratings yet

- Signals & Systems Theory - 4th Semester-C - Lesson PlanDocument5 pagesSignals & Systems Theory - 4th Semester-C - Lesson PlansakibNo ratings yet

- M-CO - VISemDataWarehousingAndMining (CO, IF) - NEW - 141220181910Document9 pagesM-CO - VISemDataWarehousingAndMining (CO, IF) - NEW - 141220181910Sadik PimpalkarNo ratings yet

- Course Plan Control Engg 2020-2021Document7 pagesCourse Plan Control Engg 2020-2021Satheeswaran VNo ratings yet

- Syllabus and Scheme of BOC 12-7-16Document4 pagesSyllabus and Scheme of BOC 12-7-16candiescrusher20No ratings yet

- Course Profile - CSE 122Document4 pagesCourse Profile - CSE 122Md. Ramjan Ali 211021003No ratings yet

- AML - Theory - Syllabus - Chandigarh UniversityDocument4 pagesAML - Theory - Syllabus - Chandigarh UniversityMohd YusufNo ratings yet

- IF-CO WebBasedApplicationDevelopmentWithPHP 141220181908 GAE3Document9 pagesIF-CO WebBasedApplicationDevelopmentWithPHP 141220181908 GAE3imranNo ratings yet

- COA (EET2211) Assignment1Document3 pagesCOA (EET2211) Assignment1Madhusmita PandaNo ratings yet

- Syllabus - CO Wise - Programming For Problem Solving (KCS-101/KCS-201) - 2020-21Document192 pagesSyllabus - CO Wise - Programming For Problem Solving (KCS-101/KCS-201) - 2020-21ishika sharmaNo ratings yet

- Develop Applications Using Oops Concepts in C++Document8 pagesDevelop Applications Using Oops Concepts in C++pawaryogeshNo ratings yet

- Pragati Engineering College (Autonomous) : Department of Computer Science and EngineeringDocument157 pagesPragati Engineering College (Autonomous) : Department of Computer Science and EngineeringPattabhi Ram MohanNo ratings yet

- Course handout-21SC1101Document32 pagesCourse handout-21SC1101unique engineerNo ratings yet

- Co Po McaDocument3 pagesCo Po Mcaparatevedant1403No ratings yet

- Computer Corse Hand OutDocument41 pagesComputer Corse Hand OutSri pallaviNo ratings yet

- CA CourseFile AssignmentDocument14 pagesCA CourseFile AssignmentLaxman SinghNo ratings yet

- Week CO Topics Teaching Activities Assessment/Evaluation MethodDocument3 pagesWeek CO Topics Teaching Activities Assessment/Evaluation Methodleserdrac333No ratings yet

- CST202 - Ktu QbankDocument12 pagesCST202 - Ktu QbankYaseen 777No ratings yet

- DAA Content Preparation FormatDocument2 pagesDAA Content Preparation FormatSowmya KoneruNo ratings yet

- 1st Year Syllabus 23-24 - New CompressedDocument183 pages1st Year Syllabus 23-24 - New Compressedmsyashwanth432005No ratings yet

- Technical Skilling-3Document11 pagesTechnical Skilling-3Go StargNo ratings yet

- 1151CS110 Computer Organization and ArchitectureDocument2 pages1151CS110 Computer Organization and ArchitectureArun Kumar DashNo ratings yet

- Department of Computer Science and Engineering (CSE) : United International University Course SyllabusDocument4 pagesDepartment of Computer Science and Engineering (CSE) : United International University Course Syllabussabbir hossainNo ratings yet

- CSC128 - Lesson Plan (1E)Document3 pagesCSC128 - Lesson Plan (1E)محمد فائزNo ratings yet

- CSE 405 OutlineDocument4 pagesCSE 405 OutlinefaiNo ratings yet

- HjgjhgfytrtyDocument7 pagesHjgjhgfytrtyMohamed Ahmed Farouk Elsayed RadyNo ratings yet

- VNR Vignana Jyothi Institute of Engineering & Technology Hyderabad B.Tech. Ii Year (Computer Science and Business Systems) Iii Semester R19Document40 pagesVNR Vignana Jyothi Institute of Engineering & Technology Hyderabad B.Tech. Ii Year (Computer Science and Business Systems) Iii Semester R19Raghu VadlamaniNo ratings yet

- DPSD Unit 3Document175 pagesDPSD Unit 3Pragna SidhireddyNo ratings yet

- Model Predictive Control Design: New Trends and Tools: Alberto BemporadDocument6 pagesModel Predictive Control Design: New Trends and Tools: Alberto BemporadNguyễn Xuân KhảiNo ratings yet

- Syllabus BCADocument243 pagesSyllabus BCAAkshay mukundNo ratings yet

- Department of Computer Science and Engineering (CSE) : United International University Course SyllabusDocument4 pagesDepartment of Computer Science and Engineering (CSE) : United International University Course Syllabusmahbub mitulNo ratings yet

- Ipe 307Document3 pagesIpe 30732anikkumarpaulNo ratings yet

- OS LAB MANUAL - R20 Reg MLRITMDocument56 pagesOS LAB MANUAL - R20 Reg MLRITMKavya KavithaNo ratings yet

- EEE 2000 Course SyllabusDocument3 pagesEEE 2000 Course SyllabusAl AminNo ratings yet

- Computer Science and EngineeringDocument14 pagesComputer Science and EngineeringAbhinav GNo ratings yet

- IF-CO VIComputerAmp NetworkSecuritySem (CO, IF) 141220181851 GBE2Document9 pagesIF-CO VIComputerAmp NetworkSecuritySem (CO, IF) 141220181851 GBE2imranNo ratings yet

- FIRST SEMESTER 2020 - 2021 17-08-2020: Course Handout (Part Ii)Document3 pagesFIRST SEMESTER 2020 - 2021 17-08-2020: Course Handout (Part Ii)Soumil AgarwalNo ratings yet

- EE 320 (CS 320) - Computer Organization and Assembly - Jahangir IkramDocument4 pagesEE 320 (CS 320) - Computer Organization and Assembly - Jahangir IkramSheikh AsherNo ratings yet

- PPS Course MaterialDocument177 pagesPPS Course MaterialSURYA VFC100% (1)

- CSE205R01 Computer Architecture - BTech CSEDocument3 pagesCSE205R01 Computer Architecture - BTech CSERoseywhite LaraNo ratings yet

- Computer Programming Lesson Plan - AmsaDocument5 pagesComputer Programming Lesson Plan - AmsaaddssdfaNo ratings yet

- Operating System Lesson Plan 2024Document4 pagesOperating System Lesson Plan 2024ambika sNo ratings yet

- K L Deemed To Be University Department of Computer Science and Engineering - KLVZA Course Handout 2021-2022, Even SemDocument56 pagesK L Deemed To Be University Department of Computer Science and Engineering - KLVZA Course Handout 2021-2022, Even SemPRASAD SLVVNo ratings yet

- CS 201 Introduction To Object Oriented ProgrammingDocument4 pagesCS 201 Introduction To Object Oriented ProgrammingSana KhattakNo ratings yet

- Course ObjectivesDocument5 pagesCourse ObjectivesSreekanth KuNo ratings yet

- Chapter 4 - Cache Memory: 4.1 Computer Memory System Overview 4.2 Cache Memory Principles 4.3 Elements of Cache DesignDocument13 pagesChapter 4 - Cache Memory: 4.1 Computer Memory System Overview 4.2 Cache Memory Principles 4.3 Elements of Cache DesignChu Quang HuyNo ratings yet

- Acer CN517-71 - Inventec Covini-Alphard Rev X01 - 6050A3087502 (DIAGRAMAS - com.BR)Document139 pagesAcer CN517-71 - Inventec Covini-Alphard Rev X01 - 6050A3087502 (DIAGRAMAS - com.BR)Fernanda Ferreira de FreitasNo ratings yet

- ASUS 1101HA Schematic Diagram. Rev 1.2Document50 pagesASUS 1101HA Schematic Diagram. Rev 1.2Utube MaNo ratings yet

- PASOLINK Network Management System For Windows: Features and BenefitsDocument12 pagesPASOLINK Network Management System For Windows: Features and Benefitsms_aletheaNo ratings yet

- MP Unit 1Document17 pagesMP Unit 1Harshit RajputNo ratings yet

- Price ListDocument2 pagesPrice ListLerie HernandezNo ratings yet

- Unit 30 - Assignment 1Document3 pagesUnit 30 - Assignment 1BSCSComputingIT100% (1)

- Rand F ReportsDocument6 pagesRand F ReportsSri HariNo ratings yet

- Acer Travelmate 660 Series: Service GuideDocument114 pagesAcer Travelmate 660 Series: Service GuidescribdermaniacNo ratings yet

- Difference Between Timers and CounterDocument5 pagesDifference Between Timers and CounterAmit ChauhanNo ratings yet

- Advanced Microcontrollers Grzegorz Budzyń Lecture 8 - ARM Based MCUs and APs PDFDocument103 pagesAdvanced Microcontrollers Grzegorz Budzyń Lecture 8 - ARM Based MCUs and APs PDFtudor11111No ratings yet

- Homework 05 (Nand2Tetris)Document1 pageHomework 05 (Nand2Tetris)Hunter HaggardNo ratings yet

- ArrayconfigDocument4 pagesArrayconfigbillNo ratings yet

- Module 2 PDFDocument76 pagesModule 2 PDFRajadorai DsNo ratings yet

- 80x85 FormatDocument17 pages80x85 Formatnorberto_1No ratings yet

- Lisp LSTDocument263 pagesLisp LSTKarol DrożakNo ratings yet

- DDDDDocument1 pageDDDDYanetNo ratings yet

- Salient Features of 8051:: M 8051 & ARMDocument1 pageSalient Features of 8051:: M 8051 & ARMnaincy kumariNo ratings yet

- MS-DOS Operating SystemDocument58 pagesMS-DOS Operating SystembradNo ratings yet

- Keypad ScanningDocument11 pagesKeypad Scanningrose8051No ratings yet

- Introduction To Parallel ComputingDocument149 pagesIntroduction To Parallel ComputingJose MiguelNo ratings yet

- Unit 5Document40 pagesUnit 5anand_duraiswamyNo ratings yet

- Power Off Reset Reason BackupDocument5 pagesPower Off Reset Reason BackupEdvin DukaNo ratings yet

- G533QS Rev2.0Document119 pagesG533QS Rev2.0jokerNo ratings yet

- 100 Top Computer FUNDAMENTAL Questions: and AnswersDocument22 pages100 Top Computer FUNDAMENTAL Questions: and AnswersJaico DictaanNo ratings yet

- Flyer RB GT4Document2 pagesFlyer RB GT4Fabricio VigolloNo ratings yet