Professional Documents

Culture Documents

ECEG-3163 Comp Arch Course Outline

Uploaded by

Ephraim0 ratings0% found this document useful (0 votes)

2 views2 pagesComputer architecture all topics

Original Title

ECEG-3163 Comp Arch Course Outline (2)

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentComputer architecture all topics

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

2 views2 pagesECEG-3163 Comp Arch Course Outline

Uploaded by

EphraimComputer architecture all topics

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

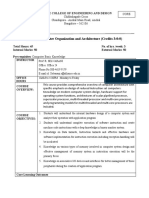

Addis Ababa University

Addis Ababa Institute Of Technology

School of Electrical and Computer Engineering

ECEG-3163: Computer Architecture and Organization: 5 (2, 3, 0)

Course Instructors: - Eyoel Getahun & Menore Tekeba

Course Assistants: - Meleake S. , Bruik T. & Dagmawi E.

Course Objectives

Understanding the architecture and organization of a computer system and its components.

To design and simulate a basic computer.

Course Outline:

Part I – Overview of Computer Systems [2 Weeks] (chapters 1 - 3 of [1])

1. Introduction

1.1 Organization and Architecture

1.2 Structure and Function

2. Computer Evolution and Performance

2.1 A Brief History of Computers

2.2 Designing for Performance

2.3 The Evolution of the Intel x86 Architecture

2.4 Performance Assessment

3. A Top-Level View of Computer Function and Interconnection

3.1 Computer Components

3.2 Computer Function

3.3 Interconnection Structures

3.4 Bus Interconnection

Part II - The Central Processing Unit [5.5 Weeks] (chapters 9 - 14 of [1])

4. Computer Arithmetic

4.1 The Arithmetic and Logic Unit (ALU)

4.2 Integer Representation

4.3 Integer Arithmetic

4.4 Floating-Point Representation

4.5 Floating-Point Arithmetic

Test I covering chapters 1 – 4 , Administered by the end 4th week

5. Instruction Sets and Addressing Modes

5.1 Machine Instruction Characteristics

5.2 Types of Operands

5.3 Types of Operations

5.4 Addressing

5.5 Instruction Formats

5.6 Assembly Language

6. Processor Structure and Organization

6.1 Processor Organization

6.2 Register Organization

6.3 The Instruction Cycle

6.4 Instruction Pipelining

7. Pipelining: Basic and Intermediate Concepts (Appendix A of [2])

7.1 Introduction

7.2 Pipeline Hazards

7.3 Pipeline Implementation

8. Reduced Instruction Set Computer

8.1 Instruction Execution Characteristics

Course Syllabus Page 1 of 2 AAiT, SECE, ECEG 3163

8.2 The Use of a Large Register File

8.3 Compiler-Based Register Optimization

8.4 Reduced Instruction Set Architecture

8.5 RISC Pipelining

8.6 The RISC versus CISC Controversy

Part III – The Control Unit [2 weeks] (chapters 15, 16 of [1])

9. Control Unit Operation

9.1 Micro-operations

9.2 Control of the Processor

9.3 Hardwired Implementation

10. Micro-programmed Control

10.1 Basic Concepts

10.2 Microinstruction Sequencing

10.3 Microinstruction Execution

Test II covering chapters 5 – 10, Administered by the end 10th week

Part IV Memory and I/O Technologies [3.5 Weeks] (chapters 4 -7 of [1])

11. Cache Memory

11.1 Computer Memory System Overview

11.2 Cache Memory Principles

11.3 Elements of Cache Design

12. Internal Memory

12.1 Semiconductor Main Memory

12.2 Error Correction

12.3 Advanced DRAM Organization

13. External Memory

13.1 Magnetic Disk

13.2 RAID

13.3 Optical Memory

13.4 Magnetic Tape

14. Input/output

14.1 External Devices

14.2 I/O Modules

14.3 Programmed I/O

14.4 Interrupt-Driven I/O

14.5 Direct Memory Access

14.6 I/O Channels and Processors

Prerequisite: Digital Logic Design

Evaluation System: Continuous Assessment

Assignments and Tests (50 %),

Final exam (50%)

Textbook:

[1] William Stallings: Prentice Hall 2010, Computer Organization and Architecture 8th Edition

References:

[2] David A Patterson: John L. Hennessy: Computer Architecture A Quantitative Approach 4th Edition

[3] M. M. Mano: Computer System Architecture

[4] Barry Wilkinson: Computer Architecture Design and Performance

Teaching & Learning Methods: Lectures supported by tutorials.

Attendance Requirements: 75%lecture attendance

Course Syllabus Page 2 of 2 AAiT, SECE, ECEG 3163

You might also like

- Computer Systems 1 - 2 PDFDocument10 pagesComputer Systems 1 - 2 PDFkadsNo ratings yet

- Embedded System (3-1-2)Document2 pagesEmbedded System (3-1-2)Anil MarsaniNo ratings yet

- Fundamentals of Operating Systems CompressDocument171 pagesFundamentals of Operating Systems CompresskowserNo ratings yet

- CC ZG502 Course HandoutDocument10 pagesCC ZG502 Course HandoutpoonamNo ratings yet

- Computer Architecture: Beg 473 EcDocument2 pagesComputer Architecture: Beg 473 EcSaroj TimsinaNo ratings yet

- Fundamentals of Computer Organization and ArchitectureFrom EverandFundamentals of Computer Organization and ArchitectureRating: 5 out of 5 stars5/5 (1)

- Embedded Control Systems Course GuideDocument5 pagesEmbedded Control Systems Course GuideAlemayehu AsmareNo ratings yet

- Microcontrollers - Architecture, Programming, Interfacing and System Design, 2nd Edition (Book)Document26 pagesMicrocontrollers - Architecture, Programming, Interfacing and System Design, 2nd Edition (Book)dinesh M.A.No ratings yet

- Department of Computer Science and Engineering Kathmandu UniversityDocument4 pagesDepartment of Computer Science and Engineering Kathmandu UniversityAcharya SuyogNo ratings yet

- Course 24. Embedded Systems (Video Course) Faculty Coordinator(s) : 1Document4 pagesCourse 24. Embedded Systems (Video Course) Faculty Coordinator(s) : 1Shaheda JamalNo ratings yet

- Operating SystemsDocument16 pagesOperating SystemsLyndon PadamaNo ratings yet

- Birla Institute of Technology & Science, Pilani: Work Integrated Learning ProgrammesDocument8 pagesBirla Institute of Technology & Science, Pilani: Work Integrated Learning ProgrammesRaja KarthikNo ratings yet

- Hawassa University Faculty of Informatics Department of Computer ScienceDocument3 pagesHawassa University Faculty of Informatics Department of Computer ScienceElijah IbsaNo ratings yet

- Birla Institute of Technology & Science, Pilani: Work Integrated Learning ProgrammesDocument8 pagesBirla Institute of Technology & Science, Pilani: Work Integrated Learning ProgrammesSunny KumarNo ratings yet

- Computer Architecture Course OverviewDocument2 pagesComputer Architecture Course OverviewBilal Ashfaq AhmedNo ratings yet

- CS 223 Comp Org and Assembly LangDocument2 pagesCS 223 Comp Org and Assembly LangHassaan NaveedNo ratings yet

- NPTEL Phase II - Electrical Engineering - Embedded SystemsDocument4 pagesNPTEL Phase II - Electrical Engineering - Embedded SystemsShalini JainNo ratings yet

- Final Project Guidline For RVUDocument4 pagesFinal Project Guidline For RVUFitsum TesfayeNo ratings yet

- Embedded Course ManualDocument5 pagesEmbedded Course ManualAlemayehu AsmareNo ratings yet

- Computer Organization and ArchitectureDocument3 pagesComputer Organization and ArchitectureAnil MarsaniNo ratings yet

- T.Y.B.sc. Computer Science 30juneDocument53 pagesT.Y.B.sc. Computer Science 30juneAshutosh MorwalNo ratings yet

- A. M. Lister (Auth.) - Fundamentals of Operating Systems-Springer-Verlag New York (1984) PDFDocument172 pagesA. M. Lister (Auth.) - Fundamentals of Operating Systems-Springer-Verlag New York (1984) PDFSelva100% (2)

- Course Plan Microprocessor and Assembly LLDocument3 pagesCourse Plan Microprocessor and Assembly LLGcross NGNo ratings yet

- Se 4Document15 pagesSe 4Nabin TimsinaNo ratings yet

- Bit SliceDocument101 pagesBit SlicebinkyfishNo ratings yet

- Mechanisms for Reliable Distributed Real-Time Operating Systems: The Alpha KernelFrom EverandMechanisms for Reliable Distributed Real-Time Operating Systems: The Alpha KernelNo ratings yet

- Modeling Embedded Systems and SoC's: Concurrency and Time in Models of ComputationFrom EverandModeling Embedded Systems and SoC's: Concurrency and Time in Models of ComputationNo ratings yet

- Database Management Systems: Course ObjectivesDocument18 pagesDatabase Management Systems: Course ObjectivesZems ShakyaNo ratings yet

- Computer-Architecture 1 PDFDocument0 pagesComputer-Architecture 1 PDFwww.bhawesh.com.npNo ratings yet

- Course Outline of CSE 309 - Section A PDFDocument5 pagesCourse Outline of CSE 309 - Section A PDFSafialIslamAyonNo ratings yet

- Chapter One: Introduction of Whole Project Process: Computing and Informatics College Final Project Template - 2017Document3 pagesChapter One: Introduction of Whole Project Process: Computing and Informatics College Final Project Template - 2017bk channelNo ratings yet

- Final Report Layout of Senior ProjectDocument3 pagesFinal Report Layout of Senior ProjectDesalegn AbebawNo ratings yet

- DEE Curriculum Final 2014Document17 pagesDEE Curriculum Final 2014Dharma Raj JaisiNo ratings yet

- Embedded Systems and Real-Time SystemsDocument9 pagesEmbedded Systems and Real-Time SystemsMOUNI VARMANo ratings yet

- Course Plan Microprocessor and Assembly LDocument3 pagesCourse Plan Microprocessor and Assembly LGcross NGNo ratings yet

- course outline -Computer Organization and Architecture1 dt-2024-02-24 15-49-19Document5 pagescourse outline -Computer Organization and Architecture1 dt-2024-02-24 15-49-19Caleb fikaduNo ratings yet

- IT6203 SyllabusDocument7 pagesIT6203 SyllabusDeepak VermaNo ratings yet

- BOEYM2529A - 21z 2021 - 1 - CPA Textbook Upper Sec - 29 Sep 2022 (2) 5Document226 pagesBOEYM2529A - 21z 2021 - 1 - CPA Textbook Upper Sec - 29 Sep 2022 (2) 5chungkaiqingchloeNo ratings yet

- Domain Architectures: Models and Architectures for UML ApplicationsFrom EverandDomain Architectures: Models and Architectures for UML ApplicationsNo ratings yet

- 10) WASE 2018 - Comp - Org - Archi - Flipped - HODocument14 pages10) WASE 2018 - Comp - Org - Archi - Flipped - HOShreyansh AnshumanNo ratings yet

- Syllabus: Course On Computer Concepts (CCC)Document6 pagesSyllabus: Course On Computer Concepts (CCC)Abdul QadirNo ratings yet

- Project Report EeDocument47 pagesProject Report Eeadarshtiwari123321No ratings yet

- COA Full Syllabus-CSEDocument3 pagesCOA Full Syllabus-CSEAMARTYA KUMARNo ratings yet

- Computer Organization Course Outline To Be Printed-1Document2 pagesComputer Organization Course Outline To Be Printed-1habtamu fentewNo ratings yet

- Applied Operating SystemDocument3 pagesApplied Operating SystemAnil MarsaniNo ratings yet

- Introduction To Computer ConceptsDocument5 pagesIntroduction To Computer ConceptsVikram Rao100% (1)

- Syllabus CEA201 Spring 2022Document15 pagesSyllabus CEA201 Spring 2022Dang Hoang Viet (K17 HCM)No ratings yet

- Course Outline Computer Netwoking IDocument3 pagesCourse Outline Computer Netwoking IGeez DesignNo ratings yet

- OS Course OutlineDocument5 pagesOS Course OutlineAyano BoresaNo ratings yet

- Fallsem2023-24 Bcse303l TH VL2023240100692 Cat-1-Qp - KeyDocument10 pagesFallsem2023-24 Bcse303l TH VL2023240100692 Cat-1-Qp - KeyBetha Sai Dheeraj 21BCE3046No ratings yet

- Course OutlineDocument2 pagesCourse OutlineAbdulaziz AbajebelNo ratings yet

- Digital Logic and Object Oriented ProgrammingDocument13 pagesDigital Logic and Object Oriented ProgrammingRam Krishna ThapaNo ratings yet

- Final Report Documentation Guidelines 9-10Document2 pagesFinal Report Documentation Guidelines 9-10abhi241No ratings yet

- Computer Science Ocr - j277Document18 pagesComputer Science Ocr - j277naseerNo ratings yet

- Syllabus For BIT 4 Smester: Computer OrganizationDocument2 pagesSyllabus For BIT 4 Smester: Computer OrganizationBijay MishraNo ratings yet

- Intro - Comp ArchDocument17 pagesIntro - Comp ArchEphraimNo ratings yet

- Comparch Top Level ViewDocument74 pagesComparch Top Level ViewEphraimNo ratings yet

- Chache Memory, Internal Memory and External MemoryDocument113 pagesChache Memory, Internal Memory and External MemoryEphraimNo ratings yet

- 02 - Computer Evolution and PerformanceDocument20 pages02 - Computer Evolution and PerformanceAmir EyniNo ratings yet

- Embedded System Components PDFDocument208 pagesEmbedded System Components PDFHoang Manh100% (1)

- Types of Operating System SchedulersDocument26 pagesTypes of Operating System SchedulersVa SuNo ratings yet

- 2.2 Pipelining: AsynchronousDocument24 pages2.2 Pipelining: Asynchronouseshankapur25% (4)

- CS 532Document4 pagesCS 532Humaira ChNo ratings yet

- CSE Scheme and Syllabus for III, IV SemesterDocument164 pagesCSE Scheme and Syllabus for III, IV SemesterÇháråñ ÇhèrryNo ratings yet

- MicroprocessorDocument2,540 pagesMicroprocessorManas PandeyNo ratings yet

- Risc CiscDocument1 pageRisc CiscabhiNo ratings yet

- 11 Wheelen Strategic Issues in Managing Technology and InnovationDocument24 pages11 Wheelen Strategic Issues in Managing Technology and InnovationVerVe Lim100% (2)

- Chapter 1 - Understanding The Concept of Microprocessor and MicrocomputerDocument5 pagesChapter 1 - Understanding The Concept of Microprocessor and MicrocomputerFaizur FarihaNo ratings yet

- System Architecture: Lab Notes For Week 1: The MIPS CPU, Assembly Programming 1 Introduction To System ArchitectureDocument7 pagesSystem Architecture: Lab Notes For Week 1: The MIPS CPU, Assembly Programming 1 Introduction To System ArchitectureNabil AlzeqriNo ratings yet

- The SPARC Architecture ManualDocument393 pagesThe SPARC Architecture ManualRaja MustafaNo ratings yet

- Arm Processor ArchitectureDocument84 pagesArm Processor Architecturebhargava PrasadNo ratings yet

- Lecture - Notes On CSC 200Document58 pagesLecture - Notes On CSC 200Sanctus EmekumehNo ratings yet

- CS 404 - COA Course PlanDocument8 pagesCS 404 - COA Course PlanAishwarya RajeshNo ratings yet

- Arm Multiple ChoiceDocument4 pagesArm Multiple ChoiceStalin Sbr33% (9)

- Basic Structure of ComputersDocument39 pagesBasic Structure of Computersapi-3723664No ratings yet

- Microprocessor - Overview: Block Diagram of A ComputerDocument5 pagesMicroprocessor - Overview: Block Diagram of A Computersurya pratapNo ratings yet

- ARM7 Processor ArchitectureDocument33 pagesARM7 Processor ArchitectureRamanan MNo ratings yet

- CSE 305 Computer Architecture: InstructionsDocument103 pagesCSE 305 Computer Architecture: InstructionsRayan IslamNo ratings yet

- From Mainframes To MicroprocessorsDocument8 pagesFrom Mainframes To MicroprocessorsAsif MemonNo ratings yet

- MB91F467DB - Microcontrolador 32 BitsDocument140 pagesMB91F467DB - Microcontrolador 32 BitsTiago LeonhardtNo ratings yet

- Finger Print Based Electronic Voting MachineDocument93 pagesFinger Print Based Electronic Voting MachineThejaswani Rajamani85% (13)

- Lecture 5: Memory Addressing: KT6144 / KT6213Document57 pagesLecture 5: Memory Addressing: KT6144 / KT6213Saiful RizamNo ratings yet

- Unit 4 MPMCDocument22 pagesUnit 4 MPMCSekhar ReddyNo ratings yet

- Unix Old BookDocument319 pagesUnix Old BookChristopher LambertNo ratings yet

- KRISHNENDU GUIN - Assignment 2Document20 pagesKRISHNENDU GUIN - Assignment 2Krishnendu GuinNo ratings yet

- PA RISC All InfoDocument350 pagesPA RISC All InfoullassimonNo ratings yet

- CMP e 220 MergedDocument657 pagesCMP e 220 Mergedsaksham mahajanNo ratings yet

- Design of A Microsoft Version of MIPS Microprocessor SimulatorDocument32 pagesDesign of A Microsoft Version of MIPS Microprocessor SimulatorMohammed El-KhoudaryNo ratings yet

- Unit-1 PicDocument40 pagesUnit-1 Picsarath100% (1)