Professional Documents

Culture Documents

8259 Programmable Interrupt Controller

Uploaded by

artbyvishaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8259 Programmable Interrupt Controller

Uploaded by

artbyvishaCopyright:

Available Formats

8085 M ICROPROCESSOR BHARAT ACHARYA EDUCATION

Cell: 98204 08217

BharatSir@hotmail.com

8259

PROGRAMMABLE INTERRUPT CONTROLLER

www.BharatAcharyaEducation.com Page No: 67

8085 M ICROPROCESSOR BHARAT ACHARYA EDUCATION

Cell: 98204 08217

BharatSir@hotmail.com

Salient Features of 8259 PIC

¶ 8259 is a Programmable Interrupt Controller (PIC) designed to work with 8085, 8086 etc.

¶ A single 8259 can handle 8 interrupts, while a cascaded configuration of 8 slave 8259's and

1 master 8259 can handle 64 interrupts.

¶ 8259 can handle edge as well as level triggered interrupts.

¶ 8259 has a flexible priority structure.

¶ In 8259 interrupts can be masked individually.

¶ The Vector address of the interrupts is programmable.

¶ Status of interrupts (pending, In-service, masked) can be easily read by the µP.

Architecture of 8259

www.BharatAcharyaEducation.com Page No: 68

8085 M ICROPROCESSOR BHARAT ACHARYA EDUCATION

Cell: 98204 08217

BharatSir@hotmail.com

The architecture of 8259 can be divided into the following parts:

1) Interrupt Request Register (IRR)

− 8259 has 8 interrupt input lines IR7 … IR0.

− The IRR is an 8-bit register having one bit for each of the interrupt lines.

− When an interrupt request occurs on any of these lines, the corresponding bit is set in the

Interrupt Request Register (IRR).

2) In-Service Register (InSR)

− It is an 8-bit register, which stores the level of the Interrupt Request, which is currently

being serviced.

3) Interrupt Mask Register (IMR)

− It is an 8-bit register, which stores the masking pattern for the interrupts of 8259.

It stores one bit per interrupt level.

4) Priority Resolver

− It examines the IRR, InSR, and IMR and determines which interrupt is of highest priority

and should be sent to the µP.

5) Control Logic

− It has INT output signal connected to the INTR of the µP, to send the Interrupt to the µP.

− It also has the INTA input signal connected to the INTA of the µP, to receive the interrupt

acknowledge.

− It is also used to control the remaining blocks.

6) Data Bus Buffer

− It is a bi-directional buffer used to interface the internal data bus of 8259 with the external

(system) data bus.

7) Read/Write Logic

− It is used to accept the RD, WR, A0 and CS signal.

− It also holds the Initialization Command Words (ICW's) and the Operational Command Words

(OCW's).

8) Cascade Buffer / Comparator

− It is used in cascaded mode of operation.

− It has two components:

i. CAS2, CAS1, CAS0 lines:

¶ These lines are output for the master, input for the slave.

¶ The Master sends the address of the slave on these lines (hence output).

¶ The Salves read the address on these lines (hence input).

¶ As there are 8 interrupt levels for the Master, there are 3 CAS lines (∵ 23 = 8).

ii. SP/EN (Slave Program/Master Enable):

¶ In Buffered Mode, it functions as the EN line and is used to enable the buffer.

¶ In Non buffered mode, it functions as the SP output line.

¶ For Master 8259 SP should be high, and for the Slave SP should be low.

www.BharatAcharyaEducation.com Page No: 69

You might also like

- 8259 Programmable ControllerDocument44 pages8259 Programmable ControllerShilpa ShettyNo ratings yet

- Doosan VMC Maintenance DNM 500Document123 pagesDoosan VMC Maintenance DNM 500sunhuynh100% (2)

- Computer Organization and Design: The Hardware / Software InterfaceFrom EverandComputer Organization and Design: The Hardware / Software InterfaceRating: 4 out of 5 stars4/5 (12)

- Process Flow ChartDocument4 pagesProcess Flow Chartdaniel_sasikumarNo ratings yet

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureFrom EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureRating: 1 out of 5 stars1/5 (1)

- Otis Door Drive User ManualDocument34 pagesOtis Door Drive User ManualRoyal Akash100% (8)

- 330D L Excavator-Before OperationDocument8 pages330D L Excavator-Before Operationvkannan07666No ratings yet

- Hc3500t Multimeter ManualDocument3 pagesHc3500t Multimeter Manualjmfcoto33% (3)

- Motortronics 2013 Product Selection Guide - SoftstarterDocument121 pagesMotortronics 2013 Product Selection Guide - SoftstarterJoeDabidNo ratings yet

- 8259A Programmable Interrupt Controller: Segment 8BDocument31 pages8259A Programmable Interrupt Controller: Segment 8Bgebretensaymamu11No ratings yet

- EEE 311 Online Class 3Document5 pagesEEE 311 Online Class 3KhairulNo ratings yet

- ADC Interfacing With 8085 MicroprocessorDocument5 pagesADC Interfacing With 8085 MicroprocessorraghulNo ratings yet

- 8259 Microprocessor: Some Features of This MicroprocessorDocument6 pages8259 Microprocessor: Some Features of This Microprocessorabu sayedNo ratings yet

- Lecture 2Document7 pagesLecture 2tejashraj93No ratings yet

- Lecture-51 INTEL 8259A Programmable Interrupt ControllerDocument7 pagesLecture-51 INTEL 8259A Programmable Interrupt ControllerSahil KKNo ratings yet

- INTEL 8259A Programmable Interrupt ControllerDocument19 pagesINTEL 8259A Programmable Interrupt ControllerHimanshi SinghNo ratings yet

- Programmable Interrupt Controller (SUB: Microprocessor and Interfaces)Document7 pagesProgrammable Interrupt Controller (SUB: Microprocessor and Interfaces)mohit mishraNo ratings yet

- Ee6502 MM QB2Document81 pagesEe6502 MM QB2senthilkumarNo ratings yet

- Programmable Interrupt Controller: Submitted ToDocument15 pagesProgrammable Interrupt Controller: Submitted ToCSE7 NDUBNo ratings yet

- Programmable Interrupt Controller (PIC) - 8259Document23 pagesProgrammable Interrupt Controller (PIC) - 8259Arya ChandranNo ratings yet

- VBMB - 007Document42 pagesVBMB - 007gg.ganapathyNo ratings yet

- Lecture - 9 & 10pin Diagram 8085Document24 pagesLecture - 9 & 10pin Diagram 8085no fake NewsNo ratings yet

- Cat 3 ReportDocument7 pagesCat 3 ReportSATYAM ANAND 20SCSE1010341No ratings yet

- An Interrupt Is An Event Which Informs The CPU That Its Service (Action) Is Needed. - Sources of InterruptsDocument20 pagesAn Interrupt Is An Event Which Informs The CPU That Its Service (Action) Is Needed. - Sources of InterruptsMurali KrishnaNo ratings yet

- 8259A Pic-Block DiagramDocument16 pages8259A Pic-Block DiagramKarthikeyaNo ratings yet

- Where & How 8259 PIC Can Be Used To Handle Interrupts. The 8259A Programmable Interrupt ControllerDocument4 pagesWhere & How 8259 PIC Can Be Used To Handle Interrupts. The 8259A Programmable Interrupt ControllerKuberjung ThapaNo ratings yet

- 8259 A FinalDocument52 pages8259 A FinalAnitha Joseph100% (1)

- 8259a Programmable Interrupt Controller 2Document42 pages8259a Programmable Interrupt Controller 2annushaNo ratings yet

- EC2304 Microprocessors and Its Applications: Unit I 8085 CPU 9Document39 pagesEC2304 Microprocessors and Its Applications: Unit I 8085 CPU 9Irfana IrfanaNo ratings yet

- 8259Document57 pages8259Vats Alok100% (1)

- 8259a Programmable Interrupt ControllerDocument42 pages8259a Programmable Interrupt ControllerzarandijaNo ratings yet

- 1-Ee8551-Microprocessors and MicrocontrollersDocument2 pages1-Ee8551-Microprocessors and MicrocontrollersKeerthana SahadevanNo ratings yet

- CS2252 SQDocument26 pagesCS2252 SQS. GobikaNo ratings yet

- 4c The 8259 Programmable Interrupt ControllerDocument3 pages4c The 8259 Programmable Interrupt ControllerEllie AwiNo ratings yet

- WINSEM2021-22 CSE2006 ETH VL2021220503993 Reference Material I 10-02-2022 8259Document33 pagesWINSEM2021-22 CSE2006 ETH VL2021220503993 Reference Material I 10-02-2022 8259Saksham GargNo ratings yet

- Interfacing Memory Chips With 8085Document10 pagesInterfacing Memory Chips With 8085Honsyben BriansNo ratings yet

- Instruction Objectives of Each ChapterDocument9 pagesInstruction Objectives of Each ChapterahmedmalekNo ratings yet

- EE2354 Question Bank BESTDocument18 pagesEE2354 Question Bank BESTGokul ChandrasekaranNo ratings yet

- 8259 Programmable Interrupt Controller (PIC) : by Gayathri.M Asst. Professor Dept. of CSE SRM UniversityDocument57 pages8259 Programmable Interrupt Controller (PIC) : by Gayathri.M Asst. Professor Dept. of CSE SRM UniversitySugunaNo ratings yet

- 8259a Programmable Interrupt Controller 2Document42 pages8259a Programmable Interrupt Controller 2Tư Tưởng Tồi TànNo ratings yet

- 8259updatedd 141126060514 Conversion Gate02Document28 pages8259updatedd 141126060514 Conversion Gate02zelalem2022No ratings yet

- EC305 Microprocessor & MicrocontrollerDocument2 pagesEC305 Microprocessor & MicrocontrollerplbonifusNo ratings yet

- CH 13 PIC8259Document14 pagesCH 13 PIC8259gokulchandru0% (1)

- Microprocessor and MicrocontrollerDocument35 pagesMicroprocessor and MicrocontrollerPRABHVaB100% (1)

- INTEL 8259A Programmable Interrupt ControllerDocument15 pagesINTEL 8259A Programmable Interrupt ControllerSri ShandilyaNo ratings yet

- Module III - Stack and InterruptsDocument15 pagesModule III - Stack and InterruptsSNEHA MARIYA TOMNo ratings yet

- MPMC Lab ManualDocument21 pagesMPMC Lab ManualAmar KoliNo ratings yet

- MP22 8259Document8 pagesMP22 8259GAMING BUDDYNo ratings yet

- 8259 Programmable Interrupt ControllerDocument15 pages8259 Programmable Interrupt ControllerramkumarrajaNo ratings yet

- The 8085 Microprocessor ArchitectureDocument33 pagesThe 8085 Microprocessor Architecturemodismm330% (1)

- MPMCDocument20 pagesMPMCAnonymous 3XeTp7drNo ratings yet

- 8259A Programmable Interrupt ControllerDocument18 pages8259A Programmable Interrupt ControllerBasheer V.PNo ratings yet

- FALLSEM2022-23 CSE2006 ETH VL2022230103866 Reference Material I 08-09-2022 8259Document42 pagesFALLSEM2022-23 CSE2006 ETH VL2022230103866 Reference Material I 08-09-2022 8259Gaurav Kumar SinghNo ratings yet

- 8259 ADocument16 pages8259 Aapi-26113146100% (1)

- Microprocessor and Interfacing: Authors:Ramesh.S.Gaonkar Badri Ram Douglas.V.Hall Liu and GibsonDocument52 pagesMicroprocessor and Interfacing: Authors:Ramesh.S.Gaonkar Badri Ram Douglas.V.Hall Liu and Gibsonavireddy1No ratings yet

- 8259 PIC: Intel's Prog. Interrupt ControllerDocument22 pages8259 PIC: Intel's Prog. Interrupt ControllerAsawari DudwadkarNo ratings yet

- 3 CS305 Microprocessors and Microcontrollers Slot CDocument2 pages3 CS305 Microprocessors and Microcontrollers Slot CBinesh RBNo ratings yet

- 80186/80188 High-Integration 16-Bit Microprocessors: Figure 1. Block DiagramDocument33 pages80186/80188 High-Integration 16-Bit Microprocessors: Figure 1. Block DiagramAnasNo ratings yet

- Svcet: Sri Vidya College of Engineering & Technology Course Material (Question Bank)Document4 pagesSvcet: Sri Vidya College of Engineering & Technology Course Material (Question Bank)Balaprakash VadivelNo ratings yet

- EE6502 DecDocument90 pagesEE6502 Decsonu sabooNo ratings yet

- 8259 Pic RNMDocument43 pages8259 Pic RNMRajNo ratings yet

- 8086 CourseoutlineDocument3 pages8086 CourseoutlineBiruk DawitNo ratings yet

- EC305 Microprocessors and MicrocontrollersS5-EC-SyllabusDocument3 pagesEC305 Microprocessors and MicrocontrollersS5-EC-SyllabusshafinshamsudheenNo ratings yet

- EC305 Microprocessors and MicrocontrollersS5-EC-Syllabus PDFDocument3 pagesEC305 Microprocessors and MicrocontrollersS5-EC-Syllabus PDFHKNo ratings yet

- Gear Hobbing Unit enDocument8 pagesGear Hobbing Unit enAfriza NurdiansyahNo ratings yet

- Very Impb Prog PDFDocument284 pagesVery Impb Prog PDFVishesh ShrivastavaNo ratings yet

- Emotron Fdu2-0 Instruction Manual Incl Addendum4!21!01-4428-01 r2 enDocument198 pagesEmotron Fdu2-0 Instruction Manual Incl Addendum4!21!01-4428-01 r2 enlin2m3No ratings yet

- Pressao 68rfeDocument1 pagePressao 68rfeautomaticosbrasilNo ratings yet

- Miter Shooting BoardDocument1 pageMiter Shooting BoardJaime MontielNo ratings yet

- Easa Biweekly 20-2021Document2 pagesEasa Biweekly 20-2021ChristianNo ratings yet

- Contactors RelaysDocument22 pagesContactors Relayspradnya sadigaleNo ratings yet

- Catalogo RacoresDocument36 pagesCatalogo Racoresalix beltranNo ratings yet

- DIO-1616H-PE: Opto-Isolated Digital I/O For PCI Express 16 CH TypeDocument2 pagesDIO-1616H-PE: Opto-Isolated Digital I/O For PCI Express 16 CH TypeVictor HemzNo ratings yet

- CV - Taruna Mandiri ElektrindoDocument2 pagesCV - Taruna Mandiri ElektrindoJD JayNo ratings yet

- Jak418172 (Air To Jak)Document3 pagesJak418172 (Air To Jak)FaisalhafidzNo ratings yet

- Boiler Coal FeederDocument11 pagesBoiler Coal FeederIndra PratamaNo ratings yet

- Rechert 3Document3 pagesRechert 3WillNo ratings yet

- LFE Desicant Dryer ManualDocument12 pagesLFE Desicant Dryer ManualNaveen KumarNo ratings yet

- Design A Inverter With Nmos Enhancement LoadDocument8 pagesDesign A Inverter With Nmos Enhancement LoadfuchsialifeNo ratings yet

- Service Manual Samsung SGH T959v PDFDocument50 pagesService Manual Samsung SGH T959v PDFWalterNo ratings yet

- SILOS COMPONENTS MORE Kunststoffindustrie ENDocument15 pagesSILOS COMPONENTS MORE Kunststoffindustrie ENАлександр МихайловичNo ratings yet

- LUCY30503 Aegis Brochure March WebReadyDocument28 pagesLUCY30503 Aegis Brochure March WebReadyKhalid AwanNo ratings yet

- S400-User Manual EN - Set-1340243890Document15 pagesS400-User Manual EN - Set-1340243890noriel llanetaNo ratings yet

- Amendment in Bill of Quantities (Boq) : Paithan Mega Food Park Pvt. Ltd. at Paithan (MH)Document12 pagesAmendment in Bill of Quantities (Boq) : Paithan Mega Food Park Pvt. Ltd. at Paithan (MH)Karthick MahadevanNo ratings yet

- Parking Aid System: General InformationDocument20 pagesParking Aid System: General InformationPrvoslav DjordjevicNo ratings yet

- ZF 3-6-191 - 211 - e Repair ManualDocument6 pagesZF 3-6-191 - 211 - e Repair ManualarthurNo ratings yet

- 2001 Hermetic Check Operating InstructionsDocument6 pages2001 Hermetic Check Operating InstructionsAndres CarmonaNo ratings yet

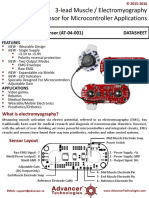

- At 04 001Document8 pagesAt 04 001parthibanNo ratings yet