Professional Documents

Culture Documents

Lab D3 CombinationalLogicCircuit Design

Uploaded by

dhanabadee.kOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab D3 CombinationalLogicCircuit Design

Uploaded by

dhanabadee.kCopyright:

Available Formats

01205301 Digital Circuits and Microcontrollers

Unit work

Name Ebo warwern ID 6410589993 Sec 1 . 10 pts)

Problem

Unit D3 : Combinational Logic Circuit Design (10 pts)

Instruction

Design and implement a combinational logic circuit to detect any three assigned numbers of 3-bit binary inputs

(N2, N1, and N0). If one of the assigned numbers is detected, the output F is HIGH. Otherwise, the output F is

LOW. The designed circuit must be in the form of minimal product and consist only of inverters, 2-input AND, and

2-input OR. Show your design steps in detail including truth table, canonical product, K-map, and minimal

product. Attach your designed circuit in Fig. 1. Use the logic analyzer to verify the function of your circuit. Record

the timing diagram from the logic analyzer in Fig. 2 and explain the timing diagram.

The assigned binary numbers (N2 N1 N0) are 001, 010, and 011.

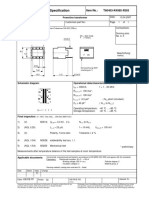

Fig. 1. Your designed circuit

Fig. 2. Recorded timing diagram from the logic analyzer

1

X

-

xY

00 01 11 10

NOW Ny Ne No F 2

6

000

2

O 00 O O 8 98

z(11 7

3

10 01 1 858

2

0191

-

3 Y

no

1

1

5 O

71 1 1 ⑧ minimal product

F Neo(N+No'

=

canonical product

4N,Ne,No(04,5,6,73

F:

=(Na+ N,+No) (Ne' + N, +NoJe /Ng'+N+NoY. IN+NNo

· ·

INg'tNe'tNO'S

01205301 Digital Circuits and Microcontrollers

Problem

Design and implement a combinational logic circuit to detect any three assigned numbers of 3-bit binary inputs

(N2, N1, and N0). If one of the assigned numbers is detected, the output F is LOW. Otherwise, the output F is

HIGH. The designed circuit must be in the form of minimal sum, and consist only of inverters, 2-input AND, and

2-input OR. Show your design steps in detail including truth table, canonical sum, K-map, and minimal sum.

Attach your designed circuit in Fig. 3. Use the logic analyzer to verify the function of your circuit. Record the

timing diagram from the logic analyzer in Fig. 4 and explain the timing diagram.

The assigned binary numbers (N2 N1 N0) are 001, 010, and 011.

Fig. 3. Your designed circuit

Fig. 4. Recorded timing diagram from the logic analyzer

2

X

-

+Y

00 01 11 10

NOW Ny N. No F 2

001 -1

2

O 000

-1

1

z(11 7

3

10 01 O 151

2

ii

-

8

3 Y

O

1

71111

Minimal sum

F: NetIN-Nos

Canonical sum

F EN, Ne,No(0,4,5,6,7)

=

:Na-N-Not(NgN!No'l+(N-N.Nolt(Nz.NNc'+(N,'N,No)

You might also like

- Layer 3 Managed 8 10G Port Switch Controller: RTL9303-CGDocument55 pagesLayer 3 Managed 8 10G Port Switch Controller: RTL9303-CG박윤지100% (1)

- Allen Holberg SolutionsDocument509 pagesAllen Holberg SolutionsLatha Venkatesh100% (1)

- Summary Studying Public Policy Michael Howlett CompleteDocument28 pagesSummary Studying Public Policy Michael Howlett CompletefadwaNo ratings yet

- Rotational System Transfer Function - Control SystemsDocument55 pagesRotational System Transfer Function - Control SystemsHaris Abbas QureshiNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Sistem Digital ADocument28 pagesSistem Digital AmengkaanNo ratings yet

- Desain Rangkain KombinasionalDocument28 pagesDesain Rangkain KombinasionalIntanSarahitaNNo ratings yet

- Lecture 2-Chapter - 1 - Digital - Systems - and - Binary - NumbersDocument14 pagesLecture 2-Chapter - 1 - Digital - Systems - and - Binary - Numbersmuhammad khubabNo ratings yet

- Lab D2 CombinationalLogicCircuitDocument10 pagesLab D2 CombinationalLogicCircuitdhanabadee.kNo ratings yet

- Example:1: A.Circular Shift: All AllDocument28 pagesExample:1: A.Circular Shift: All AllJarin TasnimNo ratings yet

- Multispan Utc 421 Digital TimerDocument4 pagesMultispan Utc 421 Digital TimerNur Awwaluddin ZNo ratings yet

- Par - 2 In-Term Exam - Course 2019/20-Q1: Memory LineDocument9 pagesPar - 2 In-Term Exam - Course 2019/20-Q1: Memory LineJuanNo ratings yet

- Security in Computing - Lecture 05 - Week 05Document20 pagesSecurity in Computing - Lecture 05 - Week 05Shahnawaz SiddiqueNo ratings yet

- Security in Computing - Lecture 05 - Week 05Document20 pagesSecurity in Computing - Lecture 05 - Week 05Shahnawaz SiddiqueNo ratings yet

- Signed Binary AdditionDocument57 pagesSigned Binary AdditionMuthukumar ManickamNo ratings yet

- Function Approximation Case Study: Smart SensorDocument10 pagesFunction Approximation Case Study: Smart SensorAlee LópezNo ratings yet

- Digital Logic For Computers (ACOE161) : Experiment #8 Flip-Flops - Pre-Lab ReportDocument8 pagesDigital Logic For Computers (ACOE161) : Experiment #8 Flip-Flops - Pre-Lab ReportOrangzaib RaoNo ratings yet

- Aiwa TV 1402 Manual de Usuario 9 10Document2 pagesAiwa TV 1402 Manual de Usuario 9 10Mr. Gonza M.No ratings yet

- Ryerson University Department of Electrical and Computer Engineering COE 328 - Digital SystemsDocument4 pagesRyerson University Department of Electrical and Computer Engineering COE 328 - Digital Systemsrokib2048No ratings yet

- Signals and System: Lab Sheet - 4Document5 pagesSignals and System: Lab Sheet - 4Shravan Kumar LuitelNo ratings yet

- Sai Madhan. K: Mca - Semester 1 REGISTER NO: 190951144Document31 pagesSai Madhan. K: Mca - Semester 1 REGISTER NO: 190951144MadhanNo ratings yet

- Experiment - 8 Date: 04/10/2021 AIM: To Design and Implement Relaxation Oscillator Using Op-Amp. TheoryDocument4 pagesExperiment - 8 Date: 04/10/2021 AIM: To Design and Implement Relaxation Oscillator Using Op-Amp. TheoryTimir PatelNo ratings yet

- 2E6 - Tutorial 2: Weeks 4,5 Michaelmas Term 2003Document4 pages2E6 - Tutorial 2: Weeks 4,5 Michaelmas Term 2003thareendaNo ratings yet

- Review Exam 1: EE 308 Spring 2011Document21 pagesReview Exam 1: EE 308 Spring 2011Abdullah Al MukitNo ratings yet

- EENG211-INFE211 Final-SolutionsDocument10 pagesEENG211-INFE211 Final-SolutionsEndalkNo ratings yet

- Powerline Transformer 4085-X003 - deDocument1 pagePowerline Transformer 4085-X003 - deejlebe mekaniNo ratings yet

- HEF4555B: 1. General DescriptionDocument10 pagesHEF4555B: 1. General DescriptionLechero De Corazon MHNo ratings yet

- NX3L1T5157: 1. General DescriptionDocument21 pagesNX3L1T5157: 1. General DescriptionMarco Antonio Bolívar SuárezNo ratings yet

- Elex - EXPERIMENT 2Document8 pagesElex - EXPERIMENT 2JayNo ratings yet

- Chapter 2Document64 pagesChapter 2Muhammad NazmiNo ratings yet

- Bit Byte: Memory UnitsDocument22 pagesBit Byte: Memory UnitsANKIT KUMARNo ratings yet

- PDF Ascii Code The Extended Ascii Table CompressDocument6 pagesPDF Ascii Code The Extended Ascii Table Compresswenny NyNo ratings yet

- Solutions Question 1 (20 Points) : JKQ Q QDocument6 pagesSolutions Question 1 (20 Points) : JKQ Q QAmin DhouibNo ratings yet

- XYZ F XYZ F: ENGI 3861 - Digital LogicDocument7 pagesXYZ F XYZ F: ENGI 3861 - Digital Logicvigneshwar RNo ratings yet

- Node To NodeDocument3 pagesNode To NodeVincinius AxelNo ratings yet

- Degrees of Freedom in Distillation: Figure 2-1: Single One-Feed Two Product Column With Reboiler and CondenserDocument11 pagesDegrees of Freedom in Distillation: Figure 2-1: Single One-Feed Two Product Column With Reboiler and CondenserMartin BishwasNo ratings yet

- 17 Timing PDFDocument4 pages17 Timing PDFControl System Engineering LabNo ratings yet

- L02 LogicDocument45 pagesL02 LogicthienvugcsNo ratings yet

- Mina Nakulkarn 1102Document21 pagesMina Nakulkarn 1102api-514272917No ratings yet

- MidtermDocument11 pagesMidtermYash RatnakarNo ratings yet

- Exercise 1 Power SupplyDocument2 pagesExercise 1 Power SupplyCikgu BibNo ratings yet

- BaudotDocument2 pagesBaudotBrian Paulo ReyesNo ratings yet

- IM316 - Sheet 2 - Linear Profiles - Model Answer Q1Document2 pagesIM316 - Sheet 2 - Linear Profiles - Model Answer Q1يحيى الأثلهNo ratings yet

- Rohini 39690128392Document4 pagesRohini 39690128392MelchikmNo ratings yet

- Multisim WorkbookDocument107 pagesMultisim WorkbookAris Eahman100% (1)

- LAN Components: TLA-3E Series Pulse Transformers DIPDocument1 pageLAN Components: TLA-3E Series Pulse Transformers DIPCharbel TadrosNo ratings yet

- Taguig City University: Computer Science DepartmentDocument3 pagesTaguig City University: Computer Science DepartmentRalph Daniel MagallanesNo ratings yet

- Answers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesFrom EverandAnswers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesRating: 1.5 out of 5 stars1.5/5 (2)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Digital and Microprocessor Techniques V11From EverandDigital and Microprocessor Techniques V11Rating: 4.5 out of 5 stars4.5/5 (2)

- Learn Digital and Microprocessor Techniques on Your SmartphoneFrom EverandLearn Digital and Microprocessor Techniques on Your SmartphoneNo ratings yet

- Ababio v. R (1972) 1 GLR 347Document4 pagesAbabio v. R (1972) 1 GLR 347Esinam Adukpo100% (2)

- Demand Letter Template 39Document3 pagesDemand Letter Template 39AIG1 LOGISTICNo ratings yet

- Octopus 900 Instructions For UseDocument18 pagesOctopus 900 Instructions For UseAli FadhilNo ratings yet

- Beijing-Michael PageDocument71 pagesBeijing-Michael Pagejohndavsg8022No ratings yet

- Fpga De0-Nano User Manual PDFDocument155 pagesFpga De0-Nano User Manual PDFCesarNo ratings yet

- Global Grants Community Assessment FormDocument3 pagesGlobal Grants Community Assessment Formlalitya xavieraNo ratings yet

- Tech Bee JavaDocument57 pagesTech Bee JavaA KarthikNo ratings yet

- TFTV3225 Service Manual 102010 Coby 26-32Document21 pagesTFTV3225 Service Manual 102010 Coby 26-32bigbrother4275% (4)

- Fouzia AnjumDocument3 pagesFouzia AnjumAbdul SyedNo ratings yet

- High-Definition Multimedia Interface SpecificationDocument51 pagesHigh-Definition Multimedia Interface SpecificationwadrNo ratings yet

- NammalvarDocument22 pagesNammalvarPranesh Brisingr100% (1)

- Lab ManualDocument15 pagesLab ManualsamyukthabaswaNo ratings yet

- AutoCAD Civil 3D Performance Optimization 2Document5 pagesAutoCAD Civil 3D Performance Optimization 2Renukadevi RptNo ratings yet

- Cyber Cafe Audience Profiling Nielsen 2009Document17 pagesCyber Cafe Audience Profiling Nielsen 2009mahi46452No ratings yet

- VOID BEQUESTS - AssignmentDocument49 pagesVOID BEQUESTS - AssignmentAkshay GaykarNo ratings yet

- Metabolic SyndromeDocument4 pagesMetabolic SyndromeNurayunie Abd HalimNo ratings yet

- Shell Omala s2 GX 320 TdsDocument2 pagesShell Omala s2 GX 320 TdsOnie Hammamz OylNo ratings yet

- Allergies To Cross-Reactive Plant Proteins: Takeshi YagamiDocument11 pagesAllergies To Cross-Reactive Plant Proteins: Takeshi YagamisoylahijadeunvampiroNo ratings yet

- Introduction and Instructions: ForewordDocument20 pagesIntroduction and Instructions: ForewordDanang WidoyokoNo ratings yet

- Inv69116728 45926324Document1 pageInv69116728 45926324dany.cantaragiuNo ratings yet

- SecureCore Datasheet V2Document2 pagesSecureCore Datasheet V2chepogaviriaf83No ratings yet

- Instrumentation and Control Important Questions and AnswersDocument72 pagesInstrumentation and Control Important Questions and AnswersAjay67% (6)

- Class B Digital Device Part 15 of The FCC RulesDocument7 pagesClass B Digital Device Part 15 of The FCC RulesHemantkumarNo ratings yet

- Alpine MRV f305Document2 pagesAlpine MRV f305Luis RrNo ratings yet

- Nelson/Salmo Pennywise March 15, 2016Document48 pagesNelson/Salmo Pennywise March 15, 2016Pennywise PublishingNo ratings yet

- Blockchain Unit Wise Question BankDocument3 pagesBlockchain Unit Wise Question BankMeghana50% (4)

- New Form 2550 M Monthly VAT Return P 1 2 1Document3 pagesNew Form 2550 M Monthly VAT Return P 1 2 1The ApprenticeNo ratings yet

- OPERATING MANUAL Micro Powder MillDocument51 pagesOPERATING MANUAL Micro Powder MillSher AhmadNo ratings yet