Professional Documents

Culture Documents

MAX15021

Uploaded by

Phong Phan CôngOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MAX15021

Uploaded by

Phong Phan CôngCopyright:

Available Formats

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

General Description Benefits and Features

The MAX15021 is a dual-output, pulse-width-modulated • Integration Reduces Power-Supply Footprint for Space-

(PWM), step-down DC-DC regulator with tracking (coin- Constrained Designs

cident and ratiometric) and sequencing options. The • Dual-Output Synchronous Buck Regulators

device operates from 2.5V to 5.5V and each output can • Integrated Switches for 4A and 2A Output Currents

be adjusted from 0.6V to the input supply (VAVIN). The • Programmable Switching Frequency from 500kHz

MAX15021 delivers up to 4A (regulator 1) and 2A (reg- to 4MHz

ulator 2) of output current. This device offers the ability • 28-Pin TQFN Package (5mm x 5mm)

to adjust the switching frequency from 500kHz to 4MHz • 180° Out-Of-Phase Operation Reduces Input

and provides the capability of optimizing the design in

Ripple Current and Thus the Size of the Input

terms of size and performance.

Bypass Capacitors

The MAX15021 utilizes a voltage-mode control scheme

• Sophisticated Tracking/Sequencing Functions

with external compensation to provide good noise

Facilitate Reliable Processor Operation

immunity and maximum flexibility in selecting inductor

• Digital Soft-Start and Soft-Stop for Tracking

values and capacitor types. The dual switching regula-

tors operate 180° out-of-phase, thereby reducing the Applications

RMS input ripple current and thus the size of the input • Digital Soft-Start into a Prebiased Load for

bypass capacitor significantly. Sequencing Applications

• Sequencing or Coincident/Ratiometric Tracking

The MAX15021 offers the ability to track (coincident or

ratiometric) or sequence during power-up and power- • Flexible Enough for Use in a Range of Designs

down operation. When sequencing, it powers up glitch- • 2.5V to 5.5V Input Voltage Range

free into a prebiased output. • Output-Voltage Adjustable from 0.6V to VAVIN

• External Compensation for Maximum Flexibility

Additional features include an internal undervoltage

lockout with hysteresis and a digital soft-start/soft-stop • 100% Maximum Duty Cycle

for glitch-free power-up and power-down. Protection • Integrated Protection Features Save Space and

features include lossless cycle-by-cycle current limit, Increase Reliability

hiccup-mode output short-circuit protection, and ther- • Lossless, Cycle-by-Cycle Current Sensing

mal shutdown. • Thermal Shutdown and Hiccup-Mode Short-Circuit

The MAX15021 is available in a space-saving, 5mm x Protection

5mm, 28-pin TQFN-EP package and is specified for • 20µA Shutdown Current Extends Battery Life in

operation from -40°C to +125°C temperature range. Portable Applications

Applications

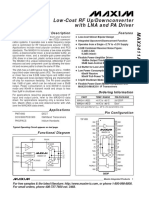

Pin Configuration

RFID Reader Cards

PGND2

DVDD2

Power-over-Ethernet (PoE) IP Phones TOP VIEW

PVIN2

N.C.

N.C.

N.C.

LX2

Automotive Multimedia 21 20 19 18 17 16 15

Multivoltage Supplies N.C. 22 14 N.C.

COMP2 23 13 N.C.

Networking/Telecom

FB2 24 12 COMP1

MAX15021

EN2 25 11 FB1

Ordering Information SGND 26 10 EN1

AVIN 27 9 DVDD1

PART TEMP RANGE PIN-PACKAGE + *EP

RT 28 8 PGND1

MAX15021ATI/V+ -40°C to +125°C 28 TQFN-EP*

1 2 3 4 5 6 7

/V denotes an automotive qualified part.

SEL

PGND1

LX1

PVIN1

PVIN1

LX1

PGND1

+Denotes a lead(Pb)-free/RoHS-compliant package.

*EP = Exposed pad.

*EP = EXPOSED PAD.

19-4106; Rev 2; 4/15

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Absolute Maximum Ratings

AVIN, PVIN_, DVDD_, EN_, FB_, RT, Continuous Power Dissipation (TA = +70°C)

SEL to SGND .........................................................-0.3V to +6V 28-Pin TQFN (derate 34.5mW/°C above +70°C) .....2758.6mW

COMP_ to SGND .....................................-0.3V to (VAVIN + 0.3V) Junction-to-Case Thermal Resistance (θJC)(Note 2) .........2°C/W

PGND_ to SGND ...................................................-0.3V to +0.3V Junction-to-Ambient Thermal Resistance (θJA)(Note 2) ..29°C/W

LX_ Current (Note 1) Operating Temperature Range .........................-40°C to +125°C

Regulator 1...............................................................................6A Maximum Junction Temperature .....................................+150°C

Regulator 2...............................................................................3A Storage Temperature Range .............................-60°C to +150°C

Current into Any Pin other than PVIN_, Lead Temperature (soldering, 10s) .................................+300°C

LX_, and PGND_ ..............................................................50mA

Note 1: LX_ has internal diodes to PGND_ and PVIN_. Applications that forward bias these diodes should take care not to exceed

the IC’s package power dissipation.

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-

layer board. For detailed information on package thermal considerations see www.maximintegrated.com/thermal-tutorial.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Electrical Characteristics

(VAVIN = VPVIN_ = VDVDD_ = 3.3V, VPGND_ = VSGND_ = 0V, RT = 25kΩ, and TA = TJ = -40°C to +125°C, unless otherwise noted.

Typical values are at TA = +25°C.) (Note 3)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SYSTEM SPECIFICATIONS

VAVIN = VPVIN1 = VPVIN2 = VDVDD1 =

Input-Voltage Range 2.5 5.5 V

VDVDD2

Undervoltage Lockout Threshold AVIN rising 2.1 2.2 2.3 V

Undervoltage Lockout Hysteresis 0.12 V

Operating Supply Current VEN_= 1.3V, VFB_ = 0.8V 3.5 6 mA

Shutdown Supply Current VEN_ = 0V 20 65 µA

PWM DIGITAL SOFT-START/SOFT-STOP

Clock

Soft-Start/Soft-Stop Duration 4096

Cycles

Reference Voltage Steps 64 Steps

PWM ERROR AMPLIFIERS

FB1, FB2 Input Bias Current -1 +1 µA

FB1, FB2 Voltage Set-Point 0.593 0.599 0.605 V

COMP1, COMP2 Voltage Range ICOMP_ = -250µA to +250µA 0.3 VAVIN - 0.5 V

Error-Amplifier Open-Loop Gain 80 dB

Error-Amplifier Unity-Gain 12 MHz

POWER MOSFETs

Regulator 1 p-Channel MOSFET VDVDD1 = 5V 50 90 mΩ

Regulator 1 n-Channel MOSFET VDVDD1 = 5V 30 50 mΩ

Regulator 1 Gate Charge VDVDD1 = 5V 8 nC

Maximum LX1 RMS Current 4 A

Regulator 2 p-Channel MOSFET VDVDD2 = 5V 100 180 mΩ

Regulator 2 n-Channel MOSFET VDVDD2 = 5V 60 100 mΩ

Regulator 2 Gate Charge VDVDD2 = 5V 4 nC

Maximum LX2 RMS Current 2 A

www.maximintegrated.com Maxim Integrated | 2

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Electrical Characteristics (continued)

(VAVIN = VPVIN_ = VDVDD_ = 3.3V, VPGND_ = VSGND_ = 0V, RT = 25kΩ, and TA = TJ = -40°C to +125°C, unless otherwise noted.

Typical values are at TA = +25°C.) (Note 3)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

PWM CURRENT LIMIT AND HICCUP MODE

VAVIN = 3.3V 4.5 4.9 5.3

Regulator 1 Peak Current Limit A

VAVIN = 2.5V 3.4 3.65 3.95

VAVIN = 3.3V 4.0 4.9 5.65

Regulator 1 Valley Current Limit A

VAVIN = 2.5V 3.0 3.7 4.25

VAVIN = 3.3V 2.25 2.45 2.65

Regulator 2 Peak Current Limit A

VAVIN = 2.5V 1.70 1.85 1.98

VAVIN = 3.3V 2.0 2.5 2.83

Regulator 2 Valley Current Limit A

VAVIN = 2.5V 1.5 1.85 2.13

Number of Cumulative Current- Clock

NCL 4

Limit Events to Hiccup Cycles

Number of Consecutive Noncurrent Clock

NCLR 3

Limit Cycles to Clear NCL Cycles

Clock

Hiccup Timeout NHT 8192

Cycles

ENABLE/SEL

EN_ Threshold VEN_ rising 1.207 1.225 1.243 V

EN_ Hysteresis 0.12 V

EN_ Input Current -2.5 +2.5 µA

SEL High Threshold 0.85 x VAVIN V

SEL Low Threshold 0.2 x VAVIN V

SEL Input Bias Current Present only during startup -100 +100 µA

OSCILLATOR

fSW = 3MHz x [VRT(V)/1.067(V)]

Switching Frequency Range fSW 500 4000 kHz

(Note 4)

fSW ≤ 1500kHz -6 +6

Oscillator Accuracy %

fSW > 1500kHz -10 +10

Phase Shift Between Regulators 180 Degrees

RT Current 0 < VRT < 1.067V 31.30 32 32.58 µA

RT Voltage Range VRT 0.13 1.067 V

Minimum Controllable On-Time 60 ns

Minimum Controllable Off-Time 60 ns

PWM Ramp Amplitude VAVIN/4 V

PWM Ramp Valley 0.3 V

THERMAL SHUTDOWN

Thermal Shutdown Temperature Temperature rising +160 °C

Thermal Shutdown Hysteresis 15 °C

Note 3: Specifications are 100% production tested at TA = +25°C and TA = +125°C. Maximum and minimum specifications over

temperature are guaranteed by design.

Note 4: When operating with VAVIN = 2.5V, the maximum switching frequency should be derated to 3MHz.

www.maximintegrated.com Maxim Integrated | 3

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Typical Operating Characteristics

(VAVIN = VDVDD1 = VDVDD2 = VPVIN1 = VPVIN2 = 5V, VOUT1 = 3.3V, VOUT2 = 1.5V, VPGND_ = 0V, RT = 16.5kΩ. TA = +25°C, unless

otherwise noted.)

CHANNEL 1 EFFICIENCY CHANNEL 1 EFFICIENCY CHANNEL 2 EFFICIENCY

vs. LOAD CURRENT vs. LOAD CURRENT vs. LOAD CURRENT

100 100 100

MAX15021 toc01

MAX15021 toc02

MAX15021 toc03

90 90 90

80 80 80

VPVIN1 = 3.3V 70 VOUT1 = 1.0V 70 PVIN2 = 3.3V

70

EFFICIENCY (%)

EFFICIENCY (%)

EFFICIENCY (%)

60 60 VOUT1 = 1.8V 60

VPVIN1 = 5V PVIN2 = 5V

50 50 50

40 VOUT1 = 3.3V 40

40

30 30

30

20 VPVIN1 = 5V 20 VOUT2 = 1.5V

20 VOUT1 = 1.8V

10 fSW = 2MHz 10 fSW = 2MHz

10 fSW = 2MHz EN2 = 0V EN1 = 0V

EN2 = 0V 0 0

0 100 1000 5000 100 1000 3000

100 1000 5000 LOAD CURRENT (mA) LOAD CURRENT (mA)

LOAD CURRENT (mA)

CHANNEL 2 EFFICIENCY CHANNEL 1 CHANNEL 2

vs. LOAD CURRENT LOAD REGULATION LOAD REGULATION

100 3.320 1.5070

MAX15021 toc06

MAX15021 toc04

MAX15021 toc05

90 3.318 1.5065

80 3.316 1.5060

VOUT2 = 2.5V

70 3.314 1.5055

EFFICIENCY (%)

VPVIN2 = 5V

60 VOUT2 = 1.5V 3.312 1.5050

VOUT2 (V)

VOUT1 (V)

50 VOUT2 = 1.0V 3.310 1.5045

40 3.308 1.5040 VPVIN2 = 3.3V

30 3.306 1.5035

20 VPVIN2 = 5V 3.304 1.5030

10 fSW = 2MHz 3.302 VPVIN1 = 5V 1.5025

EN1 = 0V fSW = 2MHz fSW = 2MHz

0 3.300 1.5020

100 1000 3000 0 0.5 1.0 1.5 2.0 2.5 3.0 0 0.25 0.50 0.75 1.00 1.25 1.50

LOAD CURRENT (mA) LOAD CURRENT (A) LOAD CURRENT (A)

SWITCHING FREQUENCY SWITCHING FREQUENCY

vs. RT RESISTANCE vs. TEMPERATURE

4.5 0.5

MAX15021 toc08

MAX15021 toc07

CHANGE IN SWITCHING FREQUENCY (%)

4.0 0.4

SWITCHING FREQUENCY (MHz)

0.3

3.5

0.2

3.0

0.1

2.5

0

2.0

-0.1

1.5 -0.2

1.0 -0.3

0.5 -0.4

fSW = 2MHz

0 -0.5

0 5 10 15 20 25 30 35 -40 -25 -10 5 20 35 50 65 80 95 110 125

RT RESISTANCE (kΩ) TEMPERATURE (°C)

www.maximintegrated.com Maxim Integrated | 4

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Typical Operating Characteristics (continued)

(VAVIN = VDVDD1 = VDVDD2 = VPVIN1 = VPVIN2 = 5V, VOUT1 = 3.3V, VOUT2 = 1.5V, VPGND_ = 0V, RT = 16.5kΩ. TA = +25°C, unless

otherwise noted.)

QUIESCENT CURRENT SWITCHING CURRENT

vs. TEMPERATURE vs. TEMPERATURE

5.00 27

MAX15021 toc09

MAX15021 toc10

26

4.75

25

4.50 24 REGULATOR 1 ENABLED

QUIESCENT CURRENT (mA)

SWITCHING CURRENT (mA)

23 VOUT1 = 3.3V

4.25

22

4.00 21

20

3.75

19

3.50 18

3.25 17

16 REGULATOR 2 ENABLED

3.00 15 VOUT2 = 1.5V

14

2.75

NO SWITCHING 13

2.50 12

-40 -25 -10 5 20 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C) TEMPERATURE (°C)

NORMALIZED UNDERVOLTAGE LOCKOUT EN_ THRESHOLD

THRESHOLD vs. TEMPERATURE vs. TEMPERATURE

1.030 1.260

MAX15021 toc12

MAX15021 toc11

1.025 1.255

NORMALIZED UVLO THRESHOLD (V)

1.020

1.250

1.015

EN_ THRESHOLD (V)

1.245

1.010

1.005 1.240

1.000 1.235

0.995 1.230

0.990

1.225

0.985

1.220

0.980

0.975 VUVLO (NOM) = 2.2V 1.215

0.970 1.210

-40 -25 -10 5 20 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C) TEMPERATURE (°C)

COINCIDENT TRACKING SOFT-START COINCIDENT TRACKING SOFT-STOP

MAX15021 toc13 MAX15021 toc14

VAVIN VAVIN

5V/div 5V/div

0V 0V

VOUT1 VOUT1

1V/div

EN1

VOUT2

VOUT2

1V/div

1V/div

0V 0V

1ms/div 400μs/div

www.maximintegrated.com Maxim Integrated | 5

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Typical Operating Characteristics (continued)

(VAVIN = VDVDD1 = VDVDD2 = VPVIN1 = VPVIN2 = 5V, VOUT1 = 3.3V, VOUT2 = 1.5V, VPGND_ = 0V, RT = 16.5kΩ. TA = +25°C, unless

otherwise noted.)

CHANNEL 1 LOAD STEP RESPONSE CHANNEL 1 LOAD STEP RESPONSE

MAX15021 toc15 MAX15021 toc16

EN2 = 0V EN2 = 0V

VPVIN1 VPVIN1

5V/div 5V/div

0V 0V

VOUT1 VOUT1

3.3V, AC-COUPLED 3.3V, AC-COUPLED

100mV/div 100mV/div

IOUT1 IOUT1

2A/div 2A/div

0A 0A

20μs/div 20μs/div

CHANNEL 2 LOAD STEP RESPONSE CHANNEL 2 LOAD STEP RESPONSE

MAX15021 toc17 MAX15021 toc18

EN1 = 0V EN1 = 0V

VPVIN2 VPVIN2

5V/div 5V/div

0V 0V

VOUT2 VOUT2

1.5V, AC-COUPLED 1.5V, AC-COUPLED

100mV/div 100mV/div

IOUT2 IOUT2

1A/div 1A/div

0A 0A

20μs/div 20μs/div

180° OUT-OF-PHASE OPERATION

MAX15021 toc19

PVIN1 = PVIN2

5V/div

0V

VLX1

5V/div

0V

VLX2

5V/div

0V

IOUT1 = 3A

IOUT2 = 1.5A

200ns/div

www.maximintegrated.com Maxim Integrated | 6

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Pin Description

PIN NAME FUNCTION

Track/Sequence Select Input. Connect SEL to ground to configure the device as a sequencer. Connect

SEL to AVIN for tracking with output 1 as the master. Leave SEL unconnected for tracking with output 2

1 SEL

as the master. Use the output with the higher voltage as the master and the output with the lower voltage

as the slave.

Power Ground Connection for Regulator 1. Connect the negative terminals of the input and output filter

2, 7, 8 PGND1 capacitor to PGND1. Connect PGND1 externally to SGND at a single point, typically at the negative

terminal of the input capacitor.

Inductor Connection for Regulator 1. LX1 is the drain connection of the internal high-side p-channel

3, 6 LX1

MOSFET and the drain connection of the internal synchronous n-channel MOSFET for regulator 1.

Input Supply Voltage for Regulator 1. Connect to an external voltage source from 2.5V to 5.5V. Bypass

4, 5 PVIN1

PVIN1 to PGND1 with a 1µF (min) ceramic capacitor.

9 DVDD1 Switch Driver Supply for Regulator 1. Connect externally to PVIN1.

Enable Input for Regulator 1. When configured as a sequencer, EN1 must exceed 1.225V (typ) for the

10 EN1 PWM controller to begin regulating output 1. When configured as a tracker, connect EN1 to the center

tap of a resistive divider from the regulator 2 output.

Feedback Regulation Point for Regulator 1. Connect FB1 to the center tap of a resistive divider from the

11 FB1

regulator 1 output to SGND to set the output voltage. The FB1 voltage regulates to 0.6V (typ).

12 COMP1 Error-Amplifier Output for Regulator 1. Connect COMP1 to the compensation feedback network.

13, 14, 15,

N.C. No Connection. Do not connect.

20, 21, 22

16 DVDD2 Switch Driver Supply for Regulator 2. Connect externally to PVIN2.

Power Ground Connection for Regulator 2. Connect the negative terminals of the input and output filter

17 PGND2 capacitors to PGND2. Connect PGND2 externally to SGND at a single point, typically at the negative

terminal of the input capacitor.

Inductor Connection for Regulator 2. LX2 is the drain connection of the internal high-side p-channel

18 LX2

MOSFET and the drain connection of the internal synchronous n-channel MOSFET for regulator 2.

Input Supply Voltage for Regulator 2. Connect to an external voltage source from 2.5V to 5.5V. Bypass

19 PVIN2

PVIN2 to PGND2 with a 1µF (min) ceramic capacitor.

23 COMP2 Error-Amplifier Output for Regulator 2. Connect COMP2 to the compensation feedback network.

Feedback Regulation Point for Regulator 2. Connect to the center tap of a resistive divider from the

24 FB2

regulator 2 output to SGND to set the output voltage. The FB2 voltage regulates to 0.6V (typ).

Enable Input for Regulator 2. When configured as a sequencer, EN2 must exceed 1.225V (typ) for the

25 EN2 PWM controller to begin regulating output 2. When configured as a tracker, connect EN2 to the center

tap of a resistive divider from the regulator 1 output.

Signal Ground. Connect SGND to PGND_ at a single point, typically near negative terminal of the input

26 SGND

bypass capacitor.

27 AVIN Input Voltage. Bypass AVIN to SGND with a 100nF (min) ceramic capacitor.

Oscillator Timing Resistor Connection. Connect a 4.2kΩ to 33kΩ resistor from RT to SGND to program

28 RT

the switching frequency from 500kHz to 4MHz.

Exposed Pad. Connect EP to a large copper plane at SGND potential to improve thermal dissipation. Do

— EP

not use as the main SGND connection.

www.maximintegrated.com Maxim Integrated | 7

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Functional Diagrams

AVIN SEL SGND

ON1 ON2 SHDN MAX15021

SEQ1 PWM CONTROLLER 1

1.225V

EN CONFIG SEQ2 SEL DECODE

1.1V

SEQ1

EN1

0.6V THERMAL SHDN

ON1

REF SHDN SEQ1 SEQ2 1.225V

1.1V

CLK1 DOWN1 OVL OVL1

VREF

SEQ1 CONFIG OVL2 DVDD1

VREF

DIGITAL VR1 PVIN1

SOFT-START CLK1 CLK2

AND SOFT-STOP E/A HIGH-SIDE

EN1

OVL1 RES CURRENT

FB1 OVERLOAD SENSE

ILIM1 MANAGEMENT

AVIN

BREAK-

D Q BEFORE- LX1

MAKE

COMP1

CPWM

EN CLK1 D0

RT RAMP

OSC LOW-SIDE

CURRENT

LEVEL

SENSE

SHIFT

CLK2 CLK

PGND1

www.maximintegrated.com Maxim Integrated | 8

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Functional Diagrams (continued)

SEQ2

EN2 SHDN

ON1 ON2 MAX15021

ON2

1.225V SEQ1 PWM CONTROLLER 2

1.1V EN CONFIG

SEQ2

VREF SEQ1 SEQ2

CLK2 DOWN2 OVL OVL1

DVDD2

SEQ1 CONFIG OVL2

VREF PVIN2

DIGITAL VR2

SOFT-START

AND SOFT-STOP E/A

EN2 CLK1 CLK2

FB2 HIGH-SIDE

OVL2 RES CURRENT

OVERLOAD SENSE

ILIM2

MANAGEMENT

AVIN

BREAK-

D Q BEFORE- LX2

MAKE

COMP2

CPWM

D0

CLK2 RAMP

LOW-SIDE

CURRENT

LEVEL CLK SENSE

SHIFT

PGND2

www.maximintegrated.com Maxim Integrated | 9

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Detailed Description when soft-start is completed, regardless of the output

capacitance and load.

The MAX15021 incorporates dual-output, PWM, step-

down, DC-DC regulators with tracking and sequencing For tracking applications, soft-stop commences when the

options. The device operates over the input-voltage enable input falls below 1.1V (typ). The soft-stop circuitry

range of 2.5V to 5.5V. Each PWM regulator provides an ramps down the reference voltage controlling the output-

adjustable output down to 0.6V and delivers up to 4A voltage rate of fall. The output voltage is decremented

(regulator 1) and 2A (regulator 2) of load current. The through 64 equal steps in 4096 clock cycles.

high switching frequency (up to 4MHz) and integrated Oscillator

power switches optimize the MAX15021 for high-perfor- Use an external resistor at RT to program the

mance and small-size power management solutions. MAX15021 switching frequency from 500kHz to 4MHz.

Each of the MAX15021 PWM regulator sections utilizes Calculate the appropriate resistor at RT for the desired

a voltage-mode control scheme for good noise immuni- output switching frequency (fSW):

ty and offers external compensation allowing for maxi-

mum flexibility with a wide selection of inductor values f [kHz] × 1.067[V]

and capacitor types. The device operates at a fixed R T [kΩ] = SW

switching frequency that is programmable from 500kHz 32[μA] × 4[MHz]

to 4MHz with a single resistor. Operating the regulators

with 180° out-of-phase clocking, and at frequencies up Tracking/Sequencing

to 4MHz, significantly reduces the RMS input ripple The MAX15021 features coincident/ratiometric tracking

current. The resulting peak input current reduction (and and sequencing (see Figure 1). Connect SEL to ground

increase in the ripple frequency) significantly reduces to configure the device as sequencer. Connect SEL to

the required amount of input bypass capacitance. AVIN for tracking with output 1 as the master. Leave SEL

unconnected for tracking with output 2 as the master.

The MAX15021 provides coincident tracking, ratiomet-

Assign the output with the higher voltage as the master.

ric tracking, or sequencing to allow tailoring of power-

up/power-down sequence depending on the system

requirements. When sequencing, it powers up glitch-

free into a prebiased output. VOUT1

The MAX15021 includes internal undervoltage lockout VOUT2

with hysteresis, digital soft-start/soft-stop for “glitch-free”

power-up and power-down. Protection features include

lossless, cycle-by-cycle current limit, hiccup-mode out- SOFT-START SOFT-STOP

put short-circuit protection, and thermal shutdown.

a) COINCIDENT TRACKING OUTPUTS

Undervoltage Lockout (UVLO)

The supply voltage (VAVIN) must exceed the default VOUT1

UVLO threshold before any operation starts. The UVLO VOUT2

circuitry keeps the MOSFET drivers, oscillator, and all

the internal circuitry shut down to reduce current con-

sumption. The UVLO rising threshold is 2.2V (typ) with SOFT-STOP

SOFT-START

a 120mV (typ) hysteresis.

Digital Soft-Start/Soft-Stop b) RATIOMETRIC TRACKING OUTPUTS

The MAX15021 soft-start feature allows the load volt- VOUT1

age to ramp up in a controlled manner, eliminating out- VOUT2

put-voltage overshoot. Soft-start begins after VAVIN

exceeds the undervoltage lockout threshold and the

enable input is above 1.225V (typ). The soft-start cir-

cuitry ramps up the reference voltage, controlling the SOFT-START SOFT-STOP

rate of rise of the output voltage, and reducing input

c) SEQUENCED OUTPUTS

surge currents during startup. The soft-start duration is

4096 clock cycles. The output voltage is incremented Figure 1. Graphical Representation of Coincident Tracking,

through 64 equal steps. The output reaches regulation Ratiometric Tracking, and Sequencing

www.maximintegrated.com Maxim Integrated | 10

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Coincident/Ratiometric Tracking when the other output is shorted to ground. When the

The enable inputs in conjunction with digital soft-start slave is shorted and enters hiccup mode, the master will

and soft-stop provide coincident/ratiometric tracking. soft-stop. When the master is shorted and the part

Track an output voltage by connecting a resistive enters in hiccup mode, the slave will ratiometrically soft-

divider from the output being tracked to its enable stop. Coming out of hiccup mode, both outputs will soft-

input. For example, for VOUT2 to coincidentally track start coincidently or ratiometrically depending on their

V OUT1, connect the same resistive divider used for initial configuration. During the thermal shutdown or

FB2, from VOUT1 to EN2 to SGND (see Figure 2). power-off when the input falls below its UVLO, the out-

Track ratiometrically by connecting EN_ to SGND. This put voltages decrease at a rate depending on the

synchonizes the soft-start and soft-stop of all the regu- respective output capacitance and load.

lator references, and hence their respective output volt- See Figure 1 for a graphical representation of coinci-

ages will track ratiometrically (see Figure 2). dent/ratiometric tracking.

When the MAX15021 regulators are configured as volt- Sequencing

age trackers, output short-circuit fault conditions at When sequencing, the voltage at the enable inputs

either master or slave output are handled carefully—nei- must exceed 1.225V (typ) for each PWM controller to

ther the master nor slave output will remain energized start (see Figure 1c).

RATIOMETRIC TRACKING COINCIDENT TRACKING COINCIDENT TRACKING

VRIN1 VRIN1 VRIN2

EN1 EN1 EN2

VOUT1 VOUT2

EN2

RA RC

SEL AVIN

EN2 EN1

OUTPUT 1 IS THE MASTER AND

OUTPUT 2 IS THE SLAVE.

RB RD

VRIN2

VOUT2 VOUT1

RA RC

EN2

FB2 FB1

RB RD

EN1

SEL UNCONNECTED SEL AVIN SEL UNCONNECTED

OUTPUT 2 IS THE MASTER AND OUTPUT 1 IS THE MASTER AND OUTPUT 2 IS THE MASTER AND

OUTPUT 1 IS THE SLAVE. OUTPUT 2 IS THE SLAVE. OUTPUT 1 IS THE SLAVE.

Figure 2. Ratiometric Tracking and Coincident Tracking Configurations

www.maximintegrated.com Maxim Integrated | 11

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Error Amplifier

The output of the internal voltage-mode error amplifier

(COMP_) is provided for frequency compensation (see

the Compensation-Design Guidelines section). FB_ is

CURRENT LIMIT IN INITIATE HICCUP

the inverting input of the error amplifier. The error COUNT OF 4 TIMEOUT

amplifier has an 80dB open-loop gain and a 12MHz NCL NHT

gain bandwidth (GBW) product. CLR

Output Short-Circuit

Protection (Hiccup Mode)

The MAX15021 features lossless, high-side peak cur-

rent limit and low-side, valley current limit. At short duty

cycles, both limits are active. At high duty cycles, only

the high-side peak current limit is active. Either limit

causes the hiccup mode count (NCL) to increment. IN

COUNT OF 3

For duty cycles less than 50%, the low-side valley cur- NCLR

rent limit is active. Once the high-side MOSFET turns off, CLR

the voltage across the low-side MOSFET is monitored. If

this voltage does not exceed the current-limit threshold

at the end of the cycle, the high-side MOSFET turns on Figure 3. Hiccup-Mode Block Diagram

normally at the start of the next cycle. If the voltage

exceeds the current-limit threshold just before the

Startup into a Prebiased Output

beginning of a new PWM cycle, the controller skips that

(Sequencing Mode)

cycle. During severe overload or short-circuit condi-

In sequencing mode, the regulators start into a prebi-

tions, the switching frequency of the device appears to

ased output and soft-stop is disabled. During soft-start,

decrease because the on-time of the low-side MOSFET

the complementary switching sequence is inhibited until

extends beyond a clock cycle.

the PWM comparator commands its first PWM pulse.

If the current-limit threshold is exceeded for more than Until then, the converters do not sink current from the

four cumulative clock cycles (NCL), the device shuts outputs. The first PWM pulse occurs when the ramping

down for 8192 clock cycles (hiccup timeout) and then reference voltage increases above the FB_ voltage.

restarts with a soft-start sequence. If three consecutive

cycles pass without a current-limit event, the count of PWM Controllers

NCL is cleared (see Figure 3). Hiccup mode protects

the device against a continuous output short circuit.

Design Procedure

The internal current limit is constant from 5.5V down to Setting the Switching Frequency

3V and decreases linearly by 50% from 3V to 2V. See Connect a 4.2kΩ to 33kΩ resistor from RT to SGND to

the Electrical Characteristics table. program the switching frequency from 500kHz to

4MHz. Calculate the resistor connected to RT using the

Thermal-Overload Protection following equation:

The MAX15021 features an integrated thermal-overload

protection with temperature hysteresis. Thermal-over- f [kHz] × 1.067[V]

load protection limits the total power dissipation in the R T [kΩ] = SW

device and protects it in the event of an extended ther- 32[μA] × 4[MHz]

mal fault condition. When the die temperature exceeds

Higher frequencies allow designs with lower inductor

+160°C, an internal thermal sensor shuts down the

values and less output capacitance. At higher switch-

device, turning off the internal power MOSFETs and

ing frequencies core losses, gate-charge currents, and

allowing the die to cool. After the die temperature falls

switching losses increase. When operating from VAVIN

by +15°C, the part restarts with a soft-start sequence.

≤ 3V, the switching frequency (fSW) should be derated

to 3MHz (maximum).

www.maximintegrated.com Maxim Integrated | 12

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Effective Input-Voltage Range where VPVIN_ is the input supply voltage, VOUT_ is the

Although the MAX15021’s regulators can operate from regulator output voltage, and fSW is the switching fre-

input supplies ranging from 2.5V to 5.5V, the input-volt- quency. Use typical values for VPVIN_ and VOUT_ so

age range can be effectively limited by the that efficiency is optimum for typical conditions. The

MAX15021’s duty-cycle limitations for a given output switching frequency (fSW) is programmable between

voltage (V OUT_ ). The maximum input voltage 500kHz and 4MHz (see the Oscillator section).

(VPVIN_MAX) can be effectively limited by the control- The peak-to-peak inductor current (ΔI P-P ), which

lable minimum on-time (tON(MIN)): reflects the peak-to-peak output ripple, is largest at the

maximum input voltage. See the Output-Capacitor

VOUT_ [V] Selection section to verify that the worst-case output

VPVIN_MAX [V] ≤

t ON(MIN) [μs] × fSW [MHz] current ripple is acceptable.

Select an inductor with a saturation current, ISAT, high-

where tON(MIN) is 0.06µs (typ). er than the maximum peak current to avoid runaway

The minimum input voltage (VPVIN_MIN) can be effec- current during continuous output short-circuit condi-

tively limited by the maximum controllable duty cycle tions. Also, confirm that the inductor’s thermal perfor-

and is calculated using the following equation: mances and projected temperature rise above ambient

does not exceed its thermal capacity. Many inductor

VOUT_ [V] manufacturers provide bias/load current versus tem-

VPVIN_MIN [V] ≥ perature rise performance curves (or similar) to obtain

1− (t OFF(MIN) [μs] × fSW [MHz])

this information.

where V OUT_ is the regulator output voltage and Input-Capacitor Selection

tOFF(MIN) is the 0.06µs (typ) controllable off-time. The discontinuous input current of the buck converter

causes large input ripple currents and therefore, the

Inductor Selection

input capacitor must be carefully chosen to withstand

Three key inductor parameters must be specified for

the input ripple current and keep the input-voltage rip-

operation with the MAX15021: inductance value (L),

ple within design requirements.

peak inductor current (IPEAK), and inductor saturation

current (ISAT). The minimum required inductance is a The input-voltage ripple is comprised of ΔVQ (caused by

function of operating frequency, input-to-output voltage the capacitor discharge) and ΔVESR (caused by the ESR

differential, and the peak-to-peak inductor current of the input capacitor). The total voltage ripple is the

(ΔIP-P). Higher ΔIP-P allows for a lower inductor value. A sum of ΔVQ and ΔVESR which peaks at the end of the

lower inductance minimizes size and cost and on-cycle. Calculate the required input capacitance and

improves large-signal and transient response. ESR for a specified ripple using the following equations:

However, efficiency is reduced due to higher peak cur-

rents and higher peak-to-peak output-voltage ripple for ΔVESR [mV]

the same output capacitor. A higher inductance ESR[mΩ] =

⎛ ΔIP−P ⎞

increases efficiency by reducing the ripple current; ⎜ILOAD(MAX) + ⎟ [A]

however, resistive losses due to extra wire turns can ⎝ 2 ⎠

exceed the benefit gained from lower ripple current lev- ⎛ VOUT_ [V] ⎞

els especially when the inductance is increased without ILOAD(MAX) [A] × ⎜ ⎟

also allowing for larger inductor dimensions. Choose ⎝ VPVIN_ [V] ⎠

CPVIN_ [μF] =

the inductor’s peak-to-peak current, ΔIP-P, in the range ΔVQ [V] × fSW [MHz]

(VPVIN_ − VOUT_ )[V] × VOUT_ [V]

of 20% to 50% of the full load current; as a rule of

thumb 30% is typical. ΔIP−P [A] =

Calculate the inductance, L, using the following equation: VPVIN_ [V] × fSW [MHz] × L[μH]

VOUT_ [V] × (VPVIN_ [V] − VOUT_ [V]) ILOAD(MAX) is the maximum output current, ΔIP-P is the

L[μH] = peak-to-peak inductor current, and VPVIN_ is the input

VPVIN_ [V] × fSW [MHz] × ΔIP−P [A]

supply voltage, VOUT_ is the regulator output voltage,

and fSW is the switching frequency.

www.maximintegrated.com Maxim Integrated | 13

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Use the following equation to calculate the input ripple put voltage deviation below the tolerable limits of the

when only one regulator is enabled: electronics being powered.

ICIN(RMS) [A] = ILOAD(MAX) [A] × Use the following equations to calculate the required

output capacitance, ESR, and ESL for minimal output

( )

VOUT_ [V] × VPVIN_ − VOUT_ [V] deviation during a load step:

VPVIN_ [V]

ΔVESR [mV]

The MAX15021 includes UVLO hysteresis to avoid possi- ESR[mΩ] =

ISTEP [A]

ble unintentional chattering during turn-on. Use additional

ISTEP [A] × t RESPONSE [μs]

bulk capacitance if the input source impedance is high. If COUT [μF] =

using a lower input voltage, additional input capacitance ΔVQ [V]

helps to avoid possible undershoot below the undervolt- ΔVESL [mV] × t STEP [μs]

age lockout threshold during transient loading. ESL[nH] =

ISTEP [A]

Output-Capacitor Selection

The allowed output-voltage ripple and the maximum where ISTEP is the load step, tSTEP is the rise time of the

deviation of the output voltage during load steps deter- load step, and tRESPONSE is the response time of the

mine the required output capacitance and its ESR. The controller.

output ripple is mainly composed of ΔVQ (caused by Compensation-Design Guidelines

the capacitor discharge) and ΔVESR (caused by the The MAX15021 uses a fixed-frequency, voltage-mode

voltage drop across the equivalent series resistance of control scheme that regulates the output voltage by

the output capacitor). The equations for calculating the comparing the output voltage against a fixed reference.

output capacitance and its ESR are: The subsequent “error” voltage that appears at the

error-amplifier output (COMP_) is compared against an

ΔIP−P [A] internal ramp voltage to generate the required duty

COUT [μF] =

8 × ΔVQ [V] × fSW [MHz] cycle of the pulse-width modulator. A second-order

2 × ΔVESR [mV] lowpass LC filter removes the switching harmonics and

ESR[mΩ] = passes the DC component of the pulse-width-modulat-

ΔIP−P [A]

ed signal to the output. The LC filter has an attenuation

slope of -40dB/decade and introduces 180° of phase

where ΔIP-P is the peak-to-peak inductor current, and shift at frequencies above the LC resonant frequency.

fSW is the switching frequency. This phase shift in addition to the inherent 180° of

ΔVESR and ΔVQ are not directly additive since they are phase shift of the regulator’s negative feedback system

out of phase from each other. If using ceramic capaci- turns the feedback into unstable positive feedback. The

tors, which generally have low ESR, ΔVQ dominates. If error amplifier and its associated circuitry must be

using electrolytic capacitors, ΔVESR dominates. designed to achieve a stable closed-loop system.

The allowable deviation of the output voltage during The basic controller loop consists of a power modulator

fast load transients also affects the output capacitance, (comprised of the regulator’s pulse-width modulator,

its ESR, and its equivalent series inductance (ESL). The associated circuitry, and LC filter), an output feedback

output capacitor supplies the load current during a divider, and an error amplifier. The power modulator has

load step until the controller responds with an a DC gain set by VAVIN/VRAMP where the ramp voltage

increased duty cycle. The response time (tRESPONSE) (VRAMP) is a function of the VAVIN and results in a fixed

depends on the gain bandwidth of the controller (see DC gain of 4V/V, providing effective feed-forward com-

the Compensation-Design Guidelines section). The pensation of input-voltage supply DC variations. The

resistive drop across the output capacitor’s ESR feed-forward compensation eliminates the dependency

(ΔVESR), the drop across the capacitor’s ESL (ΔVESL), of the power modulator’s gain on the input voltage such

and the capacitor discharge (ΔVQ) cause a voltage that the feedback compensation of the error amplifier

droop during the load-step (ISTEP). Use a combination requires no modifications for nominal input-voltage

of low-ESR tantalum/aluminum electrolyte and ceramic changes. The output filter is effectively modeled as a

capacitors for better load transient and voltage ripple double-pole and a single zero set by the output induc-

performance. Nonleaded capacitors and capacitors in tance (L), the DC resistance of the inductor (DCR), the

parallel help reduce the ESL. Keep the maximum out- output capacitance (COUT) and its equivalent series

resistance (ESR).

www.maximintegrated.com Maxim Integrated | 14

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Below are equations that define the power modulator: use aluminum electrolytic capacitors while for space-

sensitive applications, use low-ESR tantalum or multilay-

VAVIN V er ceramic chip (MLCC) capacitors at the output. The

= AVIN = 4V/V

GainMOD(DC) =

VRAMP VAVIN higher switching frequencies of the MAX15021 allow the

4 use of MLCC as the primary filter capacitor(s).

1 1 First, select the passive and active power components

fLC = ≈

⎛R π × × COUT that meet the application output ripple, component

+ ESR ⎞ 2 L

2π × L × COUT × ⎜ OUT ⎟ size, and component cost requirements. Second,

⎝ ROUT + DCR ⎠ choose the small-signal compensation components to

1 achieve the desired closed-loop frequency response

fESR = and phase margin as outlined below.

2π × ESR × COUT

Closed-Loop Response and Compensation

ROUT is the load resistance of the regulator, fLC is the of Voltage-Mode Regulators

resonant break frequency of the filter, and fESR is the The power modulator’s LC lowpass filter exhibits a vari-

ESR zero of the output capacitor. See the Closed-Loop ety of responses, dependent on the value of the L and

Response and Compensation of Voltage-Mode C and their parasitics. Higher resistive parasitics

Regulators section for more information on fLC and fESR. reduce the Q of the circuit, reducing the peak gain and

The switching frequency (f SW ) is programmable phase of the system; however, efficiency is also

between 500kHz and 4MHz. Typically, the crossover reduced under these circumstances.

frequency (fCO)—the frequency at which the system’s One such response is shown in Figure 4a. In this exam-

closed-loop gain is equal to unity (crosses 0dB)— ple, the ESR zero occurs relatively close to the filter’s

should be set at or below one-tenth the switching fre- resonant break frequency, fLC. As a result, the power

quency (fSW/10) for stable closed-loop response. modulator’s uncompensated crossover is approximate-

The MAX15021 provides an internal voltage-mode error ly one-third the desired crossover frequency, fCO. Note

amplifier with its inverting input and its output available to also, the uncompensated rolloff through the 0dB plane

the user for external frequency compensation. The flexi- follows a single-pole, -20dB/decade slope, and 90° of

bility of external compensation for each controller offers phase lag. In this instance, the inherent phase margin

a wide selection of output filtering components, especial- ensures a stable system; however, the gain-bandwidth

ly the output capacitor. For cost-sensitive applications, product is not optimized.

MAX15021 fig04a MAX15021 fig04b

40 90 80 180

fLC

60 < GEA 135

20 45

40 fLC 90

|GMOD| ASYMPTOTE

PHASE (DEGREES)

fCO

PHASE (DEGREES)

MAGNITUDE (dB)

MAGNITUDE (dB)

0 |GMOD| 0 |GEA|

20 45

-20 -45 0 0

< GMOD fESR

-20 fESR -45

-40 -90

< GMOD

-40 -90

-60 -135

-60 |GMOD| -135

-80 -180 -80 -180

10 100 1k 10k 100k 1M 10M 10 100 1k 10k 100k 1M 10M

FREQUENCY (Hz) FREQUENCY (Hz)

Figure 4a. Power Modulator Gain and Phase Response with Figure 4b. Power Modulator and Type II Compensator Gain and

Lossy Bulk Output Capacitor(s) (Aluminum) Phase Response with Lossy Bulk Output Capacitor(s) (Aluminum)

www.maximintegrated.com Maxim Integrated | 15

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

As seen in Figure 4b, a Type II compensator provides for gentler response of the previous example. This is due

stable closed-loop operation, leveraging the +20dB/ to the filter components’ lower parasitic (DCR and ESR)

decade slope of the capacitor’s ESR zero, while extend- and corresponding higher frequency of the inherent

ing the closed-loop gain-bandwidth of the regulator. The ESR zero. In this example, the desired crossover fre-

zero crossover now occurs at approximately three times quency occurs below the ESR zero frequency.

the uncompensated crossover frequency, fCO. In this example, a compensator with an inherent midfre-

The Type II compensator’s midfrequency gain (approxi- quency double-zero response is required to mitigate

mately 12dB shown here) is designed to compensate the effects of the filter’s double-pole phase lag. This is

for the power modulator’s attenuation at the desired available with the Type III topology.

crossover frequency, fCO (GainE/A + GainMOD = 0dB at As demonstrated in Figure 4d, the Type III’s midfre-

fCO). In this example, the power modulator’s inherent quency double-zero gain (exhibiting a +20dB/dec

-20dB/decade rolloff above the ESR zero (fZERO,ESR) is slope, noting the compensator’s pole at the origin) is

leveraged to extend the active regulation gain-band- designed to compensate for the power modulator’s

width of the voltage regulator. As shown in Figure 4b, double-pole -40dB/decade attenuation at the desired

the net result is a three times increase in the regulator’s crossover frequency, fCO (again, GainE/A + GainMOD =

gain bandwidth while providing greater than 75° of 0dB at fCO) (see Figure 4d).

phase margin (the difference between Gain E/A and

GainMOD respective phases at crossover, fCO). In the above example the power modulator’s inherent

(midfrequency) -40dB/decade rolloff is mitigated by the

Other filter schemes pose their own problems. For midfrequency double zero’s +20dB/decade gain to

instance, when choosing high-quality filter capacitor(s), extend the active regulation gain-bandwidth of the volt-

e.g. MLCCs, the inherent ESR zero may occur at a age regulator. As shown in Figure 4d, the net result is

much higher frequency, as shown in Figure 4c. an approximate doubling in the controller’s gain band-

As with the previous example, the actual gain and width while providing greater than 55 degrees of phase

phase response is overlaid on the power modulator’s margin (the difference between GainE/A and GainMOD

asymptotic gain response. One readily observes the respective phases at crossover, fCO).

more dramatic gain and phase transition at or near the Design procedures for both Type II and Type III com-

power modulator’s resonant frequency, fLC, versus the pensators are shown below.

MAX15021 fig04c MAX15021 fig04d

40 90 80 270

|GMOD| 60 < GEA 203

20 45

40 |GEA| 135

fLC

PHASE (DEGREES)

PHASE (DEGREES)

MAGNITUDE (dB)

0 0

MAGNITUDE (dB)

fLC 20 68

fESR fCO

-20 -45 0 0

< GMOD

|GMOD|

-20 < GMOD -68

-40 -90

-40 -135

-60 |GMOD| -135

ASYMPTOTE -60 -203

fESR

-80 -180 -80 -270

10 100 1k 10k 100k 1M 10M 10 100 1k 10k 100k 1M 10M

FREQUENCY (Hz) FREQUENCY (Hz)

Figure 4c. Power Modulator Gain and Phase Response with Figure 4d. Power Modulator and Type III Compensator Gain

Low-Parasitic Capacitor(s) (MLCCs) and Phase Response with Low Parasitic Capacitors (MLCCs)

www.maximintegrated.com Maxim Integrated | 16

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Type II: Compensation when fCO > fZERO,ESR CCF

When the fCO is greater than fESR, a Type II compensa- VOUT_

tion network provides the necessary closed-loop com- CF

RF

pensated response. The Type II compensation network R1

provides a midband compensating zero and a high-fre-

quency pole (see Figures 5a and 5b).

R F C F provides the midband zero f MID,ZERO , and FB_

R2 COMP_

RFCCF provides the high-frequency pole, fHIGH,POLE.

Use the following procedure to calculate the compen- VREF

sation network components.

Calculate the fESR and LC double pole, fLC: Figure 5a. Type II Compensation Network

1 GAIN

fESR = (dB)

2π × ESR × COUT

1

fLC ≈

2π × L × COUT

where COUT is the regulator output capacitor and ESR 1ST ASYMPTOTE

(ωR1CF)-1

is the series resistance of C OUT . See the Output-

2ND ASYMPTOTE

Capacitor Selection section for more information on cal- (RFR1)-1

culating COUT and ESR.

3RD ASYMPTOTE

Set the compensator’s leading zero, fZ1, at or below the (ωRFCCF)-1

filter’s resonant double-pole frequency from:

fZ1 ≤ fLC

1ST POLE ω (rad/sec)

(AT ORIGIN) 1ST ZERO 2ND POLE

Set the compensator’s high-frequency pole, fP1, at or (RFCF)-1 (RFCCF)-1

below one-half the switching frequency, fSW:

Figure 5b. Type II Compensation Network Response

f

fP1 ≤ SW series resistance of the output capacitor, and VOUT_ is

2 the desired output voltage.

To maximize the compensator’s phase lead, set the The gain of the error amplifier (GainE/A) in the midband

desired crossover frequency, fCO, equal to the geomet- frequencies is:

ric mean of the compensator’s leading zero, fZ1, and

R [kΩ]

high-frequency pole, fP1, as follows: GainE/A = F

R1 [kΩ]

fCO = fZ1 × fP1

The total loop gain is the product of the modulator gain

Select the feedback resistor, RF, in the range of 3.3kΩ and the error amplifier gain at fCO and should be set

to 30kΩ. equal to 1 as follows:

Calculate the gain of the modulator (GainMOD)—com- GainMOD x GainE/A = 1

prised of the regulator’s pulse-width modulator, LC filter, So:

feedback divider, and associated circuitry—at the desired

crossover frequency, fCO, using the following equation:

⎡ RF ⎤ ⎡ 4 ×ESR x VFB ⎤

ESR [mΩ] VFB [V] 20 × log10 ⎢⎣ R1 ⎥⎦ + 20 × log10 ⎢⎢ 2 π × fCO ×L x VOUT_ ⎥⎥ = 0dB

GainMOD = 4(V/V) × × ⎣ ⎦

(2π × fCO [kHz] × L[μH]) VOUT_ [V] RF

×

4 × ESR x VFB

=1

R1 2π × fCO × L x VOUT_

where VFB is the 0.6V (typ) FB_ input-voltage set-point,

L is the value of the regulator inductor, ESR is the

www.maximintegrated.com Maxim Integrated | 17

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Solving for R1:

VOUT_

CCF

RF [kΩ] × 4 × ESR[mΩ] × VFB [V]

R1 [kΩ] =

2π × fCO [kHz] × L[μH] × VOUT_ [V] RI RF CF

R1

where VFB is the 0.6V (typ) FB_ input-voltage set-point, CI

L is the value of the regulator inductor, ESR is the FB_

series resistance of the output capacitor, and VOUT_ is COMP_

the desired output voltage. R2

VREF

1) CF is determined from the compensator’s leading

zero, fZ1, and RF as follows:

1 Figure 6a. Type III Compensation Network

CF [μF] =

2π × RF [kΩ] × fZ1[kHz] GAIN

(dB)

2) CCF is determined from the compensator’s high-fre-

quency pole, fP1, and RF as follows:

1ST ASYMPTOTE

(ωR1CF)-1 4TH ASYMPTOTE

1

CCF [μF] = ( )

RF

2π × RF [kΩ] × fP1[kHz] RI

2ND ASYMPTOTE 5TH ASYMPTOTE

RF 1 3RD ASYMPTOTE (ωRICCF)-1

3) Calculate R2 using the following equation: R1( ) (ωRFCI)-1

VFB [V]

R2 [kΩ] = R1[kΩ] ×

VOUT_ [V] − VFB [V]

1ST POLE ω (rad/sec)

(AT ORIGIN) 1ST ZERO 2ND POLE 3RD POLE

where VFB = 0.6V (typ) and VOUT_ is the output voltage (RFCF)-1 (RICI)-1 (RFCCF)-1

2ND ZERO

of the regulator. (R1CI)-1

Type III: Compensation when fCO < fESR

Figure 6b. Type III Compensation Network Response

As indicated above, the position of the output capaci-

tor’s inherent ESR zero is critical in designing an appro- fP1 introduces a pole at zero frequency (integrator) for

priate compensation network. When low-ESR ceramic nulling DC output voltage errors.

output capacitors (MLCCs) are used, the ESR zero fre- fP1= at the origin (0Hz)

quency (fESR) is usually much higher than the desired

crossover frequency (fCO). In this case, a type III com- Depending on the location of the ESR zero (fESR), fP2

pensation network is recommended (see Figure 6a). can be used to cancel it, or to provide additional atten-

uation of the high-frequency output ripple.

As shown in Figure 6b, the Type III compensation net-

work introduces two zeros and three poles into the con- 1

trol loop. The error amplifier has a low-frequency pole fP2 =

2π × RI × CI

at the origin, two zeros, and two higher frequency poles

at the following frequencies: fP3 attenuates the high-frequency output ripple.

1 1

1 fP3 = =

fZ1 =

2π × R F × C F (

2π × RF × CF CCF ) C × CCF

2π × R F × F

CF + CCF

1

fZ2 =

2π × CI × (R1 + RI ) Since CCF << CF then:

Two midband zeros (fZ1 and fZ2) are designed to com- 1

fP3 =

pensate for the pair of complex poles introduced by the 2π × RF × CCF

LC filter.

www.maximintegrated.com Maxim Integrated | 18

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

The locations of the zeros and poles should be such Solving for CI:

that the phase margin peaks around fCO.

Set the ratios of fCO-to-fZ and fP-to-fCO equal to one anoth-

CI [pF] =

(2π × fCO [kHz] × L[μH] × COUT [μF])

er, e.g., fCO = fP = 5 is a good number to get approximately 4 × RF [kΩ]

fZ fCO

60° of phase margin at fCO. Whichever technique, it is 6) For those situations where fLC < fCO < fESR < fSW/2,

important to place the two zeros at or below the double as with low-ESR tantalum capacitors, the compen-

pole to avoid the conditional stability issue. sator’s second pole (fP2) should be used to cancel

fESR. This provides additional phase margin. On the

The following procedure is recommended: system Bode plot, the loop gain maintains its

1) Select a crossover frequency, fCO, at or below one- +20dB/decade slope up to 1/2 of the switching fre-

tenth the switching frequency (fSW): quency verses flattening out soon after the 0dB

crossover. Then set:

f [kHz]

fCO [kHz] ≤ SW fP2 = fESR

10 If a ceramic capacitor is used, then the capacitor ESR

2) Calculate the LC double-pole frequency, fLC : zero, fESR, is likely to be located even above one-half of

the switching frequency, that is fLC < fCO < fSW/2 <

1 fESR. In this case, the frequency of the second pole

fLC [MHz] ≈

2π × L[μH] × COUT [μF] (fP2) should be placed high enough not to significantly

erode the phase margin at the crossover frequency.

where COUT is the output capacitor of the regulator. For example, fP2 can be set at 5 x fCO, so that its con-

3) Select the feedback resistor, RF, in the range of tribution to phase loss at the crossover frequency fCO is

only about 11°:

3.3kΩ to 30kΩ.

1 fP2 = 5 x fCO

4) Place the compensator’s first fZ1 =

zero at or below the output filter’s 2 π × R F × CF Once fP2 is known, calculate RI:

double-pole, fLC , as follows:

1

1 RI [kΩ] =

CF [μF] = 2π × fP2 [kHz] × CI [μF]

2π × RF [kΩ] × 0.5 × fLC [kHz]

5) The gain of the modulator (GainMOD)—comprised of 7) Place the second zero (fZ2) at 0.2 x fCO or at fLC,

the regulator’s pulse-width modulator, LC filter, whichever is lower, and calculate R1 using the fol-

lowing equation:

feedback divider, and associated circuitry—at the

crossover frequency is:

1

1 R1[kΩ] =

GainMOD = 4 × 2π × fZ2 [kHz] × CI [μF]

(2π × fCO [MHz])2 × L[μH] × COUT [μF]

8) Place the third pole (fP3) at 1/2 the switching fre-

The gain of the error amplifier (GainE/A) in midband fre- quency and calculate CCF from:

quencies is:

GainE/A = 2π × fCO [kHz] × CI [μF] × RF [kΩ] 1

CCF [nF] =

(2 π × 0.5 × fSW [MHz] × RF [kΩ])

The total loop gain is the product of the modulator gain

and the error amplifier gain at fCO should be equal to 1, 9) Calculate R2 as:

as follows:

GainMOD x GainE/A = 1 VFB [V]

R2 [kΩ] = R1[kΩ] ×

So: VOUT_ [V] − VFB [V]

1

4× where VFB = 0.6V (typ).

2

(2π × fCO [kHz]) × COUT [μF] × L[μH]

× 2π × fCO [kHz] × CI [pF] × RF [kΩ] = 1

www.maximintegrated.com Maxim Integrated | 19

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Applications Information 6) Place the bank of the output capacitors close to the

load.

PCB Layout Guidelines 7) Connect the MAX15021 exposed pad to a large

Careful PCB layout is critical to achieve clean and sta- copper plane to maximize its power dissipation

ble operation. Follow these guidelines for good PCB capability. Connect the exposed pad to SGND

layout: plane. Do not connect the exposed pad to the

1) Place decoupling capacitors as close as possible to SGND pin directly underneath the IC.

the IC pins. 8) Use 2oz. copper to keep trace inductance and

2) Keep SGND and PGND isolated and connect them resistance to a minimum. Thin copper PCBs can

at one single point close to the negative terminal of compromise efficiency since high currents are

the input filter capacitor. involved in the application. Also thicker copper con-

3) Route high-speed switching nodes away from sensi- ducts heat more effectively, thereby reducing ther-

tive analog areas (FB_, COMP_, and EN_). mal impedance.

4) Distribute the power components evenly across the 9) A reference PCB layout included in the MAX15021

board for proper heat dissipation. Evaluation Kit is also provided to further aid layout.

5) Ensure timing resistor and all feedback connections

are short and direct. Place feedback resistors as

close as possible to the IC.

www.maximintegrated.com Maxim Integrated | 20

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Typical Operating Circuits

VIN CI2

R1FB2

RI2

C1

R1

CF2 RF2

R2FB2

C2 CIN2 CDD2 CCF2

AVIN EN2 PVIN2 DVDD2 FB2 COMP2 L2

LX2 VOUT2

RS2

COUT2

CS2

PGND2

VIN

CDD1

DVDD1

EN1 VAVIN

VIN

CIN1

MAX15021

PVIN1

L1 VOUT1

LX1

RS1

COUT1

CS1

PGND1

CI1

R1FB1 R1EN2

RI1

FB1

RT SGND SEL COMP1

R2FB1 R2EN2

PGND SGND

VAVIN CF1 RF1

RT CT

CCF1

Figure 7. MAX15021 Double Buck with Tracking

www.maximintegrated.com Maxim Integrated | 21

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Typical Operating Circuits (continued)

VOUT1

VIN CI2

R1OUT2

RI2

C1

R1

CF2 RF2

R2OUT2

C2 CIN2 CDD2 CCF2

AVIN EN2 PVIN2 DVDD2 FB2 COMP2 L2

LX2 VOUT2

RS2

COUT2

CS2

PGND2

VIN

CDD1

DVDD1

EN1 VAVIN

VIN

CIN1

MAX15021

PVIN1

L1 VOUT1

LX1

RS1

COUT1

CS1

PGND1

CI1

R1OUT1

RI1

FB1

RT SGND SEL COMP1

R2OUT1

PGND SGND

CF1 RF1

RT CT

CCF1

Figure 8. MAX15021 Double Buck with Sequencing

www.maximintegrated.com Maxim Integrated | 22

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Chip Information Package Information

PROCESS: BiCMOS For the latest package outline information and land patterns (foot-

prints), go to www.maximintegrated.com/packages. Note that a

“+”, “#”, or “-” in the package code indicates RoHS status only.

Package drawings may show a different suffix character, but the

drawing pertains to the package regardless of RoHS status.

PACKAGE PACKAGE OUTLINE LAND

TYPE CODE NO. PATTERN NO.

28 TQFN-EP T2855+6 21-0140 90-0026

www.maximintegrated.com Maxim Integrated | 23

MAX15021 Dual, 4A/2A, 4MHz, Step-Down

DC-DC Regulator withTracking/

Sequencing Capability

Revision History

REVISION REVISION PAGES

DESCRIPTION

NUMBER DATE CHANGED

0 5/08 Initial release —

1 8/12 Added automotive qualified part to Ordering Information 1

2 4/15 Updated Benefits and Features section 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated’s website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent

licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and

max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc. © 2015 Maxim Integrated Products, Inc. | 24

You might also like

- REN Isl8121 DST 20060811Document26 pagesREN Isl8121 DST 20060811blackorgonNo ratings yet

- Cpnversor DC - DC MAX17113Document30 pagesCpnversor DC - DC MAX17113Antonio ChavezNo ratings yet

- Nxpusainc Mc33926pnb Datasheets 8993Document35 pagesNxpusainc Mc33926pnb Datasheets 8993Nooragha TanhaNo ratings yet

- Ultra-High Efficiency, Dual Step-Down Controller For Notebook ComputersDocument25 pagesUltra-High Efficiency, Dual Step-Down Controller For Notebook ComputersCarlos Henrique RibasNo ratings yet

- NCP81251 Single-Phase Voltage Regulator With SVID Interface For Computing ApplicationsDocument18 pagesNCP81251 Single-Phase Voltage Regulator With SVID Interface For Computing Applicationsankur rathiNo ratings yet

- Bicmos Advanced Phase-Shift PWM Controller: Features DescriptionDocument31 pagesBicmos Advanced Phase-Shift PWM Controller: Features DescriptionSaikumarNo ratings yet

- Datasheet PDFDocument16 pagesDatasheet PDFRaul LeonNo ratings yet

- Datasheet 4Document28 pagesDatasheet 4Kholit LitNo ratings yet

- Microchip Tech MCP1827S 5002E EB - C641174Document42 pagesMicrochip Tech MCP1827S 5002E EB - C641174prexo zoneNo ratings yet

- Max 1718Document35 pagesMax 1718Barton EletronicsNo ratings yet

- A05c 0S 000060 - Aoz2261nqi 11Document18 pagesA05c 0S 000060 - Aoz2261nqi 11Chiapin LeeNo ratings yet

- MAX1932 Digitally Controlled, 0.5% Accurate, Safest APD Bias SupplyDocument16 pagesMAX1932 Digitally Controlled, 0.5% Accurate, Safest APD Bias SupplyrodrigoelbarbaroNo ratings yet

- Programmable DC/DC Controller For Advanced Microprocessors: Device Package Temp Range (T)Document6 pagesProgrammable DC/DC Controller For Advanced Microprocessors: Device Package Temp Range (T)ibrahim başderNo ratings yet

- Max15058 PDFDocument22 pagesMax15058 PDFjhnkerenNo ratings yet

- Fixed-Frequency, Full-Bridge CCFL Inverter Controller: General Description FeaturesDocument27 pagesFixed-Frequency, Full-Bridge CCFL Inverter Controller: General Description FeaturesEduardo GNo ratings yet

- Max8901 Max8901bDocument14 pagesMax8901 Max8901bPM AlejandroNo ratings yet

- MAX2411ADocument14 pagesMAX2411AalperencoskunNo ratings yet

- MCP39F511A Data Sheet 20006044ADocument68 pagesMCP39F511A Data Sheet 20006044ALuis Enrique CorzoNo ratings yet

- Ultra-Low-Power, 10Msps, Dual 8-Bit ADC: General Description FeaturesDocument22 pagesUltra-Low-Power, 10Msps, Dual 8-Bit ADC: General Description FeaturesThomas ThomasNo ratings yet

- Dacmcp 4901Document51 pagesDacmcp 4901Ri Cha RdNo ratings yet

- Datasheet LTC3728L & LTC3728LX PDFDocument32 pagesDatasheet LTC3728L & LTC3728LX PDFSelmar CavalcantiNo ratings yet

- MAX2121BDocument20 pagesMAX2121BDavy SaNo ratings yet

- MAX1710Document28 pagesMAX1710Barton EletronicsNo ratings yet

- MAX2121Document19 pagesMAX2121Davy SaNo ratings yet

- High Performance, Triple-Output, Auto-Tracking Combo ControllerDocument15 pagesHigh Performance, Triple-Output, Auto-Tracking Combo ControllerrolandseNo ratings yet

- MCZ33399 Freescale SemiconductorDocument19 pagesMCZ33399 Freescale SemiconductorgoguNo ratings yet

- CLC5957 12-Bit, 70 MSPS Broadband Monolithic A/D Converter: General Description FeaturesDocument16 pagesCLC5957 12-Bit, 70 MSPS Broadband Monolithic A/D Converter: General Description FeaturesPeter SolyomNo ratings yet

- Max 17122Document35 pagesMax 17122master -DvNo ratings yet

- 1.5Mhz, 30A High-Efficiency, Led Driver With Rapid Led Current PulsingDocument25 pages1.5Mhz, 30A High-Efficiency, Led Driver With Rapid Led Current PulsingDummy CekNo ratings yet

- STF16N50M2Document22 pagesSTF16N50M2Fabio de FeoNo ratings yet

- 5.0 A Throttle Control H-BridgeDocument26 pages5.0 A Throttle Control H-Bridgerumellemur59No ratings yet

- Notebook CPU Step-Down Controller: General Description FeaturesDocument34 pagesNotebook CPU Step-Down Controller: General Description FeaturesCarlos Henrique RibasNo ratings yet

- A Data SheetDocument36 pagesA Data SheetThiago AlmeiNo ratings yet

- 10-Bit Digital-to-Analog Converter With Two-Wire Interface: Features General DescriptionDocument24 pages10-Bit Digital-to-Analog Converter With Two-Wire Interface: Features General DescriptionSergio MuriloNo ratings yet

- SC900Document23 pagesSC900Robert PNo ratings yet

- CMT2189A Datasheet-EN-V0.8-2020915Document67 pagesCMT2189A Datasheet-EN-V0.8-2020915Rudraksh GandharvaNo ratings yet

- Infineon ICE2PCS01 DataSheet v02 - 03 ENDocument19 pagesInfineon ICE2PCS01 DataSheet v02 - 03 ENАлексей АндрияшNo ratings yet

- Integrated High Power PoE-PD Interface & DC-DC Converter ControllerDocument18 pagesIntegrated High Power PoE-PD Interface & DC-DC Converter ControllerArun PadmanabhanNo ratings yet

- Max17122 45227Document36 pagesMax17122 45227MarcioAndradeNo ratings yet

- MP3391 r1.12Document18 pagesMP3391 r1.12Elsa Nababan EchaNo ratings yet

- MP3391Document18 pagesMP3391Raul AlfaroNo ratings yet

- Datasheet NCP81109Document28 pagesDatasheet NCP81109zigmund zigmundNo ratings yet

- Linkswitch-Tn2 Family DatasheetDocument28 pagesLinkswitch-Tn2 Family DatasheetManoel LemosNo ratings yet

- Single Intelligent High-Current Self-Protected Silicon High-Side Switch (2.0 MDocument24 pagesSingle Intelligent High-Current Self-Protected Silicon High-Side Switch (2.0 MElectronica Ave FenixNo ratings yet

- DC Converter With Low PassDocument38 pagesDC Converter With Low PassMuhammad Fikri Hidayat FikriNo ratings yet

- Dynamically Adjustable, Synchronous Step-Down Controller For Notebook CpusDocument33 pagesDynamically Adjustable, Synchronous Step-Down Controller For Notebook CpusCarlos Henrique RibasNo ratings yet

- HIP6302CBDocument18 pagesHIP6302CBrjbordaNo ratings yet

- Recommended FOR NEW Design: Dual Synchronous Buck Pseudo Fixed Frequency DDR Power Supply ControllerDocument17 pagesRecommended FOR NEW Design: Dual Synchronous Buck Pseudo Fixed Frequency DDR Power Supply ControllerCarlos AntonioNo ratings yet

- MCP1825 PDFDocument38 pagesMCP1825 PDFIoan TivgaNo ratings yet

- MCP1825/MCP1825S: 500 Ma, Low Voltage, Low Quiescent Current LDO RegulatorDocument39 pagesMCP1825/MCP1825S: 500 Ma, Low Voltage, Low Quiescent Current LDO RegulatorZireael EDNo ratings yet

- Ac MonitorDocument12 pagesAc MonitorMarcos Gabriel JudewiczNo ratings yet

- Ucc 2897 ADocument47 pagesUcc 2897 Akunjbihari golaNo ratings yet

- Ucc28c40, Ucc28c41, Ucc28c42, Ucc28c43, Ucc28c44, Ucc28c45 Ucc38c40, Ucc38c41, Ucc38c42, Ucc38c43, Ucc38c44, Ucc38c45Document32 pagesUcc28c40, Ucc28c41, Ucc28c42, Ucc28c43, Ucc28c44, Ucc28c45 Ucc38c40, Ucc38c41, Ucc38c42, Ucc38c43, Ucc38c44, Ucc38c45curz0% (1)

- Maxim Max8632Document29 pagesMaxim Max8632ERICO STRAMANDINOLINo ratings yet

- Max3948 3128856Document38 pagesMax3948 3128856Philippe Englert VelhaNo ratings yet

- mcp3911 3.3v Two Channel Analog Front End ds20002286dDocument74 pagesmcp3911 3.3v Two Channel Analog Front End ds20002286dJosueEspinozaNo ratings yet

- General Description Features: 28V/10A Synchronous Ezbuck RegulatorDocument15 pagesGeneral Description Features: 28V/10A Synchronous Ezbuck RegulatorРоман ІкалюкNo ratings yet

- ADP3188 AD Analog DevicesDocument28 pagesADP3188 AD Analog DevicesMohammad UsmanNo ratings yet

- Broatcom Acpl-798jDocument21 pagesBroatcom Acpl-798jJavier De La RosaNo ratings yet

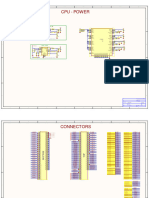

- SchematicDocument8 pagesSchematicPhong Phan CôngNo ratings yet

- FPGA Based Telemetry System For Meteorological Balloon InstrumentationDocument3 pagesFPGA Based Telemetry System For Meteorological Balloon InstrumentationPhong Phan CôngNo ratings yet

- FPGA Based Telemetry System For Meteorological Balloon InstrumentationDocument3 pagesFPGA Based Telemetry System For Meteorological Balloon InstrumentationPhong Phan CôngNo ratings yet

- Max1510 Max17510-3126819Document14 pagesMax1510 Max17510-3126819Phong Phan CôngNo ratings yet

- Energy Measuring Unit PDFDocument48 pagesEnergy Measuring Unit PDFhuynh ngoc hoi HuynhNo ratings yet

- Apctest OutputDocument11 pagesApctest Outputgybmllpusaqyzwgovs nthrw.comNo ratings yet

- Utilitech PQS45UT 500-Watt Portable Work Light ManualDocument20 pagesUtilitech PQS45UT 500-Watt Portable Work Light ManualMatthew LeingangNo ratings yet

- Measurement Systems Block DiagramDocument3 pagesMeasurement Systems Block Diagramchiranjib_kNo ratings yet

- Design and Implementation of GSM Based Automation of Household AppliancesDocument7 pagesDesign and Implementation of GSM Based Automation of Household Appliancesnur ain natasyaNo ratings yet

- 200A, 15 KV Class Loadbreak Rotatable Feed Thru Insert: 15-LFTI200Document3 pages200A, 15 KV Class Loadbreak Rotatable Feed Thru Insert: 15-LFTI200Diego AlvesNo ratings yet

- Ed - 2Document54 pagesEd - 2JaiNo ratings yet

- ASUS X540SC - Repair GuideDocument5 pagesASUS X540SC - Repair GuideИван ТопчуNo ratings yet

- Propagation Delay: Fan-InDocument3 pagesPropagation Delay: Fan-InRutu ThakkarNo ratings yet

- Electronics: A Review On Small Power Rating PV Inverter Topologies and Smart PV InvertersDocument26 pagesElectronics: A Review On Small Power Rating PV Inverter Topologies and Smart PV InvertersPadmavathi RNo ratings yet

- UX FOB HVComponentAssociatesDocument1 pageUX FOB HVComponentAssociatesCường MchwNo ratings yet

- SM Tec8300Document90 pagesSM Tec8300m.torresNo ratings yet

- Lighting Lighting: HID-Basic Semi-Parallel Ballasts For SON/CDM/MH LampsDocument2 pagesLighting Lighting: HID-Basic Semi-Parallel Ballasts For SON/CDM/MH LampsNestor Fortunato Lopez VargasNo ratings yet

- BombasDocument11 pagesBombasRolan PonceNo ratings yet

- Prospekt 20469-AEN 006Document12 pagesProspekt 20469-AEN 006MarcoNo ratings yet

- General-Purpose Switching Device Applications: N-Channel Silicon MOSFETDocument4 pagesGeneral-Purpose Switching Device Applications: N-Channel Silicon MOSFETjose luisNo ratings yet

- Service Manual: KDL-V32XBR2 KDL-V32XBR2Document75 pagesService Manual: KDL-V32XBR2 KDL-V32XBR2aquiles armandoNo ratings yet

- Commercial Mode Setup Guide: 29LY570H 32LY570H 39LY570H 42LY570H 47LY570H 55LY570H 65LY570HDocument72 pagesCommercial Mode Setup Guide: 29LY570H 32LY570H 39LY570H 42LY570H 47LY570H 55LY570H 65LY570HKevNo ratings yet

- Section 12 - Optional Class Exercise: Peer-to-Peer CommunicationsDocument15 pagesSection 12 - Optional Class Exercise: Peer-to-Peer CommunicationsBouazzaNo ratings yet

- HY5118164B, HY5116164B: DescriptionDocument8 pagesHY5118164B, HY5116164B: Descriptiontolomeo10No ratings yet

- What Causes Cables To Get Heated Up and Melt in A Circuit?Document6 pagesWhat Causes Cables To Get Heated Up and Melt in A Circuit?Fawaaz KhurwolahNo ratings yet

- Kri PDFDocument5 pagesKri PDFKrishna aug13No ratings yet

- MT6795 Android ScatterDocument8 pagesMT6795 Android ScatterHuzaifa JabbarNo ratings yet

- Microprocessors I Laboratory (MP Lab)Document4 pagesMicroprocessors I Laboratory (MP Lab)MamounNo ratings yet

- Oper For Cooling UnitDocument32 pagesOper For Cooling Unitsourabh naikyaNo ratings yet

- 2300 - Series Vibration Monitors Keyphasors Datasheet - With Hookup 105M0340Document24 pages2300 - Series Vibration Monitors Keyphasors Datasheet - With Hookup 105M0340soumya voraNo ratings yet

- RF Systems Both PartsDocument124 pagesRF Systems Both PartsJonathan CuroleNo ratings yet

- Fanuc System 10 and Series 11 Master Board Alarm CodesDocument2 pagesFanuc System 10 and Series 11 Master Board Alarm CodesLeonardusNo ratings yet

- Application of Network Theorems To Ac CircuitsDocument10 pagesApplication of Network Theorems To Ac CircuitsnivonasNo ratings yet

- Evaluates: MAX30110 and MAX30112 MAX30110 Evaluation Kit: General Description Quick StartDocument27 pagesEvaluates: MAX30110 and MAX30112 MAX30110 Evaluation Kit: General Description Quick StartVenkatesh KamathNo ratings yet