Professional Documents

Culture Documents

MAX2121B

Uploaded by

Davy SaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MAX2121B

Uploaded by

Davy SaCopyright:

Available Formats

EVALUATION KIT AVAILABLE

MAX2121B L-Band Tuner with Programmable

Baseband Filter

General Description Benefits and Features

The MAX2121B low-cost, direct-conversion tuner IC is ●● Monolithic Receiver Saves Cost and Space

designed for satellite set-top and VSAT applications. • Integrated VCO with Low Phase Noise: -97dBc/Hz

The device directly converts the satellite signals from the at 10kHz

LNB to baseband using a broadband I/Q downconverter. • Integrated 14-Bit Fractional-N Synthesizer

The operating frequency range extends from 925MHz to • Address Pin Allows for Multi-Tuner Applications

2250MHz. ●● Low Power Reduces Cost

The device includes an LNA and an RF variable-gain ampli- • 495mW Power Dissipation

fier, I and Q downconverting mixers, and digitally controlled • 10mW Standby Mode

baseband filters (40MHz to 124MHz) and variable-gain ●● High Dynamic Range Eliminates Need for External

amplifiers. Together, the RF and baseband variable-gain LNA and/or Attenuators

amplifiers provide more than 80dB of gain control range. • -75dBm to 0dBm Input Power

The device includes fully monolithic VCOs, as well as a • 8dB Noise Figure

complete fractional-N frequency synthesizer. Additionally, ●● Integrated LP Filters Simplify Design

an on-chip crystal oscillator is provided along with a buff- • Programmable Bandwidth from 40MHz to 124MHz

ered output for driving additional tuners and demodula- ●● Differential I/Q Interface Minimizes EMI

tors. Synthesizer programming and device configuration • 1VP-P Full-Scale Outputs

are accomplished with a 2-wire serial interface. The IC

features a VCO autoselect (VAS) function that automati- ●● Serial Interface and Small Package Reduce Size

cally selects the proper VCO. For multituner applications, • 5mm x 5mm, 28-Pin TQFN Package

the device can be configured to have one of two 2-wire • I2C 2-Wire Serial Interface

interface addresses. A low-power standby mode is avail-

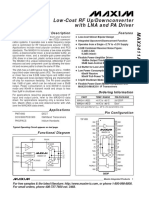

able whereupon the signal path is shut down while leaving Functional Diagram

the reference oscillator, digital interface, and buffer cir-

cuits active, providing a method to reduce power in single

VCC_BB

ADDR

QDC+

QDC-

IDC-

SCL

SDA

and multituner applications.

28 27 26 25 24 23 22

The device is the most advanced broadband/VSAT DBS +

VCC_RF2 1 21 IDC+

tuner available. The low noise figure eliminates the need INTERFACE LOGIC

DC OFFSET

CORRECTION

for an external LNA. A small number of passive compo- AND CONTROL MAX2121B

VCC_RF1 2 20 IOUT-

nents are needed to form a complete broadband satellite

tuner DVB-S2 RF front-end solution. The tuner is avail-

GND 3 19 IOUT+

able in a very small, 5mm x 5mm, 28-pin TQFN package.

Applications RFIN 4 18 QOUT-

●● VSATs GC1 5 17 QOUT+

●● Navigation Systems FREQUENCY

DIV2/DIV4

●● Satellite Set-Top Box VCC_LO 6

SYNTHESIZER

16 VCC_DIG

EP

●● DBS Tuner

VCC_VCO 7 15 REFOUT

Ordering Information appears at end of data sheet. 8 9 10 11 12 13 14

BYPVCO

TUNEVCO

GNDTUNE

GNDSYN

CPOUT

VCC_SYN

XTAL

19-7601; Rev 1; 9/16

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Absolute Maximum Ratings

VCC_ to GND.........................................................-0.3V to +3.9V Operating Temperature Range..............................-40°C to +85°C

All Other Pins to GND.................................-0.3V to (VCC + 0.3V) Junction Temperature.......................................................+150°C

RF Input Power: RFIN.....................................................+10dBm Storage Temperature Range...............................-65°C to +160°C

BYPVCO, CPOUT, XTAL, REFOUT, IOUT_, QOUT_, IDC_, Lead Temperature (soldering, 10s)...................................+300°C

QDC_ to GND Short-Circuit Protection...............................10s Soldering Temperature (reflow)........................................+260°C

Continuous Power Dissipation (TA = +70°C)

TQFN (derate 34.5mW/°C above +70°C)......................2.75W

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these

or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

device reliability.

CAUTION! ESD SENSITIVE DEVICE

DC Electrical Characteristics

(MAX2121 Evaluation Kit: VCC_ = +3.13V to +3.47V, fXTAL = 27MHz, TA = -40°C to +85°C, VGC1 = +0.5V (max gain), default register

settings except BBG[3:0] = 1011, LPF[7:0] =97h. No input signals at RF, baseband I/Os are open circuited. Typical values measured

at VCC = +3.3V, TA = +25°C, unless otherwise noted.) (Note 1)

PARAMETER CONDITIONS MIN TYP MAX UNITS

SUPPLY

Supply Voltage (VCC_) 3.13 3.3 3.47 V

Receive mode, bit STBY = 0 148 200

Supply Current mA

Standby mode, bit STBY = 1 3

ADDRESS SELECT INPUT (ADDR)

Digital Input-Voltage High, VIH 2.4 V

Digital Input-Voltage Low, VIL 0.5 V

Digital Input-Current High, IIH 50 µA

Digital Input-Current Low, IIL -50 µA

ANALOG GAIN-CONTROL INPUT (GC1)

Input Voltage Range Maximum gain = 0.5V 0.5 2.7 V

Input Bias Current -50 +50 µA

VCO TUNING VOLTAGE INPUT (TUNEVCO)

Input Voltage Range 0.4 2.3 V

2-WIRE SERIAL INPUTS (SCL, SDA)

Clock Frequency 400 kHz

0.7 x

Input Logic-Level High V

VCC

0.3 x

Input Logic-Level Low V

VCC

Input Leakage Current Digital inputs = GND or VCC ±0.1 ±1 µA

2-WIRE SERIAL OUTPUT (SDA)

Output Logic-Level Low ISINK = 1mA (Note 2) 0.4 V

www.maximintegrated.com Maxim Integrated │ 2

MAX2121B L-Band Tuner with Programmable

Baseband Filter

AC Electrical Characteristics

(MAX2121 Evaluation Kit: VCC_ = +3.13V to +3.47V, fXTAL = 27MHz, TA = -40°C to +85°C, default register settings except BBG[3:0] = 1111,

LPF[7:0] = 97h. Typical values measured at VCC = +3.3V, TA = +25°C, unless otherwise noted.) (Note 1)

PARAMETER CONDITIONS MIN TYP MAX UNITS

MAIN SIGNAL PATH PERFORMANCE

Minimum Gain fIN = 2175MHz 72 78 dB

Gain Flatness 925MHz to 2250MHz (Note 2) 4 6 dB

Input Frequency Range (Note 3) 925 2250 MHz

RF Gain-Control Range (GC1) 0.5V < VGC1 < 2.7V 65 73 dB

Baseband Gain-Control Range Bits BBG[3:0] = 1111 to 0000 11.5 13.5 dB

In-Band Input IP3 (Note 4) +2 dBm

Out-of-Band Input IP3 (Note 5) +15 dBm

Input IP2 (Note 6) +40 dBm

VGC1 is set to 0.5V (maximum RF gain) and BBG[3:0] is

adjusted to give a 1VP-P baseband output level for a 8

Noise Figure -75dBm CW input tone at 1500MHz dB

Starting with the same BBG[3:0] setting as above, VGC1

9 12

is adjusted to back off RF gain by 10dB (Note 2)

Minimum RF Input Return Loss 925MHz < fRF < 2175MHz, in 75Ω system 12 dB

BASEBAND OUTPUT CHARACTERISTICS

Nominal Output Voltage Swing RLOAD = 200Ω//5pF 0.5 1 VP-P

I/Q Amplitude Imbalance Measured at 500kHz ±1 dB

I/Q Quadrature Phase Imbalance Measured at 500kHz 3.5 Degrees

Single-Ended I/Q Output

Real ZO, from 1MHz to 140MHz 24 Ω

Impedance

Output 1dB Compression Voltage Differential 3 VP-P

Baseband Highpass -3dB

47nF capacitors at IDC_, QDC_ 400 Hz

Frequency Corner

BASEBAND LOWPASS FILTERS (5th-Order Butterworth with 1st-Order Group Delay Compensation)

Typical Filter Bandwidth Range

LPF[7:0] = 2Eh to 97h 40 124 MHz

(-3dB)

Rejection Ratio At 247.5MHz, LPF[7:0] = 97h 31 dB

Group Delay Up to 0.5dB bandwidth 1.0 ns

3dB Bandwidth Tolerance ±10 %

FREQUENCY SYNTHESIZER

RF-Divider Frequency Range 925 2175 MHz

RF-Divider Range (N) 19 251

Reference-Divider Frequency Range 12 30 MHz

Reference-Divider Range (R) 1 1

Phase-Detector Comparison

12 30 MHz

Frequency

www.maximintegrated.com Maxim Integrated │ 3

MAX2121B L-Band Tuner with Programmable

Baseband Filter

AC Electrical Characteristics (continued)

(MAX2121 Evaluation Kit: VCC_ = +3.13V to +3.47V, fXTAL = 27MHz, TA = -40°C to +85°C, default register settings except BBG[3:0] = 1111,

LPF[7:0] = 97h. Typical values measured at VCC = +3.3V, TA = +25°C, unless otherwise noted.) (Note 1)

PARAMETER CONDITIONS MIN TYP MAX UNITS

VOLTAGE-CONTROLLED OSCILLATOR AND LO GENERATION

Guaranteed LO Frequency Range 925 2250 MHz

fOFFSET = 10kHz -97

LO Phase Noise fOFFSET = 100kHz -100 dBc/Hz

fOFFSET = 1MHz -122

XTAL/REFERENCE OSCILLATOR INPUT AND OUTPUT BUFFER

XTAL Oscillator Frequency

Parallel-resonance-mode crystal (Note 7) 12 30 MHz

Range fXTAL

Input Overdrive Level AC-coupled sine-wave input 0.5 1 2.0 VP-P

XTAL Output-Buffer Divider Range 1 8 —

XTAL Output Voltage Swing 12MHz to 30MHz, CLOAD = 10pF 1 1.5 2 VP-P

XTAL Output Duty Cycle 50 %

Note 1: Min/max values are production tested at TA = +25°C. Min/max limits at TA = -40°C and TA = +85°C are guaranteed by

design and characterization.

Note 2: Guaranteed by design and characterization at TA = +25°C.

Note 3: Input gain range specifications met over this band.

Note 4: In-band IIP3 test conditions: GC1 set to provide the nominal baseband output drive when mixing down a -23dBm tone at

2175MHz to 5MHz baseband (fLO = 2170MHz). Baseband gain is set to its default value (BBG[3:0] = 1011). Two tones at

-26dBm each are applied at 2174MHz and 2175MHz. The IM3 tone at 3MHz is measured at baseband, but is referred to

the RF input.

Note 5: Out-of-band IIP3 test conditions: GC1 set to provide nominal baseband output drive when mixing down a -23dBm tone at

2175MHz to 5MHz baseband (fLO = 2170MHz). Baseband gain is set to its default value (BBG[3:0] = 1011). Two tones at

-20dBm each are applied at 1919MHz and 1663MHz. The IM3 tone at 5MHz is measured at baseband, but is referred to

the RF input.

Note 6: Input IP2 test conditions: GC1 set to provide nominal baseband output drive when mixing down a -23dBm tone at 2175MHz

to 5MHz baseband (fLO = 2170MHz). Baseband gain is set to its default value (BBG[3:0] = 1011). Two tones at -20dBm

each are applied at 925MHz and 1250MHz. The IM2 tone at 5MHz is measured at baseband, but is referred to the RF input.

Note 7: See Table 16 for crystal ESR requirements.

www.maximintegrated.com Maxim Integrated │ 4

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Typical Operating Characteristics

(MAX2121 Evaluation Kit: VCC = +3.3V, TA = +25°C, baseband output frequency = 5MHz, VGC1 = +1.2V, default register settings except

BBG[3:0] = 1011, LPF[7:0] = 97h, unless otherwise noted.)

STANDBY SUPPLY CURRENT

SUPPLY CURRENT vs. SUPPLY VOLTAGE SUPPLY CURRENT vs. LPF[7:0] vs. SUPPLY VOLTAGE

toc01a

175 150 3.0

MAX2121 toc01

MAX2121 toc02

170 TA = +85°C

STANDBY SUPPLY CURRENT (mA)

145

165

2.5

SUPPLY CURRENT (mA)

160

SUPPLY CURRENT (mA)

140

155 TA = +85°C

TA = +25°C

150 135 2.0

145

130

140 TA = -40°C

TA = -40°C 1.5

135 125

130

125 120 1.0

3.1 3.2 3.3 3.4 3.5 46 62 78 94 110 126 142 158 3.1 3.2 3.3 3.4 3.5

SUPPLY VOLTAGE (V) LPF[7:0] (DECIMAL) SUPPLY VOLTAGE (V)

QUADRATURE PHASE ERROR QUADRATURE MAGNITUDE MATCHING

HD3 vs. VOUT vs. LO FREQUENCY vs. LO FREQUENCY

-10 3.5 1.0

MAX2121 toc04

MAX2121 toc05

MAX2121 toc03

fBASEBAND = 50MHz QUADRATURE MAGNITUDE MATCHING (dB) fBASEBAND = 50MHz

BASEBAND 3RD-ORDER HARMONIC (dBc)

-15

QUADRATURE PHASE ERROR (DEG)

3.0

-20 0.8

-25 2.5

-30 0.6 TA = +25°C

2.0 TA = -40°C

-35

1.5

-40 0.4

-45 1.0 TA = -40°C

TA = +85°C

-50 TA = +85°C 0.2

0.5 TA = +25°C

-55

-60 0 0

1.0 1.5 2.0 2.5 3.0 900 1150 1400 1650 1900 2150 900 1150 1400 1650 1900 2150

VOUT (VP-P) LO FREQUENCY (MHz) LO FREQUENCY (MHz)

QUADRATURE PHASE ERROR QUADRATURE MAGNITUDE MATCHING BASEBAND FILTER FREQUENCY

vs. BASEBAND FREQUENCY vs. BASEBAND FREQUENCY RESPONSE

3.5 1.0 0

MAX2121 toc06

toc08

MAX2121 toc07

fLO = 1425MHz

QUADRATURE MAGNITUDE MATCHING (dB)

fLO = 1425MHz

QUADRATURE PHASE ERROR (DEG)

3.0 -5

TA = -40°C 0.8

BASEBAND OUTPUT LEVEL (dB)

2.5 -10

TA = +85°C

0.6 TA = +25°C -15

2.0

-20

1.5 TA = +25°C

0.4 -25

1.0 LPF=151d

TA = +85°C -30

0.2

0.5 -35

TA = -40°C LPF=46d LPF=84d LPF=121d

0 0 -40

0.1 1 10 100 0.1 1 10 100 0 50 100 150 200 250 300

BASEBAND FREQUENCY (MHz) BASEBAND FREQUENCY (MHz) BASEBAND FREQUENCY (MHz)

www.maximintegrated.com Maxim Integrated │ 5

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Typical Operating Characteristics (continued)

(MAX2121 Evaluation Kit: VCC = +3.3V, TA = +25°C, baseband output frequency = 5MHz, VGC1 = +1.2V, default register settings except

BBG[3:0] = 1011, LPF[7:0] = 97h, unless otherwise noted.)

BASEBAND FILTER 3dB FREQUENCY LOWPASS FILTER 3dB FREQUENCY

BASEBAND FILTER FREQUENCY RESPONSE vs. TEMPERATURE vs. LPF[7:0] toc10a

1 1.00 130

MAX2121 toc09

MAX2121 toc10

0 NORMALIZED AT TA = +25°C

BASEBAND GAIN ERROR AT f-3dB (dB)

0.75 120

BASEBAND OUTPUT LEVEL (dB)

-1

110

-2 0.50

-3dB BANDWIDTH (MHz)

100

-3 0.25

-4 90

0

-5 TA = +25°C 80

-6 -0.25

70

-7

-0.50 60

-8

-0.75 50

-9

-10 -1.00 40

0 25 50 75 100 125 150 -40 -20 0 20 40 60 80 46 62 78 94 110 126 142 158

BASEBAND FREQUENCY (MHz) TEMPERATURE (°C) LPF[7:0] (DECIMAL)

BASEBAND FILTER HIGHPASS NOISE FIGURE vs. LO FREQUENCY

FREQUENCY RESPONSE VOLTAGE GAIN vs. VGC1 (TA = +25°C)

0 80 11.0

MAX2121 toc13

MAX2121 toc12

MAX2121 toc11

-1 70 10.5 ADJUST BBG[3:0] FOR 1VP-P

BASEBAND OUTPUT LEVEL (dB)

-2 BBG[3:0] = 1111 BASEBAND OUTPUT WITH

60 10.0 PIN = -75dBm AND VGC1 = 0.5V

-3

VOLTAGE GAIN (dB)

NOISE FIGURE (dB)

50 9.5

-4

-5 40 9.0 10dB BACKED OFF GAIN

-6 30 8.5

-7

20 8.0

-8

-9 10 7.5

-10 0 7.0

100 1000 10,000 0 0.5 1.0 1.5 2.0 2.5 3.0 900 1150 1400 1650 1900 2150

BASEBAND FREQUENCY (Hz) VGC1 (V) LO FREQUENCY (MHz)

NOISE FIGURE vs. INPUT POWER OUT-OF-BAND IIP3 vs. INPUT POWER IN-BAND IIP3 vs. INPUT POWER

35 30 20

MAX2121 toc16

MAX2121 toc14

MAX2121 toc15

ADJUST BBG[3:0] for 1VP-P SEE NOTE 5 ON PAGE 4 FOR SEE NOTE 4 ON PAGE 4 FOR

BASEBAND OUTPUT WITH PIN = -75dBm CONDITIONS 10 CONDITIONS

30 AND VGC1 = -0.5V, fLO = 1500MHz 20

0

OUT-OF-BAND IIP3 (dBm)

NOISE FIGURE (dB)

IN-BAND IIP3 (dBm)

25 10

-10

20 0 -20

-30

15 -10

-40

10 -20

-50

5 -30 -60

-75 -65 -55 -45 -35 -75 -65 -55 -45 -35 -25 -15 -5 -75 -65 -55 -45 -35 -25 -15 -5

INPUT POWER (dBm) INPUT POWER (dBm) INPUT POWER (dBm)

www.maximintegrated.com Maxim Integrated │ 6

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Typical Operating Characteristics (continued)

(MAX2121 Evaluation Kit: VCC = +3.3V, TA = +25°C, baseband output frequency = 5MHz, VGC1 = +1.2V, default register settings except

BBG[3:0] = 1011, LPF[7:0] = 97h, unless otherwise noted.)

IIP2 vs. INPUT POWER INPUT RETURN LOSS vs. FREQUENCY

40 0

MAX2121 toc18

MAX2121 toc17

SEE NOTE 6 ON PAGE 4

35 FOR CONDITIONS

30 -5

INPUT RETURN LOSS (dB)

25

VGC1 = 0.5V

20 -10

IIP2 (dBm)

15

10 -15

5

0 -20

-5

VGC1 = 2.7V

-10 -25

-75 -65 -55 -45 -35 -25 -15 -5 900 1125 1350 1575 1800 2025 2052

INPUT POWER (dBm) FREQUENCY (MHz)

PHASE NOISE AT 10kHz OFFSET vs.

CHANNEL FREQUENCY PHASE NOISE vs. OFFSET FREQUENCY

-90 -90

MAX2121 toc19

MAX2121 toc20

PHASE NOISE AT 10kHz OFFSET (dBc/Hz)

-100

PHASE NOISE (dBc/Hz)

-95

-110

-100

-120

fLO = 1800MHz

-105 -130

925 1115 1305 1495 1685 1875 2065 2255 1.0E+03 1.0E+04 1.0E+05 1.0E+06

CHANNEL FREQUENCY (MHz) OFFSET FREQUENCY (Hz)

LO LEAKAGE vs. LO FREQUENCY VCO: KV vs. VTUNE

-70 450

MAX2121 toc22

MAX2121 toc21

MEASURED AT RF INPUT

400

350 SUB-BAND 23

-75

LO LEAKAGE (dBm)

300

KV (MHz/V)

250

-80

200 SUB-BAND 12

150

-85 100

50 SUB-BAND 0

-90 0

925 1175 1425 1675 1925 2175 0 0.5 1.0 1.5 2.0 2.5 3.0

LO FREQUENCY (MHz) VTUNE (V)

www.maximintegrated.com Maxim Integrated │ 7

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Pin Configuration

VCC_BB

ADDR

QDC+

TOP VIEW

QDC-

IDC-

SCL

SDA

28 27 26 25 24 23 22

VCC_RF2 1 21 IDC+

+

VCC_RF1 2 20 IOUT-

GND 3 19 IOUT+

MAX2121B

RFIN 4 18 QOUT-

GC1 5 17 QOUT+

VCC_LO 6 16 VCC_DIG

EP

VCC_VCO 7 15 REFOUT

8 9 10 11 12 13 14

BYPVCO

TUNEVCO

GNDTUNE

GNDSYN

CPOUT

VCC_SYN

XTAL

TQFN

(5mm x 5mm)

Pin Description

PIN NAME FUNCTION

DC Power Supply for LNA. Connect to a +3.3V low-noise supply. Bypass to GND with a 1nF capacitor

1 VCC_RF2

connected as close as possible to the pin. Do not share capacitor ground vias with other ground connections.

DC Power Supply for LNA. Connect to a +3.3V low-noise supply. Bypass to GND with a 1nF capacitor

2 VCC_RF1

connected as close as possible to the pin. Do not share capacitor ground vias with other ground connections.

3 GND Ground. Connect to board’s ground plane for proper operation.

4 RFIN Wideband 75Ω RF Input. Connect to an RF source through a DC-blocking capacitor.

RF Gain-Control Input. High-impedance analog input with a 0.5V to 2.7V operating range.

5 GC1

VGC1 = 0.5V corresponds to the maximum gain setting.

DC Power Supply for LO Generation Circuits. Connect to a +3.3V low-noise supply. Bypass to GND with

6 VCC_LO a 1nF capacitor connected as close as possible to the pin. Do not share capacitor ground vias with other

ground connections.

DC Power Supply for VCO Circuits. Connect to a +3.3V low-noise supply. Bypass to GND with a 1nF

7 VCC_VCO capacitor connected as close as possible to the pin. Do not share capacitor ground vias with other ground

connections.

www.maximintegrated.com Maxim Integrated │ 8

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Pin Description (continued)

PIN NAME FUNCTION

Internal VCO Bias Bypass. Bypass to GND with a 100nF capacitor connected as close as possible to the pin.

8 BYPVCO

Do not share capacitor ground vias with other ground connections.

High-Impedance VCO Tune Input. Connect the PLL loop filter output directly to this pin with as short of a

9 TUNEVCO

connection as possible.

10 GNDTUNE Ground for TUNEVCO. Connect to the PCB ground plane.

11 GNDSYN Ground for Synthesizer. Connect to the PCB ground plane.

Charge-Pump Output. Connect this output to the PLL loop filter input with the shortest connection

12 CPOUT

possible.

DC Power Supply for Synthesizer Circuits. Connect to a +3.3V low-noise supply. Bypass to GND with a 1nF

13 VCC_SYN capacitor connected as close as possible to the pin. Do not share capacitor ground vias with other ground

connections.

Crystal-Oscillator Interface. Use with an external parallel-resonance-mode crystal through a series 1nF

14 XTAL

capacitor. See the Typical Application Circuit.

15 REFOUT Crystal-Oscillator Buffer Output. A DC-blocking capacitor must be used when driving external circuitry.

DC Power Supply for Digital Logic Circuits. Connect to a +3.3V low-noise supply. Bypass to GND with a 1nF

16 VCC_DIG capacitor connected as close as possible to the pin. Do not share capacitor ground vias with other ground

connections.

17 QOUT+

Quadrature Baseband Differential Output. AC-couple with 47nF capacitors to the demodulator input.

18 QOUT-

19 IOUT+

In-Phase Baseband Differential Output. AC-couple with 47nF capacitors to the demodulator input.

20 IOUT-

21 IDC+

I-Channel Baseband DC Offset Correction. Connect a 47nF ceramic chip capacitor from IDC- to IDC+.

22 IDC-

23 QDC+

Q-Channel Baseband DC Offset Correction. Connect a 47nF ceramic chip capacitor from QDC- to QDC+.

24 QDC-

DC Power Supply for Baseband Circuits. Connect to a +3.3V low-noise supply. Bypass to GND with

25 VCC_BB a 1nF capacitor connected as close as possible to the pin. Do not share capacitor ground vias with other

ground connections.

26 SDA 2-Wire Serial-Data Interface. Requires ≥ 1kΩ pullup resistor to VCC.

27 SCL 2-Wire Serial-Clock Interface. Requires ≥ 1kΩ pullup resistor to VCC.

28 ADDR Address. Must be connected to either ground (logic 0) or supply (logic 1).

— EP Exposed Pad. Solder evenly to the board’s ground plane for proper operation.

www.maximintegrated.com Maxim Integrated │ 9

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Detailed Description each bit name and the bit usage information for all regis-

ters. Note that all registers must be written after and no

Register Description earlier than 100μs after the device is powered up. The

The MAX2121B includes 12 user-programmable registers VCO autoselection circuit is triggered by writing to register

and two read-only registers. See Table 1 for register con- 5. Thus register 5 should be the last register to be written

figurations. The register configuration of Table 1 shows in order to ensure proper PLL lock.

Table 1. Register Configuration

MSB LSB

REG REGISTER READ/ REG

DATA BYTE

NUMBER NAME WRITE ADDRESS

D[7] D[6] D[5] D[4] D[3] D[2] D[1] D[0]

N-Divider FRAC

1 Write 0x00 N[14] N[13] N[12] N[11] N[10] N[9] N[8]

MSB 1

N-Divider

2 Write 0x01 N[7] N[6] N[5] N[4] N[3] N[2] N[1] N[0]

LSB

Charge CPMP[1] CPMP[0] CPLIN[1] CPLIN[0]

3 Write 0x02 F[19] F[18] F[17] F[16]

Pump 0 0 0 1

F-Divider

4 Write 0x03 F[15] F[14] F[13] F[12] F[11] F[10] F[9] F[8]

MSB

F-Divider

5 Write 0x04 F[7] F[6] F[5] F[4] F[3] F[2] F[1] F[0]

LSB

XTAL

Buffer and

6 Write 0x05 XD[2] XD[1] XD[0] R[4] R[3] R[2] R[1] R[0]

Reference

Divider

7 PLL Write 0x06 D24 CPS ICP X X X X X

8 VCO Write 0x07 VCO[4] VCO[3] VCO[2] VCO[1] VCO[0] VAS ADL ADE

Lowpass

9 Write 0x08 LPF[7] LPF[6] LPF[5] LPF[4] LPF[3] LPF[2] LPF[1] LPF[0]

Filter

PWDN

10 Control Write 0x09 STBY X X BBG[3] BBG[2] BBG[1] BBG[0]

0

PLL DIV VCO BB RFMIX RFVGA FE

11 Shutdown Write 0x0A X

0 0 0 0 0 0 0

LD LD LD

CPTST[2] CPTST[1] CPTST[0] TURBO

12 Test Write 0x0B X MUX[2] MUX[1] MUX[0]

0 0 0 1

0 0 0

Status

13 Read 0x0C POR VASA VASE LD X X X X

Byte-1

Status

14 Read 0x0D VCOSBR[4] VCOSBR[3] VCOSBR[2] VCOSBR[1] VCOSBR[0] ADC[2] ADC[1] ADC[0]

Byte-2

X = Don’t care. 0 = Set to 0 for factory-tested operation. 1 = Set to 1 for factory-tested operation.

www.maximintegrated.com Maxim Integrated │ 10

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Table 2. N-Divider MSB Register (Address: 0x00)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

FRAC 7 1 Users must program to 1 upon powering up the device.

Sets the most significant bits of the PLL integer-divide number (N). N can

N[14:8] 6–0 0000000

range from 19 to 251.

Table 3. N-Divider LSB Register (Address: 0x01)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

Sets the least significant bits of the PLL integer-divide number. N can

N[7:0] 7–0 00100011

range from 19 to 251.

Table 4. Charge-Pump Register (Address: 0x02)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

Charge-pump minimum pulse width. Users must program to 00 upon

CPMP[1:0] 7–6 00

powering up the device.

Controls charge-pump linearity. Users must program to 01 upon powering

CPLIN[1:0] 5–4 00

up the device.

Sets the 4 most significant bits of the PLL fractional divide number.

F[19:16] 3–0 0010

Default value is F = 194,180 decimal.

Table 5. F-Divider MSB Register (Address: 0x03)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

Sets the most significant bits of the PLL fractional-divide number (F).

F[15:8] 7–0 11110110

Default value is F = 194,180 decimal.

Table 6. F-Divider LSB Register (Address: 0x04)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

Sets the least significant bits of the PLL fractional-divide number (F).

F[7:0] 7–0 10000100

Default value is F = 194,180 decimal.

Table 7. XTAL Buffer and Reference Divider Register (Address: 0x05)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

Sets the crystal-divider setting.

000 = Divide by 1.

001 = Divide by 2.

XD[2:0] 7–5 000 011 = Divide by 3.

100 = Divide by 4.

101 through 110 = All divide values from 5 (101) to 7 (110).

111 = Divide by 8.

Sets the PLL reference-divider (R) number. Users must program to 00001

R[4:0] 4–0 00001 upon powering up the device.

00001 = Divide by 1; other values are not tested.

www.maximintegrated.com Maxim Integrated │ 11

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Table 8. PLL Register (Address: 0x06)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

VCO divider setting.

D24 7 1 0 = Divide by 2. Use for LO frequencies ≥ 1125MHz.

1 = Divide by 4. Use for LO frequencies < 1125MHz.

Charge-pump current mode.

CPS 6 1 0 = Charge-pump current controlled by ICP bit.

1 = Charge-pump current controlled by VCO autoselect (VAS).

Charge-pump current.

ICP 5 0 0 = 600µA typical.

1 = 1200µA typical.

X 4–0 X Don’t care.

Table 9. VCO Register (Address: 0x07)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

Controls which VCO is activated when using manual VCO programming mode.

VCO[4:0] 7–3 11001

This also serves as the starting point for the VCO autoselection (VAS) mode.

VCO autoselection (VAS) circuit.

VAS 2 1 0 = Disable VCO selection must be programmed through I2C.

1 = Enable VCO selection controlled by autoselection circuit.

Enables or disables the VCO tuning voltage ADC latch when the VCO

autoselect mode (VAS) is disabled.

ADL 1 0

0 = Disables the ADC latch.

1 = Latches the ADC value.

Enables or disables VCO tuning voltage ADC read when the VCO autoselect

mode (VAS) is disabled.

ADE 0 0

0 = Disables ADC read.

1 = Enables ADC read.

Table 10. Lowpass Filter Register (Address: 0x08)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

Sets the baseband lowpass filter corner frequency.

f = 0.8 x LPF[7:0]d +3.2

LPF[7:0] 7–0 01001011 -3dB

f-3dBmin = 40MHz (LPF[7:0] = 46d = 2Eh)

f-3dBmax = 124MHz (LPF[7:0] = 151d = 97h)

www.maximintegrated.com Maxim Integrated │ 12

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Table 11. Control Register (Address: 0x09)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

Software standby control.

0 = Normal operation.

STBY 7 0 1 = Disables the signal path and frequency synthesizer leaving only the

2-wire bus, crystal oscillator, XTALOUT buffer, and XTALOUT buffer divider

active.

X 6 X Don’t care.

Factory use only.

PWDN 5 0

0 = Normal operation; other value is not tested.

X 4 X Don’t care.

Baseband gain setting (1dB typical per step).

0000 = Minimum gain (0dB, default).

BBG[3:0] 3–0 0000

…

1111 = Maximum gain (15dB typical).

Table 12. Shutdown Register (Address: 0x0A)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

X 7 X Don’t care.

PLL enable.

PLL 6 0 0 = Normal operation.

1 = Shuts down the PLL. Value not tested.

Divider enable.

DIV 5 0 0 = Normal operation.

1 = Shuts down the divider. Value not tested.

VCO enable.

VCO 4 0 0 = Normal operation.

1 = Shuts down the VCO. Value not tested.

Baseband enable.

BB 3 0 0 = Normal operation.

1 = Shuts down the baseband. Value not tested.

RF mixer enable.

RFMIX 2 0 0 = Normal operation.

1 = Shuts down the RF mixer. Value not tested.

RF VGA enable.

RFVGA 1 0 0 = Normal operation.

1 = Shuts down the RF VGA. Value not tested.

Front-end enable.

FE 0 0 0 = Normal operation.

1 = Shuts down the front-end. Value not tested.

www.maximintegrated.com Maxim Integrated │ 13

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Table 13. Test Register (Address: 0x0B)

BIT NAME BIT LOCATION (0 = LSB) DEFAULT FUNCTION

Charge-pump test modes.

CPTST[2:0] 7–5 000

000 = Normal operation (default).

X 4 X Don’t care.

Charge-pump fast lock.

TURBO 3 1

Users must program to 1 after powering up the device.

REFOUT output.

LDMUX[2:0] 2–0 000

000 = Normal operation; other values are not tested.

Table 14. Status Byte-1 Register (Address: 0x0C)

BIT NAME BIT LOCATION (0 = LSB) FUNCTION

Power-on reset status.

0 = Chip status register has been read with a stop condition since last power-on.

POR 7

1 = Power-on reset (power cycle) has occurred. Default values have been loaded in

registers.

Indicates whether VCO autoselection was successful.

VASA 6 0 = Indicates the autoselect function is disabled or unsuccessful VCO selection.

1 = Indicates successful VCO autoselection.

Status indicator for the autoselect function.

VASE 5 0 = Indicates the autoselect function is active.

1 = Indicates the autoselect process is inactive.

PLL lock detector. TURBO bit must be programmed to 1 for valid LD reading.

LD 4 0 = Unlocked.

1 = Locked.

X 3–0 Don’t care.

Table 15. Status Byte-2 Register (Address: 0x0D)

BIT NAME BIT LOCATION (0 = LSB) FUNCTION

VCOSBR[4:0] 7–3 VCO band readback.

VAS ADC output readback.

000 = Out of lock.

001 = Locked.

ADC[2:0] 2–0 010 = VAS locked.

101 = VAS locked.

110 = Locked.

111 = Out of lock.

www.maximintegrated.com Maxim Integrated │ 14

MAX2121B L-Band Tuner with Programmable

Baseband Filter

2-Wire Serial Interface Slave Address

The MAX2121B uses a 2-wire I2C-compatible serial inter- The MAX2121B has a 7-bit slave address that must be sent

face consisting of a serial-data line (SDA) and a serial clock to the device following a START condition to initiate com-

line (SCL). SDA and SCL facilitate bidirectional communi- munication. The slave address is internally programmed to

cation between the MAX2121B and the master at clock fre- 1100000. The eighth bit (R/W) following the 7-bit address

quencies up to 400kHz. The master initiates a data transfer determines whether a read or write operation occurs.

on the bus and generates the SCL signal to permit data The MAX2121B continuously awaits a START condition

transfer. The MAX2121B behaves as a slave device that followed by its slave address. When the device recog-

transfers and receives data to and from the master. SDA nizes its slave address, it acknowledges by pulling the

and SCL must be pulled high with external pullup resistors SDA line low for one clock period; it is ready to accept or

(1kΩ or greater) for proper bus operation. Pullup resistors send data depending on the R/W bit (Figure 1).

should be referenced to the MAX2121B’s VCC.

The write/read address is C0/C1 if ADDR pin is connected

One bit is transferred during each SCL clock cycle. A mini- to ground. The write/read address is C2/C3 if the ADDR

mum of nine clock cycles is required to transfer a byte in pin is connected to VCC.

or out of the MAX2121B (8 bits and an ACK/NACK). The

data on SDA must remain stable during the high period of Write Cycle

the SCL clock pulse. Changes in SDA while SCL is high When addressed with a write command, the MAX2121B

and stable are considered control signals (see the START allows the master to write to a single register or to multiple

and STOP Conditions). Both SDA and SCL remain high successive registers.

when the bus is not busy. A write cycle begins with the bus master issuing a START

START and STOP Conditions condition followed by the seven slave address bits and

a write bit (R/W = 0). The MAX2121B issues an ACK if

The master initiates a transmission with a START condi-

the slave address byte is successfully received. The bus

tion (S), which is a high-to-low transition on SDA while

master must then send to the slave the address of the

SCL is high. The master terminates a transmission with

first register it wishes to write to (see Table 1 for regis-

a STOP condition (P), which is a low-to-high transition on

ter addresses). If the slave acknowledges the address,

SDA while SCL is high.

the master can then write one byte to the register at the

Acknowledge and Not-Acknowledge Conditions specified address. Data is written beginning with the most

Data transfers are framed with an acknowledge bit (ACK) significant bit. The MAX2121B again issues an ACK if the

or a not-acknowledge bit (NACK). Both the master and data is successfully written to the register. The master

the MAX2121B (slave) generate acknowledge bits. To can continue to write data to the successive internal reg-

generate an acknowledge, the receiving device must isters with the MAX2121B acknowledging each success-

pull SDA low before the rising edge of the acknowledge- ful transfer, or it can terminate transmission by issuing a

related clock pulse (ninth pulse) and keep it low during the STOP condition. The write cycle does not terminate until

high period of the clock pulse. the master issues a STOP condition.

To generate a not-acknowledge condition, the receiver

SLAVE ADDRESS

allows SDA to be pulled high before the rising edge of

the acknowledge-related clock pulse, and leaves SDA S 1 1 0 0 0 0 0

high during the high period of the clock pulse. Monitoring R/W ACK

SDA

the acknowledge bits allows for detection of unsuccessful

data transfers. An unsuccessful data transfer happens if a SCL

1 2 3 4 5 6 7 8 9

receiving device is busy or if a system fault has occurred.

In the event of an unsuccessful data transfer, the bus Figure 1. MAX2121B Slave Address Byte with ADDR Pin

master must reattempt communication at a later time. Connected to Ground

WRITE DEVICE WRITE REGISTER WRITE DATA TO WRITE DATA TO WRITE DATA TO

ADDRESS R/W ACK ADDRESS AC REGISTER 0x00 ACK REGISTER 0x01 ACK REGISTER 0x02 ACK

START STOP

1100000 0 — 0x00 — 0x0E — 0xD8 — 0xE1 —

Figure 2. Example: Write Registers 0, 1, and 2 with 0x0E, 0xD8, and 0xE1, respectively.

www.maximintegrated.com Maxim Integrated │ 15

MAX2121B L-Band Tuner with Programmable

Baseband Filter

ACK/

WRITE DEVICE ADDRESS R/W ACK READ FROM STATUS BYTE-1 REGISTER ACK READ FROM STATUS BYTE-2 REGISTER

START NACK STOP

1100000 1 — — — — —

Figure 3. Example: Receive Data from Read Registers

Read Cycle Table 16. Maximum Crystal ESR

When addressed with a read command, the MAX2121B Requirement

allows the master to read back a single register, or mul-

ESRMAX (Ω) XTAL FREQUENCY (MHz)

tiple successive registers.

80 12 < fXTAL ≤ 14

A read cycle begins with the bus master issuing a START

60 14 < fXTAL ≤ 30

condition followed by the seven slave address bits and

a write bit (R/W = 0). The MAX2121B issues an ACK if Baseband Lowpass Filter

the slave address byte is successfully received. The bus

The MAX2121B includes a programmable on-chip 5th-

master must then send the address of the first register it

order Butterworth filter with 1st-order group delay com-

wishes to read (see Table 1 for register addresses). The

pensation. The filter -3dB corner frequency can be adjust-

slave acknowledges the address. Then, a START condi-

ed to approximately 40MHz to 124MHz by programming

tion is issued by the master, followed by the seven slave

the LPF[7:0] register using the following equation:

address bits and a read bit (R/W = 1). The MAX2121B

issues an ACK if the slave address byte is successfully LPF[7:0]dec = 1.25(f-3dB - 3.2)

received. The MAX2121B starts sending data MSB first where f-3dB is in units of MHz.

with each SCL clock cycle. At the 9th clock cycle, the

The supply current is dependant on the filter bandwidth

master can issue an ACK and continue to read succes-

setting. See the Supply Current vs. LPF[7:0] graph in the

sive registers, or the master can terminate the transmis-

Typical Operating Characteristics.

sion by issuing a NACK. The read cycle does not termi-

nate until the master issues a STOP condition. DC Offset Cancellation

Figure 3 illustrates an example in which registers 0, 1, and The DC offset cancellation is required to maintain the I/Q

2 are read back. output dynamic range. Connecting an external capacitor

between IDC+ and IDC- forms a highpass filter for the I

Applications Information channel and an external capacitor between QDC+ and

The MAX2121B downconverts RF signals in the 925MHz QDC- forms a highpass filter for the Q channel. Keep the

to 2175MHz range directly to the baseband I/Q signals. value of the external capacitor less than 47nF to form a

typical highpass corner of 250Hz.

RF Input

The RF input of the MAX2121B is internally matched to XTAL Oscillator

75Ω. Only a DC-blocking capacitor is needed. See the The MAX2121B contains an internal reference oscilla-

Typical Application Circuit. tor, reference output divider, and output buffer. All that

is required is to connect a crystal through a series 1nF

RF Gain Control capacitor. To minimize parasitics, place the crystal and

The MAX2121B features a variable-gain low-noise ampli- series capacitor as close as possible to pin 14 (XTAL).

fier providing 73dB of RF gain range. The voltage con- See Table 16 for crystal (XTAL) ESR (equivalent series

trol (VGC) range is 0.5V (minimum attenuation) to 2.7V resistance) requirements.

(maximum attenuation).

Programming the Fractional

Baseband Variable-Gain Amplifier N- Synthesizer

The receiver baseband variable-gain amplifiers provide The MAX2121B utilizes a fractional-N type synthesizer

15dB of gain control range programmable in 1dB steps. for LO frequency programming. To program the frequency

The VGA gain can be serially programmed through the I2C synthesizer, the N and F values are encoded as straight

interface by setting bits BBG[3:0] in the Control register. binary numbers. Determination of these values is illus-

trated by the following example:

www.maximintegrated.com Maxim Integrated │ 16

MAX2121B L-Band Tuner with Programmable

Baseband Filter

fLO is 2170MHz Table 17. ADC Trip Points and Lock Status

fXTAL is 27 MHz ADC[2:0] LOCK STATUS

Phase-detector comparison frequency is from 12MHz and 000 Out of lock

30MHz 001 Locked

R divider = R[4:0] = 1 010 VAS locked

fCOMP = 27MHz/1 = 27MHz 101 VAS locked

110 Locked

D = fLO/fCOMP = 2170/27 = 80.37037

111 Out of lock

Integer portion:

N = 80 the Status Byte-2 register (see Table 15). If the search

is unsuccessful, VASA is cleared and VASE is set. This

N[14:8] = 0

indicates that searching has ended but no good VCO has

N[7:0] = 0101 0000 been found, and occurs when trying to tune to a frequency

Fractional portion: outside the VCO’s specified frequency range.

F = 0.370370 x 220 = 388,361 (round up the decimal portion) Refer to Application Note 4256: Extended

Characterization for the MAX2112/MAX2120 Satellite

F = 0101 1110 1101 0000 1001

Tuners.

Note: When changing LO frequencies, all the divider

registers (integer and fractional) must be programmed to 3-Bit ADC

activate the VAS function regardless of whether individual The MAX2121B has an internal 3-bit ADC connected to

registers are changed. the VCO tune pin (TUNEVCO). This ADC can be used for

checking the lock status of the VCOs.

VCO Autoselect (VAS)

Table 17 summarizes the ADC output bits and the VCO

The MAX2121B includes 24 VCOs. The local oscillator

lock indication. The VCO autoselect routine only selects

frequency can be manually selected by programming the

a VCO in the “VAS locked” range. This allows room for

VCO[4:0] bits in the VCO register. The selected VCO is

a VCO to drift over temperature and remain in a valid

reported in the Status Byte-2 register (see Table 15).

“locked” range.

Alternatively, the MAX2121B can be set to autonomously

The ADC must first be enabled by setting the ADE bit in

choose a VCO by setting the VAS bit in the VCO reg-

the VCO register. The ADC reading is latched by a sub-

ister to logic-high. The VAS routine is initiated once the

sequent programming of the ADC latch bit (ADL = 1). The

F-Divider LSB register word (register 5) is loaded.

ADC value is reported in the Status Byte-2 register (see

Thus it is important to write register 5 after any of the fol- Table 15).

lowing PLL related bits have been changed:

N-Divider bits (registers 1 and/or 2)

Standby Mode

The MAX2121B features normal operating mode and

F-Divider bits (registers 3 and/or 4)

standby mode using the I2C interface. Setting a logic-high

Reference Divider bits (register 6) to the STBY bit in the Control register puts the device into

D24, CPS, or ICP bits (register 7) standby mode, during which only the 2-wire-compatible

bus, the crystal oscillator, the XTAL buffer, and the XTAL

This will ensure all intended bits have been programmed

buffer divider are active.

before the VAS is initiated and the PLL is locked. The VCO

value programmed in the VCO[4:0] register serves as the In all cases, register settings loaded prior to entering

starting point for the automatic VCO selection process. shutdown are saved upon transition back to active mode.

Default register values are provided for the user’s con-

During the selection process, the VASE bit in the Status

venience only. It is the user’s responsibility to load all

Byte-1 register is cleared to indicate the autoselection

the registers no sooner than 100μs after the device is

function is active. Upon successful completion, bits VASE

powered up.

and VASA are set and the VCO selected is reported in

www.maximintegrated.com Maxim Integrated │ 17

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Typical Application Circuit

SERIAL-DATA

INPUT/OUTPUT

SERIAL-CLOCK

INPUT VCC

VCC_BB

ADDR

QDC+

QDC-

SDA

IDC-

SCL

VCC

+ 28 27 26 25 24 23 22 IDC+

VCC_RF2

1 DC OFFSET 21

VCC

INTERFACE LOGIC CORRECTION

AND CONTROL IOUT-

VCC_RF1 MAX2121B

2 20

IOUT+

GND

3 19

QOUT- BASEBAND

RF INPUT

RFIN OUTPUTS

4 18

VGC QOUT+

GC1

5 17

VCC VCC

DIV2 FREQUENCY

VCC_LO SYNTHESIZER VCC_DIG

/DIV4

VCC 6 16

EP

VCC_VCO REFOUT

7 15

8 9 10 11 12 13 14

BYPVCO

TUNEVCO

GNDTUNE

GNDSYN

CPOUT

VCC_SYN

XTAL

VCC

Layout Considerations Ordering Information

The MAX2121 EV kit serves as a guide for PCB layout. PART TEMP RANGE PIN-PACKAGE

Keep RF signal lines as short as possible to minimize

MAX2121BETI+ -40°C to +85°C 28 TQFN-EP*

losses and radiation. Use controlled impedance on all

high-frequency traces. For proper operation, the exposed +Denotes a lead(Pb)-free/RoHS-compliant package.

paddle must be soldered evenly to the board’s ground *EP = Exposed pad.

plane. Use abundant vias beneath the exposed paddle

for maximum heat dissipation. Use abundant ground

vias between RF traces to minimize undesired coupling. Chip Information

Bypass each VCC pin to ground with a 1nF capacitor PROCESS: BiCMOS

placed as close as possible to the pin.

www.maximintegrated.com Maxim Integrated │ 18

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Package Information

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a “+”,

“#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing

pertains to the package regardless of RoHS status.

PACKAGE PACKAGE OUTLINE LAND

TYPE CODE NO. PATTERN NO.

28 TQFN-EP T2855+3 21-0140 90-0023

www.maximintegrated.com Maxim Integrated │ 19

MAX2121B L-Band Tuner with Programmable

Baseband Filter

Revision History

REVISION REVISION PAGES

DESCRIPTION

NUMBER DATE CHANGED

0 6/15 Initial release —

1 9/16 Updated Programming the Fractional N-Synthesizer equation 17

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated’s website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses

are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits)

shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc. © 2016 Maxim Integrated Products, Inc. │ 20

You might also like

- MAX2121Document19 pagesMAX2121Davy SaNo ratings yet

- Multi-Standard Advanced Dual Demodulator For Satellite Digital TV Broadcast Set-Top BoxesDocument4 pagesMulti-Standard Advanced Dual Demodulator For Satellite Digital TV Broadcast Set-Top BoxesGautam BalharaNo ratings yet

- Ddc2256a FinalDocument47 pagesDdc2256a Final박혜인No ratings yet

- MCP3561!2!4 Two Four Eight ChannelDocument108 pagesMCP3561!2!4 Two Four Eight ChannelMahan RezakhahNo ratings yet

- MAX15021Document24 pagesMAX15021Phong Phan CôngNo ratings yet

- MCP3561 2 4 Family Data Sheet DS20006181C-2257924Document109 pagesMCP3561 2 4 Family Data Sheet DS20006181C-2257924nidhalaloui03No ratings yet

- ATBM2040 (Silicon Tuner IC) Product BriefDocument1 pageATBM2040 (Silicon Tuner IC) Product Briefavrelec100% (1)

- Max 2769Document23 pagesMax 2769mostafaNo ratings yet

- 1 J MST 87 2023 1 8 5654Document8 pages1 J MST 87 2023 1 8 5654k3proNo ratings yet

- NCP1032 Low Power PWM Controller With On-Chip Power Switch and Startup Circuits For Telecom SystemsDocument21 pagesNCP1032 Low Power PWM Controller With On-Chip Power Switch and Startup Circuits For Telecom SystemsMalith UdayangaNo ratings yet

- MAX1535ADocument39 pagesMAX1535ALưuVănViếtNo ratings yet

- Features: PLCC-28Document35 pagesFeatures: PLCC-28肖磊No ratings yet

- Features: When Fitted On A 2600 PCB This Chip Will Work But Needs Some Modification of Hardware For Full FonctionsDocument114 pagesFeatures: When Fitted On A 2600 PCB This Chip Will Work But Needs Some Modification of Hardware For Full Fonctions肖磊No ratings yet

- GPS 12-Channel CorrelatorDocument63 pagesGPS 12-Channel Correlatorkhurram97et11No ratings yet

- BK4802N - IC Radio PDFDocument19 pagesBK4802N - IC Radio PDFpatolin_123No ratings yet

- Data Sheet: SAA5244ADocument32 pagesData Sheet: SAA5244AVitorio LogoNo ratings yet

- Features: Low Cost Very High Performance SMD GPS ModuleDocument13 pagesFeatures: Low Cost Very High Performance SMD GPS ModulemauriceNo ratings yet

- RTC MCP79410Document8 pagesRTC MCP79410hunter73100% (1)

- Oe91c1700 PDFDocument18 pagesOe91c1700 PDFJose MorenoNo ratings yet

- OE90C2800 Lite: PLCC-28Document66 pagesOE90C2800 Lite: PLCC-28肖磊No ratings yet

- Linear Technology LT2410 24bit - DatasheetDocument48 pagesLinear Technology LT2410 24bit - DatasheetdonatoNo ratings yet

- 001 LinkStar DVBS2 ModulatorDocument17 pages001 LinkStar DVBS2 Modulatorgerson846No ratings yet

- Sc900a PDFDocument23 pagesSc900a PDFgoguNo ratings yet

- PLCC-28: FeaturesDocument25 pagesPLCC-28: FeaturesTitoNo ratings yet

- DF, GNDSF HgkdskfgldfsDocument13 pagesDF, GNDSF HgkdskfgldfsRicard Comas xacnóNo ratings yet

- Features: ISL97649ADocument22 pagesFeatures: ISL97649ARajaNo ratings yet

- World'S Lowest Power 9-Axis Mems Motiontracking™ Device: General Description ApplicationsDocument89 pagesWorld'S Lowest Power 9-Axis Mems Motiontracking™ Device: General Description ApplicationsrodrigoelbarbaroNo ratings yet

- Rda 6645aDocument2 pagesRda 6645arendra zeeNo ratings yet

- MAX2411ADocument14 pagesMAX2411AalperencoskunNo ratings yet

- 24 GHZ To 44 GHZ Wideband Integrated Upconverters and Downconverters Boost Microwave Radio Performance While Reducing SizeDocument4 pages24 GHZ To 44 GHZ Wideband Integrated Upconverters and Downconverters Boost Microwave Radio Performance While Reducing SizeSergeyNo ratings yet

- T.D.A 10021HTDocument16 pagesT.D.A 10021HTJose M PeresNo ratings yet

- USB-C™ Port Controller: FeaturesDocument2 pagesUSB-C™ Port Controller: FeaturesChau Nguyen MinhNo ratings yet

- Mitsubishi : 8-Bit 8-Ch Multiplying D-A Converter With Buffer AmplifiersDocument6 pagesMitsubishi : 8-Bit 8-Ch Multiplying D-A Converter With Buffer AmplifiersquinquinoNo ratings yet

- CM508 Ri02 P05T00Document26 pagesCM508 Ri02 P05T00Javier Rolando90% (71)

- E981-03 Elmos DsDocument51 pagesE981-03 Elmos Dskuyku3097No ratings yet

- RN2483 Low Power Long Range LoRa Technology Transceiver Module DS50002346FDocument24 pagesRN2483 Low Power Long Range LoRa Technology Transceiver Module DS50002346FВіталій ПузакNo ratings yet

- Sky65171-11: 1930 - 1990 MHZ, 0.5 W High Power Power AmplifierDocument10 pagesSky65171-11: 1930 - 1990 MHZ, 0.5 W High Power Power AmplifiercopslockNo ratings yet

- TFT - LCD Module: LQ104S1LG31Document18 pagesTFT - LCD Module: LQ104S1LG31Farooq AhmedNo ratings yet

- PL - MS6M30K.1 Universal LCD LED LCD Panel 120HZ PlateDocument9 pagesPL - MS6M30K.1 Universal LCD LED LCD Panel 120HZ Platesomucdm6023100% (4)

- Ultra-Low-Power, 10Msps, Dual 8-Bit ADC: General Description FeaturesDocument22 pagesUltra-Low-Power, 10Msps, Dual 8-Bit ADC: General Description FeaturesThomas ThomasNo ratings yet

- SN 65 HVD 232Document41 pagesSN 65 HVD 232Ha Bui VietNo ratings yet

- CYG2111Document5 pagesCYG2111mendezp2410No ratings yet

- Icl7135c - TLC7135CDocument11 pagesIcl7135c - TLC7135CCarlos PosadaNo ratings yet

- rn2483 DatascheetDocument20 pagesrn2483 DatascheetbruseisiNo ratings yet

- TLC 7225Document21 pagesTLC 7225tajpan77No ratings yet

- REN Isl8121 DST 20060811Document26 pagesREN Isl8121 DST 20060811blackorgonNo ratings yet

- 150 MHZ Pixel Video Controller For Monitors: FeatureDocument19 pages150 MHZ Pixel Video Controller For Monitors: Featurezerquera3000No ratings yet

- ADF5902Document39 pagesADF5902shubhamNo ratings yet

- Intersil ISL97649AIRZ T DatasheetDocument21 pagesIntersil ISL97649AIRZ T DatasheetKeys SyekNo ratings yet

- Datasheet - HK ds1286 1090859Document12 pagesDatasheet - HK ds1286 1090859Ardians FaqihNo ratings yet

- Dialog - Semiconductor IW7011 CU TQ2E 1 DatasheetDocument6 pagesDialog - Semiconductor IW7011 CU TQ2E 1 DatasheetjamorNo ratings yet

- Gcm-0S12-024-0401-F: Motohawk Control SolutionsDocument9 pagesGcm-0S12-024-0401-F: Motohawk Control Solutionszakie0690No ratings yet

- Maxim Max8632Document29 pagesMaxim Max8632ERICO STRAMANDINOLINo ratings yet

- 3-V To 5.5-V Multichannel Rs-232 Line Driver/Receiver With 15-Kv Iec Esd ProtectionDocument31 pages3-V To 5.5-V Multichannel Rs-232 Line Driver/Receiver With 15-Kv Iec Esd ProtectionFabian OrtuzarNo ratings yet

- ICL88xx Flyback Design Guide: DG - 2103 - PL39 - 2104 - 160011Document64 pagesICL88xx Flyback Design Guide: DG - 2103 - PL39 - 2104 - 160011Michael WeirichNo ratings yet

- BQ3123Document19 pagesBQ3123Alexander Wernhart100% (1)

- Ucc28c40, Ucc28c41, Ucc28c42, Ucc28c43, Ucc28c44, Ucc28c45 Ucc38c40, Ucc38c41, Ucc38c42, Ucc38c43, Ucc38c44, Ucc38c45Document32 pagesUcc28c40, Ucc28c41, Ucc28c42, Ucc28c43, Ucc28c44, Ucc28c45 Ucc38c40, Ucc38c41, Ucc38c42, Ucc38c43, Ucc38c44, Ucc38c45curz0% (1)

- Panasonic Kx-tg2361 SMDocument40 pagesPanasonic Kx-tg2361 SMReza AranNo ratings yet

- MC33742 PDFDocument72 pagesMC33742 PDFfraurNo ratings yet

- Technical Rockwell Automation FactoryTalk HistorianDocument6 pagesTechnical Rockwell Automation FactoryTalk HistorianAmit MishraNo ratings yet

- Literature Review - Part Time Job Among StudentDocument3 pagesLiterature Review - Part Time Job Among StudentMarria65% (20)

- Or HandoutDocument190 pagesOr Handoutyared haftu67% (6)

- Introduction To Microelectronic Fabrication PDFDocument332 pagesIntroduction To Microelectronic Fabrication PDFChristy Moore92% (13)

- Chapter 6 Strategy Analysis and Choice: Strategic Management: A Competitive Advantage Approach, 16e (David)Document27 pagesChapter 6 Strategy Analysis and Choice: Strategic Management: A Competitive Advantage Approach, 16e (David)Masum ZamanNo ratings yet

- The Perception of Luxury Cars MA Thesis 25 03Document60 pagesThe Perception of Luxury Cars MA Thesis 25 03Quaxi1954No ratings yet

- Hand Winches 122 Load Sheaves 126 Gear-And Worm Gear Winches 127 Electric Worm Gear Winches 131 Snatch Blocks 133Document14 pagesHand Winches 122 Load Sheaves 126 Gear-And Worm Gear Winches 127 Electric Worm Gear Winches 131 Snatch Blocks 133Rajaram JayaramanNo ratings yet

- WCDMA Radio Access OverviewDocument8 pagesWCDMA Radio Access OverviewDocMasterNo ratings yet

- CLT Apllications NewestDocument49 pagesCLT Apllications NewestMackBrideNo ratings yet

- DIY Toolkit Arabic Web VersionDocument168 pagesDIY Toolkit Arabic Web VersionAyda AlshamsiNo ratings yet

- RESEARCHDocument5 pagesRESEARCHroseve cabalunaNo ratings yet

- Book Chapter 11 SubmissionDocument18 pagesBook Chapter 11 Submissioncristine_2006_g5590No ratings yet

- AIP 2020 FINAL JuneDocument5 pagesAIP 2020 FINAL JuneVINA ARIETANo ratings yet

- SANDWICH Elisa (Procedure) - Immunology Virtual Lab I - Biotechnology and Biomedical Engineering - Amrita Vishwa Vidyapeetham Virtual LabDocument2 pagesSANDWICH Elisa (Procedure) - Immunology Virtual Lab I - Biotechnology and Biomedical Engineering - Amrita Vishwa Vidyapeetham Virtual LabsantonuNo ratings yet

- NCERT Solutions For Class 10 Maths Chapter 5 Arithmetic Progression (Ex 5.1) Exercise 5.1Document8 pagesNCERT Solutions For Class 10 Maths Chapter 5 Arithmetic Progression (Ex 5.1) Exercise 5.1Akash DasNo ratings yet

- Structure of NABARD Grade ADocument7 pagesStructure of NABARD Grade ARojalin PaniNo ratings yet

- Corrosion Performance of Mild Steel and GalvanizedDocument18 pagesCorrosion Performance of Mild Steel and GalvanizedNarasimha DvlNo ratings yet

- Derivation Bragg's Snell Law PDFDocument4 pagesDerivation Bragg's Snell Law PDFVaswati BiswasNo ratings yet

- The Other Twelve Part 1Document5 pagesThe Other Twelve Part 1vv380100% (2)

- TCGRX BullsEye Tablet SplitterDocument2 pagesTCGRX BullsEye Tablet SplittermalucNo ratings yet

- Rare Watches (Christie's) 16. 05. 2016.Document236 pagesRare Watches (Christie's) 16. 05. 2016.Simon LászlóNo ratings yet

- Ishrana Studenata I Nastavnika Visoke Škole U Subotici Tokom Pandemije COVID-19Document4 pagesIshrana Studenata I Nastavnika Visoke Škole U Subotici Tokom Pandemije COVID-19DejanNo ratings yet

- VTB Datasheet PDFDocument24 pagesVTB Datasheet PDFNikola DulgiarovNo ratings yet

- Innocent Words That Make Her HornyDocument14 pagesInnocent Words That Make Her HornyH69% (13)

- 1.classification of Reciprocating PumpsDocument8 pages1.classification of Reciprocating Pumpsgonri lynnNo ratings yet

- CBC DrivingDocument74 pagesCBC DrivingElonah Jean ConstantinoNo ratings yet

- Final Quiz 2 - Attempt ReviewDocument6 pagesFinal Quiz 2 - Attempt Reviewkoraijohnson7No ratings yet

- Materials Management - 1 - Dr. VP - 2017-18Document33 pagesMaterials Management - 1 - Dr. VP - 2017-18Vrushabh ShelkarNo ratings yet

- Speaking RubricDocument1 pageSpeaking RubricxespejoNo ratings yet

- IPC PL 11 006 MS Auditors Issue 7.05Document32 pagesIPC PL 11 006 MS Auditors Issue 7.05saladinNo ratings yet