Professional Documents

Culture Documents

19-CP-25 Maham Zaman DSD Lab 10

Uploaded by

Emaan FatimaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

19-CP-25 Maham Zaman DSD Lab 10

Uploaded by

Emaan FatimaCopyright:

Available Formats

UNIVERSITY OF ENGINEERING

AND TECHNOLOGY, TAXILA

Lab Report 10

Digital System Design Lab

Name: Maham Zaman

Reg No.: 19-CP-25

Section: Alpha

Department: Computer Engineering

Submitted To: Sir Asghar Ismail\

Objective:

Verilog Code for Complete Module Stitching Datapath and Control Unit of Traffic Light Controller

using ASMD Technique

Apparatus List:

PC installed with Vivado Xilinx tool Nexys

4 Fpga Kit

Procedure:

Following is Procedure for Implementation on FPGA kit

1. Writing the Source Code of module and simulating it

2. Opening Elaborated Design

3. Setting Constraints

4. Running Synthesis

5. After Successful Synthesis Running Implementation

6. After Successful Implementation Generating Bit Stream

7. Downloading Bit Stream to FPGA kit using Hardware Manager

Lab Task:

Write Verilog Code for Complete Module Stitching Datapath and Control Unit of Traffic Light

Controller using ASMD Technique

Verilog Code for Top Module of TLC:

module TLC(output [1:0] TLC_SigEast, output [1:0] TLC_SigWest, output [1:0] TLC_SigNorth,

output [1:0]TLC_SigSouth, input TLC_RST,input Clk);

wire W_COD0_SigWest, W_COD0_SigEast,W_COD0_SigNorth,W_COD0_SigSouth,

W_COD0_Counter;

CU_TLC C0(.Clk(Clk),.CU_RST(TLC_RST),.CU_CountFlag(W_COD0_Counter),

.CU_SelEast(W_COD0_SigEast), .CU_SelWest(W_COD0_SigWest),

.CU_SelNorth(W_COD0_SigNorth) , .CU_SelSouth(W_COD0_SigSouth));

DP_TLC D0(.Clk(Clk),.DP_CountFlag(W_COD0_Counter),.DP_SelEast(W_COD0_SigEast),

.DP_SelWest(W_COD0_SigWest),.DP_SelNorth(W_COD0_SigNorth),

.DP_SelSouth(W_COD0_SigSouth), .DP_SigEast(TLC_SigEast),

.DP_SigWest(TLC_SigWest), .DP_SigNorth(TLC_SigNorth), .DP_SigSouth(TLC_SigSouth));

endmodule

Verilog Code for Control Unit of TLC: State

Transition:

module CU_TLC(output reg CU_SelEast,output reg CU_SelWest,output reg CU_SelNorth,

output reg CU_SelSouth, input CU_RST, input Clk,input CU_CountFlag);

parameter S_Rst=3’b000,S_East=3’b001,S_West=3’b010,S_North=3’b011,S_South=3’b100;

reg[2:0]State_Reg;

always@(posedge Clk or negedge CU_RST)

if(RST==0) State_Reg<=S_Rst;

else

case( State_Reg) S_Rst:

State_Reg<=S_West;

S_West:

if(Count_Flag==1)

State_Reg<=S_North;

else

State_Reg<=S_West; S_North:

if(Count_Flag==1)

State_Reg<=S_East;

else

State_Reg<=S_North;

S_East:

if(Count_Flag==1)

State_Reg<=S_South;

else

State_Reg<=S_East; S_South:

if(Count_Flag==1)

State_Reg<=S_West;

else

State_Reg<=S_South;

endcase

endmodule

Signal Assignment:

module CU_TLC(output reg CU_SelEast,output reg CU_SelWest,output reg CU_SelNorth,

output reg CU_SelSouth, input CU_RST, input Clk,input CU_CountFlag); parameter

S_Rst=3’b000,S_East=3’b001,S_West=3’b010,S_North=3’b011,S_South=3’b100;

reg[2:0]State_Reg;

always@(State_Reg) case(State_Reg) S_Rst:

begin

CU_SelEast<=1’b0;CU_SelNorth<=1’b0;

CU_SelSouth<=1’b01; CU_SelWest<=1’b 0;

end

S_West:

begin

CU_SelSouth<=1’b 0;CU_SelWest<=1’b 1;

end

S_North:

begin

CU_SelNorth<=1’b1; CU_SelWest<=1’b0;

end S_East:

begin

CU_SelEast<=1’b1; CU_SelNorth<=1’b0;

end

S_South:

begin

CU_SelSouth<=1’b1;CU_SelEast<=1’b0;

end

endmodule

Verilog Code for Datapath of TLC:

module DP_TLC(output [1:0]DP_South, output [1:0]DP_North, output [1:0]DP_East,

output [1:0]DP_West,input DP_CLK, input DP_Rst, input CU_North, input CU_South,

input CU_East, input CU_West, output CU_CFlag); wire [1:0] Green; wire [1:0] Red;

assign Green=2'b01;

assign Red=2'b10;

Mux21 M_East(.Mux_Out(DP_East),.Mux_In1(Red),.Mux_In2(Green),

.Mux_Sel(CU_East));

Mux21 M_West(.Mux_Out(DP_West),.Mux_In1(Red),.Mux_In2(Green),

.Mux_Sel(CU_West));

Mux21 M_South(.Mux_Out(DP_South),.Mux_In1(Red),.Mux_In2(Green),

.Mux_Sel(CU_South) );

Mux21 M_North(.Mux_Out(DP_North),.Mux_In1(Red),.Mux_In2(Green),

.Mux_Sel(CU_North) );

Counter C1(.Count_Flag(CU_CFlag), .Count_Clk(DP_CLK), .Count_Rst(DP_Rst));

endmodule

Code for Mux:

module Mux21(output [1:0] Mux_Out,input [1:0] Mux_In1,input [1:0] Mux_In2,

input Mux_Sel ); assign Mux_Out = (Mux_Sel)? Mux_In1: Mux_In2;

endmodule

Code for Counter:

module Counter(output reg Count_Flag, input Count_Clk, input Count_Rst);

reg [2:0] Count; always@(posedge Count_Clk or posedge Count_Rst)

if(Count_Rst==1) begin

Count_Flag=1'b0;

Count=3'd0; end

else

if(Count==3'd4)

Count_Flag=1'b1;

else if(Count==3'd5)

begin

Count_Flag=1'b0;

Count=3'd0;

end else

Count=Count+1;

endmodule

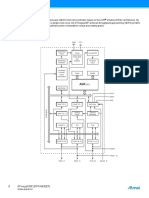

Schematic Diagram:

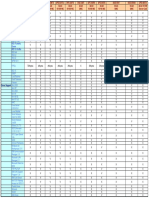

FPGA Implementation:

You might also like

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Programming FPGAsDocument38 pagesProgramming FPGAssayuri8910No ratings yet

- PWM Driver VerilogDocument24 pagesPWM Driver Veriloglizhi0007No ratings yet

- FPGA With Touch ScreenDocument23 pagesFPGA With Touch ScreenCharawut MasukNo ratings yet

- DC1010 DC1020 DC1030 DC1040: Communication ManualDocument28 pagesDC1010 DC1020 DC1030 DC1040: Communication ManualGubski Gubatayao100% (1)

- Simulation SeminarDocument45 pagesSimulation SeminarKapasi TejasNo ratings yet

- Xilinx Lab RecordDocument76 pagesXilinx Lab RecordDivya SantoshiNo ratings yet

- PIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsFrom EverandPIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsRating: 5 out of 5 stars5/5 (1)

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- Analog Electronics Lab Manual-10esl67Document61 pagesAnalog Electronics Lab Manual-10esl67manojmanojsarmaNo ratings yet

- ARM7 9 FamilyDocument46 pagesARM7 9 FamilySaravana KumarNo ratings yet

- SDFDocument18 pagesSDFManda SwamyNo ratings yet

- Ecad & Vlsi LabDocument98 pagesEcad & Vlsi LabbitseceNo ratings yet

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCFrom EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNo ratings yet

- FPGA Summer ReportDocument18 pagesFPGA Summer ReportAbhishek RajNo ratings yet

- VHDL Project: Composite Color Generation Using RGB LedDocument15 pagesVHDL Project: Composite Color Generation Using RGB LedArun GoelNo ratings yet

- Mtech Vlsi Lab Manual 1Document38 pagesMtech Vlsi Lab Manual 1Jonathan MartinezNo ratings yet

- Intro To Lab Hex CounterDocument12 pagesIntro To Lab Hex CounterYX GohNo ratings yet

- Ec 452 DC & VHDL Lab Manual FinalDocument51 pagesEc 452 DC & VHDL Lab Manual Finalravic_cietNo ratings yet

- VLSI Lab ManualDocument83 pagesVLSI Lab ManualSri SandhiyaNo ratings yet

- Digital ClockDocument11 pagesDigital ClockAmiin Gadari100% (4)

- Nexus 9000 Cloud Scale ASIC (Tahoe) NX-OS ELAMDocument7 pagesNexus 9000 Cloud Scale ASIC (Tahoe) NX-OS ELAMIsmail MirzayevNo ratings yet

- Write A Program For Interfacing The 16x2 LCD MODULES AimDocument7 pagesWrite A Program For Interfacing The 16x2 LCD MODULES AimLeelasrikanth TubatiNo ratings yet

- Evd19i018-Esdp Lab 9Document18 pagesEvd19i018-Esdp Lab 9Jampani sarath chandraNo ratings yet

- Creating IPCore Loi 11may2013Document20 pagesCreating IPCore Loi 11may2013LinkyNo ratings yet

- Atchuta Rao CommandsDocument5 pagesAtchuta Rao CommandsRAZNo ratings yet

- Cb2re TBDocument2 pagesCb2re TBOrrette BakerNo ratings yet

- ASIC Va VHDL Toan TapDocument76 pagesASIC Va VHDL Toan TapCường VũNo ratings yet

- E-Cad & Vlsi Lab ManualDocument86 pagesE-Cad & Vlsi Lab Manuallakshmikala giddaluruNo ratings yet

- Xilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyDocument5 pagesXilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyjackNo ratings yet

- Adc ProgramDocument3 pagesAdc ProgramMallikarjun DeshmukhNo ratings yet

- UartDocument19 pagesUartapi-26691029No ratings yet

- Sti Is1462 - Fic Lm10w - Rev 0.7Document55 pagesSti Is1462 - Fic Lm10w - Rev 0.7Christopher LloydNo ratings yet

- EC8711 Embedded Lab Manual FinalDocument258 pagesEC8711 Embedded Lab Manual FinalbloomeceNo ratings yet

- Experiment No 3 AdcDocument8 pagesExperiment No 3 AdcDakshata WaghNo ratings yet

- 25 LC 1024Document34 pages25 LC 1024Theviet NgoNo ratings yet

- Ec6711 Emb Lab PDFDocument92 pagesEc6711 Emb Lab PDFAnonymous LXQnmsD100% (1)

- ES Lab FileDocument37 pagesES Lab FileMøhït JáñgírNo ratings yet

- A Industrial Training Project Report ON: VHDL Coding For Decade Counter On Xilinx and Create Test Waveform"Document40 pagesA Industrial Training Project Report ON: VHDL Coding For Decade Counter On Xilinx and Create Test Waveform"SHADAN khanNo ratings yet

- MDS I ManualDocument41 pagesMDS I ManualPanku RangareeNo ratings yet

- Fujitsu Siemens Amilo Pro v2030 Fic Lm7r Rev 0.1 SCHDocument55 pagesFujitsu Siemens Amilo Pro v2030 Fic Lm7r Rev 0.1 SCHBogumiła SzmydtNo ratings yet

- Fujitsu Siemens Amilo Pro v3515Document51 pagesFujitsu Siemens Amilo Pro v3515capstan567No ratings yet

- Ecad and Vlsi Lab ManualDocument125 pagesEcad and Vlsi Lab Manualsameer7mohammadNo ratings yet

- V HDL SampleDocument5 pagesV HDL Sampleppat2006No ratings yet

- Esd Lab - 9Document19 pagesEsd Lab - 9Jampani sarath chandraNo ratings yet

- Ecad Lab Manual PvpsitDocument53 pagesEcad Lab Manual PvpsitpriyankaveeramosuNo ratings yet

- FPGA Lab 07Document14 pagesFPGA Lab 07Zain AlamgirNo ratings yet

- Cadence Nclaunch LabDocument86 pagesCadence Nclaunch Labsweety987No ratings yet

- Lglite Ate Training: Lglite + Hc125 + 24C512 (I2C)Document13 pagesLglite Ate Training: Lglite + Hc125 + 24C512 (I2C)Vijayakumar SNo ratings yet

- Timbangan Digital IoT Dan Data Logger Web Berbasis ESP32, PHP Data Object Dan PostgreSQLDocument48 pagesTimbangan Digital IoT Dan Data Logger Web Berbasis ESP32, PHP Data Object Dan PostgreSQLNurdeny PribadiNo ratings yet

- Project Report NMXXXXDocument21 pagesProject Report NMXXXXMuhammad MoinNo ratings yet

- VLSI Lab Manual - 2022-1Document54 pagesVLSI Lab Manual - 2022-1SuhailNo ratings yet

- TIMER Radovan RabrenovicDocument15 pagesTIMER Radovan RabrenovicRadovan RabrenovicNo ratings yet

- Index Page: S.No. Date Name of The Experiment Marks Awarded Remarks/ Initial's Part - ADocument39 pagesIndex Page: S.No. Date Name of The Experiment Marks Awarded Remarks/ Initial's Part - ANaveenNo ratings yet

- Design Example 5.5Document10 pagesDesign Example 5.5MaheshNo ratings yet

- Embedded Systems Lab ManualDocument60 pagesEmbedded Systems Lab Manualtmuthu123100% (1)

- Evl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLDocument34 pagesEvl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLvijithacvijayanNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- Lec 18 Been EditDocument54 pagesLec 18 Been EditEmaan FatimaNo ratings yet

- Junk Food and Its EffectsDocument16 pagesJunk Food and Its EffectsEmaan FatimaNo ratings yet

- Slaamaaaa LikummmmmmmDocument1 pageSlaamaaaa LikummmmmmmEmaan FatimaNo ratings yet

- StoryDocument1 pageStoryEmaan FatimaNo ratings yet

- SoftwareDocument22 pagesSoftwarerichmapacheNo ratings yet

- Any Small Adhesive FeetDocument4 pagesAny Small Adhesive FeetRONALD INBARAJ A PhysicsNo ratings yet

- Digix-2Document2 pagesDigix-2nvkjayanthNo ratings yet

- RP4 Drawing-Model11-1 PDFDocument1 pageRP4 Drawing-Model11-1 PDFmuhammad usmanNo ratings yet

- A Journey From Jndi/Ldap Manipulation To Remote Code Execution Dream LandDocument45 pagesA Journey From Jndi/Ldap Manipulation To Remote Code Execution Dream LandAkhmad Yudha PertamaNo ratings yet

- Basic Processes: Process Model Defines The Behavior of A Module. byDocument51 pagesBasic Processes: Process Model Defines The Behavior of A Module. byAmina KraljusicNo ratings yet

- Sic Main Final MCQDocument70 pagesSic Main Final MCQPrathamesh BhosaleNo ratings yet

- Figure 2-1. Block DiagramDocument1 pageFigure 2-1. Block DiagramsalarNo ratings yet

- Eet205 Analog Electronics, December 2021Document3 pagesEet205 Analog Electronics, December 2021Midun RamkumarNo ratings yet

- Antik Price List - 2018Document12 pagesAntik Price List - 2018jjk100% (1)

- LCD ManualDocument56 pagesLCD ManualSebastian ClavijoNo ratings yet

- 3GPP TS 38.340Document22 pages3GPP TS 38.340holapaquitoNo ratings yet

- SEC201.2 Linux FundamentalsDocument213 pagesSEC201.2 Linux FundamentalsfransiscuNo ratings yet

- Avmar Quiesce SnapshotDocument5 pagesAvmar Quiesce SnapshotJosé Luiz JúniorNo ratings yet

- Defacing WebsiteDocument26 pagesDefacing WebsiteMilorad Hapau100% (1)

- Project ReportDocument39 pagesProject ReportHimani Pandey67% (3)

- CB HardwareDocument3 pagesCB HardwareHemanthNo ratings yet

- ADA STD-1 Stereo Tapped Delay ManualDocument9 pagesADA STD-1 Stereo Tapped Delay ManualNickNo ratings yet

- DGE 528T Menu EN FRDocument1 pageDGE 528T Menu EN FRv3688eNo ratings yet

- TTKUBDocument228 pagesTTKUBerrr33No ratings yet

- PKP 2018Document13 pagesPKP 2018Roza hidayaniNo ratings yet

- SLP4N60C/SLF4N60C: 600V N-Channel MOSFETDocument7 pagesSLP4N60C/SLF4N60C: 600V N-Channel MOSFETmiler2011No ratings yet

- Programming Logic and Design Comprehensive 7th Edition Joyce Farrell Test BankDocument26 pagesProgramming Logic and Design Comprehensive 7th Edition Joyce Farrell Test BankMatthewFosteroeqyp100% (47)

- Human Computer Interaction PresentationDocument14 pagesHuman Computer Interaction PresentationFisseha AbebeNo ratings yet

- Ipad Charger Teardown - Inside Apple's Charger and A Risky PhonyDocument39 pagesIpad Charger Teardown - Inside Apple's Charger and A Risky PhonyJorge Cruz MancillaNo ratings yet

- Initial Script (3059)Document14 pagesInitial Script (3059)lucky chandelNo ratings yet

- Digital Servo Amplifier Servo Star 601... 620: Assembly, Installation, SetupDocument100 pagesDigital Servo Amplifier Servo Star 601... 620: Assembly, Installation, SetupPaul RidgeNo ratings yet