Professional Documents

Culture Documents

TCON Hi3231 V530

Uploaded by

Carlos Ruiz0 ratings0% found this document useful (0 votes)

120 views1 pageHi3231

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentHi3231

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

120 views1 pageTCON Hi3231 V530

Uploaded by

Carlos RuizHi3231

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

Hi3231 V530

Hi3231 V530 芯片简介

Demura

Key specifications Wide-angle processing

4K x 2K@60 Hz TCON High-performance multi-partition line OD compensation

4K x 2K@120 Hz TCON (2 chips cascaded) Pre-charging

EPAD-LQFP128 package 1D1G, dual-gate, and tri-gate

Scan and reverse scan

High-speed input interface Flexible POL n+m line inversion

8 lane V-by-One (VBO) RX video interface PDF

4K x 2K@60 Hz 8-/10-bit video data

DE only mode Memory control interfaces

1/2 partition input format One embedded DDR memory

TCON flash and demura flash accesses

High-speed output interface

P2P/mini-LVDS TX interface

System and peripheral interfaces

4K x 2K@60 Hz or 4K x 1K@120 Hz output Embedded high-performance RISC CPU

Up to 12-pair P2P output I2C interface

All mainstream P2P protocols UART interface

Adjustable pre-emphasis and swing Multiple groups of GPIO ports

Integrated POR module

Professional HiSilicon graphics engine Multiple aging modes

Hi-Imprex, embedded image enhancement engine

High-order color management

Other

12-bit programmable gamma LUT Download and execution of the boot program through the

chip interface

Demo-mode PQ algorithms

Output spread spectrum

TCON functions

±3% spread spectrum configurable

Configurable driver timing control

30–300 kHz modulation frequencies

Configurable GOA timing control

OD/MOD

版权所有 © 上海海思技术有限公司 2019。 保留一切权利。

深圳市龙岗区坂田华为基地 D 区

邮编:518129 1 www.hisilicon.com

版本:01 日期:2019-04-23

You might also like

- F15 Maintenance MANUALDocument420 pagesF15 Maintenance MANUALАнѓелковска Марија50% (2)

- Philips L04Document94 pagesPhilips L04Marco Antonio100% (20)

- Service Manual: WWW - Audac.euDocument18 pagesService Manual: WWW - Audac.euVovaNo ratings yet

- Brief Data Sheet: Hi3516E V200 Economical HD Ip Camera SocDocument7 pagesBrief Data Sheet: Hi3516E V200 Economical HD Ip Camera Socsijovow282No ratings yet

- 2014 TV Firmware Upgrade Instruction T-NT14UAKUCDocument4 pages2014 TV Firmware Upgrade Instruction T-NT14UAKUCFatmeStathiraBarsineNo ratings yet

- AT&T R225 User's Manual PDFDocument18 pagesAT&T R225 User's Manual PDFedgarNo ratings yet

- Training BookDocument50 pagesTraining BookNicolas GandolfoNo ratings yet

- KT-LVDS-40p Display Cable ListDocument9 pagesKT-LVDS-40p Display Cable ListtsatkuNo ratings yet

- Service Manual: LE50M3571/69 LE50M3572/69Document46 pagesService Manual: LE50M3571/69 LE50M3572/69marcellobbNo ratings yet

- CNC Milling (Arabic Book)Document146 pagesCNC Milling (Arabic Book)Mohamed WahidNo ratings yet

- Tps 65178Document2 pagesTps 65178Fernando SotoNo ratings yet

- Mstar - Firmware Download - enDocument16 pagesMstar - Firmware Download - enrabas_No ratings yet

- 7cw SMD Mmbt2222a - NXPDocument8 pages7cw SMD Mmbt2222a - NXPnikkoninNo ratings yet

- Panel LG Display Lc216exn-Sfa1 0Document36 pagesPanel LG Display Lc216exn-Sfa1 0Rinaldy100% (1)

- Manual GW7 DiagramasDocument32 pagesManual GW7 DiagramasAlejandro IrarrazabalNo ratings yet

- Express Luck Group: Specification PhotoDocument1 pageExpress Luck Group: Specification PhotoYesenia Jaime RoaNo ratings yet

- Panasonic 2012 LCD-TV Et5 Dt50 Wt50 Series Technical GuideDocument93 pagesPanasonic 2012 LCD-TV Et5 Dt50 Wt50 Series Technical GuideRajaNo ratings yet

- LVDS Source Synchronous 7:1 Serialization and Deserialization Using Clock MultiplicationDocument18 pagesLVDS Source Synchronous 7:1 Serialization and Deserialization Using Clock MultiplicationRoman BacikNo ratings yet

- Service Manual CD Stereo System NSX-D20 NSX-R20Document56 pagesService Manual CD Stereo System NSX-D20 NSX-R20taz1mxNo ratings yet

- Confu HDMI To LVDS RGB TTL Driver - Specification V1802Document2 pagesConfu HDMI To LVDS RGB TTL Driver - Specification V1802ROBERTO LUONo ratings yet

- Philips 28pfl2908h-12 Chassis Vem1.1ela 17mb82sDocument43 pagesPhilips 28pfl2908h-12 Chassis Vem1.1ela 17mb82svios08No ratings yet

- Samsung Led-Tv Ue32!37!40 - 46c5xxx, Ue32c4000px N92aDocument84 pagesSamsung Led-Tv Ue32!37!40 - 46c5xxx, Ue32c4000px N92aR Muhamad Ka RidwanNo ratings yet

- LG 42LE5500 LCDDocument40 pagesLG 42LE5500 LCDundiablo100% (1)

- Sony HCD Rv222 Ver 1.1Document86 pagesSony HCD Rv222 Ver 1.1Carlos Raul100% (2)

- CV9202L TDocument57 pagesCV9202L TElhani MarocNo ratings yet

- Sony HCD Bx3 Dx3Document66 pagesSony HCD Bx3 Dx3videoson100% (2)

- LVDSDocument2 pagesLVDSmarco giustiNo ratings yet

- TV Product Service Manual GuideDocument57 pagesTV Product Service Manual GuideSimon Tyzack0% (1)

- Bd9423efv e 1223519 PDFDocument61 pagesBd9423efv e 1223519 PDFVươngNo ratings yet

- Hisense Pdp32xx Service ManualDocument49 pagesHisense Pdp32xx Service Manualvideoson50% (2)

- Maida Catalog Specifications Standard SeriesDocument16 pagesMaida Catalog Specifications Standard SeriesRetanaMaferNo ratings yet

- MT8222Document13 pagesMT8222Glaucio Almeida100% (1)

- 715t3181 LG Psu Schematic PDFDocument1 page715t3181 LG Psu Schematic PDFSAS WAJINo ratings yet

- PHILIPS Chassis QM14.3E LA PDFDocument98 pagesPHILIPS Chassis QM14.3E LA PDFboroda2410No ratings yet

- MT185WHM N10Document28 pagesMT185WHM N10Tmfiros FirosNo ratings yet

- Max 17126Document34 pagesMax 17126918329078250% (2)

- Specification PL - ms6M30.1X V1.1Document8 pagesSpecification PL - ms6M30.1X V1.1RajeshNo ratings yet

- LP154WX4 TlabDocument31 pagesLP154WX4 TlabsuzukkNo ratings yet

- Rda5876 RdaDocument22 pagesRda5876 RdaTolikNo ratings yet

- TSUM56AL MstarDocument95 pagesTSUM56AL Mstarwilliam tolentinoNo ratings yet

- rtd2662 Spec BriefDocument15 pagesrtd2662 Spec BriefWiebren van ErveNo ratings yet

- Historia de BoliviaDocument2 pagesHistoria de BoliviaAlejandro BlancoNo ratings yet

- RTD2270L/ RTD2280L: RealtekDocument8 pagesRTD2270L/ RTD2280L: RealtekAcronix SolucionesNo ratings yet

- Manual Motorola DCX3400 - ManualsBase.comDocument2 pagesManual Motorola DCX3400 - ManualsBase.comjosmi.usacNo ratings yet

- Hi 3516 DDocument7 pagesHi 3516 Dco_stel817842No ratings yet

- GP477R - 9.1" Amber HMI: Pro-Face Operator InterfacesDocument3 pagesGP477R - 9.1" Amber HMI: Pro-Face Operator Interfacesnam_54tnNo ratings yet

- Hi 3516 CDocument6 pagesHi 3516 Cco_stel817842100% (1)

- Hi3516a Professional HD Ip Camera Soc Brief Data Sheet PDFDocument7 pagesHi3516a Professional HD Ip Camera Soc Brief Data Sheet PDFАндрей ПоляковNo ratings yet

- Hi3516A Professional HD IP Camera SoC Brief Data SheetDocument7 pagesHi3516A Professional HD IP Camera SoC Brief Data Sheetco_stel817842No ratings yet

- Stih416: Advanced HD Application Processor With 3D Graphics Acceleration and Arm Cortex-A9 SMP CpuDocument5 pagesStih416: Advanced HD Application Processor With 3D Graphics Acceleration and Arm Cortex-A9 SMP CpuRegistroregistroglobNo ratings yet

- RTD2662/2660 Series Flat Panel Display ControllerDocument15 pagesRTD2662/2660 Series Flat Panel Display ControllerLuisNo ratings yet

- Hi 3 Yt 318201Document3 pagesHi 3 Yt 318201partha khatuaNo ratings yet

- Xemo_W_ENDocument2 pagesXemo_W_ENAndrei LupuNo ratings yet

- Hisilicon Professional HD Ip Camera Soc Brief Data SheetDocument8 pagesHisilicon Professional HD Ip Camera Soc Brief Data Sheetapi-415832676No ratings yet

- AI-Nvidia-RoboEX_eDocument4 pagesAI-Nvidia-RoboEX_eandreasmonNo ratings yet

- Hi3716C V200Document5 pagesHi3716C V200Marcelo CedroNo ratings yet

- Hi3751 V320 Brief Data Sheet: Key Specifications Key FeaturesDocument4 pagesHi3751 V320 Brief Data Sheet: Key Specifications Key Featuresnani_amlprm5912No ratings yet

- Multi-screen Controller for 19Document2 pagesMulti-screen Controller for 19thomvalensiNo ratings yet

- Hi 3520 DDocument7 pagesHi 3520 Daurumstar2000No ratings yet

- Ateme Kyrion Dr5000 DatasheetDocument2 pagesAteme Kyrion Dr5000 DatasheetFirdan M. Wirawan SoeditaNo ratings yet

- Hi 3798 MV200Document3 pagesHi 3798 MV200bernard benoitNo ratings yet

- Microprocessor Architectures and Systems: RISC, CISC and DSPFrom EverandMicroprocessor Architectures and Systems: RISC, CISC and DSPRating: 4 out of 5 stars4/5 (1)

- BiocomDocument179 pagesBiocompipul36No ratings yet

- CCN Driver User GuideDocument54 pagesCCN Driver User GuideCarlos RuizNo ratings yet

- REN Isl88731 DST 20060711Document22 pagesREN Isl88731 DST 20060711Rudy BudimanNo ratings yet

- XMT 450 CC/CV: (400 Volt Model) CEDocument56 pagesXMT 450 CC/CV: (400 Volt Model) CECarlos RuizNo ratings yet

- Virus Detection by ResonanceDocument42 pagesVirus Detection by ResonanceCarlos RuizNo ratings yet

- Service Manual: 39" LCD TVDocument56 pagesService Manual: 39" LCD TVCarlos RuizNo ratings yet

- Fast Track Troubleshooting French Door RefrigeratorDocument13 pagesFast Track Troubleshooting French Door RefrigeratorCarlos RuizNo ratings yet

- Stm8 Programming ManualDocument162 pagesStm8 Programming ManualimpulstekNo ratings yet

- Portable Power Drive 600: Parts List and DiagramDocument2 pagesPortable Power Drive 600: Parts List and DiagramCarlos RuizNo ratings yet

- Samsung Magician 7: Installation GuideDocument14 pagesSamsung Magician 7: Installation GuideCarlos RuizNo ratings yet

- Sieps80000098c 2 0 PDFDocument363 pagesSieps80000098c 2 0 PDFCarlos RuizNo ratings yet

- Service Manual: Whirlpool & Maytag 6.2 Cu FT Direct Drive Top Load WasherDocument68 pagesService Manual: Whirlpool & Maytag 6.2 Cu FT Direct Drive Top Load WasherCarlos Ruiz100% (1)

- IP Camera User Manual: For Further Help, Please VisitDocument34 pagesIP Camera User Manual: For Further Help, Please VisitCarlos RuizNo ratings yet

- DCU3 JtaggingDocument135 pagesDCU3 JtaggingCarlos Ruiz100% (1)

- FanucmasterboardalarmsDocument3 pagesFanucmasterboardalarmssanchai2No ratings yet

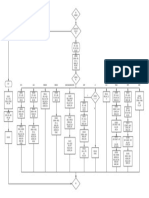

- 微程序流程图Document1 page微程序流程图Carlos RuizNo ratings yet

- Garuda PuranamDocument793 pagesGaruda PuranamJayant Nagarkar100% (1)

- Maytag Maxima Washer MHW6000XW Service PDFDocument52 pagesMaytag Maxima Washer MHW6000XW Service PDFCarlos RuizNo ratings yet

- Pequeno Manual OSCAMDocument14 pagesPequeno Manual OSCAMbalabuch6241No ratings yet

- Service Manual: Auto WasherDocument38 pagesService Manual: Auto WasherCarlos RuizNo ratings yet

- The Orphan Tsunami of 1700Document8 pagesThe Orphan Tsunami of 1700Carlos RuizNo ratings yet

- Repair Fanuc A02B-0168-B012 Power Mate B PDFDocument3 pagesRepair Fanuc A02B-0168-B012 Power Mate B PDFCarlos RuizNo ratings yet

- Sieps80000098c 2 0 PDFDocument363 pagesSieps80000098c 2 0 PDFCarlos RuizNo ratings yet

- Eurosky Dvb9004-A5 SCH PDFDocument4 pagesEurosky Dvb9004-A5 SCH PDFCarlos RuizNo ratings yet

- Control Integrated Power System (Cipos™) Igcm04G60Ha: DatasheetDocument16 pagesControl Integrated Power System (Cipos™) Igcm04G60Ha: DatasheetNur ArifinNo ratings yet

- ASSY1411Document2 pagesASSY1411Carlos RuizNo ratings yet

- Pcie Gen 1 X4 Port Dual Ecp3 Fpga Board 3X 2Gb Ddr3 4X Input and 4X Output 3.125 GHZ SFP Links 1X 1080P Single Link Hdmi OutputDocument2 pagesPcie Gen 1 X4 Port Dual Ecp3 Fpga Board 3X 2Gb Ddr3 4X Input and 4X Output 3.125 GHZ SFP Links 1X 1080P Single Link Hdmi OutputCarlos RuizNo ratings yet

- DCU3 JtaggingDocument135 pagesDCU3 JtaggingCarlos Ruiz100% (1)

- 8086 ProcessorDocument49 pages8086 ProcessorLolllNo ratings yet

- Linux Cheat SheetDocument39 pagesLinux Cheat Sheetsasha zavatinNo ratings yet

- Let's Make The Most of Your 2 Week Trial!: SetupDocument1 pageLet's Make The Most of Your 2 Week Trial!: SetupRenzo Gandolfi DiazNo ratings yet

- Laravel 2023Document6 pagesLaravel 2023Mohamed BakryNo ratings yet

- Chrome Book ListDocument6 pagesChrome Book Listbizdeal23No ratings yet

- Customize Guide For NE80E V600R003C00 Version UpgradeDocument24 pagesCustomize Guide For NE80E V600R003C00 Version UpgradeIslam AtiaNo ratings yet

- Network +Document19 pagesNetwork +Tolea TolNo ratings yet

- Generate Polish Notation from infix expressionDocument45 pagesGenerate Polish Notation from infix expressionPriya R Chourasia33% (3)

- Blue Elf Ver II ManualDocument5 pagesBlue Elf Ver II ManualMarcelo GonçalavesNo ratings yet

- Transparent Bridged FirewallDocument7 pagesTransparent Bridged FirewallLaxman G GalipelliNo ratings yet

- OCR AssignmentDocument5 pagesOCR AssignmenteyembackNo ratings yet

- How-TO Add Custom SIP Account in Nimbuzz (Tutorial) - TruVoIPBuzz PDFDocument9 pagesHow-TO Add Custom SIP Account in Nimbuzz (Tutorial) - TruVoIPBuzz PDFmuthuswamy77No ratings yet

- Advances in Power System ProtectionDocument41 pagesAdvances in Power System ProtectionHemangkumar TailorNo ratings yet

- SJL AppNote 009 - Ciphering and Secure RRC DecodingDocument22 pagesSJL AppNote 009 - Ciphering and Secure RRC DecodingRandy ChungNo ratings yet

- 2021, Annual Procurement PlanDocument178 pages2021, Annual Procurement PlanMark SantosNo ratings yet

- Blank DRP TemplateDocument44 pagesBlank DRP Templatenigger boyNo ratings yet

- Igcse Ict Year11 Week3day3Document29 pagesIgcse Ict Year11 Week3day3Warnnie Musah0% (1)

- 15 0 PGW AdminDocument538 pages15 0 PGW AdminNelsonbohrNo ratings yet

- Using Eclipse Project 3.6 PDFDocument37 pagesUsing Eclipse Project 3.6 PDFramravichandran100% (1)

- Database 12C Multi Tenant White PaperDocument53 pagesDatabase 12C Multi Tenant White PaperSrinivasa Rao AsuruNo ratings yet

- 482 Permutation Arrays: InputDocument1 page482 Permutation Arrays: InputxartemisxNo ratings yet

- Building A Radial Menu Control For Surface Devices - Developer BlogDocument19 pagesBuilding A Radial Menu Control For Surface Devices - Developer BlogIhab El AghouryNo ratings yet

- LIBROSDocument2 pagesLIBROSYesdy Ruiz ArenasNo ratings yet

- Equip Sim User ManualDocument131 pagesEquip Sim User ManualveerabossNo ratings yet

- Web - Based Attendance Monitoring SystemDocument8 pagesWeb - Based Attendance Monitoring SystemIOER International Multidisciplinary Research Journal ( IIMRJ)No ratings yet

- DIGITAL LIBRARIES DEFINITIONS, ISSUES AND CHALLENGES - Udt-Op8Document10 pagesDIGITAL LIBRARIES DEFINITIONS, ISSUES AND CHALLENGES - Udt-Op8SagarNo ratings yet

- Restoring Division Algorithm For Unsigned Integer - GeeksforGeeksDocument1 pageRestoring Division Algorithm For Unsigned Integer - GeeksforGeeksAshok KaushikNo ratings yet

- Programming in CDocument132 pagesProgramming in CchandrasekarNo ratings yet

- How to Write a Chronological Resume: GuideDocument2 pagesHow to Write a Chronological Resume: GuideMAYANK CHAUDHARYNo ratings yet