Professional Documents

Culture Documents

UEC612

Uploaded by

wizard01.2022Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UEC612

Uploaded by

wizard01.2022Copyright:

Available Formats

0 Ric--e- c_totpe4 (-0

Roll Number:

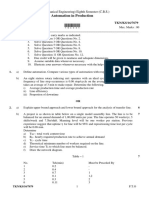

Thapar Institute of Engineering and Technology, Patiala

Department of Electronics and Communication Engineering

B. E. 2nd year ECE, End Semester Test Course Code: UEC612

Course Name: Digital System Design 12th December, 2023

Time: 3 Hours, M. Marks: 35 Instructor: Dr. Alpana Agarwal, Dr. Manu Bansal, Dr. Anil

Singh

NOTE: Attempt any 5 questions out of 6.

1 (a) Consider the values given below in the tables for 74 series gates:

.,- ♦, ' , -74ALS , -74P,

Voltage parameters

V0H(min) 2.4 2.7 2.7 2.5 2.5 2.5

Vodmax) 0.4 0.5 0.5 0.5 0.5 0.5

4(min) 2.0 2.0 2.0 2.0 2.0 2.0

Vidmax) 0.8 0.8 0.8 0.8 0.8 0.8

Mel

rn. - IL

lac

74 -0.4 mA 16 mA 40 pA -1.6 mA

74S -1 mA 20 mA 50 pA -2 mA

74LS -0.4 mA 8 mA 20 pA -0.4 mA

74AS -2 mA 20 mA 20 p.A -0.5 mA

74ALS -0.4 mA 8 mA 20 pA -0.1 mA

74F -1 mA 20 mA 20 p.A -0.6 mA

(1) Calculate the noise margins of 74ALS. 2

(ii) Calculate the fan-out value of 74ALS. 1

(iii) Calculate the average power dissipation per gate of 74ALSOO quad 2-input 1

NAND gate if Vcc = 5V, Ica! = 0.85mA, Ica = 3mA.

(b) Draw the schematic of a 3-input NOR gate at CMOS level. 3

2 A PN flip-flop has four operations: clear to 0, no change, toggle and set to 1, when

inputs P and N are 00, 01, 10, and 11, respectively.

(a) Tabulate the characteristic table 2

(b) Derive the characteristic equation 2

(c) Tabulate the excitation table 2

(d) Show how PN flip-flop can be converted to D flip-flop. 1

3 Design a 4-bit Johnson counter shift register and write its truth table along with 7

timing diagrams.

4 Design a Mealy machine to detect the sequence 1011 considering non- 7

overlapping case with the help of its state diagram. Use positive triggered T-flip

flop in the design.

5 Design a counter with T flip-flops that goes through the following binary 7

repeated sequence: 0, 1, 3, 7, 6, 4. Show that when binary states 010 and 101 are

considered as don't care conditions, the counter may not operate properly. Find a

way to correct the design.

6 Minimize and Implement using gates the following function using VEM Method 7

F=Im (3,4,7,8,9,10, 14)-1- d(2,15)

You might also like

- UEC612Document1 pageUEC612goyaldeepanshugoyal9000No ratings yet

- UEC612Document2 pagesUEC612wizard01.2022No ratings yet

- UEC612Document1 pageUEC612wizard01.2022No ratings yet

- UEC612Document1 pageUEC612goyaldeepanshugoyal9000No ratings yet

- L-4rr-l/EEE Date: 25/09/2022Document50 pagesL-4rr-l/EEE Date: 25/09/2022Nure Alam DipuNo ratings yet

- Cmos Nor and Nand GateDocument3 pagesCmos Nor and Nand GateClarisse GambotaNo ratings yet

- DL 1002Document2 pagesDL 1002Gagan SLNo ratings yet

- Lab2 - 1 EngDocument5 pagesLab2 - 1 EngDƯƠNG NGUYỄN THÁI BÌNHNo ratings yet

- V Semester B.Tech (Electrical & Electronics Engineering) Makeup Examinations, Dec 2016 - Jan 2017Document2 pagesV Semester B.Tech (Electrical & Electronics Engineering) Makeup Examinations, Dec 2016 - Jan 2017DuoDrenchNo ratings yet

- V Semester B. Tech (Electrical & Electronics Engineering) End Semester Examinations, November 2019Document3 pagesV Semester B. Tech (Electrical & Electronics Engineering) End Semester Examinations, November 2019DuoDrenchNo ratings yet

- Automation in Production: B.E. (Mechanical Engineering) Eighth Semester (C.B.S.)Document4 pagesAutomation in Production: B.E. (Mechanical Engineering) Eighth Semester (C.B.S.)Sufiyan RehmanNo ratings yet

- Tutorial 1 15Document13 pagesTutorial 1 15Charan Kanwal SinghNo ratings yet

- Digital Electronics Tutorial Sheet-1Document13 pagesDigital Electronics Tutorial Sheet-1shraddhabansalNo ratings yet

- Practice Problems For Instrumentation and MeasurementDocument13 pagesPractice Problems For Instrumentation and MeasurementMark lord bongatNo ratings yet

- F Phy143Document2 pagesF Phy143studyzilaNo ratings yet

- Solution ST1 Set ADocument12 pagesSolution ST1 Set Agaurika.sawhney2003No ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityRutu ThakkarNo ratings yet

- DL 128Document2 pagesDL 128Gagan SLNo ratings yet

- Assignment Two Topic QuestionsDocument5 pagesAssignment Two Topic QuestionsBame SereboloNo ratings yet

- Digital Electronics Question BankDocument6 pagesDigital Electronics Question BankReshna ShowkathNo ratings yet

- April 2005 WithsloutionDocument21 pagesApril 2005 Withsloutionapi-3755462No ratings yet

- DEC Lab Experiments - 2017aDocument5 pagesDEC Lab Experiments - 2017aManjeet SinghNo ratings yet

- Aprilmay 2009Document8 pagesAprilmay 2009Viswa ChaitanyaNo ratings yet

- Faculty of Engineering: Circuits and Signals EEL 2186 TRIMESTER 1 (2014/2015)Document7 pagesFaculty of Engineering: Circuits and Signals EEL 2186 TRIMESTER 1 (2014/2015)Rameshkumar JayaramanNo ratings yet

- EC Lab ManualsDocument53 pagesEC Lab ManualsArish AliNo ratings yet

- 18 MHC 205 JDocument3 pages18 MHC 205 JSem 4thNo ratings yet

- Guessing Papers 1-2-12th Electronics Sub Code C2Document6 pagesGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922No ratings yet

- June July 2017 PDFDocument2 pagesJune July 2017 PDFmabhatNo ratings yet

- IcaDocument2 pagesIcaapi-279049687No ratings yet

- Ec1313 Dec07 Question PaperDocument3 pagesEc1313 Dec07 Question PapersrwaseemahamedNo ratings yet

- ESD TutoDocument5 pagesESD TutoSwaroop MohapatraNo ratings yet

- Parameterize A Lookup Table-Based MOSFET From SPICE - MATLAB & Simulink - MathWorks IndiaDocument4 pagesParameterize A Lookup Table-Based MOSFET From SPICE - MATLAB & Simulink - MathWorks IndiaSouvik ChatterjeeNo ratings yet

- Expritment No 5Document29 pagesExpritment No 5044 Rohan KanseNo ratings yet

- Pulse and Digital CircuitsDocument8 pagesPulse and Digital CircuitsSatish SmartNo ratings yet

- Pulse and Digital CircuitsDocument8 pagesPulse and Digital CircuitsKota divyasreeNo ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- BIT Nsigned Ultiplier: Charles Hastings David HopkinsDocument19 pagesBIT Nsigned Ultiplier: Charles Hastings David HopkinsRashmi ShankarNo ratings yet

- PSG College of Technology, Coimbatore - 641 004 Semester Examinations, SemesterDocument2 pagesPSG College of Technology, Coimbatore - 641 004 Semester Examinations, SemesterAravindh AadhityaNo ratings yet

- ME862VI-SampleMidSemQuestions 01Document4 pagesME862VI-SampleMidSemQuestions 01Manoj S KNo ratings yet

- IAT-II Question Paper With Solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H PDFDocument10 pagesIAT-II Question Paper With Solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H PDFKavyashreeMNo ratings yet

- Lab 2: Nodal Analysis and Mesh Analysis Techniques: V V I V Ia V V I V Ib V I V V IDocument5 pagesLab 2: Nodal Analysis and Mesh Analysis Techniques: V V I V Ia V V I V Ib V I V V Igurdian skyNo ratings yet

- Assembly Mid AnswerDocument5 pagesAssembly Mid AnswerskpheroNo ratings yet

- LDICA 10M QuestionsDocument2 pagesLDICA 10M Questionsdeepa reddyNo ratings yet

- ST - Anne'S: Multiple Choice Questions UNIT-2 (50X1 50 Marks)Document6 pagesST - Anne'S: Multiple Choice Questions UNIT-2 (50X1 50 Marks)St. Anne's CET (EEE Department)No ratings yet

- ESim Lab ManualDocument61 pagesESim Lab ManualDhana PrasadNo ratings yet

- Digital Electronic Circuits (ELE-208) RCSDocument2 pagesDigital Electronic Circuits (ELE-208) RCSSudhakar JoshiNo ratings yet

- Digital LabDocument51 pagesDigital LabBala SubramanianNo ratings yet

- E415 Ec415 Ic Analysis Design and ApplicationsDocument2 pagesE415 Ec415 Ic Analysis Design and ApplicationsvijaykumarNo ratings yet

- Cad Exp ManualDocument23 pagesCad Exp ManualRavindra KumarNo ratings yet

- AVR Microcontroller TestDocument9 pagesAVR Microcontroller TestNiranjan AgravatNo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.ManimegalaiNo ratings yet

- r05321404 Linear and Digital Ic ApplicationsDocument7 pagesr05321404 Linear and Digital Ic ApplicationsSRINIVASA RAO GANTANo ratings yet

- Experiment 1 - Leds and 7-Segment Display (Part 1) : A. Learning OutcomesDocument10 pagesExperiment 1 - Leds and 7-Segment Display (Part 1) : A. Learning OutcomesBianca ReyNo ratings yet

- Final Apr 03 SolnsDocument16 pagesFinal Apr 03 Solnsapi-3755462No ratings yet

- Analog Circuits and DesignDocument4 pagesAnalog Circuits and Designlalitkumar bannagareNo ratings yet

- V Semester B.Tech (Electrical & Electronics Engineering) End Semester Examinations, November 2017Document2 pagesV Semester B.Tech (Electrical & Electronics Engineering) End Semester Examinations, November 2017DuoDrenchNo ratings yet

- Lab Manual Advanced MicrocontrollerDocument79 pagesLab Manual Advanced MicrocontrollertrippinNo ratings yet

- GARCH Models: Structure, Statistical Inference and Financial ApplicationsFrom EverandGARCH Models: Structure, Statistical Inference and Financial ApplicationsRating: 5 out of 5 stars5/5 (1)

- Btech Syllabus Cse 2018 31545Document100 pagesBtech Syllabus Cse 2018 31545Yakshit JoshiNo ratings yet

- MSK ModulationDocument31 pagesMSK Modulationnassr_ismailNo ratings yet

- 4-Bit Counter Using Modified Master - Slave Edge Triggered RegisterDocument20 pages4-Bit Counter Using Modified Master - Slave Edge Triggered Registermilanjauhari0% (1)

- Seca - 374 Baby Scale Service ManualDocument19 pagesSeca - 374 Baby Scale Service ManualWaseem AlmuhtasebNo ratings yet

- Instrucciones Basicas WinproladderDocument38 pagesInstrucciones Basicas Winproladderjose_rojas_574239No ratings yet

- Toshiba Prosec T1 T1S PLCsDocument19 pagesToshiba Prosec T1 T1S PLCsDaniel BarrosNo ratings yet

- Fast Binary Counters and Compressors Generated by Sorting NetworkDocument11 pagesFast Binary Counters and Compressors Generated by Sorting Networkpsathishkumar1232544No ratings yet

- Esd-05-15 (Fraucsher Axle Counter)Document26 pagesEsd-05-15 (Fraucsher Axle Counter)RupeshAkreNo ratings yet

- HCF4020Document11 pagesHCF4020jnax101No ratings yet

- Digital Electronics Question BankDocument34 pagesDigital Electronics Question Banksujithaa13100% (1)

- AN - MTN.01 Architecture For EtherCAT Master PDFDocument18 pagesAN - MTN.01 Architecture For EtherCAT Master PDFMarcelo MatosNo ratings yet

- Unit-4 PLCDocument100 pagesUnit-4 PLCKANISHKAR Hem SankarNo ratings yet

- CD 4 ReDocument4 pagesCD 4 ReTathagata GhoshNo ratings yet

- Contador Frecuencia 1-50Document4 pagesContador Frecuencia 1-50jose100% (2)

- COA Lab FileDocument25 pagesCOA Lab FileChetan MittalNo ratings yet

- Digital StopwatchDocument3 pagesDigital StopwatchAsim SaleemNo ratings yet

- Hardwired ControlDocument3 pagesHardwired ControlHulk ManNo ratings yet

- HDL Lab Manual For VTU Syllabus (10ECL48)Document64 pagesHDL Lab Manual For VTU Syllabus (10ECL48)Ravikiran B A100% (4)

- S.V.University, Tirupati: Semester: IiDocument13 pagesS.V.University, Tirupati: Semester: IiMallikaNo ratings yet

- 7SR23 DAD Complete Technical ManualDocument222 pages7SR23 DAD Complete Technical Manualsvanand88No ratings yet

- Rexroth Inline Modules PDFDocument26 pagesRexroth Inline Modules PDFhemNo ratings yet

- 7SR11 and 7SR12 Argus: Answers For Infrastructure & CitiesDocument24 pages7SR11 and 7SR12 Argus: Answers For Infrastructure & CitiesSumith VkNo ratings yet

- PAPER EI (2) by Pankaj SirDocument247 pagesPAPER EI (2) by Pankaj SirMahesh SinghNo ratings yet

- Basket 3 PDFDocument98 pagesBasket 3 PDFSadhan PadhiNo ratings yet

- MicroprocessorDocument51 pagesMicroprocessorBishal TiwariNo ratings yet

- Tutorial 1 15Document13 pagesTutorial 1 15Charan Kanwal SinghNo ratings yet

- Create Sinewcwes Using Digital IC's: 6 New CircuitsDocument4 pagesCreate Sinewcwes Using Digital IC's: 6 New CircuitsNatanael ManriqueNo ratings yet

- HDL Lab Manual VTUDocument63 pagesHDL Lab Manual VTUSyed MisbahNo ratings yet

- Digital CounterDocument18 pagesDigital CounterbotakezuNo ratings yet

- BSC Physics Hon 482010Document64 pagesBSC Physics Hon 482010Venugopal ReddyvariNo ratings yet