Professional Documents

Culture Documents

74LS109

Uploaded by

jaja558Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74LS109

Uploaded by

jaja558Copyright:

Available Formats

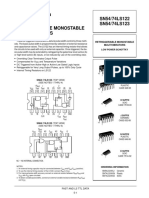

SN54/74LS109A

DUAL JK POSITIVE

EDGE-TRIGGERED FLIP-FLOP

The SN54 / 74LS109A consists of two high speed completely independent

transition clocked JK flip-flops. The clocking operation is independent of rise

and fall times of the clock waveform. The JK design allows operation as a D DUAL JK POSITIVE

flip-flop by simply connecting the J and K pins together. EDGE-TRIGGERED FLIP-FLOP

LOW POWER SCHOTTKY

LOGIC DIAGRAM

SET (SD)

5(11)

Q

CLEAR (CD) 6(10) J SUFFIX

1(15) CERAMIC

CLOCK CASE 620-09

4(12) 16

1

Q

7(9)

J

2(14)

K N SUFFIX

3(13) PLASTIC

16 CASE 648-08

1

D SUFFIX

SOIC

16

1 CASE 751B-03

MODE SELECT — TRUTH TABLE

INPUTS OUTPUTS

OPERATING MODE ORDERING INFORMATION

SD CD J K Q Q

SN54LSXXXJ Ceramic

Set L H X X H L

SN74LSXXXN Plastic

Reset (Clear) H L X X L H

SN74LSXXXD SOIC

*Undetermined L L X X H H

Load “1” (Set) H H h h H L

Hold H H l h q q

Toggle H H h l q q

Load “0” (Reset) H H l l L H LOGIC SYMBOL

* Both outputs will be HIGH while both SD and CD are LOW, but the output states

are unpredictable if SD and CD go HIGH simultaneously. 5 11

H, h = HIGH Voltage Level

L, I = LOW Voltage Level J SD Q 6 14 J SD

2 Q 10

X = Don’t Care

l, h (q) = Lower case letters indicate the state of the referenced input (or output) CP 12 CP

4

l, h (q) = one set-up time prior to the LOW to HIGH clock transition.

7 13

3 K C Q K C Q 9

D D

1 15

VCC = PIN 16

GND = PIN 8

FAST AND LS TTL DATA

5-1

SN54/74LS109A

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

VCC Supply Voltage 54 4.5 5.0 5.5 V

74 4.75 5.0 5.25

TA Operating Ambient Temperature Range 54 – 55 25 125 °C

74 0 25 70

IOH Output Current — High 54, 74 – 0.4 mA

IOL Output Current — Low 54 4.0 mA

74 8.0

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

S b l

Symbol P

Parameter Min Typ Max U i

Unit T

Test C di i

Conditions

Guaranteed Input HIGH Voltage for

VIH Input HIGH Voltage 2.0 V

All Inputs

54 0.7 Guaranteed Input

p LOW Voltage

g for

VIL Input LOW Voltage V

74 0.8 All Inputs

VIK Input Clamp Diode Voltage – 0.65 – 1.5 V VCC = MIN, IIN = – 18 mA

54 25

2.5 35

3.5 V VCC = MIN

MIN,, IOH = MAX,

MAX, VIN = VIH

VOH O

Output HIGH Voltage

V l

74 2.7 3.5 V or VIL per Truth Table

54, 74 0.25 0.4 V IOL = 4.0 mA VCC = VCC MIN,

VOL Output LOW Voltage VIN = VIL or VIH

74 0.35 0.5 V IOL = 8.0 mA per Truth Table

Input HIGH Current

J, K, Clock 20 µA VCC = MAX, VIN = 2.7 V

IIH Set, Clear 40

J, K, Clock 0.1

mA VCC = MAX, VIN = 7.0 V

Set, Clear 0.2

Input LOW Current

IIL J, K, Clock – 0.4 mA VCC = MAX, VIN = 0.4 V

Set, Clear – 0.8

IOS Output Short Circuit Current (Note 1) – 20 – 100 mA VCC = MAX

ICC Power Supply Current 8.0 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS (TA = 25°C, VCC = 5.0 V)

Limits

S b l

Symbol P

Parameter Min Typ Max U i

Unit T

Test C

Conditions

di i

fMAX Maximum Clock Frequency 25 33 MHz

VCC = 5.0

50V

tPLH 13 25 ns

Clock Clear

Clock, Clear, Set to Output CL = 15 pF

tPHL 25 40 ns

AC SETUP REQUIREMENTS (TA = 25°C, VCC = 5.0 V)

Limits

S b l

Symbol P

Parameter Min Typ Max U i

Unit T

Test C

Conditions

di i

tW Clock High Clear, Set Pulse Width 25 ns

Data Setup

p Time — HIGH 20 ns

ts VCC = 5

5.0

0V

Data Setup Time — LOW 20 ns

th Hold time 5.0 ns

FAST AND LS TTL DATA

5-2

You might also like

- 74LS112Document2 pages74LS112jaja558No ratings yet

- Datasheet 74ls74Document3 pagesDatasheet 74ls74minhquyen_130689No ratings yet

- Dual D-Type Positive Edge-Triggered Flip-Flop SN54/74LS74A: Low Power SchottkyDocument3 pagesDual D-Type Positive Edge-Triggered Flip-Flop SN54/74LS74A: Low Power Schottkygd8uj123100% (1)

- 74LS113Document2 pages74LS113jaja558No ratings yet

- 74LS73N DatasheetDocument3 pages74LS73N DatasheetHennie SerfonteinNo ratings yet

- 74LS76Document2 pages74LS76manjunath212coolNo ratings yet

- 74LS112Document4 pages74LS112Rick CastilloNo ratings yet

- Sn74ls76a DDocument5 pagesSn74ls76a Djuanmmm41No ratings yet

- Dual JK Negative Edge-Triggered Flip-Flop SN54/74LS114A: Low Power SchottkyDocument4 pagesDual JK Negative Edge-Triggered Flip-Flop SN54/74LS114A: Low Power SchottkyThoif ZaraNo ratings yet

- Dual JK Negative Edge-Triggered Flip-Flop SN54/74LS113A: Low Power SchottkyDocument3 pagesDual JK Negative Edge-Triggered Flip-Flop SN54/74LS113A: Low Power SchottkyDivianisOktaviyaniNo ratings yet

- 74LS173Document4 pages74LS173jaja558No ratings yet

- 74LS375Document3 pages74LS375jaja558No ratings yet

- Quad D Flip-Flop SN54/74LS175: Low Power SchottkyDocument5 pagesQuad D Flip-Flop SN54/74LS175: Low Power SchottkyNicolasNo ratings yet

- 74LS42 PDFDocument3 pages74LS42 PDFbeesahNo ratings yet

- 74LS174Document3 pages74LS174jaja558No ratings yet

- Quad Set-Reset Latch SN54/74LS279: Low Power SchottkyDocument5 pagesQuad Set-Reset Latch SN54/74LS279: Low Power Schottkytzf32799No ratings yet

- 74LS151Document3 pages74LS151Kang RoyNo ratings yet

- 74LS165Document6 pages74LS165jaja558No ratings yet

- 74 Ls 138Document3 pages74 Ls 138RushabhShahNo ratings yet

- 74LS138 EdDocument2 pages74LS138 EdThiago AlvesNo ratings yet

- Datasheet - Live: HD74HC273Document8 pagesDatasheet - Live: HD74HC273OskarNo ratings yet

- 74LS125ADocument5 pages74LS125Abl19cm7No ratings yet

- 74LS125Document3 pages74LS125jaja558No ratings yet

- Synchronous Presettable BCD Decade Counter MC74F160A MC74F162ADocument4 pagesSynchronous Presettable BCD Decade Counter MC74F160A MC74F162AdavidNo ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument6 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataAmirNo ratings yet

- SN74LS74A Dual D-Type Positive Edge-Triggered Flip-Flop: LOW Power SchottkyDocument8 pagesSN74LS74A Dual D-Type Positive Edge-Triggered Flip-Flop: LOW Power SchottkyjannamuNo ratings yet

- Compuerta 74 LS132Document3 pagesCompuerta 74 LS132richarbmwNo ratings yet

- 74LS155Document4 pages74LS155jaja558No ratings yet

- Onsms12244 1Document8 pagesOnsms12244 1HeartBraveNo ratings yet

- MC74HC04A Hex Inverter: High Performance Silicon Gate CMOSDocument9 pagesMC74HC04A Hex Inverter: High Performance Silicon Gate CMOSjavierNo ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument6 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataMuhammad Rizwan Haider DurraniNo ratings yet

- Datasheet 74ls151 PDFDocument5 pagesDatasheet 74ls151 PDFYoshaniNo ratings yet

- BlitzEssentials V2Document16 pagesBlitzEssentials V2Heitor MedeirosNo ratings yet

- SN54/74LS640 SN54/74LS641 SN54/74LS642 SN54/74LS645: Low Power SchottkyDocument4 pagesSN54/74LS640 SN54/74LS641 SN54/74LS642 SN54/74LS645: Low Power SchottkyCharbel TadrosNo ratings yet

- 74LS242Document3 pages74LS242jaja558No ratings yet

- Wiring Diagram: Noise Filter PowerDocument4 pagesWiring Diagram: Noise Filter Powervoicedont dieNo ratings yet

- SN54ACT574, SN74ACT574 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsDocument6 pagesSN54ACT574, SN74ACT574 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsYenco Barliza DiazNo ratings yet

- 74LS157Document3 pages74LS157jaja558No ratings yet

- 4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyDocument4 pages4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyLoth Matheus Barba MazaNo ratings yet

- TTL Ic 7448Document3 pagesTTL Ic 7448haseeb ahmad ch.0% (1)

- 4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyDocument5 pages4-Bit Binary Full Adder With Fast Carry SN54/74LS283: Low Power SchottkyJessica RojasNo ratings yet

- Data Sheet Pic16f886Document5 pagesData Sheet Pic16f886cesar beltran agustinNo ratings yet

- 74LS377Document5 pages74LS377jaja558No ratings yet

- Dual Decade Counter Dual 4-Stage Binary Counter SN54/74LS390 SN54/74LS393Document5 pagesDual Decade Counter Dual 4-Stage Binary Counter SN54/74LS390 SN54/74LS393gd8uj123No ratings yet

- SN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power SchottkyDocument5 pagesSN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power Schottkygd8uj123No ratings yet

- SN5474LS95B 4-Bit Shift RegisterDocument6 pagesSN5474LS95B 4-Bit Shift RegisterhayssamNo ratings yet

- 74LS148DDocument8 pages74LS148Depahk3631No ratings yet

- LS PDFDocument8 pagesLS PDFEfrain Nina MaytaNo ratings yet

- 74LS151Document3 pages74LS151Kang RoyNo ratings yet

- 74LS155Document4 pages74LS155jaja558No ratings yet

- Dual Monostable Multivibrators With Schmitt-Trigger Inputs SN54/74LS221Document5 pagesDual Monostable Multivibrators With Schmitt-Trigger Inputs SN54/74LS221parsa mahvisNo ratings yet

- 74LS00Document2 pages74LS00jaja558No ratings yet

- 74LS01Document2 pages74LS01amarch65No ratings yet

- Datos 74LS166-2Document5 pagesDatos 74LS166-2valarconbravoNo ratings yet

- 417680Document6 pages417680rakeshNo ratings yet

- DM 74 Ls 00Document6 pagesDM 74 Ls 00LiviaMariaNo ratings yet

- Quad 2-Input Multiplexer SN54/74LS158: Low Power SchottkyDocument3 pagesQuad 2-Input Multiplexer SN54/74LS158: Low Power SchottkyEden K.CNo ratings yet

- 74LS90 Contador AsincronoDocument7 pages74LS90 Contador AsincronoFISRAELGRNo ratings yet

- 7402 LSDocument2 pages7402 LSHafizhan Hudani GhazzanNo ratings yet

- SN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power SchottkyDocument5 pagesSN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power Schottkygd8uj123No ratings yet

- 74LS290Document7 pages74LS290jaja558No ratings yet

- Ficha Tecnica 74LS04 Compuerta NOTDocument2 pagesFicha Tecnica 74LS04 Compuerta NOTSteven BallardNo ratings yet

- SN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power SchottkyDocument5 pagesSN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power Schottkygd8uj123No ratings yet

- 4-Bit Arithmetic Logic Unit SN54/74LS181: Low Power SchottkyDocument7 pages4-Bit Arithmetic Logic Unit SN54/74LS181: Low Power SchottkyMauro JimenezNo ratings yet

- 74LS54Document2 pages74LS54jaja558No ratings yet

- 74LS86 PDFDocument3 pages74LS86 PDFYouness AmdiazNo ratings yet

- 74LS91Document4 pages74LS91jaja558No ratings yet

- Datasheet 74ls83 PDFDocument3 pagesDatasheet 74ls83 PDFLioni Dávila AguilarNo ratings yet

- 74LS76ADocument7 pages74LS76ALikasmita DaleiNo ratings yet

- KPLABS Course - Cloud Practitioner D1 PDFDocument8 pagesKPLABS Course - Cloud Practitioner D1 PDFSree Harsha Ananda RaoNo ratings yet

- NAME: Sai Kumar.p REG - NO:18BCA0079: Assessment 5 Ita1005 - Database Management Systems LabDocument12 pagesNAME: Sai Kumar.p REG - NO:18BCA0079: Assessment 5 Ita1005 - Database Management Systems LabSaikumar P 18BCA0079No ratings yet

- MBD Blockchain e Brochure 6 MonthsDocument22 pagesMBD Blockchain e Brochure 6 MonthsZrake 24No ratings yet

- Code (Edited)Document8 pagesCode (Edited)Khương MaiNo ratings yet

- Components of Project ReportDocument2 pagesComponents of Project Reportambrosialnectar100% (3)

- FEA Top 10 Analysis ChecksDocument4 pagesFEA Top 10 Analysis ChecksGarry TaylorNo ratings yet

- Yamaha Psr-Ew400 SMDocument57 pagesYamaha Psr-Ew400 SMGabriel SaucedoNo ratings yet

- Internet Censorship NodrmDocument352 pagesInternet Censorship NodrmulixesfoxNo ratings yet

- Dogar Brothers MCQs by Haadi 03037008586 PDFDocument178 pagesDogar Brothers MCQs by Haadi 03037008586 PDFMujeeb JuttNo ratings yet

- Young's Natural Representation of S - 4Document13 pagesYoung's Natural Representation of S - 4Quinton WestrichNo ratings yet

- Set B and C Text With Work BookDocument146 pagesSet B and C Text With Work BookPhyo ThutaNo ratings yet

- Dual Usage - Low Voltage & High Voltage Universal Lithium MobileDocument2 pagesDual Usage - Low Voltage & High Voltage Universal Lithium MobileFernando medina medinaNo ratings yet

- LCCM Class Activity Audit Program - Nov 16 2020-StudentDocument4 pagesLCCM Class Activity Audit Program - Nov 16 2020-StudentLeane MarcoletaNo ratings yet

- DBMSDocument11 pagesDBMSOperation ResearchNo ratings yet

- 350201F - O&m - I&mdocs 500-55 (-Ce)Document250 pages350201F - O&m - I&mdocs 500-55 (-Ce)Euler Mairena100% (1)

- Igcse Computer Science WorkbookDocument81 pagesIgcse Computer Science WorkbookWaqas Asad86% (7)

- Lawyers, Cloud Computing and Innovation (How Cloud Computing Facilitates Innovation in The Delivery of Legal Services)Document19 pagesLawyers, Cloud Computing and Innovation (How Cloud Computing Facilitates Innovation in The Delivery of Legal Services)ainNo ratings yet

- Conventional Detector Bases: Ns6 and Ns4 Series BaseDocument2 pagesConventional Detector Bases: Ns6 and Ns4 Series Baseuygar öztürkNo ratings yet

- Instantaneous Frequency Estimation Using TVAR ModelingDocument22 pagesInstantaneous Frequency Estimation Using TVAR ModelingravitadishettiNo ratings yet

- Experimental Evaluation of Efficient Sparse Matrix DistributionsDocument8 pagesExperimental Evaluation of Efficient Sparse Matrix DistributionsFani LizNo ratings yet

- DS-400 Semi-Auto Chemistry Analyzer CatalogDocument1 pageDS-400 Semi-Auto Chemistry Analyzer CatalogJason WangNo ratings yet

- Transcript Russia CryptoDocument13 pagesTranscript Russia CryptoSean PowersNo ratings yet

- Republic of The Philippines Social Security System MemberDocument1 pageRepublic of The Philippines Social Security System MemberMaeNo ratings yet

- Fol500 002 14 Rev04Document8 pagesFol500 002 14 Rev04Franco DeottoNo ratings yet

- Web Scraping Using Python: A Step by Step Guide: September 2019Document7 pagesWeb Scraping Using Python: A Step by Step Guide: September 2019abhinavtechnocratNo ratings yet

- Steps in Constructing A Frequency DistributionDocument1 pageSteps in Constructing A Frequency DistributionJason MontesaNo ratings yet

- HDSD Masterscan D70 User GuideDocument126 pagesHDSD Masterscan D70 User GuideNguyen binhNo ratings yet

- Brkarc 3980Document144 pagesBrkarc 3980José AlexandreNo ratings yet

- SCM - Oracle Cloud Maintenance Enhancements To Maintenance ProgramsDocument28 pagesSCM - Oracle Cloud Maintenance Enhancements To Maintenance ProgramsMohamed MahmoudNo ratings yet

- Cdcvm-Faq FinalDocument4 pagesCdcvm-Faq Finalspectra testNo ratings yet