10/31/2023

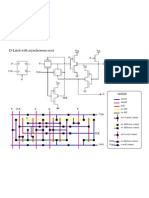

Introduction to RTL, High-Level State Machines,

RTL Design Process

Introduction outputs

inputs

bi bo

FSM

FSM

• Controllers Combinational

– Control input/output: single bit (or just a logic n1

few) representing event or state n0

s1 s0

– Finite-state machine describes

State register

behavior; implemented as state register clk

and combinational logic

• Datapath components

– Data input/output: Multiple bits Register Comparator

collectively representing single entity si

– Datapath components included sians

Register file

registers, adders, ALU, comparators, ALU

register files, etc.

bi bo

• This chapter: custom processors

e

Combinational Register file

– Processor: Controller and datapath logic n1

components working together to n0

s1 s0 ALU

implement an algorithm

State register

Datapath

Controller 2

1

� 10/31/2023

RTL Design: Capture Behavior, Convert to Circuit

• Recall

– Combinational Logic Design

• First step: Capture behavior (using equation

or truth table)

• Remaining steps: Convert to circuit

Capture behavior

– Sequential Logic Design

• First step: Capture behavior (using FSM)

• Remaining steps: Convert to circuit

• RTL Design (the method for creating

Convert to circuit

custom processors)

– First step: Capture behavior (using high-

level state machine, to be introduced)

– Remaining steps: Convert to circuit

RTL Design

High-Level State Machines (HLSMs)

Some behaviors too complex for

equations, truth tables, or FSMs s a

Ex: Soda dispenser

c: bit input, 1 when coin deposited

c Soda

a: 8-bit input having value of deposited coin

d dispenser

s: 8-bit input having cost of a soda processor

d: bit output, processor sets to 1 when total

value of deposited coins equals or exceeds

cost of a soda

FSM can’t represent…

s a 25

8-bit input/output

Storage of current total 25

50

Addition (e.g., 25 + 10) 0 1 0 1 0

c Soda

d dispenser tot:

tot:50

25

0 1 0 processor a

2

� 10/31/2023

RTL Design

HLSMs

s a

High-level state machine (HLSM) 8 8

extends FSM with:

Multi-bit input/output c Soda

dispenser

Local storage d

processor

Arithmetic operations

Inputs: c (bit), a (8 bits), s (8 bits)

Conventions Outputs: d (bit) // '1' dispenses soda

Numbers: Local storage: tot (8 bits)

Single-bit: '0' (single quotes) c

Integer: 0 (no quotes) Add

Multi-bit: “0000” (double quotes) Init Wait

tot:=tot+a

== for equal, := for assignment

a

d:='0' c’ * (tot<s)

Multi-bit outputs must be registered via tot:=0 c’*(tot<s)’

local storage Disp

// precedes a comment

SodaDispenser d:='1'

RTL Design

Ex: Cycles-High Counter

P = total number (in binary) of cycles that m is 1 CountHigh

m

Capture behavior as HLSM clk Preg

Preg required (multibit outputs must be registered) 32

Use to hold count P

CountHigh Inputs: m (bit) CountHigh Inputs: m (bit) CountHigh Inputs: m (bit)

Outputs: P (32 bits) Outputs: P (32 bits) Outputs: P (32 bits)

Local storage: Preg Local storage: Preg Local storage: Preg

S_Clr // Clear Preg to 0s S_Clr // Clear Preg to 0s S_Clr

// Clear Preg to 0s

Preg := 0 Preg := 0 Preg := 0

a

? m' // Wait for m == '1' m' // Wait for m == '1'

S_Wt S_Wt

m m' m

? // Increment Preg

m S_Inc Preg := Preg + 1

(a) (b) (c)

a

6

3

� 10/31/2023

RTL Design

Example: Laser-Based Distance Measurer

T (in seconds)

laser

D

Object of

a

interest

sensor

2D = T sec * 3*108 m/sec

Laser-based distance measurement – pulse laser, measure time T to sense

reflection

8

Laser light travels at speed of light, 3*10 m/sec

8

Distance is thus D = (T sec * 3*10 m/sec) / 2

RTL Design

Example: Laser-Based Distance Measurer

T (in seconds)

B L

laser from button to laser

Laser-based

distance

sensor D 16 measurer S

to display from sensor

Inputs/outputs

B: bit input, from button, to begin measurement

L: bit output, activates laser

S: bit input, senses laser reflection

D: 16-bit output, to display computed distance

4

� 10/31/2023

RTL Design

Example: Laser-Based Distance Measurer

DistanceMeasurer B Laser-based L

Inputs : B (bit), S (bit) 16 distance measurer

Outputs : L (bit), D (16 bits) D S

Local storage: Dreg(16)

a

S0 ?

(first state usually

L := '0' // laser off initializes the system)

Dreg := 0 // distance is 0

Declare inputs, outputs, and local storage

Dreg required for multi-bit output

Create initial state, name it S0

Initialize laser to off (L:='0')

Initialize displayed distance to 0 (Dreg:=0)

Recall: '0' means single bit, 0

means integer

9

RTL Design

Example: Laser-Based Distance Measurer

B Laser-based L

DistanceMeasurer

16 distance measurer

... B' // button not pressed D S

S0 S1 ?

B

L := '0' // button

Dreg := 0 pressed

Add another state, S1, that waits for a button press

B' – stay in S1, keep waiting

B – go to a new state S2 Q: What should S2 do?

A: Turn on the laser

10

5

� 10/31/2023

RTL Design

Example: Laser-Based Distance Measurer

B Laser-based L

16 distance measurer

DistanceMeasurer D S

... B'

S0 S1 S2 S3

B

L := '0' L := '1' L := '0'

Dreg := 0 // laser on // laser off

Add a state S2 that turns on the laser (L:='1')

Then turn off laser (L:='0') in a state S3

Q: What do next?

a

A: Start timer, wait to sense reflection

11

RTL Design

Example: Laser-Based Distance Measurer

DistanceMeasurer Inputs : B (bit), S (bit) Outputs : L (bit), D (16 bits) B Laser-based L

Local storage: Dreg, Dctr (16 bits) 16 distance measurer

B' S' // no reflection D S

S // reflection

S0 S1 S2 S3 ?

B

L := '0' Dctr := 0 L := '1' L := '0'

Dreg := 0 // reset cycle Dctr := Dctr + 1

count // count cycles

a

Stay in S3 until sense reflection (S)

To measure time, count cycles while in S3

To count, declare local storage Dctr

Initialize Dctr to 0 in S1. In S2 would have been O.K. too.

Don't forget to initialize local storage—common mistake

Increment Dctr each cycle in S3

12

6

� 10/31/2023

RTL Design

Example: Laser-Based Distance Measurer

DistanceMeasurer Inputs : B (bit), S (bit) Outputs : L (bit), D (16 bits) B Laser-based L

Local storage: Dreg, Dctr (16 bits) 16 distance measurer

D S

B' S'

S0 S1 S2 S3 S4

B S

L := '0' Dctr := 0 L := '1' L := '0' Dreg := Dctr/2

Dreg := 0 Dctr := Dctr+1 // calculate D

Once reflection detected (S), go to new state S4

Calculate distance

8

Assuming clock frequency is 3x10 , Dctr holds number of meters, so Dreg:=Dctr/2

After S4, go back to S1 to wait for button again

13