Professional Documents

Culture Documents

HW 7

HW 7

Uploaded by

pskumarvlsipdOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HW 7

HW 7

Uploaded by

pskumarvlsipdCopyright:

Available Formats

EECS 151/251A Homework 7

Due Monday, March 19th , 2018

Problem 1: Hazard Drills

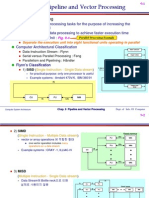

Say you have a simple 3 stage in-order pipelined processor with the following stages:

1. Instruction fetch and decode

2. Execute

3. Writeback

Registers are read in the first stage and are written to in the third stage. Writes to registers occur

at the end of a cycle while reads occur at the start.

(a) Assume that data forwarding isn’t implemented in this datapath. How many cycles will the

following assembly take to execute?

add x0, x1, x2

sub x2, x3, x4

add x2, x3, x4

or x3, x2, x0

and x4, x1, x0

xor x2, x1, x4

add x1, x2, x0

(b) What is the CPI of this process for this block of code?

Problem 2: Microarchitecture

In the circuit below, block D is a delay element (i.e. register) and block A performs multiplication

by A.

(a) Write down the expression for y[n].

EECS 151/251A Homework 7 2

(b) Unroll the loop such that each iteration covers two iterations of the original case. Substitute

for y[n − 1] using the expression from (a) and then draw the resulting block diagram.

(c) Try to pipeline your design from part b.

Problem 3: True or False?

(a) Consider a single-cycle MIPS processor with only four instructions, add, sub, lw, and sw,

running programs where each of the four instructions occur with equal probability. If it were

practical to do so, varying the clock period on a per instruction basis would result in a overall

performance improvement of at least 10%.

(b) Multi-threading is a known way to help eliminate hazards in pipelined processors. Instructions

from multiple independent programs (or threads) are interleaved in the pipeline. This is

equivalent to the “C-slow” technique we presented for optimal pipeline utilization.

Consider a standard 5-stage MIPS pipeline implementation, but with no bypassing or for-

warding circuitry. Multithreading this processor with 4 independent interleaved instruction

streams is sufficient to eliminate all control and data hazards.

Problem 4: DDCA Exercise 8.12

You are building an instruction cache for a MIPS processor. It has a total capacity of 4C = 2c+2 .

It is N = 2n -way set-associative (N ≥ 8), with a block size of b = 2b bytes (b ≥ 8). Give your

answers to the following questions in terms of these parameters:

(a) Which bits of the address are used to select a word within a block?

(b) Which bits of the address are used to select the set within the cache?

(c) How many bits are in each tag?

(d) How many tag bits are in the entire cache?

You might also like

- Chevrolet Transfer Case 231Document8 pagesChevrolet Transfer Case 231jorge antonio guillenNo ratings yet

- ch09 Morris ManoDocument15 pagesch09 Morris ManoYogita Negi RawatNo ratings yet

- After How Much Time Concrete Should Be RejectedDocument7 pagesAfter How Much Time Concrete Should Be RejectedDEBOPRASAD BISWAS100% (1)

- Neet Digestion systemMCQDocument58 pagesNeet Digestion systemMCQiGadgetProNo ratings yet

- Acid Mine Drainage Workshop - 1995Document102 pagesAcid Mine Drainage Workshop - 1995Scott DownsNo ratings yet

- Alarm & ESD Set Point-R01Document5 pagesAlarm & ESD Set Point-R01Hossein Zohdi RadNo ratings yet

- Homework3 Solution v2Document41 pagesHomework3 Solution v2razi haiderNo ratings yet

- CENG400-Final-Fall 2014Document11 pagesCENG400-Final-Fall 2014Mohamad IssaNo ratings yet

- Name:: CMSC 313 Fall 2001 Computer Organization & Assembly Language Programming Exam 1Document11 pagesName:: CMSC 313 Fall 2001 Computer Organization & Assembly Language Programming Exam 1Mahadeva HerbalsNo ratings yet

- Gate Sample PaperDocument7 pagesGate Sample Papershettyashwin19No ratings yet

- Ecen 324 Practice Exam: Midterm #2: Int Unknown (A B && B C: B B A && A C: A 1: C )Document5 pagesEcen 324 Practice Exam: Midterm #2: Int Unknown (A B && B C: B B A && A C: A 1: C )ThatOnePerson123No ratings yet

- Solutions To Set 8Document18 pagesSolutions To Set 8kitana_sectNo ratings yet

- 2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Document7 pages2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Avik MitraNo ratings yet

- Cs2106 1617s1 Midterm SolutionDocument13 pagesCs2106 1617s1 Midterm SolutionReynard ArdianNo ratings yet

- hệ điều hànhDocument18 pageshệ điều hànhfranklampardnumber8No ratings yet

- MCS 012 Previous Year Question Papers by IgnouassignmentguruDocument96 pagesMCS 012 Previous Year Question Papers by IgnouassignmentguruMayank ChoudharyNo ratings yet

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Document4 pagesIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelNo ratings yet

- CSE 332 L 14 Short & 15 - 24th & 26th Sep 2020Document28 pagesCSE 332 L 14 Short & 15 - 24th & 26th Sep 2020Nz SaadNo ratings yet

- 1b10, Computer Architecture: Answer Any Three Questions., 2.5 HoursDocument5 pages1b10, Computer Architecture: Answer Any Three Questions., 2.5 HoursVenki MeenuNo ratings yet

- MC251Document10 pagesMC251Deepak SinghNo ratings yet

- Future SoftDocument5 pagesFuture Softashokno1985No ratings yet

- CS211 ExamDocument10 pagesCS211 ExamTetzNo ratings yet

- GATE QnADocument5 pagesGATE QnAGaurav MoreNo ratings yet

- ECE 341 Final Exam Solution: Problem No. 1 (10 Points)Document9 pagesECE 341 Final Exam Solution: Problem No. 1 (10 Points)bsudheertecNo ratings yet

- Time: 03 Hours Maximum Marks: 100: (Autonomous Institution Under VTU) VI Semester B. E. Examinations, May/Jun 14Document3 pagesTime: 03 Hours Maximum Marks: 100: (Autonomous Institution Under VTU) VI Semester B. E. Examinations, May/Jun 14PrateekMandiNo ratings yet

- Technical QuestionsDocument15 pagesTechnical Questionscse_soloNo ratings yet

- Your Name:: Final ExamDocument9 pagesYour Name:: Final ExamDaniel EcheverriaNo ratings yet

- Technical Questions: CalypsoDocument17 pagesTechnical Questions: CalypsoPradeep TiwariNo ratings yet

- Combined Bank: Cloud IT Solution MCQDocument23 pagesCombined Bank: Cloud IT Solution MCQSakib MuhaiminNo ratings yet

- Midtermarch 2Document9 pagesMidtermarch 2Ghina BaassiriNo ratings yet

- Comp Architecture Sample QuestionsDocument9 pagesComp Architecture Sample QuestionsMohamaad SihatthNo ratings yet

- EC360 - Computer CommunicationDocument9 pagesEC360 - Computer CommunicationTtfcfgbbNo ratings yet

- ECE408 2012 Practice Exam1Document10 pagesECE408 2012 Practice Exam1shahdabdelrhman8xNo ratings yet

- Test OSDocument5 pagesTest OSankitamaheshwariNo ratings yet

- EXAMDec2012 SolutionDocument8 pagesEXAMDec2012 Solutionخالد ناهض نايف نجمNo ratings yet

- Quick Heal Placement Paper February 2012Document2 pagesQuick Heal Placement Paper February 2012nishantnishiNo ratings yet

- NPTEL CC Assignment 0Document6 pagesNPTEL CC Assignment 0Arun KumarNo ratings yet

- HW 9Document3 pagesHW 9pskumarvlsipdNo ratings yet

- Question #1 (9 Marks) : Operating Systems (CS C372) Comprehensive Exam RegularDocument4 pagesQuestion #1 (9 Marks) : Operating Systems (CS C372) Comprehensive Exam RegularVishal MittalNo ratings yet

- Bài kiểm tra cuối kỳ - Xem lại lần làm thửDocument9 pagesBài kiểm tra cuối kỳ - Xem lại lần làm thử21021618 Vương Hoàng MinhNo ratings yet

- Btech Cs 3 Sem Computer Organization and Architecture rcs302 2022Document2 pagesBtech Cs 3 Sem Computer Organization and Architecture rcs302 2022GsgsgdhNo ratings yet

- Q1: Choose The Correct AnswerDocument15 pagesQ1: Choose The Correct AnswerMohammed ShannenNo ratings yet

- Answer Key CSE 105 II - CIA PART A (10X2 20)Document4 pagesAnswer Key CSE 105 II - CIA PART A (10X2 20)K SriNo ratings yet

- QuestionsdsaDocument26 pagesQuestionsdsaSiddharth SharmaNo ratings yet

- ECE 452: Computer Organization and DesignDocument9 pagesECE 452: Computer Organization and Designdermeister1988No ratings yet

- 2008 FinalExam SoCN Final Master SolutionDocument10 pages2008 FinalExam SoCN Final Master SolutionBobby BeamanNo ratings yet

- Logic Design LaboratoryDocument9 pagesLogic Design LaboratoryKerim NjuhovićNo ratings yet

- Examination Paper: May/June 201 9 COMP2211-WE01Document6 pagesExamination Paper: May/June 201 9 COMP2211-WE01africa threeNo ratings yet

- Computer Architecture: CS/B.TECH (CSE-NEW) /SEM-4/CS-403/2012Document8 pagesComputer Architecture: CS/B.TECH (CSE-NEW) /SEM-4/CS-403/2012Avik MitraNo ratings yet

- Solutions To Set 5Document5 pagesSolutions To Set 5kitana_sectNo ratings yet

- Pdfjoiner PDFDocument26 pagesPdfjoiner PDFbakosey323No ratings yet

- MCS 012Document118 pagesMCS 012SongYak YamNo ratings yet

- 計組考古Document13 pages計組考古e24114100No ratings yet

- Punjab Technical University: Computer ArchitectureDocument2 pagesPunjab Technical University: Computer ArchitecturesandeepaprNo ratings yet

- Tute AnswersDocument11 pagesTute AnswerschulaNo ratings yet

- Axes - Placement Sample Question Papers: Micro ProcessorDocument7 pagesAxes - Placement Sample Question Papers: Micro ProcessorNagaValliNo ratings yet

- MCA (Revised) Term-End Examination N-R-R) December, 2013 Mcs-012: Computer Organisation & Assembly Language ProgrammingDocument3 pagesMCA (Revised) Term-End Examination N-R-R) December, 2013 Mcs-012: Computer Organisation & Assembly Language ProgrammingpritywizNo ratings yet

- CSF204 CS214 OS Garima End Garima Verma MDocument2 pagesCSF204 CS214 OS Garima End Garima Verma Mshivangi SinghNo ratings yet

- Assignment Solution Week11Document5 pagesAssignment Solution Week11Rahi Sarkar100% (1)

- Short Notes To Memorize GateDocument50 pagesShort Notes To Memorize GateappasamiNo ratings yet

- MCS-012 MCA (Revised) TR) Term-End Examination cNI June, 2011 0, - Mcs-012: Computer Organisation & Assembly Language ProgrammingDocument3 pagesMCS-012 MCA (Revised) TR) Term-End Examination cNI June, 2011 0, - Mcs-012: Computer Organisation & Assembly Language ProgrammingRajib SahaNo ratings yet

- Final Techquiz QuestionsDocument6 pagesFinal Techquiz QuestionsJayarudranNo ratings yet

- As A Single PDFDocument3 pagesAs A Single PDFauctmetuNo ratings yet

- 10-Pin, 24-Bit, 192 KHZ Stereo D/A Converter: Features DescriptionDocument24 pages10-Pin, 24-Bit, 192 KHZ Stereo D/A Converter: Features DescriptionpskumarvlsipdNo ratings yet

- HW 8Document6 pagesHW 8pskumarvlsipdNo ratings yet

- HW 10Document4 pagesHW 10pskumarvlsipdNo ratings yet

- HW 9Document3 pagesHW 9pskumarvlsipdNo ratings yet

- 1-Bisection Method: Equation Number One (3 X+sin (X) - Exp (X) )Document4 pages1-Bisection Method: Equation Number One (3 X+sin (X) - Exp (X) )seraj sersawiNo ratings yet

- 2.30 SL Elek e PDFDocument45 pages2.30 SL Elek e PDFIsos CellNo ratings yet

- Cs Practical Manas NewDocument58 pagesCs Practical Manas Newswyam sharmaNo ratings yet

- Welding Chrome-Moly Steel: What You Should Know About T-1 WiresDocument22 pagesWelding Chrome-Moly Steel: What You Should Know About T-1 WiresKentDemeterioNo ratings yet

- How Do You Make Paper From A TreeDocument1 pageHow Do You Make Paper From A TreeGeeanNo ratings yet

- Lab 7 Free & Force ConvectionDocument7 pagesLab 7 Free & Force Convectionmahen DinhoNo ratings yet

- CS 8100 Family Error Codes - Error - Err - S - Acq - 10 - PDF - Ethernet - Computer NetworkDocument125 pagesCS 8100 Family Error Codes - Error - Err - S - Acq - 10 - PDF - Ethernet - Computer NetworkAneta DimitrievskiNo ratings yet

- ECE Faculty HandbookDocument48 pagesECE Faculty Handbookamir_shafiq123No ratings yet

- Introduction To Storage Performance TroubleshootingDocument5 pagesIntroduction To Storage Performance TroubleshootingvinoopnvNo ratings yet

- Cell Differentiation and Organogenesis 2Document34 pagesCell Differentiation and Organogenesis 2Dahal Babin100% (1)

- Iron Kingdoms Roleplaying Game Character SheetDocument2 pagesIron Kingdoms Roleplaying Game Character Sheetjoshua vogelNo ratings yet

- Form PDFDocument8 pagesForm PDFChitresh143No ratings yet

- Does Inflation Affect Capital BudgetingDocument15 pagesDoes Inflation Affect Capital BudgetingASSISTANCE P NGWENYANo ratings yet

- Tidsdiskret Pid RegDocument5 pagesTidsdiskret Pid RegLucian GomoescuNo ratings yet

- Tugas Hari PertamaDocument3 pagesTugas Hari PertamaMakmur RidhoNo ratings yet

- MEC 532 Composite MaterialsDocument2 pagesMEC 532 Composite MaterialsSumit SharmaNo ratings yet

- CbetDocument21 pagesCbetManfred GithinjiNo ratings yet

- An Overview of ArtDocument3 pagesAn Overview of ArtsergsNo ratings yet

- Aros Install Manual Version 0.40aDocument30 pagesAros Install Manual Version 0.40aayranayranNo ratings yet

- Improving Market Access For Smallholder Farmers: What Works in Out-Grower Schemes - Evidence From Timor-LesteDocument5 pagesImproving Market Access For Smallholder Farmers: What Works in Out-Grower Schemes - Evidence From Timor-LesteNhialNo ratings yet

- Mission Statement of UfoneDocument1 pageMission Statement of UfoneKamir Shahbaz50% (2)

- CMIT-602-COM-00.08-210001 Execution Management Plan - 0Document17 pagesCMIT-602-COM-00.08-210001 Execution Management Plan - 0Santo KuolNo ratings yet

- Aw y Gin 2011 - Prevalence and Genetic Diversity of Waterborne Pathogenic Viruses in Surface Waters of Tropical Urban CatchmentsDocument13 pagesAw y Gin 2011 - Prevalence and Genetic Diversity of Waterborne Pathogenic Viruses in Surface Waters of Tropical Urban CatchmentsYoNo ratings yet

- Rule 57 Case DigestsDocument4 pagesRule 57 Case DigestsLe Obm SizzlingNo ratings yet

- OM CML720 CANopen Description V05 enDocument24 pagesOM CML720 CANopen Description V05 enMartín Hurtado MongeNo ratings yet