0% found this document useful (0 votes)

66 views14 pagesConcurrent Statement

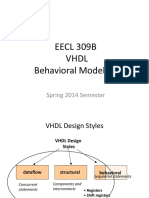

The document discusses concurrent and sequential signal assignment statements in VHDL, highlighting their differences and providing examples of selected signal assignments. It includes VHDL code for a 4:1 multiplexer and a 3:8 decoder using selected signal assignment, as well as conditional signal assignments for designing an 8:1 multiplexer and a 3:8 decoder. The document emphasizes the event-triggered nature of concurrent statements and the importance of order in sequential statements.

Uploaded by

ravipandey1729Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

66 views14 pagesConcurrent Statement

The document discusses concurrent and sequential signal assignment statements in VHDL, highlighting their differences and providing examples of selected signal assignments. It includes VHDL code for a 4:1 multiplexer and a 3:8 decoder using selected signal assignment, as well as conditional signal assignments for designing an 8:1 multiplexer and a 3:8 decoder. The document emphasizes the event-triggered nature of concurrent statements and the importance of order in sequential statements.

Uploaded by

ravipandey1729Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd