Professional Documents

Culture Documents

Instruction Format

Uploaded by

Ashok Rachapalli0 ratings0% found this document useful (0 votes)

19 views33 pagesinstruction format COA

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentinstruction format COA

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

19 views33 pagesInstruction Format

Uploaded by

Ashok Rachapalliinstruction format COA

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

You are on page 1of 33

Instruction Code format, Instruction

Cycle and Instruction Format

Instruction code

• A computer instruction is a binary code that

determines the micro-operations in a

sequence for a computer.

• They are saved in the memory along with the

information. Each computer has its specific

group of instructions.

Instruction code

• They can be categorized into two elements as

Operation codes (Opcodes) and Address.

Opcodes specify the operation for specific

instructions.

• An address determines the registers or the

areas that can be used for that operation.

Operands are definite elements of computer

instruction that show what information is to be

operated on.

Instruction code

• It consists of 12 bits of memory that are required to

define the address as the memory includes 4096 words.

• The 15th bit of the instruction determines the

addressing mode (where direct addressing corresponds

to 0, indirect addressing corresponds to 1).

• Therefore, the instruction format includes 12 bits of

address and 1 bit for the addressing mode, 3 bits are

left for Opcodes.

Instruction code format

Addressing Modes

• Instructions that define the address of a

definite memory location are known as

memory reference instructions.

• The method in which a target address or

effective address is recognized within the

instruction is known as addressing mode.

Addressing Mode

• The address field for instruction can be represented in two

different ways are as follows −

Direct Addressing − It uses the address of the operand.

Indirect Addressing − It facilitates the address as a pointer to

the operand.

• The address of the operand or the target address is called the

effective address.

• Effective Address (EA) − It defines the address that can be

executed as a target address for a branch type instruction or

the address that can be used directly to create an operand

for a computation type instruction, without creating any

changes.

Opcodes

• An opcode is a collection of bits that represents the

basic operations including add, subtract, multiply,

complement, and shift. The total number of

operations provided through the computer

determines the number of bits needed for the

opcode.

• The minimum bits accessible to the opcode should

be n for 2n operations. These operations are

implemented on information that is saved in

processor registers or memory.

Address

• The address is represented as the location where a specific

instruction is constructed in the memory. The address bits

of an instruction code is used as an operand and not as an

address.

• In such methods, the instruction has an immediate

operand. If the second part has an address, the instruction

is referred to have a direct address.

• There is another possibility in the second part including the

address of the operand. This is referred to as an indirect

address. In the instruction code, one bit can signify if the

direct or indirect address is executed.

The figure shows a diagram showing direct

and indirect addresses

Computer Instructions

• Computer instructions are a set of machine language

instructions that a particular processor understands and

executes. A computer performs tasks on the basis of the

instruction provided.

• An instruction comprises of groups called fields. These fields

include:

• The Operation code (Opcode) field which specifies the

operation to be performed.

• The Address field which contains the location of the

operand, i.e., register or memory location.

• The Mode field which specifies how the operand will be

located.

• A basic computer has three instruction code

formats which are:

• Memory - reference instruction

• Register - reference instruction

• Input-Output instruction

Memory - reference instruction

• In Memory-reference instruction, 12 bits of

memory is used to specify an address and one

bit to specify the addressing mode 'I'.

Register Reference Instruction

• The Register-reference instructions are

represented by the Opcode 111 with a 0 in the

leftmost bit (bit 15) of the instruction.

• A Register-reference instruction specifies an

operation on or a test of the AC (Accumulator)

register.

Input-Output instruction

• Just like the Register-reference instruction, an Input-

Output instruction does not need a reference to

memory and is recognized by the operation code 111

with a 1 in the leftmost bit of the instruction. The

remaining 12 bits are used to specify the type of the

input-output operation or test performed.

Basic Computer Instructions

Instruction Cycle

• A program residing in the memory unit of a computer consists

of a sequence of instructions. These instructions are executed

by the processor by going through a cycle for each instruction.

• In a basic computer, each instruction cycle consists of the

following phases:

• Fetch instruction from memory.

• Decode the instruction.

• Read the effective address from memory.

• Execute the instruction.

Instruction Cycle

Instruction Cycle

• Fetch and Decode:- Initially, the program counter PC is

loaded with the address of the first instruction in the

program.

• The sequence counter SC is cleared to 0, providing a

decoded timing signal T0.

• After each clock pulse, SC is incremented by one, so that

the timing signals go through a sequence T0, T1, T2, and

so on.

• The microoperations for the fetch and decode phases can

be specified by the following register transfer statements.

Instruction Cycle

• Since only AR is connected to the address inputs of memory, it

is necessary to transfer the address from PC to AR during the

clock transition associated with timing signal T0

• The instruction read from memory is then placed in the

instruction register IR with the clock transition associated with

timing signal T1

• At the same time, PC is incremented by one to prepare it for

the address of the next instruction in the program. At time T2,

the operation code in IR is decoded, the indirect bit is

transferred to flip-flop I, and the address part of the instruction

is transferred to AR .

• Note that SC is incremented after each clock pulse to produce

the sequence To, T1, and T2

Instruction cycle flowchart

flowchart

• Determine the Type of Instruction:-The timing signal that is active after the

decoding is T3

• During time T3 the control unit determines the type of instruction that was just

read from memory.

• Decoder output D7 is equal to 1 if the operation code is equal to binary 111.

• If D7 = 1 and I = 1, then execute the input output instruction .

• If D7 = 1 and I = 0, then execute the register reference instruction .

• If D7= 0, the operation code must be one of the other seven values 000 through

110, specifying a memory-reference

• instruction.

• If D7 = 0 and I = 1, we have a memory reference instruction with an indirect

address access .

• If D7 = 0 and I = 0, we have a memory reference instruction with an direct

address access.

Instruction Formats

• Operations specified by computer instructions are executed

on some data stored in memory or processor registers.

• Operands residing in memory are specified by their

memory address.

• Operands residing in processor registers are specified with

a register address.

• Thus a CPU with 16 processor registers R0 through R15 will

have a register address field of four bits.

• The binary number 0101, for example, will designate

register RS.

Instruction Format

• Computers may have instructions of several different lengths

containing varying number of addresses.

• The number of address fields in the instruction format of a

computer depends on the internal organization of its registers.

• Most computers fall into one of three types of CPU

organizations:

• 1. Single accumulator organization.

• 2. General register organization.

• 3. Stack organization.

Instruction Format

• An example of an accumulator-type organization instruction.

A D D X where X is the address of the operand.

• The ADD instruction in this case results in the operation AC <--

AC + M [X]. AC is the accumulator register and M [X]

symbolizes the memory word located at address X.

• An example of a general register type of organization was

presented in An example of register organization instruction.

• Thus the instruction for an arithmetic addition may be written

in an assembly language as ADD R 1 , R 2 , R 3 t o denote the

operation R 1 <--- R2 + R 3 .

• The number o f address fields in the instruction can be

reduced from three to two if the destination register is the

same as one of the source registers.

Instruction Format

• Thus the instruction A D D R 1 , R 2 would denote the operation R

1 <--- R 1 + R2.

• Only register addresses for R 1 and R2 need be specified in this

instruction. . The stack-organized instruction .

• Computers with stack organization would have PUSH and POP

instructions which require an address field.

• PUSH X will push the word at address X to the top of the stack. The

stack pointer is updated automatically.

• Operation type instructions do not need an address field in stack-

organized computers. This is because the operation is performed

on the two items that are on top of the stack. The instruction

ADD .

Three-Address Instructions

• Computers with three-address instruction formats can use each

address field to specify either a processor register or a memory

operand.

• The program in assembly language that evaluates X = (A + B) *

(C + D) is shown below, together with comments that explain

the register transfer operation of each instruction.

• It is assumed that the computer has two processor registers, R

1 and R2.

• The symbol M [A ] denotes the operand at memory address

symbolized by A .

Three-Address Instructions

• The advantage o f the three-address format i s

that i t results i n short programs when

evaluating arithmetic expressions.

• The disadvantage is that the binary-coded

instructions require too many bits to specify

three addresses.

Two-Address Instructions

• Two-address instructions are the most

common in commercial computers. Here again

each address field can specify either a

processor register or a memory word. The

program to evaluate X = (A + B) * (C + D) is as

follows

RISC Instructions

• A reduced instruction set computer (RISC). The instruction

set of a typical RISC processor is restricted to the use of load

and store instructions when communicating between

memory and CPU.

• All other instructions are executed within the registers of the

CPU without referring to memory.

• A program for a RISC-type CPU consists of LOAD and STORE

instructions that have one memory and one register address,

and computational-type instructions that have three

addresses with all three specifying processor registers.

• The following is a program to evaluate X = (A + B) • (C + D).

You might also like

- Golden Dawn 2 9 The Moon BreathDocument4 pagesGolden Dawn 2 9 The Moon BreathF_RCNo ratings yet

- Assignment in English Plus Core 11 Full CircleDocument76 pagesAssignment in English Plus Core 11 Full CircleRitu Maan68% (38)

- Java Programming Lab Programs ListDocument51 pagesJava Programming Lab Programs ListPalakonda SrikanthNo ratings yet

- OOPS 2 Marks Questions AnswersDocument22 pagesOOPS 2 Marks Questions AnswersRaja SekarenNo ratings yet

- Number RepresentationDocument59 pagesNumber RepresentationAdam Tri RamdaniNo ratings yet

- Computer OrgnisationDocument138 pagesComputer OrgnisationmadhuNo ratings yet

- 2 1 Flash Klasa 6 Mod 1b Test ExtendedDocument4 pages2 1 Flash Klasa 6 Mod 1b Test ExtendedMonika Ciepłuch-Jarema100% (1)

- CSE331L - Introduction to Assembly LanguageDocument7 pagesCSE331L - Introduction to Assembly LanguageTanjila Islam Ritu 1811017642No ratings yet

- Fi & EiDocument3 pagesFi & EiPrasanna S Kulkarni100% (1)

- Introduction To Computer Security'Document19 pagesIntroduction To Computer Security'Aarti SoniNo ratings yet

- Python ProgramsDocument6 pagesPython ProgramsdsreNo ratings yet

- CPU Architecture: Control Unit (CU)Document10 pagesCPU Architecture: Control Unit (CU)i study100% (1)

- UNIT-1 Assembly Language ProgrammingDocument30 pagesUNIT-1 Assembly Language ProgrammingIshan Tiwari100% (1)

- Sap-1 Computer Part1Document56 pagesSap-1 Computer Part1Tawki BakiNo ratings yet

- K Map Electronics Simplification GuideDocument14 pagesK Map Electronics Simplification GuideSaurabh KhandelwalNo ratings yet

- Assembly Language - A Low-Level Programming LanguageDocument67 pagesAssembly Language - A Low-Level Programming LanguageprithiksNo ratings yet

- Parallel Processing Chapter - 2: Basics of Architectural DesignDocument29 pagesParallel Processing Chapter - 2: Basics of Architectural DesignGetu GeneneNo ratings yet

- Bathymetry and Its Applications PDFDocument158 pagesBathymetry and Its Applications PDFArseni MaximNo ratings yet

- 715ECT04 Embedded Systems 2M & 16MDocument32 pages715ECT04 Embedded Systems 2M & 16Msumathi0% (1)

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationDocument13 pagesUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaNo ratings yet

- RTWP OptimisationHanFeedbackDocument31 pagesRTWP OptimisationHanFeedbackSeth Mawuli Dedzoe100% (1)

- Adder and SubtractorDocument17 pagesAdder and SubtractorVELURU RANJITH URK18CS020No ratings yet

- CS1203 System Software UNIT I Question AnsDocument10 pagesCS1203 System Software UNIT I Question AnskeerthisivaNo ratings yet

- Interrupts in 8086Document4 pagesInterrupts in 8086Radhakrishna100% (1)

- Multilevel view of a machine's architectureDocument3 pagesMultilevel view of a machine's architectureVarsha Rani0% (1)

- CA 2marksDocument41 pagesCA 2marksJaya ShreeNo ratings yet

- CS6402 Design and Analysis of Algorithms Question BankDocument27 pagesCS6402 Design and Analysis of Algorithms Question BankRamesh Kumar MNo ratings yet

- Instruction pipelining explainedDocument5 pagesInstruction pipelining explainedAyush KumarNo ratings yet

- Microprocessor & microcontroller introductionDocument20 pagesMicroprocessor & microcontroller introductionjeravi84No ratings yet

- CO Unit 2-1Document15 pagesCO Unit 2-1Aravinder Reddy SuramNo ratings yet

- Source Port: 16 Bits: TCP Header FormatDocument6 pagesSource Port: 16 Bits: TCP Header Format254186No ratings yet

- Computer Organization and ArchitectureDocument21 pagesComputer Organization and ArchitectureHebziba Jeba Rani S100% (1)

- Ee8551 8085 NotesDocument31 pagesEe8551 8085 NotesKUMARANSCRNo ratings yet

- Module3 ISADocument51 pagesModule3 ISAwatsontamilNo ratings yet

- FinalDocument178 pagesFinalBiki JhaNo ratings yet

- Computer Organization Concise NotesDocument57 pagesComputer Organization Concise NoteschutiyaNo ratings yet

- Why bus protocol is importantDocument4 pagesWhy bus protocol is importantashar565No ratings yet

- Basic Computer OrganizationDocument20 pagesBasic Computer OrganizationMag Creation100% (1)

- 07 - Recursion PDFDocument28 pages07 - Recursion PDFarshNo ratings yet

- Pentium 4Document8 pagesPentium 4smitaksNo ratings yet

- Operating SystemsDocument5 pagesOperating Systemskp_phani3694284No ratings yet

- EC2303 2 Marks With AnswersDocument19 pagesEC2303 2 Marks With AnswersVijay Arunagiri ANo ratings yet

- Purpose of Language ProcessorsDocument7 pagesPurpose of Language Processorsall4downloads100% (2)

- Computer Instructions and Its TypesDocument12 pagesComputer Instructions and Its TypesAshish100% (1)

- LAB-CYCLE-XHTML-JS-PERLDocument2 pagesLAB-CYCLE-XHTML-JS-PERLLuke KennyNo ratings yet

- IT 2353 Web Technology - NotesDocument68 pagesIT 2353 Web Technology - NotesDivya Vijayakumar67% (3)

- Unit 1 Fundamentals of ComputerDocument8 pagesUnit 1 Fundamentals of Computerpruthvimgowda1997No ratings yet

- CS2352 - Principles of Compiler Design PDFDocument86 pagesCS2352 - Principles of Compiler Design PDFRam KumarNo ratings yet

- Berkeley SocketDocument7 pagesBerkeley Socketom18sahuNo ratings yet

- Unit 2Document44 pagesUnit 2nagpal3No ratings yet

- Von Neumann ArchitectureDocument4 pagesVon Neumann Architectureawais nadeemNo ratings yet

- Chapter 3 - String ProcessingDocument28 pagesChapter 3 - String ProcessingTanveer Ahmed HakroNo ratings yet

- Introduction To Assembly Language (Chapter 1)Document27 pagesIntroduction To Assembly Language (Chapter 1)sara100% (2)

- Register, Bus and Memory Transfer-5Document17 pagesRegister, Bus and Memory Transfer-5Dinesh KumarNo ratings yet

- BC0040 Computer Organization and Architecture Assignment (IA)Document9 pagesBC0040 Computer Organization and Architecture Assignment (IA)SundeepKumar100% (3)

- Course Notes - Unit 1 PDFDocument4 pagesCourse Notes - Unit 1 PDFMichael SkyersNo ratings yet

- T00160030120134075 (L) Pert 1 - Algorithm & Programming and Introduction To C ProgrammingDocument46 pagesT00160030120134075 (L) Pert 1 - Algorithm & Programming and Introduction To C ProgrammingtermaponNo ratings yet

- Fetch Execute Cycle PDFDocument4 pagesFetch Execute Cycle PDFAditya Ghose50% (2)

- Systems Software QuestionDocument82 pagesSystems Software QuestionkhalidNo ratings yet

- Assembly Programming Tutorial: What Is Assembly Language?Document75 pagesAssembly Programming Tutorial: What Is Assembly Language?Bhagya Gaddam100% (1)

- COD Unit 2 PDFDocument49 pagesCOD Unit 2 PDFYash Gupta MauryaNo ratings yet

- Cod Unit 2Document44 pagesCod Unit 2anilNo ratings yet

- Quarter 1-Module 2 Modern ArtDocument20 pagesQuarter 1-Module 2 Modern ArtKimberly Trocio Kim100% (1)

- 4.2 - Traditional Double-Walled HapaDocument25 pages4.2 - Traditional Double-Walled HapaThakur VeeruNo ratings yet

- (New) Adjustable Voltage Power Supply 55 V - 20A High Power and Current - Automatic Fan On - OffDocument1 page(New) Adjustable Voltage Power Supply 55 V - 20A High Power and Current - Automatic Fan On - OffSek PyroNo ratings yet

- TCB E-F 015cukDocument2 pagesTCB E-F 015cukTempcoNo ratings yet

- Fesh S A0001171549 1Document7 pagesFesh S A0001171549 1ismuNo ratings yet

- 3 Soal Ganjil Inggris MaritimDocument8 pages3 Soal Ganjil Inggris MaritimFikri Mu'izNo ratings yet

- A Study On Renewable Energy Resources in IndiaDocument39 pagesA Study On Renewable Energy Resources in IndiaDevendra SharmaNo ratings yet

- Zooniverse Book 2022Document28 pagesZooniverse Book 2022Dr Pankaj DhussaNo ratings yet

- TheologicalDiscipleship English 2011-1Document144 pagesTheologicalDiscipleship English 2011-1bilnyangnatNo ratings yet

- Definisi, Karakteristik dan Contoh Aplikasi SIGDocument28 pagesDefinisi, Karakteristik dan Contoh Aplikasi SIGtoyota taaNo ratings yet

- Maximizing Area and Minimizing Costs with CalculusDocument18 pagesMaximizing Area and Minimizing Costs with Calculusanon_218576188No ratings yet

- Philips HD5 enDocument5 pagesPhilips HD5 enmohamed boufasNo ratings yet

- A Feminist Analysis of Habba Khatoon'S Poetry: Dr. Mir Rifat NabiDocument7 pagesA Feminist Analysis of Habba Khatoon'S Poetry: Dr. Mir Rifat NabiShabir AhmadNo ratings yet

- Tcgbutopia G8Document216 pagesTcgbutopia G8faffsNo ratings yet

- Interfacial Phenomena in Pharmaceutical FormulationDocument21 pagesInterfacial Phenomena in Pharmaceutical FormulationNickson DrabeNo ratings yet

- Kant On Religion and ScienceDocument21 pagesKant On Religion and ScienceEduardo CharpenelNo ratings yet

- The Following Functional Health Pattern Assessment Is Based On A 65 Year Old Scottish Woman Who Lives Independently With Her Husband in Their Home at Happy ValleyDocument9 pagesThe Following Functional Health Pattern Assessment Is Based On A 65 Year Old Scottish Woman Who Lives Independently With Her Husband in Their Home at Happy ValleyJajangNo ratings yet

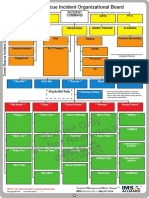

- Sample Only Do Not Reproduce: Trench Rescue Incident Organizational BoardDocument1 pageSample Only Do Not Reproduce: Trench Rescue Incident Organizational BoardLuis Diaz CerdanNo ratings yet

- Mec 323Document68 pagesMec 323VINAY B.SNo ratings yet

- What Is The Kingdom of GodDocument10 pagesWhat Is The Kingdom of GodSunil ChelladuraiNo ratings yet

- PR900 Operator ManualDocument21 pagesPR900 Operator ManualAlan TanNo ratings yet

- HymssheetDocument4 pagesHymssheettoby_wardmanNo ratings yet

- Calculation of Carbon Footprint: HouseDocument3 pagesCalculation of Carbon Footprint: HouseUmut ÇağırganNo ratings yet

- Engineering Statics FundamentalsDocument28 pagesEngineering Statics FundamentalsurwaNo ratings yet