Professional Documents

Culture Documents

Pin On Side of Chip

Uploaded by

Alonso CoradoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Pin On Side of Chip

Uploaded by

Alonso CoradoCopyright:

Available Formats

Simple Input/Output using the MSP430 (note: these notes are written with the MSP430F149 in mind !

he MSP430 uses memor" mapped I/O# From a programmer$s perspe%ti&e' the e((e%t o( this is that writing to parti%ular memor" lo%ations %hanges the logi% state o( pins (outputs on the side o( the %hip# )eads (rom parti%ular memor" lo%ations return the logi% states o( parti%ular pins (inputs # *p to + ports are supported : P1 to P+ depending on the model o( the MSP430 ,eing used# -ll ports .map to/ 0 ,it memor" lo%ations# 1a%h port is asso%iated with (at least three memor" lo%ations: PnI2' PnO*! and Pn3I)(e%tion where $n$ represents the port num,er# 4onsider Port1 (or a moment# P1I2 is mapped to memor" address 50 (he6 P1O*! is mapped to memor" address 51 (he6 P13I) is mapped to memor" address 55 (he6 # !he 3ata dire%tion register determines whether a parti%ular ,it in a port is an input or an output# Figure 1 shows how ,it 1 o( port 1 ma" ,e %on(igured as an input or an output ," setting or %learing ,it 1 o( the 3ire%tion register# I( a 3I)e%tion register ,it is a .1/ then the %orresponding port data ,it is an output# I( a 3I)e%tion register ,it is a .0/ then the %orresponding port data ,it is an input#

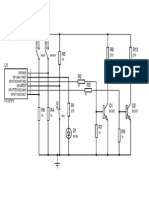

3ata (low P1O*! Pin on side of chip

P1I2 3ata (low P13I) Inside MSP430

2ow lets sa" we want to use Port 1 to monitor the status o( a push ,utton and to %ontrol a 7ight 1mitting 3iode when the ,utton is pressed# !he %ir%uit %ould ,e represents as shown in Figure 5 ,elow:

)1 )5 P1 3#3;

,1 ,0

Figure 5 !o turn on the 713' ,it1 o( PO)!1 should ,e set to 0# !o turn o(( the 713' ,it1 o( PO)!1 should ,e set to 1# !he program %ontinuall" monitors P1I2 %he%8ing to see whether its least signi(i%ant ,it is a 0 or 1# !his ,it will ,e 9ero i( the ,utton is pressed' and i( so' the 713 is turned on# :e %ould program this in 4 as (ollows:

typedef unsigned char byte; #define P1IN *((byte *)0x20) #define P1OU *((byte *)0x21) #define P1!I" *((byte *)0x22) #define P#IN *((byte *) 0x1c ) #define P#OU *((byte *) 0x1d ) #define P#!I" *((byte *) 0x1e ) $$ %atchd&g ti'er definiti&ns (see (ater) #define %! )* *((sh&rt *)0x120) #define %! +O*! 0x00,0 #define %! P% 0x-a00 .&id 'ain(.&id) / %! ) * 0 %! P% 1 %! +O*!; $$ 2t&p 3atchd&g ti'er (see (ater) P1!I" 40 0x02; $$ 2et P251 is an &utput 3hi(e( 1001 ) / if( (P1IN 6 0x01) 70 0) / $$ 2%I )+ I2 OP8N 2O U"N O99 *8! P1OU 0 P1OU 4 2; : e(se / $$ 2%I )+ I2 OP8N 2O U"N ON *8! P1OU 0 P1OU 6 0xfd; : : :

Ports 1 to + (where a&aila,le are memor" mapped as (ollows (note the .06/ in (ront implies <1= : Port PnIN PnOUT PnDIR PnSEL P1 P5 P3 P4 P> P+ 0650 0650 0610 061% 0630 0634 0651 0659 0619 061d 0631 063> 0655 065a 061a 061e 0635 063+ 065+ 065e 061, 061( 0633 063?

You might also like

- Yamaha FZ6-SS (SSC) 2004 Service ManualDocument432 pagesYamaha FZ6-SS (SSC) 2004 Service ManualBivol LeonidNo ratings yet

- Z Purlin DesignDocument22 pagesZ Purlin DesignGautam PaulNo ratings yet

- Oracle Forms 10g TutorialDocument41 pagesOracle Forms 10g TutorialSudhakarNo ratings yet

- Boiler Safety ProgramDocument8 pagesBoiler Safety ProgramHussain KhanNo ratings yet

- CPCCSF2003A Cut and Bend Materials Using Oxy LPG Equipment LR V1Document141 pagesCPCCSF2003A Cut and Bend Materials Using Oxy LPG Equipment LR V1FfdsfdsNo ratings yet

- Functional SpecificationDocument12 pagesFunctional SpecificationGowtham Krishna Maganti100% (1)

- Exercise 1: Using PointersDocument6 pagesExercise 1: Using PointersShekhar ChaudharyNo ratings yet

- C - Question Paper Quark Media House India Pvt. LTD.: 1. What Is The Output of The Following CodeDocument9 pagesC - Question Paper Quark Media House India Pvt. LTD.: 1. What Is The Output of The Following CodesumikannuNo ratings yet

- General Purpose Input/Output: TopicDocument16 pagesGeneral Purpose Input/Output: TopicvantienbkNo ratings yet

- STM32F103ZET6 Development BoardDocument10 pagesSTM32F103ZET6 Development BoardpiramidonNo ratings yet

- BC420 - 46C - 016appendix (Tasks)Document23 pagesBC420 - 46C - 016appendix (Tasks)mkumarshahiNo ratings yet

- Rangkaian AritmetikaDocument47 pagesRangkaian AritmetikaamamanghNo ratings yet

- INT 21h - The General Function DespatcherDocument23 pagesINT 21h - The General Function DespatcherSreekanth PagadapalliNo ratings yet

- Standart Penamaan CommandDocument5 pagesStandart Penamaan CommandRidwan FauziNo ratings yet

- ABAPDocument15 pagesABAPSiddhartha BaruaNo ratings yet

- Symbosium DetailsDocument32 pagesSymbosium Detailsbazeerahamed1232248No ratings yet

- Seminar Report On 8051 MicrocontrollerDocument21 pagesSeminar Report On 8051 MicrocontrollerHapi ER50% (2)

- HY-JK02-M 5-Axis Interface Board ManualDocument13 pagesHY-JK02-M 5-Axis Interface Board ManualSeyton123No ratings yet

- StruCAD3D Import PDFDocument35 pagesStruCAD3D Import PDFla_civilNo ratings yet

- Programming AT90S2313Document4 pagesProgramming AT90S2313Juan Luis MerloNo ratings yet

- I. Shareware Ii. PHP: Informatics Practices (065) Sample Question Paper - 1Document17 pagesI. Shareware Ii. PHP: Informatics Practices (065) Sample Question Paper - 1Arjun PrasadNo ratings yet

- °prosesor:: Control Dan DatapathDocument46 pages°prosesor:: Control Dan DatapathlinglingnoNo ratings yet

- FAQ's of C ProgrammingDocument42 pagesFAQ's of C ProgrammingP Venu Gopala RaoNo ratings yet

- PHP Basics 1-1Document11 pagesPHP Basics 1-1Rochana RamanayakaNo ratings yet

- Pic 18 Help TopicsDocument6 pagesPic 18 Help TopicsЄвген ЛісовийNo ratings yet

- Class V Computer AssignmentDocument5 pagesClass V Computer AssignmentQadir MohideenNo ratings yet

- OSN1500 V100R001 Slot Configuration PrinciplesDocument3 pagesOSN1500 V100R001 Slot Configuration PrinciplesWilliam BlackNo ratings yet

- Chapter 03 IOSDocument11 pagesChapter 03 IOSsatkm87No ratings yet

- Relational and Logical OperatorsDocument13 pagesRelational and Logical OperatorsVamsi YvcNo ratings yet

- Canon Printer IX5000 & IX4000 - Service ManualDocument8 pagesCanon Printer IX5000 & IX4000 - Service ManualVaxsis SisvaxNo ratings yet

- CNET Lab-3 - ECB19025Document2 pagesCNET Lab-3 - ECB19025Kaushik MazumderNo ratings yet

- Data Plan VoucherDocument4 pagesData Plan VoucherJaackson SabastianNo ratings yet

- Direct Digital Synthesizer: Design of ROMDocument53 pagesDirect Digital Synthesizer: Design of ROMYermakov Vadim IvanovichNo ratings yet

- Panasonic TVsDocument4 pagesPanasonic TVsmarshlee405No ratings yet

- A. Golden RULE Profit Maximized Where MR MC TC TR TR TR Max TC MR 0 MR MCDocument6 pagesA. Golden RULE Profit Maximized Where MR MC TC TR TR TR Max TC MR 0 MR MCzlemischNo ratings yet

- C QuestionDocument65 pagesC QuestionJamuna12No ratings yet

- PROJECT - Computer Science Project - NAME - Vivek Yadav - SECTION - F - Vivek YadavDocument21 pagesPROJECT - Computer Science Project - NAME - Vivek Yadav - SECTION - F - Vivek YadavADWAITH EditzNo ratings yet

- Launch x431 MasterDocument15 pagesLaunch x431 MasterJuan Carlos Antipan NuñezNo ratings yet

- Giai de Thi Thu CTDL ThaykhangDocument14 pagesGiai de Thi Thu CTDL Thaykhangmy hoangNo ratings yet

- Brosur Spek JarkomDocument27 pagesBrosur Spek JarkomAngus Item RueNo ratings yet

- Server ProgramDocument6 pagesServer ProgramAswaraj PandeyNo ratings yet

- ColicosDocument367 pagesColicosFamilia Echavarria GageyNo ratings yet

- 19" 1U Rack Mounting Auto Gain Multi Port Video Receiver HubDocument4 pages19" 1U Rack Mounting Auto Gain Multi Port Video Receiver HubLuis NascimentoNo ratings yet

- SMS Signaling For Roaming BillingDocument19 pagesSMS Signaling For Roaming BillingMadhunath YadavNo ratings yet

- CCNP Lead 2 PassDocument194 pagesCCNP Lead 2 PassPisotonesNo ratings yet

- IF408 IOG-AR Outbound InterfaceDocument13 pagesIF408 IOG-AR Outbound InterfaceSrinivas GirnalaNo ratings yet

- Orcad PLDDocument8 pagesOrcad PLDmeeduma4582No ratings yet

- Note CardDocument3 pagesNote CardTheOxyCleanGuyNo ratings yet

- Batch 2 SolutionDocument2 pagesBatch 2 SolutionJeswin EldhoNo ratings yet

- Psedo CodeDocument7 pagesPsedo CodesamarxdasNo ratings yet

- Lab#2Document8 pagesLab#2Ali Nawaz RanjhaNo ratings yet

- DTMB Propeller GeometryDocument17 pagesDTMB Propeller GeometryKivanc Ali ANILNo ratings yet

- Interview QaDocument119 pagesInterview QaJoney DeepNo ratings yet

- Teknikat e Gjuheve Te Programimit-1Document120 pagesTeknikat e Gjuheve Te Programimit-1Llazi LegjendaNo ratings yet

- Ec2308: Microprocessors & Microcontrollers Lab Manual V Sem EceDocument99 pagesEc2308: Microprocessors & Microcontrollers Lab Manual V Sem EceSandy RonaldoNo ratings yet

- PPTP Server Running On Your FirewallDocument11 pagesPPTP Server Running On Your FirewallHernanCossuNo ratings yet

- Date Object: Javascript Quick Reference CardDocument2 pagesDate Object: Javascript Quick Reference CardAlexander ReinagaNo ratings yet

- Vdocument - in Electricity Billing SystemDocument81 pagesVdocument - in Electricity Billing SystemShammah MakowaniNo ratings yet

- CodingDocument25 pagesCodingArun KrishNo ratings yet

- Divided States: Strategic Divisions in EU-Russia RelationsFrom EverandDivided States: Strategic Divisions in EU-Russia RelationsNo ratings yet

- Learn C Programming through Nursery Rhymes and Fairy Tales: Classic Stories Translated into C ProgramsFrom EverandLearn C Programming through Nursery Rhymes and Fairy Tales: Classic Stories Translated into C ProgramsNo ratings yet

- Themaclassic F30E and F30E SB Instructions For Use Installation and ServicingDocument52 pagesThemaclassic F30E and F30E SB Instructions For Use Installation and ServicingAlonso CoradoNo ratings yet

- SD6109Document10 pagesSD6109Alonso Corado100% (1)

- Draw On Google Earth and Export The Objects To AutoCAD - DevCADLispDocument14 pagesDraw On Google Earth and Export The Objects To AutoCAD - DevCADLispAlonso CoradoNo ratings yet

- Samsung 713BNDocument46 pagesSamsung 713BNAlonso CoradoNo ratings yet

- Alarma GarajDocument1 pageAlarma GarajAlonso CoradoNo ratings yet

- PlotterGraphtec 07I107EDocument5 pagesPlotterGraphtec 07I107EAlonso CoradoNo ratings yet

- Steca PV Off Grid enDocument31 pagesSteca PV Off Grid enAlonso CoradoNo ratings yet

- FSC v5535 z17mDocument31 pagesFSC v5535 z17mAlonso CoradoNo ratings yet

- HP Pavilion Dv6 Dv7 Quanta Ut12 Rev 1a SCHDocument48 pagesHP Pavilion Dv6 Dv7 Quanta Ut12 Rev 1a SCHAlonso CoradoNo ratings yet

- Aisikai Auto Transfer Switch DocumentationDocument7 pagesAisikai Auto Transfer Switch DocumentationAlonso Corado100% (1)

- TL866 ProgDocument9 pagesTL866 ProgAlonso CoradoNo ratings yet

- DeltaSol BS Plus V2.MonenDocument52 pagesDeltaSol BS Plus V2.MonenAlonso CoradoNo ratings yet

- 1006 MTL 4840 HartDocument14 pages1006 MTL 4840 HartAlonso CoradoNo ratings yet

- Control Stations Comex: Selection ChartDocument2 pagesControl Stations Comex: Selection ChartAlonso CoradoNo ratings yet

- ABS Submersible Sewage Pump AFP M8 M9Document2 pagesABS Submersible Sewage Pump AFP M8 M9Alonso CoradoNo ratings yet

- Trasfo CurentDocument11 pagesTrasfo CurentAlonso CoradoNo ratings yet

- Ba Sar1!07!16 Norm enDocument48 pagesBa Sar1!07!16 Norm enAlonso CoradoNo ratings yet

- Power ControlDocument96 pagesPower ControlAlonso CoradoNo ratings yet

- Common Examples and Applications of Copolymers. Acrylonitrile Butadiene Styrene (ABS)Document4 pagesCommon Examples and Applications of Copolymers. Acrylonitrile Butadiene Styrene (ABS)Yashi SrivastavaNo ratings yet

- Mahila Pay and ParkDocument113 pagesMahila Pay and ParkSaurabh PednekarNo ratings yet

- ODAA Support LetterDocument2 pagesODAA Support LetterStatesman JournalNo ratings yet

- Topobase Performance and ScalabilityDocument16 pagesTopobase Performance and ScalabilityFernandoKNo ratings yet

- Lab 11.4.1: Using The Scandisk and Defrag Utilities: Estimated Time: 30 Minutes ObjectiveDocument2 pagesLab 11.4.1: Using The Scandisk and Defrag Utilities: Estimated Time: 30 Minutes ObjectiveHamzaSpahijaNo ratings yet

- QUBEDocument2 pagesQUBEJován MéridaNo ratings yet

- Jeppesen Charts LegendsDocument34 pagesJeppesen Charts LegendsFatih OguzNo ratings yet

- Manual de Parts ES16D6Document36 pagesManual de Parts ES16D6Eduardo CortezNo ratings yet

- Transfer FunctionDocument19 pagesTransfer FunctionVinay Kumar SmartyNo ratings yet

- Sub Test Mole Concept PDFDocument7 pagesSub Test Mole Concept PDFVIKAS GARGNo ratings yet

- Impact Sprinkler Troubleshooting GuideDocument11 pagesImpact Sprinkler Troubleshooting GuidemuthuvelaaNo ratings yet

- Pipe and Tube Operations - DaytonaDocument123 pagesPipe and Tube Operations - Daytonaramon nava0% (1)

- ASSEMBLY AND PARTS ALBUM - Kipor Power Systems - KDE6700TA PDFDocument2 pagesASSEMBLY AND PARTS ALBUM - Kipor Power Systems - KDE6700TA PDFracsoNo ratings yet

- Apple Value ChainDocument3 pagesApple Value ChainKeng Keat Lim100% (2)

- Mechatronics R16 Oct 2019 PDFDocument4 pagesMechatronics R16 Oct 2019 PDFrajuNo ratings yet

- Project On RaymondDocument36 pagesProject On Raymonddinesh beharaNo ratings yet

- Co Linear Antenna DesignDocument2 pagesCo Linear Antenna DesignAhmed JafarNo ratings yet

- Ansi Asabe S261.7 Feb1989 (R2011)Document5 pagesAnsi Asabe S261.7 Feb1989 (R2011)StephanNo ratings yet

- List of Sanitary and Plumbing ItemsDocument4 pagesList of Sanitary and Plumbing ItemssumalathaNo ratings yet

- Nitrile RubberDocument1 pageNitrile RubberMohamedNo ratings yet

- Analysis of Open-Channel Flow Transitions Using Specific Energy DiagramDocument13 pagesAnalysis of Open-Channel Flow Transitions Using Specific Energy DiagramRandy ViolaNo ratings yet

- SmartBright LED Downlight G3Document11 pagesSmartBright LED Downlight G3Puji SnNo ratings yet

- Ampeg BA115HPTDocument3 pagesAmpeg BA115HPTFederico BrunoNo ratings yet

- Assessment 1 - Questioning - Written Assessment: Satisfactory or Not Yet SatisfactoryDocument35 pagesAssessment 1 - Questioning - Written Assessment: Satisfactory or Not Yet SatisfactorySonal Awasthi MishraNo ratings yet

- Dokumen - Tips - Curriculum Vitae Adrian Danar Wibisono 1Document2 pagesDokumen - Tips - Curriculum Vitae Adrian Danar Wibisono 1Reo DeraNo ratings yet

- Company Profile Traya Lintas PersadaDocument24 pagesCompany Profile Traya Lintas PersadaAyu Catra KastaraNo ratings yet

- pLINES Datasheet FP V2.22Document2 pagespLINES Datasheet FP V2.22TrinhDinhLoc0% (1)

- GRE Sentence CompletionDocument3 pagesGRE Sentence Completionapi-3699142No ratings yet