Professional Documents

Culture Documents

Interrupts and The 8259 Chip

Interrupts and The 8259 Chip

Uploaded by

Veda Vyas0 ratings0% found this document useful (0 votes)

5 views30 pagesa

Original Title

Ece

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documenta

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

5 views30 pagesInterrupts and The 8259 Chip

Interrupts and The 8259 Chip

Uploaded by

Veda Vyasa

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 30

CHAPTER 6

INTERRUPTS AND THE 8259 CHIP

What happens on interrupt?

Micro automatically saves (on stack) the FR (flag register), IP (instruction pointer), CS (code segement register). There are 255 interrupts. The address of the appropriate ISR can be computed by multiplying the interrupt number by 4! The 4 bytes in the interrupt vector table contain CS:IP The address where the ISR is located is IP <= IP value in table + CS value in table (shifted left one nybble!) Example: CS value in table is $0001 and IP is $1820 then ISR routine starts at $11820

Interrupt Vector Table

8088 Interrupt List

Hardware Versus Software Interrupts

INTR (pos level sensitive) and NMI (posedge sensitive) INT is command that causes software interrupt. Also, have EXCEPTIONS (SWI that happens automatically w/o INT cmd)

If we only have one INTR pin, does that mean we can only have one kind of interrupt? NO. 8259 chip will allow us to have up to 8 AND if we use nine 8259 chips we can have up to 64!

Condition Codes (Status) Register

ISR Addresses

8259 Programmable Interrupt Controller

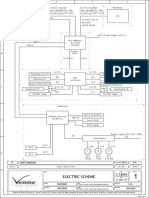

8259 Programmable Interrupt Controller Block Diagram

Addresses for 8259 ICWs

ICW1 and ICW2 Formats

INT Numbers

ICW3 and ICW4 Formats

Finding ICWs for a 8259

Addresses for 8259 OCWs

OCW Format for the 8259

Enabling IR0 thru IR7

Issuing the EOI to 8259 Chip

8259 Port Addresses in IBM PC/XT Computer

PC/XT I/O Address Map

IBM PC/XT hardware Interrupts

IBM PC/XT Initialization of 8259

What happens on interrupt?

PC/XT Sources of Hardware Interrupt

PC/XT Sources of NMI Interrupt

PC/XT Port Uses

What caused the NMI?

Ch 6 Problems (part1)

Ch 6 Problems (part 2)

Ch 6 Problems (part 3)

You might also like

- Tuazon v. FuentesDocument2 pagesTuazon v. FuentesJay jogsNo ratings yet

- Startland Annual Report 2022Document21 pagesStartland Annual Report 2022StartlandNo ratings yet

- Assignment 1Document12 pagesAssignment 1arswishNo ratings yet

- Lab 10Document8 pagesLab 10zeeshan AkramNo ratings yet

- FeaturesDocument8 pagesFeaturesRoshan RajuNo ratings yet

- 8086 InterruptDocument10 pages8086 Interruptavireddy1No ratings yet

- Interrupts in 8086Document4 pagesInterrupts in 8086Radhakrishna100% (1)

- Ee314 5Document12 pagesEe314 5Keerthi Vasan SNo ratings yet

- Lesson 13Document27 pagesLesson 13kadaNo ratings yet

- Intel 8085 Microprocessor ArchitectureDocument9 pagesIntel 8085 Microprocessor Architectureapi-3740045100% (4)

- 2 Advanced+MicroprocesorDocument66 pages2 Advanced+MicroprocesorMilind KhanderaoNo ratings yet

- 3 Mod3Document19 pages3 Mod3Sagar ChaulagaiNo ratings yet

- Microprocessor Is A Programmable Multipurpose Clock Driven Sequential Digital Integrated Electronic ComponentDocument43 pagesMicroprocessor Is A Programmable Multipurpose Clock Driven Sequential Digital Integrated Electronic ComponentKUMARANSCRNo ratings yet

- CH 8Document13 pagesCH 8Gcross NGNo ratings yet

- Iii Unit Mpi Part ADocument5 pagesIii Unit Mpi Part AN.RAMAKUMARNo ratings yet

- Advanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. PDocument46 pagesAdvanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. Pvishu212167% (3)

- 8086 Interrupts: InterruptDocument5 pages8086 Interrupts: InterruptN.RAMAKUMARNo ratings yet

- 8086 InterruptsDocument24 pages8086 InterruptsAshwini ManojNo ratings yet

- Assignment ON Microprocessor AND Microcontroller: Joyal Jose AugustineDocument63 pagesAssignment ON Microprocessor AND Microcontroller: Joyal Jose Augustineajas777BNo ratings yet

- 8085 Architecture & Pin DescriptionFileDocument19 pages8085 Architecture & Pin DescriptionFileKaseya TakahashiNo ratings yet

- 80x86 InterruptsDocument33 pages80x86 InterruptsVIVEK K PNo ratings yet

- Iii Unit Mpi Part ADocument16 pagesIii Unit Mpi Part ADarshan BysaniNo ratings yet

- 8 8086 InterruptsDocument26 pages8 8086 InterruptsAnshuman MitraNo ratings yet

- Mpi Unit 5Document32 pagesMpi Unit 5anishadandaNo ratings yet

- Lecture 7 - CSE 3205 - Microprocessor and Assembly Language - by - Marjia - Sultana (Autosaved)Document25 pagesLecture 7 - CSE 3205 - Microprocessor and Assembly Language - by - Marjia - Sultana (Autosaved)Marjia SultanaNo ratings yet

- 8086 Interrupts NewDocument33 pages8086 Interrupts NewVineeth Valiyaveedu Vijayan100% (1)

- InterruptDocument25 pagesInterruptPallvi BhardwajNo ratings yet

- Sup0405 8Document5 pagesSup0405 8jonycrashNo ratings yet

- ALPQPDocument20 pagesALPQPTanujaramNo ratings yet

- Numaric Data Processor 8087Document6 pagesNumaric Data Processor 8087Sowmya PNo ratings yet

- 8259 PicDocument6 pages8259 PicpreethipattabiramanNo ratings yet

- Experiment - 5 InterruptsDocument4 pagesExperiment - 5 InterruptsEC100 Diya SoniNo ratings yet

- Interrupts PDFDocument4 pagesInterrupts PDFHermain Fayyaz KarimNo ratings yet

- Introduction To 8085 Architecture and Programming: Ifetce/It/Ii Year/ Iv Sem/IT141402/MPMC/ Ver 1.0 1Document89 pagesIntroduction To 8085 Architecture and Programming: Ifetce/It/Ii Year/ Iv Sem/IT141402/MPMC/ Ver 1.0 1Palani UthirapathyNo ratings yet

- REAL TIME EMBEDDED SYSTEM - Lec5Document17 pagesREAL TIME EMBEDDED SYSTEM - Lec5parthasarothi_sikder79No ratings yet

- Interrupts in Personal Computers: Experiment #6Document10 pagesInterrupts in Personal Computers: Experiment #6Asaad HalayqaNo ratings yet

- CS601: Microprocessor & Interfacing: UNIT 1: 05/03/2010 1 Arvind ShrivastavaDocument23 pagesCS601: Microprocessor & Interfacing: UNIT 1: 05/03/2010 1 Arvind ShrivastavaArvind ShrivastavaNo ratings yet

- 80486Document15 pages80486Namitha NairNo ratings yet

- Interrupt and Interfacing of 8086Document12 pagesInterrupt and Interfacing of 8086vreshmi885113No ratings yet

- 8051 TutorialDocument8 pages8051 TutorialVivek GuptaNo ratings yet

- Chapter 3Document16 pagesChapter 3زياد عبدالله عبدالحميدNo ratings yet

- MP Two Marks Jansi1Document34 pagesMP Two Marks Jansi1SAHEEM SAJILANo ratings yet

- Mic Module IVDocument11 pagesMic Module IVroshnibijuNo ratings yet

- 8259 PicDocument6 pages8259 PicJeslin JohnNo ratings yet

- MPMC Model Exam Answer KeyDocument21 pagesMPMC Model Exam Answer KeyVenkatesan SundaramNo ratings yet

- Microprocessor: Asst. Prof. Satyanarayan PradhanDocument3 pagesMicroprocessor: Asst. Prof. Satyanarayan PradhanAnurag PalNo ratings yet

- COE301 Lab 8 MIPS Exceptions and IODocument10 pagesCOE301 Lab 8 MIPS Exceptions and IOItz Sami UddinNo ratings yet

- Cs1304 Q&A MWDocument35 pagesCs1304 Q&A MWksrajasekarNo ratings yet

- Interrupts in 8086 MicroprocessorDocument8 pagesInterrupts in 8086 MicroprocessorGemechis GurmesaNo ratings yet

- MM Lab Viva QuestionsDocument7 pagesMM Lab Viva QuestionsDinesh SundarNo ratings yet

- 3002 Microprocessor - S4 - InterruptDocument13 pages3002 Microprocessor - S4 - InterruptLim Yee FattNo ratings yet

- Unit 1Document78 pagesUnit 1Vasunthara DNo ratings yet

- 3 Interrupts and Interrupt Service Routines: 3.1 What Is An Interrupt?Document11 pages3 Interrupts and Interrupt Service Routines: 3.1 What Is An Interrupt?Khalifa EltayebNo ratings yet

- EE2354 Question Bank BESTDocument18 pagesEE2354 Question Bank BESTGokul ChandrasekaranNo ratings yet

- An Interrupt Is An Event Which Informs The CPU That Its Service (Action) Is Needed. - Sources of InterruptsDocument20 pagesAn Interrupt Is An Event Which Informs The CPU That Its Service (Action) Is Needed. - Sources of InterruptsMurali KrishnaNo ratings yet

- An Over View of 8085Document12 pagesAn Over View of 8085nskprasad89No ratings yet

- DSPDocument63 pagesDSPNishita ParuchuriNo ratings yet

- Laboratory Manual Microprocessor and Micro Controller LaboratoryDocument19 pagesLaboratory Manual Microprocessor and Micro Controller LaboratoryDilip KumarNo ratings yet

- MODULE 3 MPDocument20 pagesMODULE 3 MPrinsha. febnNo ratings yet

- Assembly Lab 2Document9 pagesAssembly Lab 2Jefferson Medinaceli Malayao100% (1)

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- The Major Components of Unified Modelling Language: Deployment DiagramDocument10 pagesThe Major Components of Unified Modelling Language: Deployment DiagramVeda VyasNo ratings yet

- Lead Black SlideDocument52 pagesLead Black SlideVeda VyasNo ratings yet

- Multiply Two 8 Bit NumbersDocument3 pagesMultiply Two 8 Bit NumbersVeda VyasNo ratings yet

- Chapter 24 - Socket InterfaceDocument42 pagesChapter 24 - Socket InterfaceVeda VyasNo ratings yet

- Array ProcessorDocument19 pagesArray ProcessorVeda VyasNo ratings yet

- Integrity ConstraintDocument1 pageIntegrity ConstraintVeda VyasNo ratings yet

- Binary Number SystemDocument18 pagesBinary Number SystemMuhammad AliNo ratings yet

- Wind Load Calculations For PV Arrays: Solar America Board For Codes and StandardsDocument24 pagesWind Load Calculations For PV Arrays: Solar America Board For Codes and StandardsSalman KhanNo ratings yet

- Single Tuned Passive Harmonic Filter Design Considering Variances of Tuning and Quality FactorDocument8 pagesSingle Tuned Passive Harmonic Filter Design Considering Variances of Tuning and Quality FactorDeptiranjan MohapatraNo ratings yet

- Linsangan Vs TolentinoDocument2 pagesLinsangan Vs TolentinoDaniela Erika Beredo InandanNo ratings yet

- Summary of SEJ Gold Mining ConcessionDocument26 pagesSummary of SEJ Gold Mining ConcessionAgni NovasandiNo ratings yet

- 28 - Operator TrainingDocument101 pages28 - Operator TrainingRajesh Kumar100% (1)

- Villa v. SandiganbayanDocument14 pagesVilla v. SandiganbayanmisterdodiNo ratings yet

- Resume Dhiraj BeriDocument4 pagesResume Dhiraj BeriParth BeriNo ratings yet

- Taos TCS3472 DatasheetDocument26 pagesTaos TCS3472 DatasheetKathryn WorkmanNo ratings yet

- 10 BVDM Mediastandard Print 2016Document78 pages10 BVDM Mediastandard Print 2016Duy KhoaNo ratings yet

- Business English BrochureDocument12 pagesBusiness English BrochureGer Brenner100% (1)

- Abundance, Structure, and Spatial Mapping of Mangrove Diversity in Matalom, LeyteDocument1 pageAbundance, Structure, and Spatial Mapping of Mangrove Diversity in Matalom, Leyteeirene gomezNo ratings yet

- West Bengal Services Death-cum-Retirement Benefit Rules-1971 PDFDocument127 pagesWest Bengal Services Death-cum-Retirement Benefit Rules-1971 PDFচক্রকূট ভট্টাচার্যNo ratings yet

- SBD-E-Commerce and Internet MarketingDocument12 pagesSBD-E-Commerce and Internet MarketingjacvillarbaNo ratings yet

- Amrutha Raj (SIP)Document41 pagesAmrutha Raj (SIP)Rajasimha KalakondaNo ratings yet

- Annex05 Electric SchemeDocument1 pageAnnex05 Electric SchemeRobertoNo ratings yet

- Square Roots Worksheet: SolveDocument2 pagesSquare Roots Worksheet: SolvelgNo ratings yet

- Knowledge, Skills & Attributes: Maritime Human ResourcesDocument1 pageKnowledge, Skills & Attributes: Maritime Human Resources757rustamNo ratings yet

- Taking Bunkers: Job Safety AnalysisDocument4 pagesTaking Bunkers: Job Safety AnalysisOgunwa EmmanuelNo ratings yet

- Cover Letter UpesDocument1 pageCover Letter UpesRakesh PrasadNo ratings yet

- Sonoma User GuideDocument4 pagesSonoma User GuideAndrew FloresNo ratings yet

- At Am MethodDocument35 pagesAt Am MethodJeffersonNo ratings yet

- Introduction To ManagementDocument6 pagesIntroduction To ManagementVăn Đức LêNo ratings yet

- Chapter 4 111Document8 pagesChapter 4 111angelyn.ardenoNo ratings yet

- Marine Shoreline Design GuidelinesDocument419 pagesMarine Shoreline Design GuidelinesdunglxNo ratings yet

- Director of Lands vs. Roman Catholic BishopdocxDocument1 pageDirector of Lands vs. Roman Catholic BishopdocxMrsv VelacruzNo ratings yet

- VUL Mock Exam 1 (October 2018)Document12 pagesVUL Mock Exam 1 (October 2018)Alona Villamor ChancoNo ratings yet