Professional Documents

Culture Documents

G3-to-S0 Power Sequence

Uploaded by

Ashok Jangra0 ratings0% found this document useful (0 votes)

4 views1 pageschematic

Original Title

Sequence v31.8

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentschematic

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

4 views1 pageG3-to-S0 Power Sequence

Uploaded by

Ashok Jangraschematic

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

Power Sequencing

5.4.3.

G3-to-S0 Power-Up Sequence

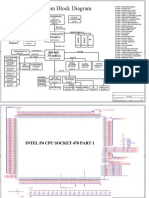

Figure 5-3 shows the C51/MCP51 G3-to-S0 Power-up Sequence diagram. This sequence is followed by the Cold Reset Sequence in Chapter 6 (see Figure 6-2).

P S 122

LP C_ P D# P S 121 HT _ V L D P S 115 +1 .2 V _ HT P S 1 16

H T V DD _E N

P S 1 14

CP U_V LD P S 112 +V _ C P U P S 1 13

CP UV DD _E N

P S 111

C LK OU T _ 2 0 0 MHZ L P C _ CL K

P S 1 10

Running Running

S US C LK (32 kH z)

P W R GD P S 108 C ORE P o w e rP l a n e s

P S 109

S LP _S 3 # P S 106

P S 107

P S 120 ME M_ V L D P S 105 +2 .5 V _ S U S +1 .25 V _V T T _ S U S S LP _S 5 # P S 104

P W R GD _ S B P S 1 01 2 5 Mh z xta l B U F_ 25 MH Z +5 V _ D UA L +3 .3 V _ D UA L +1 .5 V _ D UA L

P S 102

Running

P S 100

+3.0 V _ V B A T

CO RE P ow e r P la ne s inc lude :

+1 .2 V Co re , +1 .5 V _ P L L _H T , +3.3 V _ P LL _ HT , +1 .2 V _ P E _ P L L _ A V D D, +1.2 V _ P E _P L L_ DV D D, +1 .2V _ P E _ P L L _ C OR E , +1 .2 V _ P E _ D, +1 .2 V _ P E _ A , +3 .3 V _ P E _ P L L _ CORE , +1 .5 V _ S P _ P L L _ A V D D, +1.5 V _ S P _P L L_ DV D D, +1 .5V _ S P _ P L L _ C OR E ,, +1 .5 V _ S P _ D, +1 .5 V _ S P _ A , +3 .3 V _ S P _ P L L _ CORE , +3 .3 V _ P L L _C P U, +3 .3V _ S P _ P L L _ U S B , +3 .3 V , +5V

P ow e r P la ne s a re in Re d M CP 5 1 output s igna ls a re in Blue M othe rboa rd ge ne ra te d inputs to M C P 5 1 a re in P urple

Figure 5-3. C51/MCP51 Power-Up Sequence

DG-01632-001_v3.8 10/27/05

112

NVIDIA CONFIDENTIAL

You might also like

- Electronic Circuit Design Ideas: Edn Series for Design EngineersFrom EverandElectronic Circuit Design Ideas: Edn Series for Design EngineersRating: 5 out of 5 stars5/5 (2)

- SC1403 Data SheetDocument30 pagesSC1403 Data Sheetnomi_nomiNo ratings yet

- Itautec A7520 - 6-71-W2400-D03 GPDocument45 pagesItautec A7520 - 6-71-W2400-D03 GPAlex Morais67% (9)

- Water Level ControlDocument1 pageWater Level ControlRajasekar ElavarasanNo ratings yet

- F0af6 Clevo W830T W840TDocument46 pagesF0af6 Clevo W830T W840TOsvaldo LucianiNo ratings yet

- So Do Nguyen LyDocument1 pageSo Do Nguyen LyKhánh TrầnNo ratings yet

- Bài Tập 1: V C C - 5 VDocument21 pagesBài Tập 1: V C C - 5 VShin DongNo ratings yet

- P89V51Rd2 Microcontroller BoardDocument6 pagesP89V51Rd2 Microcontroller BoardlkpavangbhNo ratings yet

- KLBB Rnav (GPS) 35lDocument1 pageKLBB Rnav (GPS) 35lrotorbrentNo ratings yet

- PLL and Audio Circuit DiagramDocument11 pagesPLL and Audio Circuit DiagrampasantitoNo ratings yet

- Nguyen Ly Cube 5x5x5Document1 pageNguyen Ly Cube 5x5x5Phan VũNo ratings yet

- Layout Docdoc1Document2 pagesLayout Docdoc1Sharanu PatilNo ratings yet

- 16 AUV Motor ControllerDocument1 page16 AUV Motor ControllerGhazal IraniNo ratings yet

- C 5200 65e 001 Unifilar Sulfurosrev4 - 12 (Ocr)Document1 pageC 5200 65e 001 Unifilar Sulfurosrev4 - 12 (Ocr)Gianc87No ratings yet

- La GitaneDocument11 pagesLa GitaneCristian Alexis Vega100% (1)

- Ad 2. Aerodromes Vabp 2.1 Aerodrome Location Indicator and Name Vabp-Bhopal /domestic Vabp Ad 2.2 Aerodrome Geographical and Administrative DataDocument7 pagesAd 2. Aerodromes Vabp 2.1 Aerodrome Location Indicator and Name Vabp-Bhopal /domestic Vabp Ad 2.2 Aerodrome Geographical and Administrative DataShibin JohneyNo ratings yet

- Plant 5 MVA generation cell installation project (El QuimboDocument38 pagesPlant 5 MVA generation cell installation project (El QuimboYeissonSanabriaNo ratings yet

- MMLODocument12 pagesMMLOAr AbisaiNo ratings yet

- RPCL - GMW - 3Document1 pageRPCL - GMW - 3Sridhar Reddy GandraNo ratings yet

- ABB ACS800 Crane Drive Control 7.1 (Firmware Manual)Document216 pagesABB ACS800 Crane Drive Control 7.1 (Firmware Manual)Star Trek0% (1)

- Psychrometric Properties of Humid Air Calculation ProceduresDocument18 pagesPsychrometric Properties of Humid Air Calculation ProceduresArturoNo ratings yet

- Suzie Q: Transcribed by CCN Words and Music by Hawkins/Lewis/BroadwaterDocument6 pagesSuzie Q: Transcribed by CCN Words and Music by Hawkins/Lewis/BroadwaterMigliorino Carmelo0% (1)

- 8 Sensors Circuit DiagramDocument6 pages8 Sensors Circuit DiagramtrngocluanNo ratings yet

- List PompaDocument10 pagesList PompamarthtjuluNo ratings yet

- (Vaid1 7) IndoreDocument7 pages(Vaid1 7) IndoreShibin JohneyNo ratings yet

- Schematic Diagrams Appendix BDocument0 pagesSchematic Diagrams Appendix BfclodoaldoNo ratings yet

- JEPPESEN CUZCO STAR CHART UPDATESDocument22 pagesJEPPESEN CUZCO STAR CHART UPDATESoscar2k27No ratings yet

- CM8870/70C CMOS Integrated DTMF Receiver: California Micro DevicesDocument9 pagesCM8870/70C CMOS Integrated DTMF Receiver: California Micro Devicespilar12345678No ratings yet

- ht56r6x 6xxv110Document108 pagesht56r6x 6xxv110tanhaoclcNo ratings yet

- BHEL Auxiliary Systems DesignationsDocument13 pagesBHEL Auxiliary Systems Designationssuleman247No ratings yet

- Uha A Uha IhaDocument10 pagesUha A Uha IhaJuan MillánNo ratings yet

- Transmitter Section: VCC - Bar VCC - BarDocument2 pagesTransmitter Section: VCC - Bar VCC - BarsridharparthipanNo ratings yet

- So Do Mach Nguyen LyDocument1 pageSo Do Mach Nguyen LyNguyễn Thị Cẩm NhungNo ratings yet

- JeppView Mexico City Intl Airport ChartDocument21 pagesJeppView Mexico City Intl Airport ChartMartin Reyes RNo ratings yet

- MUAYATcffdddDocument2 pagesMUAYATcffdddSoekarman RucyNo ratings yet

- Irf 9 Z 24 NDocument9 pagesIrf 9 Z 24 NGiovanni Carrillo VillegasNo ratings yet

- Thermodynamics (Prausnitz) Manual SolutionDocument195 pagesThermodynamics (Prausnitz) Manual SolutionColin Zhang78% (9)

- OMDBDocument17 pagesOMDBKenneth WongNo ratings yet

- Irl 3705Document9 pagesIrl 3705Carlos De La Rosa SanchezNo ratings yet

- Airport Information: Details For Col Carlos Ciriani Santa RosaDocument8 pagesAirport Information: Details For Col Carlos Ciriani Santa RosaAlvaroFariasNo ratings yet

- WSSSDocument35 pagesWSSSaavianiacNo ratings yet

- Tps 51125Document37 pagesTps 51125Naresh Kumar100% (1)

- Rarts G 聞脚Llo GDocument78 pagesRarts G 聞脚Llo GAnonymous LvDzlYvvNo ratings yet

- Omdb/Dxb Dubai, Uae: Darax 1T Bubin 3TDocument25 pagesOmdb/Dxb Dubai, Uae: Darax 1T Bubin 3TMohannad AlamayrehNo ratings yet

- Commensurabilities among Lattices in PU (1,n). (AM-132), Volume 132From EverandCommensurabilities among Lattices in PU (1,n). (AM-132), Volume 132No ratings yet

- Physical Chemistry and Its Biological ApplicationsFrom EverandPhysical Chemistry and Its Biological ApplicationsRating: 3 out of 5 stars3/5 (1)

- PNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGFrom EverandPNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGNo ratings yet

- Method of Lines PDE Analysis in Biomedical Science and EngineeringFrom EverandMethod of Lines PDE Analysis in Biomedical Science and EngineeringNo ratings yet

- An Introduction to Equilibrium Thermodynamics: Pergamon Unified Engineering SeriesFrom EverandAn Introduction to Equilibrium Thermodynamics: Pergamon Unified Engineering SeriesNo ratings yet

- D500EDocument29 pagesD500EAshok JangraNo ratings yet

- Clevo d800p Sager Np8890Document114 pagesClevo d800p Sager Np8890Oprescu Sorin-ConstantinNo ratings yet

- Table 1 - 1: The Following Table Indicates Where To Find The Appropriate Schematic DiagramDocument32 pagesTable 1 - 1: The Following Table Indicates Where To Find The Appropriate Schematic DiagramAshok JangraNo ratings yet

- D870P Service ManualDocument96 pagesD870P Service Manualss87622No ratings yet

- D700T Block Diagram: Grantsdale GMCHDocument28 pagesD700T Block Diagram: Grantsdale GMCHAshok JangraNo ratings yet

- System Block Diagram: Sis 648FxDocument43 pagesSystem Block Diagram: Sis 648FxAshok JangraNo ratings yet

- Table 1 - 1: The Following Table Indicates Where To Find The Appropriate Schematic DiagramDocument32 pagesTable 1 - 1: The Following Table Indicates Where To Find The Appropriate Schematic DiagramAshok JangraNo ratings yet

- D700T Block Diagram: Grantsdale GMCHDocument28 pagesD700T Block Diagram: Grantsdale GMCHAshok JangraNo ratings yet

- Appendix B:Schematic DiagramsDocument44 pagesAppendix B:Schematic DiagramsAshok JangraNo ratings yet

- AMD CPU and Memory InterfaceDocument42 pagesAMD CPU and Memory InterfaceAshok JangraNo ratings yet

- Block Diagram: Sis656 GMCHDocument35 pagesBlock Diagram: Sis656 GMCHAshok JangraNo ratings yet

- Schematic Diagrams GuideDocument44 pagesSchematic Diagrams GuideAshok JangraNo ratings yet

- 71 D40u0 D04Document42 pages71 D40u0 D04Ashok JangraNo ratings yet

- Appendix B:Schematic DiagramsDocument36 pagesAppendix B:Schematic DiagramsAshok JangraNo ratings yet

- Clevo D400S 410SDocument113 pagesClevo D400S 410SIvanM72No ratings yet

- Clevo D400S 410SDocument113 pagesClevo D400S 410SIvanM72No ratings yet

- D470K/D400K System Block Diagram: VIA 8235 CE 539 mBGADocument42 pagesD470K/D400K System Block Diagram: VIA 8235 CE 539 mBGAAshok JangraNo ratings yet

- Banias Processor Block DiagramDocument43 pagesBanias Processor Block DiagramAshok JangraNo ratings yet

- D400J/D400K System Block Diagram: VIA 8235 CE 539 mBGADocument43 pagesD400J/D400K System Block Diagram: VIA 8235 CE 539 mBGAAshok JangraNo ratings yet

- Clevo 8880 EsmDocument103 pagesClevo 8880 EsmAshok JangraNo ratings yet

- D400 System Block Diagram: Sis M650Document35 pagesD400 System Block Diagram: Sis M650Ashok JangraNo ratings yet

- Appendix B:Schematic DiagramsDocument42 pagesAppendix B:Schematic DiagramsAshok JangraNo ratings yet

- Aw 1Document933 pagesAw 1Ashok JangraNo ratings yet

- 5600DDocument30 pages5600DAshok JangraNo ratings yet

- Dell Latitude C640 Schematics Quanta Comp.Document37 pagesDell Latitude C640 Schematics Quanta Comp.phoenix136No ratings yet

- 888EDocument45 pages888EAshok JangraNo ratings yet

- Power SequenceDocument3 pagesPower SequenceAshok JangraNo ratings yet

- Aw1 MB 0705Document41 pagesAw1 MB 0705Ashok JangraNo ratings yet

- 跑马灯Port80Document6 pages跑马灯Port80Ashok JangraNo ratings yet