Professional Documents

Culture Documents

Ee101 Basics 1

Uploaded by

Shreeroop AjaykumarOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ee101 Basics 1

Uploaded by

Shreeroop AjaykumarCopyright:

Available Formats

EE101: Basics KCL, KVL, power, Thevenins theorem

M. B. Patil

mbpatil@ee.iitb.ac.in Department of Electrical Engineering Indian Institute of Technology Bombay

M. B. Patil, IIT Bombay

Kirchhos laws

A i2 v2

v4

v3 R2 i3 v6 R1 v1 i1

B i6 V0

v4 R3 i4 v5

C i5 I0

M. B. Patil, IIT Bombay

Kirchhos laws

A i2 v2

v4

v3 R2 i3 v6 R1 v1 i1

B i6 V0

v4 R3 i4 v5

C i5 I0

* Kirchhos current law (KCL): P ik = 0 at each node.

M. B. Patil, IIT Bombay

Kirchhos laws

A i2 v2

v4

v3 R2 i3 v6 R1 v1 i1

B i6 V0

v4 R3 i4 v5

C i5 I0

* Kirchhos current law (KCL): P ik = 0 at each node. e.g., at node B, i3 + i6 + i4 = 0.

M. B. Patil, IIT Bombay

Kirchhos laws

A i2 v2

v4

v3 R2 i3 v6 R1 v1 i1

B i6 V0

v4 R3 i4 v5

C i5 I0

* Kirchhos current law (KCL): P ik = 0 at each node. e.g., at node B, i3 + i6 + i4 = 0. (We have followed the convention that current leaving a node is positive.)

M. B. Patil, IIT Bombay

Kirchhos laws

A i2 v2

v4

v3 R2 i3 v6 R1 v1 i1

B i6 V0

v4 R3 i4 v5

C i5 I0

* Kirchhos current law (KCL): P ik = 0 at each node. e.g., at node B, i3 + i6 + i4 = 0. (We have followed the convention that current leaving a node is positive.) * Kirchhos voltage law (KVL): P vk = 0 for each loop.

M. B. Patil, IIT Bombay

Kirchhos laws

A i2 v2

v4

v3 R2 i3 v6 R1 v1 i1

B i6 V0

v4 R3 i4 v5

C i5 I0

* Kirchhos current law (KCL): P ik = 0 at each node. e.g., at node B, i3 + i6 + i4 = 0. (We have followed the convention that current leaving a node is positive.) * Kirchhos voltage law (KVL): P vk = 0 for each loop. e.g., v3 + v6 v1 v2 = 0.

M. B. Patil, IIT Bombay

Kirchhos laws

A i2 v2

v4

v3 R2 i3 v6 R1 v1 i1

B i6 V0

v4 R3 i4 v5

C i5 I0

* Kirchhos current law (KCL): P ik = 0 at each node. e.g., at node B, i3 + i6 + i4 = 0. (We have followed the convention that current leaving a node is positive.) * Kirchhos voltage law (KVL): P vk = 0 for each loop. e.g., v3 + v6 v1 v2 = 0. (We have followed the convention that voltage drop across a branch is positive.)

M. B. Patil, IIT Bombay

Circuit elements

Element Resistor

Symbol

v i

Equation v =Ri v =L di dt dv dt

Inductor

i

Capacitor

i

i =C

v i

C

Diode BJT

to be discussed to be discussed

E

M. B. Patil, IIT Bombay

Sources

Element Independent Voltage source Current source Dependent VCVS VCCS CCVS CCCS

Symbol

v i v i v i v i v i v i

Equation v (t ) = vs (t ) i (t ) = is (t ) v (t ) = vc (t ) i (t ) = g vc (t ) v (t ) = r ic (t ) i (t ) = ic (t )

* , : dimensionless, r : , g : 1 or

(mho)

* The subscript c denotes the controlling voltage or current.

M. B. Patil, IIT Bombay

Instantaneous power absorbed by an element

i1 V1 VN iN

i2 V2 V3 i3

P (t ) = V 1 (t ) i 1 (t ) + V 2 (t ) i 2 (t ) + + V N (t ) i N (t ) , where V1 , V2 , etc. are node voltages (measured with respect to a reference node).

M. B. Patil, IIT Bombay

Instantaneous power absorbed by an element

i1 V1 VN iN

i2 V2 V3 i3

P (t ) = V 1 (t ) i 1 (t ) + V 2 (t ) i 2 (t ) + + V N (t ) i N (t ) , where V1 , V2 , etc. are node voltages (measured with respect to a reference node).

* two-terminal element:

v V1 i1 i2 V2

P = V1 i 1 + V2 i 2 = V 1 i 1 + V 2 ( i 1 ) = [V 1 V 2 ] i 1 = v i 1

M. B. Patil, IIT Bombay

Instantaneous power absorbed by an element

i1 V1 VN iN

i2 V2 V3 i3

P (t ) = V 1 (t ) i 1 (t ) + V 2 (t ) i 2 (t ) + + V N (t ) i N (t ) , where V1 , V2 , etc. are node voltages (measured with respect to a reference node).

* two-terminal element:

v V1 i1 i2 V2

P = V1 i 1 + V2 i 2 = V 1 i 1 + V 2 ( i 1 ) = [V 1 V 2 ] i 1 = v i 1 P = V B i B + V C i C + V E ( i E )

iC iE

* three-terminal element:

VC VB iB VE

= V B i B + V C i C V E (i B + i C ) = (VB VE ) iB + (VC VE ) iC = VBE iB + VCE iE

M. B. Patil, IIT Bombay

Instantaneous power

* A resistor can only absorb power (from the circuit) since v and i have the same sign, making P > 0. The energy absorbed by a resistor goes in heating the resistor and the rest of the world.

M. B. Patil, IIT Bombay

Instantaneous power

* A resistor can only absorb power (from the circuit) since v and i have the same sign, making P > 0. The energy absorbed by a resistor goes in heating the resistor and the rest of the world. * Often, a heat sink is provided to dissipate the thermal energy eectively so that the device temperature does not become too high.

M. B. Patil, IIT Bombay

Instantaneous power

* A resistor can only absorb power (from the circuit) since v and i have the same sign, making P > 0. The energy absorbed by a resistor goes in heating the resistor and the rest of the world. * Often, a heat sink is provided to dissipate the thermal energy eectively so that the device temperature does not become too high. * A source (e.g., a DC voltage source) can absorb or deliver power since the signs of v and i are independent. For example, when a battery is charged, it absorbs energy which gets stored within.

M. B. Patil, IIT Bombay

Instantaneous power

* A resistor can only absorb power (from the circuit) since v and i have the same sign, making P > 0. The energy absorbed by a resistor goes in heating the resistor and the rest of the world. * Often, a heat sink is provided to dissipate the thermal energy eectively so that the device temperature does not become too high. * A source (e.g., a DC voltage source) can absorb or deliver power since the signs of v and i are independent. For example, when a battery is charged, it absorbs energy which gets stored within. * A capacitor can absorb or deliver power. When it is absorbing power, its charge builds up. Similarly, an inductor can store energy (in the form of magnetic ux).

M. B. Patil, IIT Bombay

Resistors in series

v1

A

v2 R2

v3

B A

v i

B

R1

R3

M. B. Patil, IIT Bombay

Resistors in series

v1

A

v2 R2

v3

B A

v i

B

R1

R3

v1 = i R1 , v2 = i R2 , v3 = i R3 , v = v1 + v2 + v3 = i (R1 + R2 + R3 )

M. B. Patil, IIT Bombay

Resistors in series

v1

A

v2 R2

v3

B A

v i

B

R1

R3

v1 = i R1 , v2 = i R2 , v3 = i R3 , v = v1 + v2 + v3 = i (R1 + R2 + R3 ) * The equivalent resistance is Req = R1 + R2 + R3 .

M. B. Patil, IIT Bombay

Resistors in series

v1

A

v2 R2

v3

B A

v i

B

R1

R3

v1 = i R1 , v2 = i R2 , v3 = i R3 , v = v1 + v2 + v3 = i (R1 + R2 + R3 ) * The equivalent resistance is Req = R1 + R2 + R3 . * The voltage drop across Rk is v Rk . Req

M. B. Patil, IIT Bombay

Resistors in parallel

v i1

A

R1

B A

v i

B

i2 i3

R2 R3

M. B. Patil, IIT Bombay

Resistors in parallel

v i1

A

R1

B A

v i

B

i2 i3

R2 R3

i1 = G1 v , i2 = G2 v , i3 = G3 v , where G1 = 1/R1 , etc. i = i1 + i2 + i3 = (G1 + G2 + G3 ) v .

M. B. Patil, IIT Bombay

Resistors in parallel

v i1

A

R1

B A

v i

B

i2 i3

R2 R3

i1 = G1 v , i2 = G2 v , i3 = G3 v , where G1 = 1/R1 , etc. i = i1 + i2 + i3 = (G1 + G2 + G3 ) v . * The equivalent conductance is Geq = G1 + G2 + G3 , and the equivalent resistance is Req = 1/Geq .

M. B. Patil, IIT Bombay

Resistors in parallel

v i1

A

R1

B A

v i

B

i2 i3

R2 R3

i1 = G1 v , i2 = G2 v , i3 = G3 v , where G1 = 1/R1 , etc. i = i1 + i2 + i3 = (G1 + G2 + G3 ) v . * The equivalent conductance is Geq = G1 + G2 + G3 , and the equivalent resistance is Req = 1/Geq . * The current through Rk is i Gk . Geq

M. B. Patil, IIT Bombay

Resistors in parallel

v i1

A

R1

B A

v i

B

i2 i3

R2 R3

i1 = G1 v , i2 = G2 v , i3 = G3 v , where G1 = 1/R1 , etc. i = i1 + i2 + i3 = (G1 + G2 + G3 ) v . * The equivalent conductance is Geq = G1 + G2 + G3 , and the equivalent resistance is Req = 1/Geq . * The current through Rk is i Gk . Geq

* If N = 2, we have R1 R2 R2 R1 Req = , i1 = i , i2 = i . R1 + R2 R1 + R2 R1 + R2

M. B. Patil, IIT Bombay

Resistors in parallel

v i1

A

R1

B A

v i

B

i2 i3

R2 R3

i1 = G1 v , i2 = G2 v , i3 = G3 v , where G1 = 1/R1 , etc. i = i1 + i2 + i3 = (G1 + G2 + G3 ) v . * The equivalent conductance is Geq = G1 + G2 + G3 , and the equivalent resistance is Req = 1/Geq . * The current through Rk is i Gk . Geq

* If N = 2, we have R1 R2 R2 R1 Req = , i1 = i , i2 = i . R1 + R2 R1 + R2 R1 + R2 * If Rk = 0, all of the current will go through Rk .

M. B. Patil, IIT Bombay

Example

i1 4 3 6V i2

5

(a)

2.5

2.5

Example

i1 4 3 6V i2

5

(a)

2.5

2.5

Example

i1 4 3 6V i2

i1 4 i2 3 5 2.5 2.5

(b)

2 1 3

6V

(a)

Example

i1 4 3 6V i2

i1 4 i2 3 5 2.5 2.5

(b)

2 1 3

6V

(a)

Example

i1 4 3 6V i2

i1 4 i2 3 5 2.5 2.5

(b)

2 1 3

6V

(a)

i1 4 6V

(c)

i2 6 3

Example

i1 4 3 6V i2

i1 4 i2 3 5 2.5 2.5

(b)

2 1 3

6V

(a)

i1 4 6V

(c)

i2 6 3

Example

i1 4 3 6V i2

i1 4 i2 3 5 2.5 2.5

(b)

2 1 3

6V

(a)

3 i1 4 6V i2 6 3

(d)

i1

4 2 6V

(c)

Example

i1 4 3 6V i2

i1 4 i2 3 5 2.5 2.5

(b)

2 1 3

6V

(a)

3 i1 4 6V i2 6 3

(d)

i1

4 2 6V

i1 =

6V = 1A. 4+2

(c)

Example

i1 4 3 6V i2

i1 4 i2 3 5 2.5 2.5

(b)

2 1 3

6V

(a)

3 i1 4 6V i2 6 3

(d)

i1

4 2 6V

i1 =

6V = 1A. 4+2

2 6 = A. i2 = i1 6+3 3

(c)

M. B. Patil, IIT Bombay

Example

i1 4 3 6V i2

i1 4 i2 3 5 2.5 2.5

(b)

2 1 3

6V

(a)

3 i1 4 6V i2 6 3

(d)

i1

4 2 6V

i1 =

6V = 1A. 4+2

2 6 = A. i2 = i1 6+3 3

(c)

Home work: * Verify that KCL and KVL are satised for each node/loop.

M. B. Patil, IIT Bombay

Example

i1 4 3 6V i2

i1 4 i2 3 5 2.5 2.5

(b)

2 1 3

6V

(a)

3 i1 4 6V i2 6 3

(d)

i1

4 2 6V

i1 =

6V = 1A. 4+2

2 6 = A. i2 = i1 6+3 3

(c)

Home work: * Verify that KCL and KVL are satised for each node/loop. * Verify that the total power absorbed by the resistors is equal to the power supplied by the source.

M. B. Patil, IIT Bombay

Nodal analysis

V1

R1 R2

V2 R3 v3 k v3

I0

0

R4

V3

M. B. Patil, IIT Bombay

Nodal analysis

* Take some node as the reference node and denote the node voltages of the remaining nodes by V1 , V2 , etc.

V1

R1 R2

V2 R3 v3 k v3

I0

0

R4

V3

M. B. Patil, IIT Bombay

Nodal analysis

* Take some node as the reference node and denote the node voltages of the remaining nodes by V1 , V2 , etc. * Write KCL at each node in terms of the node voltages. Follow a xed convention, e.g., current leaving a node is positive.

V2 R3 v3 k v3 0 R4 V3

V1

R1 R2

I0

M. B. Patil, IIT Bombay

Nodal analysis

* Take some node as the reference node and denote the node voltages of the remaining nodes by V1 , V2 , etc. * Write KCL at each node in terms of the node voltages. Follow a xed convention, e.g., current leaving a node is positive.

V2 R3 v3 k v3 0 R4 V3

V1

R1 R2

I0

1 ( V 1 V 2 ) I0 k ( V 2 V 3 ) = 0 , R1 1 1 1 (V 2 V 1 ) + (V 2 V 3 ) + (V 2 ) = 0 , R1 R3 R2 1 1 k (V 2 V 3 ) + (V 3 V 2 ) + (V 3 ) = 0 . R3 R4

M. B. Patil, IIT Bombay

Nodal analysis

* Take some node as the reference node and denote the node voltages of the remaining nodes by V1 , V2 , etc. * Write KCL at each node in terms of the node voltages. Follow a xed convention, e.g., current leaving a node is positive.

V2 R3 v3 k v3 0 R4 V3

V1

R1 R2

I0

1 ( V 1 V 2 ) I0 k ( V 2 V 3 ) = 0 , R1 1 1 1 (V 2 V 1 ) + (V 2 V 3 ) + (V 2 ) = 0 , R1 R3 R2 1 1 k (V 2 V 3 ) + (V 3 V 2 ) + (V 3 ) = 0 . R3 R4 * Solve for the node voltages branch voltages and currents.

M. B. Patil, IIT Bombay

Nodal analysis

* Take some node as the reference node and denote the node voltages of the remaining nodes by V1 , V2 , etc. * Write KCL at each node in terms of the node voltages. Follow a xed convention, e.g., current leaving a node is positive.

V2 R3 v3 k v3 0 R4 V3

V1

R1 R2

I0

1 ( V 1 V 2 ) I0 k ( V 2 V 3 ) = 0 , R1 1 1 1 (V 2 V 1 ) + (V 2 V 3 ) + (V 2 ) = 0 , R1 R3 R2 1 1 k (V 2 V 3 ) + (V 3 V 2 ) + (V 3 ) = 0 . R3 R4 * Solve for the node voltages branch voltages and currents. * Remark: Nodal analysis needs to be modied if there are voltage sources.

M. B. Patil, IIT Bombay

Mesh analysis

R1

R2

Vs i1 is

R3 i2

r1 is

M. B. Patil, IIT Bombay

Mesh analysis

R1

R2

Vs i1 is

R3 i2

r1 is

* Write KVL for each loop in terms of the mesh currents i1 and i2 . Use a xed convention, e.g., voltage drop is positive. (Note that is = i1 i2 .)

M. B. Patil, IIT Bombay

Mesh analysis

R1

R2

Vs i1 is

R3 i2

r1 is

* Write KVL for each loop in terms of the mesh currents i1 and i2 . Use a xed convention, e.g., voltage drop is positive. (Note that is = i1 i2 .) Vs + i1 R1 + (i1 i2 ) R3 = 0 , R2 i2 + r1 (i1 i2 ) + (i2 i1 ) R3 = 0 .

M. B. Patil, IIT Bombay

Mesh analysis

R1

R2

Vs i1 is

R3 i2

r1 is

* Write KVL for each loop in terms of the mesh currents i1 and i2 . Use a xed convention, e.g., voltage drop is positive. (Note that is = i1 i2 .) Vs + i1 R1 + (i1 i2 ) R3 = 0 , R2 i2 + r1 (i1 i2 ) + (i2 i1 ) R3 = 0 . * Solve for i1 and i2 compute other quantities of interest (branch currents and branch voltages).

M. B. Patil, IIT Bombay

Linearity and superposition

* A circuit containing independent sources, dependent sources, and resistors is linear, i.e., the system of equations describing the circuit is linear.

M. B. Patil, IIT Bombay

Linearity and superposition

* A circuit containing independent sources, dependent sources, and resistors is linear, i.e., the system of equations describing the circuit is linear. * The dependent sources are assumed to be linear, e.g., if we have a CCVS with 2 + b , the resulting system will be no longer linear. v = a ic

M. B. Patil, IIT Bombay

Linearity and superposition

* A circuit containing independent sources, dependent sources, and resistors is linear, i.e., the system of equations describing the circuit is linear. * The dependent sources are assumed to be linear, e.g., if we have a CCVS with 2 + b , the resulting system will be no longer linear. v = a ic * For a linear system, we can apply the principle of superposition.

M. B. Patil, IIT Bombay

Linearity and superposition

* A circuit containing independent sources, dependent sources, and resistors is linear, i.e., the system of equations describing the circuit is linear. * The dependent sources are assumed to be linear, e.g., if we have a CCVS with 2 + b , the resulting system will be no longer linear. v = a ic * For a linear system, we can apply the principle of superposition. * In the context of circuits, superposition enables us to consider the independent sources one at a time, compute the desired quantity of interest in each case, and get the net result by adding the individual contributions.

M. B. Patil, IIT Bombay

Linearity and superposition

* A circuit containing independent sources, dependent sources, and resistors is linear, i.e., the system of equations describing the circuit is linear. * The dependent sources are assumed to be linear, e.g., if we have a CCVS with 2 + b , the resulting system will be no longer linear. v = a ic * For a linear system, we can apply the principle of superposition. * In the context of circuits, superposition enables us to consider the independent sources one at a time, compute the desired quantity of interest in each case, and get the net result by adding the individual contributions. * Caution: Superposition cannot be applied to dependent sources.

M. B. Patil, IIT Bombay

Superposition

* Superposition refers to superposition of response due to independent sources.

M. B. Patil, IIT Bombay

Superposition

* Superposition refers to superposition of response due to independent sources. * We can consider one independent source at a time, deactivate all other independent sources.

M. B. Patil, IIT Bombay

Superposition

* Superposition refers to superposition of response due to independent sources. * We can consider one independent source at a time, deactivate all other independent sources. * Deactivating a current source is = 0, i.e., replace the current source with an open circuit.

M. B. Patil, IIT Bombay

Superposition

* Superposition refers to superposition of response due to independent sources. * We can consider one independent source at a time, deactivate all other independent sources. * Deactivating a current source is = 0, i.e., replace the current source with an open circuit. * Deactivating a voltage source vs = 0, i.e., replace the voltage source with a short circuit.

M. B. Patil, IIT Bombay

Example

2 i1 18 V 4 3A

Example

Case 1: Keep Vs , deactivate Is . 2 2 i1 18 V 4 3A 4 18 V i1

Example

Case 1: Keep Vs , deactivate Is . 2 2 i1 18 V 4 3A 4 18 V i1 (1) i1 = 3 A

Example

Case 1: Keep Vs , deactivate Is . 2 2 i1 18 V 4 3A Case 2: Keep Is , deactivate Vs . 2 i1 4 3A 4 18 V i1 (1) i1 = 3 A

Example

Case 1: Keep Vs , deactivate Is . 2 2 i1 18 V 4 3A Case 2: Keep Is , deactivate Vs . 2 i1 4 3A (2) i1 = 3 A 2 = 1A 2+4 4 18 V i1 (1) i1 = 3 A

Example

Case 1: Keep Vs , deactivate Is . 2 2 i1 18 V 4 3A Case 2: Keep Is , deactivate Vs . 2 (1) (2) inet 1 = i1 + i1 = 3 + 1 = 4 A i1 4 3A (2) i1 = 3 A 2 = 1A 2+4 4 18 V i1 (1) i1 = 3 A

M. B. Patil, IIT Bombay

Example

i 1

12 V

6A 2i

Example

Case 1: Keep Vs , deactivate Is .

i 1 i 1 6A 2i 12 V v 3

12 V

2i

Example

Case 1: Keep Vs , deactivate Is .

i 1 i 1 6A 2i 12 V v 3

12 V

3 KVL: 12 + 3 i + 2 i + i = 0 i = 2 A , v(1) = 6 V .

2i

Example

Case 1: Keep Vs , deactivate Is .

i 1 i 1 6A 2i 12 V v 3

12 V

3 KVL: 12 + 3 i + 2 i + i = 0 i = 2 A , v(1) = 6 V .

2i

Case 2: Keep Is , deactivate Vs .

i 1

6A 2i

Example

Case 1: Keep Vs , deactivate Is .

i 1 i 1 6A 2i 12 V v 3

12 V

3 KVL: 12 + 3 i + 2 i + i = 0 i = 2 A , v(1) = 6 V .

2i

Case 2: Keep Is , deactivate Vs .

i 1

3 KVL: i + (6 + i) 3 + 2 i = 0 6A i = 3 A , v(2) = (3 + 6) 3 = 9 V .

2i

Example

Case 1: Keep Vs , deactivate Is .

i 1 i 1 6A 2i 12 V v 3

12 V

3 KVL: 12 + 3 i + 2 i + i = 0 i = 2 A , v(1) = 6 V .

2i

Case 2: Keep Is , deactivate Vs .

vnet = v(1) + v(2) = 6 + 9 = 15 V

i 1

3 KVL: i + (6 + i) 3 + 2 i = 0 6A i = 3 A , v(2) = (3 + 6) 3 = 9 V .

2i

M. B. Patil, IIT Bombay

Superposition: Why does it work?

V1 R1 Vs 0 A R2 R3

V2 B Is

M. B. Patil, IIT Bombay

Superposition: Why does it work?

V1 R1 Vs 0 A R2 R3

V2 B Is

KCL at nodes A and B: 1 1 1 (V 1 V s ) + V1 + (V 1 V 2 ) = 0 , R1 R2 R3 1 (V 2 V 1 ) = 0 . Is + R3

M. B. Patil, IIT Bombay

Superposition: Why does it work?

V1 R1 Vs 0 A R2 R3

V2 B Is

KCL at nodes A and B: 1 1 1 (V 1 V s ) + V1 + (V 1 V 2 ) = 0 , R1 R2 R3 1 (V 2 V 1 ) = 0 . Is + R3 Writing in a matrix form, we get (using G1 = 1/R1 , etc.), G1 + G2 + G3 G3 G3 G3 V1 V2 = G1 Vs Is

M. B. Patil, IIT Bombay

Superposition: Why does it work?

V1 R1 Vs 0 A R2 R3

V2 B Is

KCL at nodes A and B: 1 1 1 (V 1 V s ) + V1 + (V 1 V 2 ) = 0 , R1 R2 R3 1 (V 2 V 1 ) = 0 . Is + R3 Writing in a matrix form, we get (using G1 = 1/R1 , etc.), G1 + G2 + G3 G3 i.e., A V1 V2 = G3 G3 G1 Vs Is V1 V2 V1 V2 = G1 Vs Is

1

=A

G1 Vs Is

M. B. Patil, IIT Bombay

Superposition: Why does it work?

V1 R1 Vs 0 A R2 R3

V2 B Is

V1 V2

=A

G1 Vs Is

m11 m21

m12 m22

G1 Vs Is

M. B. Patil, IIT Bombay

Superposition: Why does it work?

V1 R1 Vs 0 A R2 R3

V2 B Is

V1 V2

=A

G1 Vs Is

m11 m21

m12 m22

G1 Vs Is

We are now in a position to see why superposition works. V1 V2 = m11 G1 m21 G1 m12 m22 Vs 0 m11 G1 + m21 G1 m12 m22 0 Is " V1 V2

(1) (1)

# " +

V1 V2

(2) (2)

# .

M. B. Patil, IIT Bombay

Superposition: Why does it work?

V1 R1 Vs 0 A R2 R3

V2 B Is

V1 V2

=A

G1 Vs Is

m11 m21

m12 m22

G1 Vs Is

We are now in a position to see why superposition works. V1 V2 = m11 G1 m21 G1 m12 m22 Vs 0 m11 G1 + m21 G1 m12 m22 0 Is " V1 V2

(1) (1)

# " +

V1 V2

(2) (2)

# .

The rst vector is the response due to Vs alone (and Is deactivated). The second vector is the response due to Is alone (and Vs deactivated).

M. B. Patil, IIT Bombay

Superposition: Why does it work?

V1 R1 Vs 0 A R2 R3

V2 B Is

V1 V2

=A

G1 Vs Is

m11 m21

m12 m22

G1 Vs Is

We are now in a position to see why superposition works. V1 V2 = m11 G1 m21 G1 m12 m22 Vs 0 m11 G1 + m21 G1 m12 m22 0 Is " V1 V2

(1) (1)

# " +

V1 V2

(2) (2)

# .

The rst vector is the response due to Vs alone (and Is deactivated). The second vector is the response due to Is alone (and Vs deactivated). All other currents and voltages are linearly related to V1 and V2 Any voltage (node voltage or branch voltage) or current can also be computed using superposition.

M. B. Patil, IIT Bombay

Thevenins theorem

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

Thevenins theorem

RTh

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

VTh

B B

M. B. Patil, IIT Bombay

Thevenins theorem

RTh

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

VTh

B B

* VTh is simply VAB when nothing is connected on the other side, i.e., VTh = Voc .

M. B. Patil, IIT Bombay

Thevenins theorem

RTh

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

VTh

B B

* VTh is simply VAB when nothing is connected on the other side, i.e., VTh = Voc . * RTh can be found by dierent methods.

M. B. Patil, IIT Bombay

Thevenins theorem: RTh

Method 1:

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

VTh

B B

* Deactivate all independent sources.

Thevenins theorem: RTh

Method 1:

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

VTh

B B

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

* Deactivate all independent sources.

Thevenins theorem: RTh

Method 1:

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

VTh

B B

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

* Deactivate all independent sources. * RTh can often be found by inspection.

Thevenins theorem: RTh

Method 1:

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

A Is

VTh Vs

B B B

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

* Deactivate all independent sources. * RTh can often be found by inspection. * RTh may be found by connecting a test source.

Thevenins theorem: RTh

Method 1:

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

A Is

VTh Vs

B B B

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

Vs Is

B B B

* Deactivate all independent sources. * RTh can often be found by inspection. * RTh may be found by connecting a test source.

Thevenins theorem: RTh

Method 1:

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

A Is

VTh Vs

B B B

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

RTh

A A

Vs Is

B B B

* Deactivate all independent sources. * RTh can often be found by inspection. * RTh may be found by connecting a test source.

M. B. Patil, IIT Bombay

Thevenins theorem: RTh

Method 2:

A

Voc

* Find Voc .

Thevenins theorem: RTh

Method 2:

A A

Voc

Isc

* Find Voc . * Find Isc .

M. B. Patil, IIT Bombay

Thevenins theorem: RTh

Method 2:

A A

Voc

Isc

* Find Voc . * Find Isc . Voc * RTh = . Isc

M. B. Patil, IIT Bombay

Thevenins theorem: RTh

Method 2:

A A

Voc

Isc

* Find Voc . * Find Isc . Voc * RTh = . Isc * Note: Sources are not deactivated.

M. B. Patil, IIT Bombay

Thevenins theorem: example

6 R1 3 9V R2 R3

2

A

RL

B

Thevenins theorem: example

6 R1 3 9V R2 R3

2

A

RTh

RL

B

VTh

RL

B

Thevenins theorem: example

6 R1 3 9V R2 R3

2

A

RTh

RL

B

VTh

RL

B

VTh :

2

A

3 9V

Voc

B

Thevenins theorem: example

6 R1 3 9V R2 R3

2

A

RTh

RL

B

VTh

RL

B

VTh :

2

A

3 9V

Voc

B

Voc = 9 V = 9V

3 6+3 1 = 3V 3

Thevenins theorem: example

6 R1 3 9V R2 R3

2

A

RTh

RL

B

VTh

RL

B

VTh :

2

A

RTh :

2

A

3 9V

Voc

B

3

B

Voc = 9 V = 9V

3 6+3 1 = 3V 3

Thevenins theorem: example

6 R1 3 9V R2 R3

2

A

RTh

RL

B

VTh

RL

B

VTh :

2

A

RTh :

2

A

3 9V

Voc

B

3

B

Voc = 9 V

3 6+3

RTh = (R1

R2 ) + R3 = (3

6) + 2

1 = 9V = 3V 3

12 =3 +2 = 4 1+2

Thevenins theorem: example

6 R1 3 9V R2 R3

2

A

RTh

RL

B

VTh

RL R L

B

3V

RL

VTh :

2

A

RTh :

2

A

3 9V

Voc

B

3

B

Voc = 9 V

3 6+3

RTh = (R1

R2 ) + R3 = (3

6) + 2

1 = 9V = 3V 3

12 =3 +2 = 4 1+2

M. B. Patil, IIT Bombay

Maximum power transfer

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

iL RL

Maximum power transfer

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

iL RL

* Power transferred to load is, 2R . PL = iL L

Maximum power transfer

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

iL RL

* Power transferred to load is, 2R . PL = iL L * For a given black box, what is the value of RL for which PL is maximum?

Maximum power transfer

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

iL RL

* Power transferred to load is, 2R . PL = iL L * For a given black box, what is the value of RL for which PL is maximum? * Replace the black box with its Thevenin equivalent.

Maximum power transfer

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

iL RL

* Power transferred to load is, 2R . PL = iL L * For a given black box, what is the value of RL for which PL is maximum? * Replace the black box with its Thevenin equivalent.

RTh

iL VTh RL

B

Maximum power transfer

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

iL RL

* Power transferred to load is, 2R . PL = iL L * For a given black box, what is the value of RL for which PL is maximum? * Replace the black box with its Thevenin equivalent.

RTh

iL VTh RL

* iL =

B

VTh , RTh + RL

2 PL = VTh

RL . (RTh + RL )2

Maximum power transfer

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

iL RL

* Power transferred to load is, 2R . PL = iL L * For a given black box, what is the value of RL for which PL is maximum? * Replace the black box with its Thevenin equivalent.

RTh

iL VTh RL

* iL =

B

VTh , RTh + RL

2 PL = VTh

RL . (RTh + RL )2

* For

dPL = 0 , we need dRL

(RTh + RL )2 RL 2 (RTh + RL ) = 0, (RTh + RL )4 i.e., RTh + RL = 2 RL RL = RTh .

Maximum power transfer

Circuit

(resistors, voltage sources, current sources, CCVS, CCCS, VCVS, VCCS)

iL RL

* Power transferred to load is, 2R . PL = iL L * For a given black box, what is the value of RL for which PL is maximum? * Replace the black box with its Thevenin equivalent.

RTh

iL VTh RL

* iL =

B

VTh , RTh + RL

PL Pmax L

2 PL = VTh

RL . (RTh + RL )2

* For

dPL = 0 , we need dRL

(RTh + RL )2 RL 2 (RTh + RL ) = 0, (RTh + RL )4 i.e., RTh + RL = 2 RL RL = RTh .

RL RL = RTh

M. B. Patil, IIT Bombay

Maximum power transfer: example

Find RL for which PL is maximum. 3 2 R1 R3 6 12 V R2 2A

RL

B

Maximum power transfer: example

Find RL for which PL is maximum. 3 2 R1 R3 6 12 V R2 3 R1 2 2A

RL

B

RTh :

R3 6 R2

B

Maximum power transfer: example

Find RL for which PL is maximum. 3 2 R1 R3 6 12 V R2 3 R1 2 2A

RL

B

RTh :

R3 6 R2

B

RTh = (R1 =3

R2 ) + R3 = (3 12 +2 = 4 1+2

6) + 2

Maximum power transfer: example

Find RL for which PL is maximum. 3 2 R1 R3 6 12 V R2 3 R1 2 2A

Voc : R1

2

A

R3 6

RL 12 V

B

R2

2A

B

RTh :

R3 6 R2

B

RTh = (R1 =3

R2 ) + R3 = (3 12 +2 = 4 1+2

6) + 2

Maximum power transfer: example

Find RL for which PL is maximum. 3 2 R1 R3 6 12 V R2 3 R1 2 2A

Voc : R1

2

A

R3 6

RL 12 V

B

R2

2A

B

RTh :

R3 6 R2

B

Use superposition to nd Voc : 3 2

A

3 R1 R2

B

2

A

R1 12 V R2

R3 6

R3 6 2A

B

RTh = (R1

R2 ) + R3 = (3

6) + 2

12 =3 +2 = 4 1+2

Maximum power transfer: example

Find RL for which PL is maximum. 3 2 R1 R3 6 12 V R2 3 R1 2 2A

Voc : R1

2

A

R3 6

RL 12 V

B

R2

2A

B

RTh :

R3 6 R2

B

Use superposition to nd Voc : 3 2

A

3 R1 R2

B

2

A

R1 12 V R2

R3 6

R3 6 2A

B

RTh = (R1

R2 ) + R3 = (3

6) + 2

12 =3 +2 = 4 1+2

6 (1) Voc = 12 = 8 V 9

Maximum power transfer: example

Find RL for which PL is maximum. 3 2 R1 R3 6 12 V R2 3 R1 2 2A

Voc : R1

2

A

R3 6

RL 12 V

B

R2

2A

B

RTh :

R3 6 R2

B

Use superposition to nd Voc : 3 2

A

3 R1 R2

B

2

A

R1 12 V R2

R3 6

R3 6 2A

B

RTh = (R1

R2 ) + R3 = (3

6) + 2

12 =3 +2 = 4 1+2

6 (1) Voc = 12 = 8 V 9

(2) Voc = 4 2 A = 8 V

Maximum power transfer: example

Find RL for which PL is maximum. 3 2 R1 R3 6 12 V R2 3 R1 2 2A

Voc : R1

2

A

R3 6

RL 12 V

B

R2

2A

B

RTh :

R3 6 R2

B

Use superposition to nd Voc : 3 2

A

3 R1 R2

B

2

A

R1 12 V R2

R3 6

R3 6 2A

B

RTh = (R1

R2 ) + R3 = (3

6) + 2

12 =3 +2 = 4 1+2

6 (1) (2) Voc = 12 = 8 V Voc = 4 2 A = 8 V 9 (1) (2) Voc = Voc + Voc = 8 + 8 = 16 V

Maximum power transfer: example

Find RL for which PL is maximum. 3 2 R1 R3 6 12 V R2 3 R1 2 2A

Voc : R1

2

A

R3 6

RL 12 V

B

R2

2A

B

RTh :

R3 6 R2

B

Use superposition to nd Voc : 3 2

A

3 R1 R2

B

2

A

R1 12 V R2

R3 6

R3 6 2A

B

RTh = (R1

R2 ) + R3 = (3

6) + 2

12 =3 +2 = 4 1+2 RTh

A

6 (1) (2) Voc = 12 = 8 V Voc = 4 2 A = 8 V 9 (1) (2) Voc = Voc + Voc = 8 + 8 = 16 V

iL VTh RL

PL is maximum when RL = RTh = 4 iL = VTh /(2 RTh ) = 2 A 2 Pmax L = 2 4 = 16 W .

M. B. Patil, IIT Bombay

Thevenins theorem: example

4 6A 2

4 48 V

12

12

Thevenins theorem: example

4 6A 2 RTh : 4

4 48 V

12

12

12

12

Thevenins theorem: example

4 6A 2 RTh : 4

4 48 V

12

12

2

A B

12

12

4

C

Thevenins theorem: example

4 6A 2 RTh : 4

4 48 V

12

12

2

A B

12

12

4

C

RTh = 7

Thevenins theorem: example

4 6A 2 RTh : 4

4 48 V

Voc :

4 12

4 48 V 12

Voc

12

12 2 6A

C i

2

A B

12

12

4

C

RTh = 7

Thevenins theorem: example

4 6A 2 RTh : 4

4 48 V

Voc :

4 12

4 48 V 12

Voc

12

12 2 6A

C i

Note: i = 0 (since there is no return path). VAB = VA VB = (VA VC ) + (VC VB ) = VAC + VCB = 24 V + 36 V = 60 V

2

A B

12

12

4

C

RTh = 7

Thevenins theorem: example

4 6A 2 RTh : 4

4 48 V

Voc :

4 12

4 48 V 12

Voc

12

12 2 6A

C i

Note: i = 0 (since there is no return path). VAB = VA VB = (VA VC ) + (VC VB ) = VAC + VCB = 24 V + 36 V = 60 V

2

A B

12

12

4

C

RTh = 7

VTh = 60 V RTh = 7

Thevenins theorem: example

4 6A 2 RTh : 4

4 48 V

Voc :

4 12

4 48 V 12

Voc

12

12 2 6A

C i

Note: i = 0 (since there is no return path). VAB = VA VB = (VA VC ) + (VC VB ) = VAC + VCB = 24 V + 36 V = 60 V

A B

2

A B

12

12

4

C

RTh = 7

VTh = 60 V RTh = 7

7 60 V

M. B. Patil, IIT Bombay

Graphical method for nding VTh and RTh

SEQUEL le: ee101 thevenin 1.sqproj

4 6A 2

4 48 V

12

12

Graphical method for nding VTh and RTh

SEQUEL le: ee101 thevenin 1.sqproj

4 6A 2

4 48 V

12

12

Connect a voltage source between A and B. Plot i versus v. 4 6A 2

i v A B

4 48 V 12

12

Voc = intercept on the v-axis. Isc = intercept on the i-axis.

Graphical method for nding VTh and RTh

SEQUEL le: ee101 thevenin 1.sqproj

4 6A 2

4 48 V

i (Amp)

10 8 6 4 2

12

12

Connect a voltage source between A and B. Plot i versus v. 4 6A 2

i v A B

0 0 20 40 v (Volt) 60

4 48 V 12

12

Voc = intercept on the v-axis. Isc = intercept on the i-axis.

Graphical method for nding VTh and RTh

SEQUEL le: ee101 thevenin 1.sqproj

4 6A 2

4 48 V

i (Amp)

10 8 6 4 2

12

12

Connect a voltage source between A and B. Plot i versus v. 4 6A 2

i v A B

0 0 20 40 v (Volt) 60

4 48 V 12

Voc = 60 V, Isc = 8.5714 A RTh = Vsc /Isc = 7

12

Voc = intercept on the v-axis. Isc = intercept on the i-axis.

Graphical method for nding VTh and RTh

SEQUEL le: ee101 thevenin 1.sqproj

4 6A 2

4 48 V

i (Amp)

10 8 6 4 2

12

12

Connect a voltage source between A and B. Plot i versus v. 4 6A 2

i v A B

0 0 20 40 v (Volt) 60

4 48 V 12

Voc = 60 V, Isc = 8.5714 A RTh = Vsc /Isc = 7

A B

12

Voc = intercept on the v-axis. Isc = intercept on the i-axis.

VTh = 60 V RTh = 7

7 60 V

M. B. Patil, IIT Bombay

Norton equivalent circuit

RTh

A

VTh

B

Norton equivalent circuit

RTh

A A

VTh

B

IN

RN

B

Norton equivalent circuit

RTh

A A

VTh

B

IN

RN

B

* Consider the open circuit case.

Norton equivalent circuit

RTh

A A

VTh

B

IN

RN

B

* Consider the open circuit case. Thevenin circuit: VAB = VTh .

Norton equivalent circuit

RTh

A A

VTh

B

IN

RN

B

* Consider the open circuit case. Thevenin circuit: VAB = VTh . Norton circuit: VAB = IN RN .

Norton equivalent circuit

RTh

A A

VTh

B

IN

RN

B

* Consider the open circuit case. Thevenin circuit: VAB = VTh . Norton circuit: VAB = IN RN . VTh = IN RN .

Norton equivalent circuit

RTh

A A

RTh

A A

RN VTh

B

IN

RN

B

VTh

Isc IN

B

Isc

B

* Consider the open circuit case. Thevenin circuit: VAB = VTh . Norton circuit: VAB = IN RN . VTh = IN RN . * Consider the short circuit case.

Norton equivalent circuit

RTh

A A

RTh

A A

RN VTh

B

IN

RN

B

VTh

Isc IN

B

Isc

B

* Consider the open circuit case. Thevenin circuit: VAB = VTh . Norton circuit: VAB = IN RN . VTh = IN RN . * Consider the short circuit case. Thevenin circuit: Isc = VTh /RTh .

Norton equivalent circuit

RTh

A A

RTh

A A

RN VTh

B

IN

RN

B

VTh

Isc IN

B

Isc

B

* Consider the open circuit case. Thevenin circuit: VAB = VTh . Norton circuit: VAB = IN RN . VTh = IN RN . * Consider the short circuit case. Thevenin circuit: Isc = VTh /RTh . Norton circuit: Isc = IN .

Norton equivalent circuit

RTh

A A

RTh

A A

RN VTh

B

IN

RN

B

VTh

Isc IN

B

Isc

B

* Consider the open circuit case. Thevenin circuit: VAB = VTh . Norton circuit: VAB = IN RN . VTh = IN RN . * Consider the short circuit case. Thevenin circuit: Isc = VTh /RTh . Norton circuit: Isc = IN . RTh = RN .

M. B. Patil, IIT Bombay

Example

5 20 V

1A

10

Example

5 20 V

B

1A

10

Example

5 20 V

B

1A

RN = 5 IN = 20 V = 4A 5

10

Example

5 20 V

B A

1A

RN = 5 IN = 20 V = 4A 5

10

4A 5

B

1A

10

Example

5 20 V

B A

1A

RN = 5 IN = 20 V = 4A 5

3A 5

10

10

4A 5

B

1A

10

Example

5 20 V

B A

1A

RN = 5 IN = 20 V = 4A 5

3A 5

10

10

4A 5

B

1A

i = 3A = 1A

5 5 + 10

10

M. B. Patil, IIT Bombay

Example

5 20 V

B A

1A

RN = 5 IN = 20 V = 4A 5

3A 5

10

10

4A 5

B

1A

i = 3A = 1A

5 5 + 10

10

Home work: * Find i by superposition and compare.

M. B. Patil, IIT Bombay

Example

5 20 V

B A

1A

RN = 5 IN = 20 V = 4A 5

3A 5

10

10

4A 5

B

1A

i = 3A = 1A

5 5 + 10

10

Home work: * Find i by superposition and compare. * Compute the power absorbed by each element and verify that P Pi = 0 .

M. B. Patil, IIT Bombay

You might also like

- Ee101 DGTL 1Document152 pagesEe101 DGTL 1PECMURUGANNo ratings yet

- Ee101 BJT 1Document95 pagesEe101 BJT 1Shubham MittalNo ratings yet

- Basic Building Blocks for Amplifier Design: Transistors as Active ElementsDocument47 pagesBasic Building Blocks for Amplifier Design: Transistors as Active ElementsSourya DewanNo ratings yet

- Updated DEVICE EXP - 6 LAB Manual - StudentDocument4 pagesUpdated DEVICE EXP - 6 LAB Manual - StudentAnonymous Uy4UyU31BNo ratings yet

- Ee101 Dac 1Document159 pagesEe101 Dac 1Piyush KabraNo ratings yet

- Ee101 Diodes 1Document112 pagesEe101 Diodes 1anon_617914067No ratings yet

- BJT Small Signal AnalysisDocument15 pagesBJT Small Signal AnalysisAkash KumarNo ratings yet

- 7b. DIRECT CURRENTDocument6 pages7b. DIRECT CURRENTLitiaMikoNo ratings yet

- Experiment No. 6 Op-Amp As Comparator & Schmitt Trigger: Analog Circuits LAB ManualDocument14 pagesExperiment No. 6 Op-Amp As Comparator & Schmitt Trigger: Analog Circuits LAB ManualchaitanyaNo ratings yet

- IGBT in SeriesDocument8 pagesIGBT in SeriesvasiliyNo ratings yet

- A Low Voltage High Performance OTA in 0.18 Micron With High LinearityDocument10 pagesA Low Voltage High Performance OTA in 0.18 Micron With High LinearitymohsenparsauniNo ratings yet

- Circuit simulation techniquesDocument164 pagesCircuit simulation techniquesDarwinNo ratings yet

- Ee8552 Power Electronics MCQDocument21 pagesEe8552 Power Electronics MCQSandesh DalviNo ratings yet

- Ee101 Diodes 1Document112 pagesEe101 Diodes 1sanjayb1976No ratings yet

- ED Lab Experiment Manual 6 2Document9 pagesED Lab Experiment Manual 6 2Jahid Al IslamNo ratings yet

- Phy Inv Project - Common Base TransistorDocument9 pagesPhy Inv Project - Common Base TransistorShaan NayeemNo ratings yet

- PHY212: Physics Lab IV: Study of P-N JunctionDocument16 pagesPHY212: Physics Lab IV: Study of P-N JunctionRajdeep DeyNo ratings yet

- Research Procedure For Buck-Boost Converter For Small Electric VehiclesDocument7 pagesResearch Procedure For Buck-Boost Converter For Small Electric Vehiclesali ghalibNo ratings yet

- Bfo Motor PDFDocument9 pagesBfo Motor PDFNaima RahouaNo ratings yet

- Redresseurs monophasés et triphasésDocument35 pagesRedresseurs monophasés et triphasésRajhiHoussem100% (2)

- BJT Ac AnalysisDocument9 pagesBJT Ac Analysisksay1504No ratings yet

- Physics MarathonDocument130 pagesPhysics MarathonSantosh TiwariNo ratings yet

- By Anshuman Shukla October 27th, 2007Document27 pagesBy Anshuman Shukla October 27th, 2007ShikhaNeeraj AggarwalNo ratings yet

- Chapter 4Document34 pagesChapter 4Yanendra SahNo ratings yet

- Parallel Circuit PDFDocument32 pagesParallel Circuit PDFSarsalejo MarsthinieNo ratings yet

- Band GapDocument16 pagesBand GapmchernitskyNo ratings yet

- Ckts 1 Module 3 FinalsDocument27 pagesCkts 1 Module 3 FinalsAdrian Prince LopezNo ratings yet

- BJT SummaryDocument34 pagesBJT SummarybekirNo ratings yet

- BJTDocument23 pagesBJTEd JudgeNo ratings yet

- Circuit Analysis: 5.1 Kirchoff'S RulesDocument8 pagesCircuit Analysis: 5.1 Kirchoff'S RulesLuqman HakimNo ratings yet

- BJT Fundamentals Experiment ResultsDocument4 pagesBJT Fundamentals Experiment ResultsRhamde PillogoNo ratings yet

- Star DeltaDocument7 pagesStar DeltagopikrishnaraoNo ratings yet

- Academic Excellence in Electronics & Communication EngineeringDocument2 pagesAcademic Excellence in Electronics & Communication Engineeringpatilvk2003No ratings yet

- Basic Electrical DiscussionDocument157 pagesBasic Electrical Discussionseul jichuNo ratings yet

- Experiment No 01Document4 pagesExperiment No 01محمد جان100% (2)

- Multidisciplinary Research: EPRA International Journal ofDocument7 pagesMultidisciplinary Research: EPRA International Journal ofAnand Parakkat ParambilNo ratings yet

- CAPE U2 LAB#2 Azariah BarrettDocument6 pagesCAPE U2 LAB#2 Azariah BarrettazaribarrNo ratings yet

- Ece255lecture 12 Feb22 BJT Small SignalsDocument15 pagesEce255lecture 12 Feb22 BJT Small Signalsblackpantherr2101No ratings yet

- Electrical TechnologyDocument55 pagesElectrical TechnologyRajeev Ranjan Pushp50% (2)

- Kirchoff's LawsDocument24 pagesKirchoff's LawsCarl Ian SamonteNo ratings yet

- Band GapDocument15 pagesBand GapMoin PashaNo ratings yet

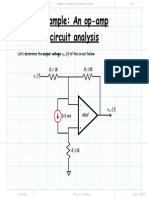

- Example An Op Amp Circuit Analysis LectureDocument23 pagesExample An Op Amp Circuit Analysis LectureAthiyo MartinNo ratings yet

- Power Electronics محاضراتDocument159 pagesPower Electronics محاضراتHasan Al-asadiNo ratings yet

- TransistorDocument22 pagesTransistorShahzali SariNo ratings yet

- EE 306 ManualDocument55 pagesEE 306 Manualzain khuramNo ratings yet

- Electric Current in ConductorsDocument31 pagesElectric Current in ConductorsthinkiitNo ratings yet

- Powerlosscalculationfor IGBTand MOSFETDocument6 pagesPowerlosscalculationfor IGBTand MOSFETDr. Jagabar Sathik Mohammed AliNo ratings yet

- Direct Current Circuit: What Should You Know!!!!Document7 pagesDirect Current Circuit: What Should You Know!!!!angelNo ratings yet

- 8.JEE Main 2019 Jan 12 Afternoon Session Answer Key SolutionDocument26 pages8.JEE Main 2019 Jan 12 Afternoon Session Answer Key Solutiongp1in007No ratings yet

- Resistive-NetworksOLDocument22 pagesResistive-NetworksOLEugenio Tabilog IIINo ratings yet

- Pw3 - Ac RL Parallel Circuit - v1Document6 pagesPw3 - Ac RL Parallel Circuit - v1Hairul Anuar Masrol100% (1)

- 6 - Chapter 5Document13 pages6 - Chapter 5AhmedNo ratings yet

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- Solution Manual for an Introduction to Equilibrium ThermodynamicsFrom EverandSolution Manual for an Introduction to Equilibrium ThermodynamicsNo ratings yet

- Modern Electrical Installation for Craft StudentsFrom EverandModern Electrical Installation for Craft StudentsRating: 4.5 out of 5 stars4.5/5 (4)

- VLF Radio Engineering: International Series of Monographs in Electromagnetic WavesFrom EverandVLF Radio Engineering: International Series of Monographs in Electromagnetic WavesNo ratings yet

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1From EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1No ratings yet

- Hide&SeekDocument6 pagesHide&SeekShreeroop AjaykumarNo ratings yet

- AlgebraDocument2 pagesAlgebraGagandeep RatheeNo ratings yet

- EceDocument3 pagesEceShreeroop AjaykumarNo ratings yet

- Ee101 DGTL 5Document150 pagesEe101 DGTL 5Shreeroop AjaykumarNo ratings yet

- DSP Ec '11Document3 pagesDSP Ec '11Shreeroop AjaykumarNo ratings yet