Professional Documents

Culture Documents

Dataflow Modeling: Implement A Dual 4:1 Multiplexer (IC74F153) Using Data Flow Modeling

Dataflow Modeling: Implement A Dual 4:1 Multiplexer (IC74F153) Using Data Flow Modeling

Uploaded by

Shreyash SillOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dataflow Modeling: Implement A Dual 4:1 Multiplexer (IC74F153) Using Data Flow Modeling

Dataflow Modeling: Implement A Dual 4:1 Multiplexer (IC74F153) Using Data Flow Modeling

Uploaded by

Shreyash SillCopyright:

Available Formats

DATAFLOW MODELING

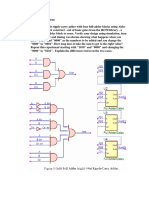

Task 1: Implement a Dual 4:1 Multiplexer (IC74F153)using data flow modeling

Implement an 8:1 multiplexer using 74F153

Task 2: Implement a single bit Full carry adder using data flow modeling in zero delay Model Add delay of 10 for the sum and 7 for carry bit in the full one bit adder and observe the results Implement a 4-bit full carry adder using the above single bit full carry adder in zero delay model Implement a 4-bit full carry adder using the above single bit full carry adder as per the delays mentioned in the step 2 in task 2 and observe the maximum delay that can occur by applying the worst case inputs. Hint : In these cases, Testbench will help better than forcing one input at a time.

Task 3: Implement 4 Bit adder subtractor using the zero delay 1-bit full adder modules designed in task 2.

You might also like

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- Rabadon - Exercise3 FullAdderDocument13 pagesRabadon - Exercise3 FullAdderChristian RabadonNo ratings yet

- Ecen 248 Lab 8 ReportDocument7 pagesEcen 248 Lab 8 Reportapi-241454978No ratings yet

- Ecen 248 Lab 7 ReportDocument7 pagesEcen 248 Lab 7 Reportapi-241454978No ratings yet

- DLD Lab Report 07Document11 pagesDLD Lab Report 07Muneeb ahmadNo ratings yet

- Experiment 2: Counter: Overview of The ExperimentDocument3 pagesExperiment 2: Counter: Overview of The ExperimentTanuj KumarNo ratings yet

- Lab 1 Spring 13Document3 pagesLab 1 Spring 13Kumaraguru RauNo ratings yet

- Department of Biomedical Engineering CSE-221L - Digital Logic DesignDocument8 pagesDepartment of Biomedical Engineering CSE-221L - Digital Logic DesignMUHAMMAD ARSLANNo ratings yet

- Vlsi Exp 1 FinalDocument12 pagesVlsi Exp 1 FinalMANASA P (RA2011004010071)No ratings yet

- Comprehensive Verilog Course Lab Manual V 2.0Document18 pagesComprehensive Verilog Course Lab Manual V 2.0Junaid AsadNo ratings yet

- DLD Lab Report 08Document9 pagesDLD Lab Report 08Muneeb ahmadNo ratings yet

- Lab Exercise 3 (Part B) Network Performance: ObjectivesDocument10 pagesLab Exercise 3 (Part B) Network Performance: ObjectivesNhung HPNo ratings yet

- Laboratory Activity 3 VHDL Modeling of Arithmetic Circuits: Digital Systems Design LaboratoryDocument21 pagesLaboratory Activity 3 VHDL Modeling of Arithmetic Circuits: Digital Systems Design LaboratoryFrancis CadienteNo ratings yet

- Exp 2Document6 pagesExp 2jatinshaarmaaNo ratings yet

- EE 2174 Lab 9 NewDocument6 pagesEE 2174 Lab 9 NewnotdrphilNo ratings yet

- Design and Implementation of A Fast Unsigned 32-Bit Multiplier Using VHDLDocument4 pagesDesign and Implementation of A Fast Unsigned 32-Bit Multiplier Using VHDLAniruddh JainNo ratings yet

- MAC Unit Using Carry Lookahead Adder and Wallace Tree MultiplierDocument11 pagesMAC Unit Using Carry Lookahead Adder and Wallace Tree MultiplierAnandNo ratings yet

- Implementation of Carry Select Adder Using Verilog On FPGA: Sapan Desai (17BEC023) & Devansh Chawla (17BEC024)Document9 pagesImplementation of Carry Select Adder Using Verilog On FPGA: Sapan Desai (17BEC023) & Devansh Chawla (17BEC024)Sapan DesaiNo ratings yet

- DIGLAB2 - Design of Hold Registers and MultiplexersDocument12 pagesDIGLAB2 - Design of Hold Registers and MultiplexersMarlon BoucaudNo ratings yet

- Lab4 CombMultDocument12 pagesLab4 CombMultMayank AgarwalNo ratings yet

- MIPSIt 1Document4 pagesMIPSIt 1Nirneya GuptaNo ratings yet

- VLSI Lab - LIST OF EXPERIMENTSDocument5 pagesVLSI Lab - LIST OF EXPERIMENTSp muraNo ratings yet

- Transmission Control ProtocolDocument11 pagesTransmission Control ProtocolabdulimpNo ratings yet

- Ripple Carry and Carry Lookahead Adders: 1 ObjectivesDocument7 pagesRipple Carry and Carry Lookahead Adders: 1 ObjectivesMercely Christy PriyaNo ratings yet

- CO Expt No. 4Document6 pagesCO Expt No. 4amol maliNo ratings yet

- Computer Organization and Architecture Cs2253: Part-ADocument21 pagesComputer Organization and Architecture Cs2253: Part-AjanukarthiNo ratings yet

- Real Time Systems Lab: Handling Shared ResourcesDocument14 pagesReal Time Systems Lab: Handling Shared ResourcesJ robertsNo ratings yet

- EN TP1 DocDocument3 pagesEN TP1 DocSmail SmartNo ratings yet

- Ece4750 Lab1 ImulDocument7 pagesEce4750 Lab1 ImulThuy NguyenNo ratings yet

- Simulation and Timing Analysis in Cadence Using Verilog XL and Build GatesDocument20 pagesSimulation and Timing Analysis in Cadence Using Verilog XL and Build Gatesrakeshreddy23No ratings yet

- hw6 Solutions PDFDocument13 pageshw6 Solutions PDFJohn Jeshurun SamonteNo ratings yet

- Ripple Carry and Carry Lookahead Adders: 1 ObjectivesDocument8 pagesRipple Carry and Carry Lookahead Adders: 1 ObjectivesYasser RaoufNo ratings yet

- Digital Circuits and Systems LabDocument15 pagesDigital Circuits and Systems LabRonit jainNo ratings yet

- A 8bit Sequential MultiplierDocument6 pagesA 8bit Sequential MultiplierJyoti TeliNo ratings yet

- Experiment 0 ReportDocument3 pagesExperiment 0 ReportTanuj KumarNo ratings yet

- 4 Bit Multiplier Using StructuralDocument7 pages4 Bit Multiplier Using Structuralvinayaka11No ratings yet

- Exercises Chap 2Document4 pagesExercises Chap 2Thought CatalogueNo ratings yet

- Chapter 4 Revisado FinalDocument10 pagesChapter 4 Revisado FinalariovaldojrNo ratings yet

- An 8 Bit Multiplier Project ReportDocument8 pagesAn 8 Bit Multiplier Project ReportAsad Malik0% (1)

- Lab 3 Manual (At Zachry)Document6 pagesLab 3 Manual (At Zachry)jamesNo ratings yet

- Socket Programming ExercisesDocument15 pagesSocket Programming ExercisesJacquesVergesNo ratings yet

- CA PresDocument29 pagesCA PresSadia AwanNo ratings yet

- ECNG 3016 Advanced Digital Electronics: Eneral NformationDocument11 pagesECNG 3016 Advanced Digital Electronics: Eneral NformationMarlon BoucaudNo ratings yet

- Lab 6 - 10 DLDDocument16 pagesLab 6 - 10 DLDSouban JavedNo ratings yet

- Riverbed LAB 1Document6 pagesRiverbed LAB 1Mohamed MazharNo ratings yet

- Vedic Multiplier Part1Document11 pagesVedic Multiplier Part1Chemanthi RojaNo ratings yet

- 491 Part%2B1%2B-%2BTareaDocument3 pages491 Part%2B1%2B-%2BTareaDiana PanchanaNo ratings yet

- Ccnpnuevo 3Document21 pagesCcnpnuevo 3leonel ruizNo ratings yet

- "Digital Technique": Micro Project Work Submitted byDocument9 pages"Digital Technique": Micro Project Work Submitted bysudarshan sonawane50% (2)

- PP 1Document41 pagesPP 1Murtaza AliNo ratings yet

- DicaDocument26 pagesDicaganga_ch1No ratings yet

- Lab 4 Review, Summary & Building Skill Dr. John Abraham Professor, UTPADocument4 pagesLab 4 Review, Summary & Building Skill Dr. John Abraham Professor, UTPAKiệtNo ratings yet

- Carry Save AdderDocument8 pagesCarry Save AdderSwati Malik33% (3)

- GE3171 - Python Lab ManuaLall PrintDocument111 pagesGE3171 - Python Lab ManuaLall PrintKarnan SuganyaNo ratings yet

- Week 3Document10 pagesWeek 3Eufemie AlvaradoNo ratings yet

- Hallo Kubernetes: Container, Orchestration, Management, and MonitoringFrom EverandHallo Kubernetes: Container, Orchestration, Management, and MonitoringNo ratings yet

- Lab 5. FIR Filter Design in MatlabDocument14 pagesLab 5. FIR Filter Design in MatlabShreyash SillNo ratings yet

- Fibonacci-Recursion Kamal Lohia Sir PDFDocument6 pagesFibonacci-Recursion Kamal Lohia Sir PDFShreyash SillNo ratings yet

- Active and Passive Filter Synthesis Using MatlabDocument11 pagesActive and Passive Filter Synthesis Using MatlabShreyash SillNo ratings yet

- Instruction Set & ALPDocument13 pagesInstruction Set & ALPShreyash SillNo ratings yet

- Programmer's Model 8086-80486Document20 pagesProgrammer's Model 8086-80486Shreyash SillNo ratings yet

- Book NameDocument1 pageBook NameShreyash SillNo ratings yet

- Cadence Vlsi Certificate Program (CVCP)Document1 pageCadence Vlsi Certificate Program (CVCP)Shreyash SillNo ratings yet

- Person Tells Different Stories Knight Is Assigned A Mission Different Books-Stories of Their JourneyDocument2 pagesPerson Tells Different Stories Knight Is Assigned A Mission Different Books-Stories of Their JourneyShreyash SillNo ratings yet

- Programmer's Model 8086-80486Document20 pagesProgrammer's Model 8086-80486Shreyash SillNo ratings yet

- Microprocessor & InterfacingDocument18 pagesMicroprocessor & InterfacingShreyash SillNo ratings yet

- Microprocessor & InterfacingDocument20 pagesMicroprocessor & InterfacingShreyash SillNo ratings yet

- Faerie Queene Is Notable For Its Form: It Was The First Work Written in Spenserian StanzaDocument1 pageFaerie Queene Is Notable For Its Form: It Was The First Work Written in Spenserian StanzaShreyash SillNo ratings yet

- Birla Institute of Technology and Science Pilani - K K Birla Goa CampusDocument3 pagesBirla Institute of Technology and Science Pilani - K K Birla Goa CampusShreyash SillNo ratings yet

- Hilbert TransformDocument12 pagesHilbert TransformShreyash SillNo ratings yet

- The Romantic Movement 1Document39 pagesThe Romantic Movement 1Shreyash SillNo ratings yet

- Conclusion:: CharactersDocument4 pagesConclusion:: CharactersShreyash SillNo ratings yet

- Stanza FormsDocument23 pagesStanza FormsShreyash SillNo ratings yet

- Astrophel and StellaDocument1 pageAstrophel and StellaShreyash SillNo ratings yet

- English Literary Forms 2Document29 pagesEnglish Literary Forms 2Shreyash SillNo ratings yet

- Renaissance and ReformationDocument40 pagesRenaissance and ReformationShreyash SillNo ratings yet

- Symbolist Movement and Impact of Sigmund Freud's Psychoanalytic TheoryDocument12 pagesSymbolist Movement and Impact of Sigmund Freud's Psychoanalytic TheoryShreyash SillNo ratings yet

- Modernism (1900-1965) Post Modernism (1965-)Document35 pagesModernism (1900-1965) Post Modernism (1965-)Shreyash SillNo ratings yet