Professional Documents

Culture Documents

Uart Universal Asynchronous Receiver and Transmitter

Uart Universal Asynchronous Receiver and Transmitter

Uploaded by

Gian Carlos Manrique ValentinOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Uart Universal Asynchronous Receiver and Transmitter

Uart Universal Asynchronous Receiver and Transmitter

Uploaded by

Gian Carlos Manrique ValentinCopyright:

Available Formats

Hardware Design with VHDL Design Example: UART

ECE 443

UART Universal Asynchronous Receiver and Transmitter A serial communication protocol that sends parallel data through a serial line. Typically used with RS-232 standard. Your FPGA boards have an RS-232 port with a standard 9-pin connector. The voltages of the FPGA and serial port are different, and therefore a levelconverter circuit is also present on the board. The board handles the RS-232 standard and therefore our focus is on the UART. The UART includes both a transmitter and receiver. The transmitter is a special shift register that loads data in parallel and then shifts it out bit-by-bit. The receiver shifts in data bit-by-bit and reassembles the data byte. The data line is 1 when idle.

ECE UNM

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

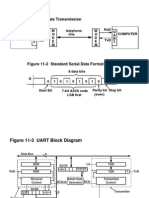

UART Spec Transmission starts when a start bit (a 0) is sent, followed by a number of data bits (either 6, 7 or 8), an optional partity bit and stop bits (with 1, 1.5 or 2 1s). idle start d0 d1 d2 d3 d4 d5 d6 d7 stop

This is the transmission of 8 data bits and 1 stop bit. Note that no clk signal is sent through the serial line. This requires agreement on the transmission parameters by both the transmitter and receiver in advance. This information includes the band rate (number of bits per second), the number of data bits and stop bits, and whether parity is being used. Common baud rates are 2400, 4800, 9600 and 19,200.

ECE UNM

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Receiving Subsystem An oversampling scheme is commonly used to locate the middle position of the transmitted bits, i.e., where the actual sample is taken. The most common oversampling rate is 16 times the baud rate. Therefore, each serial bit is sampled 16 times but only one sample is saved as we will see. The oversampling scheme using N data bits and M stop bits: Wait until the incoming signal becomes 0 (the start bit) and then start the sampling tick cnter. When the cnter reaches 7, the incoming signal reaches the middle position of the start bit. Clear the cnter and restart. When the cnter reaches 15, we are at the middle of the rst data bit. Retrieve it and shift into a register. Restart the cnter. Repeat the above step N-1 times to retrieve the remaining data bits. If optional parity bit is used, repeat this step once more. Repeat this step M more times to obtain the stop bits.

ECE UNM

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

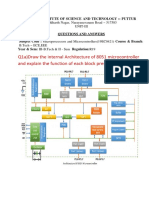

UART Receiving Subsystem The oversampling scheme replaces the function of the clock. Instead of using the rising edge to sample, the sampling ticks are used to estimate the center position of each bit. Note that the system clock must be much faster than the baud rate for oversampling to be possible. The receiver block diagram consists of three components rx clk tick baud rate generator rx s_tick UART receiver interface circuit d_out rx_done_tick d_out r_data rd_uart rx_empty

The interface circuit provides a buffer and status between the UART and the computer or FPGA. ECE UNM 4 (9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Receiving Subsystem The baud rate generator generates a sampling signal whose frequency is exactly 16 times the UARTs designated baud rate. To avoid creating a new clock domain, the output of the baud rate generator will serve to enable ticks within the UART rather than serve as the clk signal. The whole system will use one clk as we will see. For a 19,200 baud rate, the sampling rate has to be 307,200 (19,200*16) ticks per second. With a system clk at 50 MHz, the baud rate generator need a mod-163 cnter (50 MHz/307,200). Therefore, the tick output will assert for one clk cycle every 163 clk cycles of the system clk. The following code from page 83 of the text can be used to implement a mod-163 cnter.

ECE UNM

(9/17/08)

Hardware Design with VHDL Design Example: UART UART Receiving Subsystem: mod-163 cnter library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity mod_m_cnter is generic( N: integer := 4; M: integer := 10; ); port( clk, reset: in std_logic; max_tick: out std_logic; q: out std_logic_vector(N-1 downto 0); ); end mod_m_cnter; architecture arch of mod_m_cnter is signal r_reg: unsigned(N-1 downto 0); signal r_next: unsigned(N-1 downto 0); ECE UNM 6

ECE 443

(9/17/08)

Hardware Design with VHDL Design Example: UART UART Receiving Subsystem: mod-163 cnter begin process(clk, reset) begin if (reset = 1) then r_reg <= (others => 0); elsif (clkevent and clk=1) then r_reg <= r_next; end if; end process; end arch; -- next state logic r_next <= (others => 0) when r_reg=(M-1) else r_reg + 1; -- output logic q <= std_logic_vector(r_reg); max_tick <= 1 when r_reg=(M-1) else 0; end arch; ECE UNM 7

ECE 443

(9/17/08)

Hardware Design with VHDL Design Example: UART UART Receiving Subsystem: UART receiver The ASMD chart for the receiver is shown below:

ECE 443

idle F rx = 0 s <= 0 start F F s_tick=1 s=7 F F F

data s_tick=1 s=15 F F

stop s_tick=1 s=SB_TICK-1

s <= s+1 s <= s+1 s <= 0 b <= rx&(b>>1) n=D_BIT-1 states: idle, start, data, stop s_tick is enable tick from baud generator. rx_done_tick <= 1

s <= s+1 s <= 0 n <= 0

n <= n+1

D_BIT indicates the number of data bits and SB_TICK indicates the number of ticks needed for the stop bits (16, 24 and 32 for 1, 1.5 and 2 stop bits).

ECE UNM

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Receiving Subsystem: UART receiver We will assign D_BIT and SB_TICK to 8 and 16, respectively, in our design. library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity uart_rx is generic( DBIT: integer := 8; SB_TICK: integer := 16; ); port( clk, reset: in std_logic; rx: in std_logic; s_tick: in std_logic; rx_done_tick: out std_logic; dout: out std_logic_vctor(7 downto 0) ); end uart_rx;

ECE UNM

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Receiving Subsystem: UART receiver architecture arch of uart_rx is type state_type is (idle, start, data, stop); signal state_reg, state_next: state_type; signal s_reg, s_next: unsigned(3 downto 0); signal n_reg, n_next: unsigned(2 downto 0); signal b_reg, b_next: std_logic_vector(7 downto 0); begin process(clk, reset) -- FSMD state and data regs. begin if (reset = 1) then state_reg <= idle; s_reg <= (others => 0); n_reg <= (others => 0); b_reg <= (others => 0); elsif (clkevent and clk=1) then state_reg <= state_next; s_reg <= s_next; n_reg <= n_next; ECE UNM 10 (9/17/08)

Hardware Design with VHDL Design Example: UART UART Receiving Subsystem: UART receiver b_reg <= b_next; end if; end process;

ECE 443

-- next state logic process (state_reg, s_reg, n_reg, b_reg, s_tick, rx) begin state_next <= state_reg; s_next <= s_reg; n_next <= n_reg; b_next <= b_reg; rx_done_tick <= 0; case state_reg is when idle => if (rx = 0) then state_next <= start; s_next <= (others => 0); end if; ECE UNM 11 (9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Receiving Subsystem: UART receiver when start => if (s_tick = 1) then if (s_reg = 7) then state_next <= data; s_next <= (others => 0); n_next <= (others => 0); else s_next <= s_reg + 1; end if; end if; when data => if (s_tick = 1) then if (s_reg = 15) then s_next <= (others => 0); b_next <= rx & b_reg(7 downto 1); if (n_reg = (DBIT - 1)) then state_next <= stop; else ECE UNM 12 (9/17/08)

Hardware Design with VHDL Design Example: UART UART Receiving Subsystem: UART receiver n_next <= n_reg + 1; end if; else s_next <= s_reg + 1; end if; end if; when stop => if (s_tick = 1) then if (s_reg = (SB_TICK-1)) then state_next <= idle; rx_done_tick <= 1; else s_next <= s_reg + 1; end if; end if; end case; end process; dout <= b_reg; end arch; ECE UNM 13

ECE 443

(9/17/08)

Hardware Design with VHDL Design Example: UART UART Receiving Subsystem: Interface Circuit The receiver interface circuit has two functions: It provides a mechanism to signal the availability of a new word It provides buffer space between the receiver and main system.

ECE 443

Several architectures are possible, including one with a FIFO. Here is one with a ag FF (to indicate the reception of a data byte) and a one byte buffer. rx clk tick baud rate generator rx s_tick UART receiver d_out rx_done_tick q d_out en register set_ag ag clr_ag register r_data rd_uart

rx_empty

rd_uart

Here, rx_done_tick is connected to set_ag while the system connects to clr_ag. The system checks rx_empty to determine when a data byte is available.

ECE UNM

14

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Receiving Subsystem: Interface Circuit When rx_done_tick is asserted, the received byte is loaded to the buffer and the ag FF is asserted. The receiver can continue to fetch the next byte, giving time for the system to retrieve the current byte. library ieee; use ieee.std_logic_1164.all; entity flag_buff is generic(W: integer := 8); port( clk, reset: in std_logic; clr_flag, set_flag: in std_logic; din: in std_logic_vector(W-1 downto 0); dout: out std_logic_vector(W-1 downto 0); flag: out std_logic ); end flag_buff;

ECE UNM

15

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Receiving Subsystem: Interface Circuit architecture arch of flag_buff is signal buf_reg, buf_next: std_logic_vector(W-1 downto 0); signal flag_reg, flag_next: std_logic; begin process(clk, reset) begin if (reset = 1) then buf_reg <= (others =>0); flag_reg <= 0; elsif (clkevent and clk=1) then buf_reg <= buf_next; flag_reg <= flag_next; end if; end process; -- next-state logic

ECE UNM

16

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Receiving Subsystem: Interface Circuit process (buf_reg, flag_reg, set_flag, clr_flag, din) begin buf_next <= buf_reg; flag_next <= flag_reg; if (set_flag = 1) then buf_next <= din; flag_next <= 1; elsif (clr_flag = 1) then flag_next <= 0; end if; end process; -- output logic dout <= buf_reg; flag <= flag_reg; end arch;

ECE UNM

17

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Transmitting Subsystem The UART transmitting subsystem is similar to the receiving subsystem. It consists of UART transmitter, baud rate generator and interface circuit. Roles are reversed for the interface circuit, i.e., the system sets the ag FF or writes the buffer interface circuit while the UART transmitter clears FF or reads the buffer. The transmitter is essentially a shift register that shifts out data bits. Since no oversampling is involved, the frequency of the ticks are 16 times slower than that of the receiver. However, instead of introducing another cnter, the transmitter usually shares the baud rate generator and uses an internal cnter to cnt through the 16 ticks. library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all;

ECE UNM

18

(9/17/08)

Hardware Design with VHDL Design Example: UART UART Transmitting Subsystem entity uart_tx is generic( DBIT: integer := 8; SB_TICK: integer := 16; ); port( clk, reset: in std_logic; tx_start: in std_logic; s_tick: in std_logic; din: out std_logic_vctor(7 downto 0) tx_done_tick: out std_logic; tx: out std_logic ); end uart_tx;

ECE 443

ECE UNM

19

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Transmitting Subsystem architecture arch of uart_tx is type state_type is (idle, start, data, stop); signal state_reg, state_next: state_type; signal s_reg, s_next: unsigned(3 downto 0); signal n_reg, n_next: unsigned(2 downto 0); signal b_reg, b_next: std_logic_vector(7 downto 0); signal tx_reg, tx_next: std_logic; begin process(clk, reset) -- FSMD state and data regs. begin if (reset = 1) then state_reg <= idle; s_reg <= (others => 0); n_reg <= (others => 0); b_reg <= (others => 0); tx_reg <= 1;

ECE UNM

20

(9/17/08)

Hardware Design with VHDL Design Example: UART UART Transmitting Subsystem elsif (clkevent and clk=1) then state_reg <= state_next; s_reg <= s_next; n_reg <= n_next; b_reg <= b_next; tx_reg <= tx_next; end if; end process;

ECE 443

-- next state logic process (state_reg, s_reg, n_reg, b_reg, s_tick, tx_reg, tx_start, din) begin state_next <= state_reg; s_next <= s_reg; n_next <= n_reg; b_next <= b_reg; tx_next <= tx_reg; ECE UNM 21 (9/17/08)

Hardware Design with VHDL Design Example: UART UART Transmitting Subsystem tx_done_tick <= 0; case state_reg is when idle => tx_next <= 1; if (tx_start = 1) then state_next <= start; s_next <= (others => 0); b_next <= din; end if; when start => tx_next <= 0; if (s_tick = 1) then if (s_reg = 15) then state_next <= data; s_next <= (others => 0); n_next <= (others => 0); else s_next <= s_reg + 1; ECE UNM 22

ECE 443

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

UART Transmitting Subsystem end if; end if; when data => tx_next <= b_reg(0); if (s_tick = 1) then if (s_reg = 15) then s_next <= (others => 0); b_next <= 0 & b_reg(7 downto 1); if (n_reg = (DBIT - 1)) then state_next <= stop; else n_next <= n_reg + 1; end if; else s_next <= s_reg + 1; end if; end if;

ECE UNM

23

(9/17/08)

Hardware Design with VHDL Design Example: UART UART Transmitting Subsystem when stop => tx_next <= 1; if (s_tick = 1) then if (s_reg = (SB_TICK-1)) then state_next <= idle; rx_done_tick <= 1; else s_next <= s_reg + 1; end if; end if; end case; end process; tx <= tx_reg; end arch;

ECE 443

ECE UNM

24

(9/17/08)

Hardware Design with VHDL Design Example: UART Entire UART System Block diagram of whole system rx clk tick baud rate generator rx s_tick UART receiver d_out rx_done_tick w_data r_data wr register set_ag ag clr_ag register d_in tx s_tick tx_done_tick tx_start set_ag ag clr_ag register UART transmitter r_data w_data rd register

ECE 443

r_data rd_uart rx_empty

rd_uart w_data wr_uart tx_full

tx

rd_uart

ECE UNM

25

(9/17/08)

Hardware Design with VHDL Design Example: UART

ECE 443

Entire UART System See text for the UART main module that instantiates the entities discussed above. Note text uses a FIFO buffer so the diagram above is different. The text also includes a loop-back circuit that instantiates the UART and connects the outputs of the receiver with the inputs of the transmitter on the FPGA. It also adds 1 to the incoming data before looping it back to the computer. Windows hyperterminal is discussed as a mechanism to communicate directly to the serial ports on your computer.

ECE UNM

26

(9/17/08)

You might also like

- Introduction To The I/O Buses Technical and Historical Background For The I/O BusesDocument9 pagesIntroduction To The I/O Buses Technical and Historical Background For The I/O BusesshankyguptaNo ratings yet

- Asic Prototyping AldecDocument10 pagesAsic Prototyping AldecKhaled Abou ElseoudNo ratings yet

- Clocks Basics in 10 Minutes or Less: Edgar Pineda Field Applications Engineer Arrow Components MexicoDocument20 pagesClocks Basics in 10 Minutes or Less: Edgar Pineda Field Applications Engineer Arrow Components MexicoshyamsubbuNo ratings yet

- SPI I2C Interface AnDocument13 pagesSPI I2C Interface AnNivin PaulNo ratings yet

- 9FB Gas TurbineDocument2 pages9FB Gas TurbineRene GonzalezNo ratings yet

- VHDL UartDocument53 pagesVHDL UartEhsan Mahdavi100% (1)

- Elektor Electronics USA - January-February 2016Document132 pagesElektor Electronics USA - January-February 2016Adrian_Andrei_4433100% (8)

- UART in VHDL and Verilog For An FPGADocument10 pagesUART in VHDL and Verilog For An FPGATrọngHữuNguyễnNo ratings yet

- Zynq 7000 TRMDocument1,770 pagesZynq 7000 TRMSambhav VermanNo ratings yet

- Module-2, Session-1 HDL Design Concepts and RTL Coding With VHDLDocument7 pagesModule-2, Session-1 HDL Design Concepts and RTL Coding With VHDLPraveen KumarNo ratings yet

- Lec20 RTL DesignDocument40 pagesLec20 RTL DesignVrushali patilNo ratings yet

- VHDL 4 RTL ModelsDocument33 pagesVHDL 4 RTL ModelsNguyễn Minh NghĩaNo ratings yet

- BS 5950-1 1990Document126 pagesBS 5950-1 1990Anoy100% (4)

- Register and Its OperationsDocument56 pagesRegister and Its OperationsSARTHAK VARSHNEYNo ratings yet

- DDR SDR Sdram ComparisionDocument12 pagesDDR SDR Sdram ComparisionSrinivas CherukuNo ratings yet

- DVD2 JNTU Set1 SolutionsDocument12 pagesDVD2 JNTU Set1 Solutionsకిరణ్ కుమార్ పగడాలNo ratings yet

- FSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017Document25 pagesFSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017antoniocljNo ratings yet

- 2.sys Bus ArchDocument14 pages2.sys Bus ArchChar MondeNo ratings yet

- DSD 12 Synchronous DesignDocument9 pagesDSD 12 Synchronous DesignDavis AbrahamNo ratings yet

- Coreapb3: Nivin PaulDocument19 pagesCoreapb3: Nivin PaulNivin PaulNo ratings yet

- Bus System & Data TransferDocument5 pagesBus System & Data Transferlmehta16No ratings yet

- 05 Systemc TutorialDocument32 pages05 Systemc TutorialjasonturfNo ratings yet

- Chapter 7: Register Transfer: ObjectivesDocument7 pagesChapter 7: Register Transfer: ObjectivesSteffany RoqueNo ratings yet

- Chapter 6 - IO (Part 2)Document42 pagesChapter 6 - IO (Part 2)Nurhidayatul FadhilahNo ratings yet

- SOC TestingDocument27 pagesSOC TestingMaria AllenNo ratings yet

- Lecture 5 - Combinatorial and Sequential LogicDocument76 pagesLecture 5 - Combinatorial and Sequential LogicantoniocljNo ratings yet

- Organization: Basic Computer Organization and DesignDocument29 pagesOrganization: Basic Computer Organization and DesignGemechisNo ratings yet

- 5 - Internal MemoryDocument22 pages5 - Internal Memoryerdvk100% (1)

- BGK MPMC Unit-3 Q and ADocument21 pagesBGK MPMC Unit-3 Q and AMallesh ArjaNo ratings yet

- Commands Used in Soc Workshop PDFDocument16 pagesCommands Used in Soc Workshop PDFabhishek bhandareNo ratings yet

- Arduino-Based Embedded System ModuleDocument8 pagesArduino-Based Embedded System ModuleIJRASETPublicationsNo ratings yet

- Testability in EOCHL (And Beyond ) : Vladimir ZivkovicDocument24 pagesTestability in EOCHL (And Beyond ) : Vladimir ZivkovicsenthilkumarNo ratings yet

- ASIC TimingDocument54 pagesASIC TimingKrishna MohanNo ratings yet

- Unit - IV: Input - OutputDocument50 pagesUnit - IV: Input - Outputkarvind08No ratings yet

- Atrenta Tutorial PDFDocument15 pagesAtrenta Tutorial PDFTechy GuysNo ratings yet

- Register Transfer Methodology: PrincipleDocument25 pagesRegister Transfer Methodology: PrincipleKhalidTaherAl-HussainiNo ratings yet

- Vi For Smaties Linux EditorDocument10 pagesVi For Smaties Linux EditorSandeep ChaudharyNo ratings yet

- Buffer InsertionDocument47 pagesBuffer InsertionAkshay DesaiNo ratings yet

- 03b - FIE - Parcial #3 PLD - Resumen 04c 09Document36 pages03b - FIE - Parcial #3 PLD - Resumen 04c 09amilcar93No ratings yet

- Topic 6 - Clocking & Met A StabilityDocument9 pagesTopic 6 - Clocking & Met A Stabilityanish1988100% (1)

- Vi Editor Basic CommandsDocument2 pagesVi Editor Basic CommandsJust FriendNo ratings yet

- EC8661 VLSI Design Laboratory PDFDocument53 pagesEC8661 VLSI Design Laboratory PDFSINDHUNo ratings yet

- Image Cryptography Design Based On Nano AES Security AlgorithmDocument6 pagesImage Cryptography Design Based On Nano AES Security AlgorithmIJRASETPublicationsNo ratings yet

- Low Power VLSI Design: J.Ramesh ECE Department PSG College of TechnologyDocument146 pagesLow Power VLSI Design: J.Ramesh ECE Department PSG College of TechnologyVijay Kumar TNo ratings yet

- Cause and Correlation in Biology - A User's Guide To Path Analysis, Structural Equations and Causal InferenceDocument330 pagesCause and Correlation in Biology - A User's Guide To Path Analysis, Structural Equations and Causal InferenceLycurgue100% (1)

- Project FileDocument131 pagesProject FileshaanjalalNo ratings yet

- UARTDocument34 pagesUARTMohit Dayal67% (3)

- USB To RS-232 ConverterDocument11 pagesUSB To RS-232 Converteryeateshwarrior100% (1)

- Clock Domain ClockingDocument12 pagesClock Domain Clockingarunsrl100% (1)

- VLSI FPGA Projects Topics Using VHDL - Verilog - VLSI EncyclopediaDocument4 pagesVLSI FPGA Projects Topics Using VHDL - Verilog - VLSI EncyclopediaGunapalli venkata saikiranNo ratings yet

- Topic 7 - Clocking Strategies (4up)Document8 pagesTopic 7 - Clocking Strategies (4up)vijjuvardhan100% (1)

- Rs-232 To I2c Protocol ConverterDocument4 pagesRs-232 To I2c Protocol ConverterHarsha100% (2)

- FPGA Implementation of 9 Bit Universal Asynchronous Receiver TransmitterDocument3 pagesFPGA Implementation of 9 Bit Universal Asynchronous Receiver TransmitterMeghanand KumarNo ratings yet

- Bus InterconnectionDocument11 pagesBus InterconnectionGame ZoneNo ratings yet

- UART Communication Protocol - How It Works - Codrey ElectronicsDocument14 pagesUART Communication Protocol - How It Works - Codrey ElectronicsPhogat Ashish100% (1)

- Chapter 8 - CPU PerformanceDocument40 pagesChapter 8 - CPU PerformanceNurhidayatul FadhilahNo ratings yet

- 9-Serial Comm (Autosaved)Document48 pages9-Serial Comm (Autosaved)M ADNAN Z100% (1)

- USART UART RS232 USB SPI I2C TTL Etc What Are All of These and How Do They Relate To Each OtherDocument4 pagesUSART UART RS232 USB SPI I2C TTL Etc What Are All of These and How Do They Relate To Each OtherMohamed Ashraf100% (1)

- Exclusive OR/Exclusive NOR (XOR/XNOR) : XOR/XNOR Truth Table Xor B A Xnor B 0 0 0 1 0 1 1 0 1 0 1 0 1 1 0 1Document30 pagesExclusive OR/Exclusive NOR (XOR/XNOR) : XOR/XNOR Truth Table Xor B A Xnor B 0 0 0 1 0 1 1 0 1 0 1 0 1 1 0 1Mustafa Rashik Hasnain100% (1)

- UartDocument21 pagesUartSusie MaestreNo ratings yet

- FPGA Implementation of Universal Asynchronous Receiver and Transmitter (UART)Document13 pagesFPGA Implementation of Universal Asynchronous Receiver and Transmitter (UART)VaseaPupchinNo ratings yet

- Modular UARTDocument28 pagesModular UARTpreetiNo ratings yet

- Serial Communication in Embedded SystemsDocument30 pagesSerial Communication in Embedded SystemsRishabh RanjanNo ratings yet

- ELEC 418 Advanced Digital Systems Dr. Ron Hayne: Images Courtesy of Thomson EngineeringDocument34 pagesELEC 418 Advanced Digital Systems Dr. Ron Hayne: Images Courtesy of Thomson EngineeringRama KrishnaNo ratings yet

- A Rosenblatt Transformation Method Based On Copula Function For Solving Structural ReliabilityDocument7 pagesA Rosenblatt Transformation Method Based On Copula Function For Solving Structural ReliabilityRAJKUMAR SAHANo ratings yet

- DATASHEETDocument3 pagesDATASHEETPersonal OpxionNo ratings yet

- "Facts Are Not Science - As The Dictionary Is Not Literature." Martin H. FischerDocument16 pages"Facts Are Not Science - As The Dictionary Is Not Literature." Martin H. FischerVivek TripathyNo ratings yet

- Cruise Control Izusu CamionesDocument12 pagesCruise Control Izusu CamionesAnonymous KOtSfT6qNo ratings yet

- File 2Document1 pageFile 23Bsbss Abo SafanNo ratings yet

- Is JIT Manufacturing The Right PrescriptionDocument1 pageIs JIT Manufacturing The Right PrescriptionjoannakamNo ratings yet

- A-Perpetual-Holiday EssayDocument2 pagesA-Perpetual-Holiday EssayAlex OpreanNo ratings yet

- LampiranKeputusan Menteri Keuangan RI Data PIM PDFDocument33 pagesLampiranKeputusan Menteri Keuangan RI Data PIM PDFkhomeinitjNo ratings yet

- Eco-Friendly Water FilterDocument2 pagesEco-Friendly Water FilterRaphael EdogunNo ratings yet

- Draft Ordinance For Bike Lanes in Q.CDocument4 pagesDraft Ordinance For Bike Lanes in Q.CRosé AlcalaNo ratings yet

- Ship ParticularsDocument1 pageShip ParticularsEbony CarterNo ratings yet

- HBXX-3817TB1-VTM - HBXX-3817TB1-A2M: Electrical SpecificationsDocument3 pagesHBXX-3817TB1-VTM - HBXX-3817TB1-A2M: Electrical SpecificationsTối ƯuNo ratings yet

- NFSS 160 Exam 1 Study GuideDocument3 pagesNFSS 160 Exam 1 Study GuideKaitlyn RobisonNo ratings yet

- Fema - 1989 Handbook of Chemical Hazard Analysis ProceduresDocument520 pagesFema - 1989 Handbook of Chemical Hazard Analysis ProceduresMario RodriguezNo ratings yet

- The Coca-Cola CompanyDocument21 pagesThe Coca-Cola CompanyNadeem KhanNo ratings yet

- Gabbett 2019 TheBig3Elements JOSPT InPressDocument9 pagesGabbett 2019 TheBig3Elements JOSPT InPressPrem AnandNo ratings yet

- Sodium Alginate: The Wonder Polymer For Controlled Drug DeliveryDocument10 pagesSodium Alginate: The Wonder Polymer For Controlled Drug DeliveryAinii BasriNo ratings yet

- Last Heroes 2 WalkthroughDocument9 pagesLast Heroes 2 WalkthroughSezo TariantoNo ratings yet

- CZ 85 en Es Cs de FR 06 2009Document68 pagesCZ 85 en Es Cs de FR 06 2009Chris HaerringerNo ratings yet

- Mechanical ProjectDocument7 pagesMechanical ProjectAbi Nesan100% (1)

- Wa0052.Document59 pagesWa0052.hofonad662No ratings yet

- Installing of Solar Panel For Rural CommunityDocument11 pagesInstalling of Solar Panel For Rural Communityvenkata rao dNo ratings yet

- Chapter 9 - Biodiversity N GMODocument39 pagesChapter 9 - Biodiversity N GMORhealyn RobledoNo ratings yet

- V-Gel Cleaning & User GuideDocument3 pagesV-Gel Cleaning & User GuideInstrulife OostkampNo ratings yet

- Principles For Layout Plans and Sectioning Diagrams For 25 KV Ac TractionDocument4 pagesPrinciples For Layout Plans and Sectioning Diagrams For 25 KV Ac TractionPragati SrivastavaNo ratings yet