Professional Documents

Culture Documents

Memory Consistyency

Uploaded by

bsgindia82Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Memory Consistyency

Uploaded by

bsgindia82Copyright:

Available Formats

(ii)MEMORY CONSISTENCY:

a. sequential consistency b. relaxed consistency

(a)SEQUENTIAL CONSISTENCY:

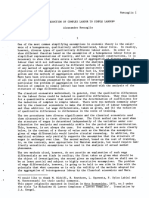

At any given instant in time in a sequential program, memory has a well defined state. This is called sequential consistency. In parallel programs, it all depends upon the viewpoint. Two writes to memory by a hardware thread may be seen in a different order by another thread. The reason is that when a hardware thread writes to memory, the written data goes through a path of buffers and caches before reaching main memory. Along this path, a later write may reach main memory sooner than an earlier write. Similar effects apply to reads. If one read requires a fetch from main memory and a later read hits in cache, the processor may allow the faster read to pass the slower read. i!ewise, reads and writes might pass each other

. ( )RELA!E" CONSISTENCY: The processor does not have to guarantee that other processors see those reads and writes in the original order. Systems that allow this reordering are said to exhibit relaxed consistency. "ecause relaxed consistency relates to how hardware threads observe each other#s actions, it is not an issue for programs running time sliced on a single hardware thread. Inattention to consistency issues can result in concurrent programs that run correctly on single$threaded hardware, or even hardware running with %T Technology, but fail when run on multi$threaded hardware with dis&oint caches. The hardware is not the only cause of relaxed consistency. 'ompilers are often free to reorder instructions. The reordering is critical to most ma&or compiler optimi(ations. )or instance, compilers typically hoist loop$invariant reads out of a loop, so that the read is done once per loop instead of once per loop iteration. anguage rules typically grant the compiler license to presume the code is single$threaded, even if it is not.

You might also like

- CS326 Parallel and Distributed Computing: SPRING 2021 National University of Computer and Emerging SciencesDocument33 pagesCS326 Parallel and Distributed Computing: SPRING 2021 National University of Computer and Emerging SciencesNehaNo ratings yet

- Operating System NotesDocument1 pageOperating System Notes2K19/EC/005 AASTIKNo ratings yet

- Implement Write-Invalidate Protocol To Demonstrate The Memory CoherencyDocument10 pagesImplement Write-Invalidate Protocol To Demonstrate The Memory CoherencyNAGARJUNANo ratings yet

- Unit - 4 Computing Technologies: To - Bca 4 Sem BY-Vijayalaxmi ChiniwarDocument34 pagesUnit - 4 Computing Technologies: To - Bca 4 Sem BY-Vijayalaxmi ChiniwarVidya BudihalNo ratings yet

- Different Parallel Processing ArchitectureDocument41 pagesDifferent Parallel Processing Architecturesanzog raiNo ratings yet

- ThreadsDocument48 pagesThreadssurveyacc2023No ratings yet

- Memory Hierarchy: Haresh Dagale Dept of ESEDocument32 pagesMemory Hierarchy: Haresh Dagale Dept of ESEmailstonaikNo ratings yet

- Lec13 MultiprocessorsDocument69 pagesLec13 MultiprocessorsdoomachaleyNo ratings yet

- Unit 5 Memory SystemDocument77 pagesUnit 5 Memory SystemsubithavNo ratings yet

- Qn:Explain Different Latency Hiding Techniques /mechanisms? (Ans:Describe Sections 6.1.2,6.1.3, 6.1.5, 6.2.2.)Document28 pagesQn:Explain Different Latency Hiding Techniques /mechanisms? (Ans:Describe Sections 6.1.2,6.1.3, 6.1.5, 6.2.2.)ripcord jakeNo ratings yet

- William Stallings Computer Organization and Architecture 8th Edition Cache MemoryDocument43 pagesWilliam Stallings Computer Organization and Architecture 8th Edition Cache MemoryabbasNo ratings yet

- ACA Unit 4Document41 pagesACA Unit 4sushil@irdNo ratings yet

- Unit4 CaosDocument8 pagesUnit4 CaosTruptimayee MishraNo ratings yet

- CA-unit 5-Material-For ReferenceDocument16 pagesCA-unit 5-Material-For Reference22iz014No ratings yet

- Chapter 3 ProcessesDocument42 pagesChapter 3 ProcessesLusi ሉሲNo ratings yet

- Chapter 6Document24 pagesChapter 6angawNo ratings yet

- Term Paper: Cahe Coherence SchemesDocument12 pagesTerm Paper: Cahe Coherence SchemesVinay GargNo ratings yet

- Distributed Shared Memory For Advanced OsDocument21 pagesDistributed Shared Memory For Advanced OsmjspinoNo ratings yet

- Design Patterns Concurrency PatternDocument11 pagesDesign Patterns Concurrency Patternhaider aliNo ratings yet

- Chapter 4Document15 pagesChapter 4MehreenAkramNo ratings yet

- Shared Memory MultiprocessorsDocument45 pagesShared Memory MultiprocessorsSushma Rani VatekarNo ratings yet

- Cache CoherenceDocument3 pagesCache CoherenceAmit SinghNo ratings yet

- Mu Os Fall 2020 ch01 IntroductionDocument54 pagesMu Os Fall 2020 ch01 IntroductionAbdallateef ShohdyNo ratings yet

- Threads in OSDocument32 pagesThreads in OSIzzan DienurrahmanNo ratings yet

- CS347 04 Process SyncDocument14 pagesCS347 04 Process SyncahilanNo ratings yet

- 03 - Lecture #3Document32 pages03 - Lecture #3Fatma mansourNo ratings yet

- Operating System Lect12Document34 pagesOperating System Lect12gogochor5No ratings yet

- Chapter 1 Part 2Document33 pagesChapter 1 Part 2Mat Dunlop Bin Senapang GajahNo ratings yet

- CP4253 Map Unit IiDocument23 pagesCP4253 Map Unit IiNivi VNo ratings yet

- Unit 5 (Slides)Document75 pagesUnit 5 (Slides)Keerthana g.krishnanNo ratings yet

- OS Unit - 4 NotesDocument35 pagesOS Unit - 4 NoteshahahaNo ratings yet

- 05 ThreadsDocument37 pages05 Threadsomnia amirNo ratings yet

- Background Naming and Transparency Remote File Access Stateful Versus Stateless Service File Replication Example SystemsDocument24 pagesBackground Naming and Transparency Remote File Access Stateful Versus Stateless Service File Replication Example SystemsFarooq ShadNo ratings yet

- Aca Unit5Document13 pagesAca Unit5karunakarNo ratings yet

- 0014 SharedMemoryArchitectureDocument31 pages0014 SharedMemoryArchitectureAsif KhanNo ratings yet

- 2.2 DD2356 ThreadsDocument22 pages2.2 DD2356 ThreadsDaniel AraújoNo ratings yet

- Shared Memory Multiprocessors: Logical Design and Software InteractionsDocument107 pagesShared Memory Multiprocessors: Logical Design and Software Interactionsfariha2002No ratings yet

- OS Unit - IIDocument74 pagesOS Unit - IIDee ShanNo ratings yet

- Multicore ComputersDocument18 pagesMulticore ComputersMikias YimerNo ratings yet

- Chapter 2Document30 pagesChapter 2eyob abelNo ratings yet

- Memory ManagementDocument75 pagesMemory ManagementJong KookNo ratings yet

- Notes On Memory Consistency and Cache Coherence: Rege+RegfDocument9 pagesNotes On Memory Consistency and Cache Coherence: Rege+RegfYong LiNo ratings yet

- Distributed SystemsDocument238 pagesDistributed SystemsOTMANE ER-RAGRAGUINo ratings yet

- Operating Systems: Chapter 3: Memory ManagementDocument51 pagesOperating Systems: Chapter 3: Memory ManagementMultiple Criteria DssNo ratings yet

- Multithreading in PythonDocument23 pagesMultithreading in Pythondigi oceanNo ratings yet

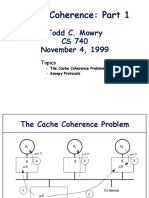

- Cache Coherence: Part 1: Todd C. Mowry CS 740 November 4, 1999Document39 pagesCache Coherence: Part 1: Todd C. Mowry CS 740 November 4, 1999AthreyaNo ratings yet

- Distributed Shared Memory: Jonathan WalpoleDocument14 pagesDistributed Shared Memory: Jonathan WalpoleArindam SarkarNo ratings yet

- A Survey of Cache Coherence Mechanisms in Shared MDocument27 pagesA Survey of Cache Coherence Mechanisms in Shared Msahasubhajit32102No ratings yet

- OS 1 For Students-1Document31 pagesOS 1 For Students-1Sadia NasirNo ratings yet

- Different Levels of The Memory HierarchyDocument200 pagesDifferent Levels of The Memory Hierarchymoonstar_dmeNo ratings yet

- ThreadsDocument2 pagesThreadsharshimogalapalliNo ratings yet

- Linux Basics: Basic Flow of OperationDocument5 pagesLinux Basics: Basic Flow of Operationdba vacancyNo ratings yet

- CS 303 Chapter1, Lecture 3Document18 pagesCS 303 Chapter1, Lecture 3HARSH MITTALNo ratings yet

- "Cache Memory" in (Microprocessor and Assembly Language) : Lecture-20Document19 pages"Cache Memory" in (Microprocessor and Assembly Language) : Lecture-20MUHAMMAD ABDULLAHNo ratings yet

- Mohamed Abdelrahman Anwar - 20011634 - Sheet 4Document15 pagesMohamed Abdelrahman Anwar - 20011634 - Sheet 4mohamed abdalrahmanNo ratings yet

- Multiprocessors and Multithreading: CS151B/EE M116C Computer Systems ArchitectureDocument13 pagesMultiprocessors and Multithreading: CS151B/EE M116C Computer Systems ArchitecturetinhtrilacNo ratings yet

- Build Your Own Distributed Compilation Cluster: A Practical WalkthroughFrom EverandBuild Your Own Distributed Compilation Cluster: A Practical WalkthroughNo ratings yet

- Java TutorialDocument23 pagesJava Tutorialbsgindia82No ratings yet

- Java TutorialDocument13 pagesJava Tutorialbsgindia82No ratings yet

- Java Platforms / Editions: 3) Enterprise ApplicationDocument11 pagesJava Platforms / Editions: 3) Enterprise Applicationbsgindia82No ratings yet

- Java Example: Platform: Any Hardware or Software Environment in Which A Program Runs, Is Known As ADocument12 pagesJava Example: Platform: Any Hardware or Software Environment in Which A Program Runs, Is Known As Absgindia82No ratings yet

- Java TutorialDocument13 pagesJava Tutorialbsgindia82No ratings yet

- Database: Rdbms MongodbDocument7 pagesDatabase: Rdbms Mongodbbsgindia82No ratings yet

- Java TutorialDocument13 pagesJava Tutorialbsgindia82No ratings yet

- Java TutorialDocument13 pagesJava Tutorialbsgindia82No ratings yet

- A Clustered Index Is Like The Contents of A Phone BookDocument7 pagesA Clustered Index Is Like The Contents of A Phone Bookbsgindia82No ratings yet

- The Tungabhadra RiverDocument4 pagesThe Tungabhadra Riverbsgindia82No ratings yet

- The Tungabhadra RiverDocument4 pagesThe Tungabhadra Riverbsgindia82No ratings yet

- Knowledge-Based SystemsDocument1 pageKnowledge-Based Systemsbsgindia82No ratings yet

- Mung Chiang Sangtae Ha: System Modelling & Advancement in Research Trends (SMART), International ConferenceDocument6 pagesMung Chiang Sangtae Ha: System Modelling & Advancement in Research Trends (SMART), International Conferencebsgindia82No ratings yet

- Constraints On Type Parameters (C# Programming Guide) - Microsoft DocsDocument7 pagesConstraints On Type Parameters (C# Programming Guide) - Microsoft Docsbsgindia82No ratings yet

- Differences DBMS RDBMSDocument4 pagesDifferences DBMS RDBMSbsgindia82No ratings yet

- BaekelandDocument11 pagesBaekelandbsgindia82No ratings yet

- Fog ComputingDocument2 pagesFog Computingbsgindia82No ratings yet

- Mung Chiang Sangtae Ha: Surve Yon Fog Comp UtingDocument2 pagesMung Chiang Sangtae Ha: Surve Yon Fog Comp Utingbsgindia82No ratings yet

- Fog ComputingDocument2 pagesFog Computingbsgindia82No ratings yet

- DBMS RDBMSDocument3 pagesDBMS RDBMSbsgindia820% (1)

- Cache Line Ping-Ponging:: Department CSE, SCAD CETDocument2 pagesCache Line Ping-Ponging:: Department CSE, SCAD CETbsgindia82No ratings yet

- FSFDSDFDocument4 pagesFSFDSDFbsgindia82No ratings yet

- Data GridDocument7 pagesData Gridbsgindia82No ratings yet

- 5.explain How Non-Blocking Algorithm Used To Resolve The Deadlock Issues? With Example?Document3 pages5.explain How Non-Blocking Algorithm Used To Resolve The Deadlock Issues? With Example?bsgindia82No ratings yet

- Copyin: Department CSE, SCAD CETDocument2 pagesCopyin: Department CSE, SCAD CETbsgindia82No ratings yet

- MailDocument3 pagesMailbsgindia82No ratings yet

- Deadlock Free CodeDocument2 pagesDeadlock Free Codebsgindia82No ratings yet

- Department CSE, SCAD CETDocument2 pagesDepartment CSE, SCAD CETbsgindia82No ratings yet

- Interleaving Single & Multiple Thread For Execution:: Department CSE, SCAD CETDocument1 pageInterleaving Single & Multiple Thread For Execution:: Department CSE, SCAD CETbsgindia82No ratings yet

- Work-Sharing Sections:: Department CSE, SCAD CETDocument2 pagesWork-Sharing Sections:: Department CSE, SCAD CETbsgindia82No ratings yet

- 8 Lesson 13 Viking FranceDocument2 pages8 Lesson 13 Viking Franceapi-332379661No ratings yet

- Online Dynamic Security Assessment of Wind Integrated Power System UsingDocument9 pagesOnline Dynamic Security Assessment of Wind Integrated Power System UsingRizwan Ul HassanNo ratings yet

- Citroen CX Manual Series 2 PDFDocument646 pagesCitroen CX Manual Series 2 PDFFilipe Alberto Magalhaes0% (1)

- Time Table & Instruction For Candidate - Faculty of Sci & TechDocument3 pagesTime Table & Instruction For Candidate - Faculty of Sci & TechDeepshikha Mehta joshiNo ratings yet

- EE 8602 - Protection and Switchgear Unit I - MCQ BankDocument11 pagesEE 8602 - Protection and Switchgear Unit I - MCQ Bankpoonam yadavNo ratings yet

- Changing Historical Perspectives On The Nazi DictatorshipDocument9 pagesChanging Historical Perspectives On The Nazi Dictatorshipuploadimage666No ratings yet

- Contoh Label Sensus 2022Document313 pagesContoh Label Sensus 2022Ajenk SablackNo ratings yet

- ZH210LC 5BDocument24 pagesZH210LC 5BPHÁT NGUYỄN THẾ0% (1)

- Group 2 - BSCE1 3 - Formal Lab Report#6 - CET 0122.1 11 2Document5 pagesGroup 2 - BSCE1 3 - Formal Lab Report#6 - CET 0122.1 11 2John Eazer FranciscoNo ratings yet

- 37270a QUERCUS GBDocument6 pages37270a QUERCUS GBMocanu Romeo-CristianNo ratings yet

- Question BankDocument3 pagesQuestion BankHimanshu SharmaNo ratings yet

- Pre Intermediate Talking ShopDocument4 pagesPre Intermediate Talking ShopSindy LiNo ratings yet

- Introduction To The Iceberg ModelDocument5 pagesIntroduction To The Iceberg ModelAbhay Tiwari100% (1)

- Slipform Construction TechniqueDocument6 pagesSlipform Construction TechniqueDivyansh NandwaniNo ratings yet

- 1974 - Roncaglia - The Reduction of Complex LabourDocument12 pages1974 - Roncaglia - The Reduction of Complex LabourRichardNo ratings yet

- Creative LibrarianDocument13 pagesCreative LibrarianulorNo ratings yet

- Abstract Cohort 1 Clin Psych FZ 20220323Document31 pagesAbstract Cohort 1 Clin Psych FZ 20220323Azizah OthmanNo ratings yet

- Electronics 12 00811Document11 pagesElectronics 12 00811Amber MishraNo ratings yet

- TMS320C67x Reference GuideDocument465 pagesTMS320C67x Reference Guideclenx0% (1)

- Machine Design REE 302: CH 1: Introduction To Mechanical Engineering DesignDocument26 pagesMachine Design REE 302: CH 1: Introduction To Mechanical Engineering DesignDull PersonNo ratings yet

- BS7430 Earthing CalculationDocument14 pagesBS7430 Earthing CalculationgyanNo ratings yet

- Relay G30 ManualDocument42 pagesRelay G30 ManualLeon KhiuNo ratings yet

- FmatterDocument12 pagesFmatterNabilAlshawish0% (2)

- Form No. 1 Gangtok Municipal Corporation Deorali, SikkimDocument2 pagesForm No. 1 Gangtok Municipal Corporation Deorali, SikkimMUSKAANNo ratings yet

- Activity 2Document5 pagesActivity 2DIOSAY, CHELZEYA A.No ratings yet

- Handbook+for+Participants+ +GCC+TeenDocument59 pagesHandbook+for+Participants+ +GCC+Teenchloe.2021164No ratings yet

- DD 3334Document2 pagesDD 3334FAQMD2No ratings yet

- Num Sheet 1Document1 pageNum Sheet 1Abinash MohantyNo ratings yet

- Formula Renault20 Mod00Document68 pagesFormula Renault20 Mod00Scuderia MalatestaNo ratings yet

- Motive 27Tmx: Data SheetDocument2 pagesMotive 27Tmx: Data SheetUlisesGómezNo ratings yet