Professional Documents

Culture Documents

Power MOSFET Basics: Figure 1b: Planar MOSFET Structure

Power MOSFET Basics: Figure 1b: Planar MOSFET Structure

Uploaded by

Jack PaneOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Power MOSFET Basics: Figure 1b: Planar MOSFET Structure

Power MOSFET Basics: Figure 1b: Planar MOSFET Structure

Uploaded by

Jack PaneCopyright:

Available Formats

1

Power MOSFET Basics

Table of Contents

1. Basic Device Structure

2. Breakdown Voltage

3. On-State Characteristics

4. Capacitance

5. Gate Charge

6. Gate Resistance

7. Turn-on and Turn-off

8. Body Diode Forward Voltage

9. Body Diode Reverse Recovery

10. Avalanche capability and ratings

11. dV/dt ratings

12. Thermal Resistance Characterization

13. Power Dissipation

14. Safe-Operating Area

15. Current Ratings

1. Basic Device Structure

Power MOSFETs (Metal Oxide Semiconductor Field Effect

Transistor) are the most commonly used power devices due to

their low gate drive power, fast switching speed and superior

paralleling capability. Most power MOSFETs feature a

vertical structure with Source and Drain on opposite sides of

the wafer in order to support higher current and voltage.

Figure 1a and 1b show the basic device structures of Trench

and Planar MOSFETs respectively. Trench MOSFETs are

mainly used for <200V voltage rating due to their higher

channel density and thus lower on-resistance. Planar

MOSFETs are good for higher voltage ratings since on-

resistance is dominated by epi-layer resistance and high cell

density is not beneficial. The basic MOSFET operation is the

same for both structures. Unless specified, the N-channel

trench MOSFET is discussed in this application note.

Figure 1a: Trench MOSFET Structure

N

+

P-body

N

-

Epi

N

+

Substrate

Drain

Source

Gate

Figure 1b: Planar MOSFET Structure

2. Breakdown Voltage

In most power MOSFETs the N

+

source and P-body junction

are shorted through source metallization to avoid accidental

turn-on of the parasitic bipolar transistor. When no bias is

applied to the Gate, the Power MOSFET is capable of

supporting a high Drain voltage through the reverse-biased P-

body and N

-

Epi junction. In high voltage devices, most of the

applied voltage is supported by the lightly doped Epi layer. A

thicker and more lightly doped Epi supports higher breakdown

voltage but with increased on-resistance. In lower voltage

devices, the P-body doping becomes comparable to the N

-

Epi

layer and supports part of the applied voltage. If the P-body is

not designed thick or heavy enough, the depletion region can

punch-through to the N

+

source region and cause lower

breakdown. But if it is over designed, the channel resistance

and threshold voltage will also increase. So careful design of

the body and Epi doping and thickness is needed to optimize

the performance.

In the datasheet, BV

DSS

is usually defined as the drain to

source voltage when leakage current is 250uA. The leakage

current flowing between source and drain is denoted by I

DSS

. It

is measured at 100% of the BV

DSS

rating. As temperature

increases, I

DSS

increases and BV

DSS

also increases for power

MOSFETs.

N

+

P-body

N

-

Epi

N

+

Substrate

Gate

Drain

3. On-State Characteristics

We consider here power MOSFET under two different modes

of operations: the first quadrant operation and the third

quadrant operation.

First-Quadrant Operation:

For an n-channel MOSFET, the device operates in the first

quadrant when a positive voltage is applied to the drain, as

shown in figure 2. As the gate voltage (V

G

) increases above

the threshold voltage (V

TH

), the MOSFET channel begins to

conduct current. The amount of current it conducts depends

on the on-resistance of the MOSFET, as defined by

D D DSON

I V R / =

For sufficiently large gate overdrive (V

G

>> V

TH

), the I

D

-V

D

curve appears linear because the MOSFET channel is fully

turned on. Under low gate overdrive, the drain current reaches

a saturation point when V

D

> (V

G

-V

TH

) due to a pinch-off

effect of the channel.

2

Figure 2: On-region characteristics (first-quadrant

operation)

For a trench MOSFET, R

DSON

consists of the following

components:

- R

S

: source resistance

- R

CH

: channel resistance

- R

ACC

: resistance from the accumulation region

- R

EPI

: resistance from the top layer of silicon (epitaxial

silicon, also known as epi); epi controls the amount of

blocking voltage the MOSFET can sustain

- R

SUBS

: resistance from the silicon substrate on which the

epi is grown

Figure 3a: R

DSON

components of a trench MOSFET

For a planar MOSFET, the R

DSON

components are similar to

that of a trench MOSFET. The primary difference is the

presence of a JFET component. As devices scale down to

smaller dimensions, R

S

, R

CH

, R

ACC

are reduced because more

individual unit cells can be packed in a given silicon area.

R

JFET

on the other hand suffers from a JFET-effect where

current is constrained to flow in a narrow n-region by the

adjacent P-body region. Due to the absence of R

JFET

, trench

MOSFETs benefit from high density scaling to achieve very

low R

DSON

.

Rs Rch

RJFET

Repi

Rsubs

Rs Rch Rs Rch

RJFET

Repi

Rsubs

Rs Rch

Figure 3b: R

DSON

components of a planar MOSFET

The channel resistance (R

CH

) is highly dependent on the

amount of the gate overdrive. R

CH

decreases with increasing

V

GS

. R

DSON

initially decreases rapidly as V

GS

increases above

V

TH

, indicating the turning-on of the MOSFET channel. As

V

GS

increases further, R

DSON

drops to a flat region because the

hannel is fully turned on and the MOSFET resistance is

es with temperature due to the decreasing carrier

mobility. This is an important characteristic for device

paralleling.

c

limited by the other resistance components.

R

DSON

increas

Rs

Rch

Racc

Repi

Rsubs

Figure 4: R

DSON

vs. gate bias and temperature

Threshold Voltage

Threshold voltage, V , is defined as the minimum gate

bias which can form a conducting channel between the source

and drain. For power MOSFETs, it is usually measured at the

drain-source current of 250uA. Gate oxide thickness and

doping concentration of the channel can be used to control the

V . Typically, 2~4V is designed for gate drive of 10-15V.

With the scaling down of the CMOS technology, the gate

drive of the power MOSFET drops to 2.5-4.5V. Therefore,

lower threshold voltages of 1-2V are needed for these

applications. T

GS(TH)

GS(TH)

he threshold voltage has a negative temperature

3

means it decreases with increasing

Transconductance

coefficient, which

temperature.

Transconductance, g

fs

, which is defined as the gain of the

MOSFETs, can be expressed as the following equation:

GS

fs

V

DS

I

g

=

CH

OX n

fs

L

W C

g

=

It is usually measured at saturation region with fixed V

DS

. The

transconductance is influenced by gate width (W), channel

gate capacitance (C

OX

) of the length (L

CH

), mobility (

n

), and

devices. g

fs

decreases with increasing temperature due to the

decreasing carrier mobility.

Third-Quadrant Operation:

Third-quadrant operation for power MOSFET is common in

C-DC buck converters, where current conduction occurs

nder relatively low current, the on-state characteristics for

sufficient large current, and

therefore sufficient large V

DON

. When V

DON

approaches the

forward drop voltage of the body diode, the body diode starts

to conduct. As a result, the current increases and no current

saturation behavior is observed.

D

under at V

DS

(for an n-channel MOSFET). Current flows in

the reverse direction compared to first-quadrant operation.

The same R

DSON

components apply.

U

the third-quadrant operation are symmetric to that of the first

quadrant operation. We may assume the same R

DSON

for both

types of operation.

Differences appear only under

-30

-25

-20

-15

-10

-5

0

-1 -0.8 -0.6 -0.4 -0.2 0

V

DS

(V)

I

D

(

A

)

V

GS

=0V

(Body diode)

2.5V

4.5V

10V

Capacitance

The MOSFETs switching behavior is affected by the parasitic

capacitances between the devices three terminals, that is,

gate-to-source (C

GS

), gate-to-drain (C

GD

) and drain-to-source

(C

DS

) capacitances as shown in Figure 6. These capacitances

values are non-linear and a function of device structure,

geometry, and bias voltages.

N

+

P-body

N

-

Epi

N

+

Substrate

Source

Gate

Drain

Cgs

Cgd

Cds

N

+

P-body

N

-

Epi

N

+

Substrate

Source

Gate

Drain

Cgs

Cgd

Cds

Figure 6: Illustration of MOSFET parasitic capacitances

During turn on, capacitors C

GD

and C

GS

are charged through

the gate, so the gate control circuit design must consider the

variation in this capacitance. The MOSFET parasitic

capacitances are provided in the data sheet parameters as C

ISS

,

C

OSS

, and C

RSS

:

C

GD

= C

RSS

C

GS

= C

ISS

C

RSS

C

DS

= C

OSS

C

RSS

C

RSS

= small-signal reverse transfer capacitance.

C

ISS

= small-signal input capacitance with the drain and source

terminals are shorted.

C

OSS

= small-signal output capacitance with the gate and

source terminals are shorted.

The MOSFET capacitances are non-linear as well as a

function of the dc bias voltage. Figure 7a shows how

capacitances vary with increased V

DS

voltage. All the

MOSFET capacitances come from a series combination of a

bias independent oxide capacitance and a bias dependent

depletion (Silicon) capacitance. The decrease in capacitances

with V

DS

comes from the decrease in depletion capacitance as

the voltage increases and the depletion region widens.

Figure 7b shows that the MOSFET gate capacitance also

increases when the V

GS

voltage increases past the threshold

voltage (for low V

DS

values) because of the formation of an

inversion layer of electrons in the MOS channel and an

accumulation layer of electrons under the trench bottom. This

why the slope of the gate charge curve increases once the

voltage goes beyond the Q

gd

phase.

Figure 5: Third-Quadrant Operation

4.

Figure 7a: Typical variation of Capacitances with V

DS

3000

3500

4000

4500

5000

0 1 2 3 4 5

V

GS

(V)

C

i

s

s

(

p

F

)

C

iss

V

DS

=0V

Figure 7b: Typical variation of C

iss

with V

GS

5. Gate Charge

Gate charge parameter can be used to estimate switching times

of the power MOSFET once the gate drive current is known. It

depends only on the device parasitic capacitances. This

parameter is also weakly dependent of the drain current, the

supply voltage, and the temperature.

A schematic the gate charge test circuit and its waveform is

shown in Figure 8. In this circuit a constant gate current

source I

g

charges the gate of the device under test, while drain

current I

D

is sourced. Measuring V

GS

vs. gate charging time

provides a direct indication of the energy spent to switch drain

current from 0 to I

D

as the Drain voltage swings from V

DC

to

its on-state voltage.

Before the gate current is turned on, the DUT withstands all

the supply voltage V

DC

, while the voltage V

GS

and the drain

current are zero. Once the gate current Ig flows, the gate-to-

source capacitance C

GS

and gate-to-drain capacitance C

GD

start

to charge and the gate-to-source voltage increases. The rate of

charging is given by I

G

/C

ISS

. Once the voltage V

GS

reaches

threshold voltage of the power MOSFET, drain current starts

to flow. The gate voltage continues to rise to the plateau

voltage V

GP

(V

GSTH

+I

D

/g

FS

), while the voltage across the DUT

remains equal to V

DC

. The charge (Ig*time) needed to reach

this state is Q

GS

. Once the drain current reaches I

D

the drain

voltage starts to fall. At this period of time, V

GS

remains

constant at V

GP

. The gate current is used to charge the C

GD

capacitance and Ig= C

GD

. dV

DS

/dt . The plateau phase ends

when V

DS

reaches its on-state value. The gate charge injected

during this plateau phase is Q

GD

and is often used to estimate

voltage transition times and switching loss.

Next, the DUT gate continues charging to its final value, and

the drain-to-source voltage becomes equal to R

DSON

x I

D

. The

gate-to-source voltage is free to rise with a slope controlled by

the gate charging current and the C

ISS

(which is higher at

V

GS

>V

TH

as shown in figure 7b, leading to a lower slope in the

gate charge curve) until the gate-to-source voltage reaches its

maximum value. This gate charge is the total gate charge Q

G

.

Figure 8: Gate charge test circuit & waveform

6. Gate Resistance

The power MOSFET gate presents an impedance like an RC

network to its gate drive. The equivalent R is referred to as the

gate resistance Rg. The gate resistance is caused by the finite

resistance of the Polysilicon gate conductors, and the metal

and contact structures that route the gate signal to the pad for

connection to external package leads. For polysilicon gate

power trench MOSFETS, the resistance of the gate electrode

depends on doping level and type (N type or P-type) of

polysilicon material, gate trench geometry and the device

layout arrangement. N-type trench power MOSFETs usually

have lower gate resistance than that of P-type trench power

MOSFETs for the same device layout due to lower sheet

resistance of N-type in situ doped polysilicon.

Most switching devices are 100% final tested for Rg using

LCR meters

7.

4

Turn-on and Turn-off

5

Figure 9: Resistive switching test circuit & waveforms

Power MOSFET datasheets often contain the resistive

switching characteristics, which depend on R

g

, C

iss

and C

rss

.

While practical measurements are influenced by parasitic

inductances and gate drive details, we examine the basic

physics here. Figure 9 shows the power MOSFET resistive

switching test circuit and waveforms.

t

d(on)

Turn-on Delay Time

This is the time from when V

gs

rises over 10% of the gate

drive voltage to when the drain current rises past 10% of the

specified current. At the moment of t

d(on)

, V

GS

reaches up to

the threshold voltage V

TH

. This period is controlled by the

time constant R

g

.C

iss

.

t

r

Rise Time

This is the time between the drain current rising from 10% to

90% of load current. This depends on the V

TH

,

transconductance g

FS

and the time constant R

g

.C

rss

.

t

d(off)

Turn-off Delay Time

It is the time from when V

gs

drops below 90% of the gate

drive voltage to when the drain current drops below 90% of

the load current. It is the delay before current starts to

transition in the load, and depends on R

g

.C

iss

.

tf Fall Time

It is the time between the drain current falling from 90% to

10% of load current. This depends on the V

TH

,

transconductance g

FS

and the time constant R

g

.C

rss

.

8.

Body Diode Forward Voltage

V

SD

is a measure of the forward voltage drop of the integral

body diode, by applying a set current to the source. The

applied current is typically 1A and is specified in the datasheet

along with the maximum limit of forward voltage drop.

Figure 10 shows typical forward I-V characteristics for the

diode at two temperatures. For AOS SRFET, the typical V

SD

is

lower than that of a normal MOSFET, with typical value of

0.4V; this low V

SD

can help to reduce power loss during diode

conduction duration. SRFET is therefore an ideal choice for

low side FETs for DC-DC conversion, and other applications

where a certain period of body diode conduction is needed.

1.0E-02

1.0E-01

1.0E+00

1.0E+01

1.0E+02

0.0 0.2 0.4 0.6 0.8 1.0

V

SD

(Volt s)

I

S

(

A

)

25C

125C

SRFET 25C

Regular FET

125C

Figure 10: Body-Diode forward Characteristics

9. Body Diode Reverse Recovery

MOSFET parasitic body diode reverse recovery occurs during

diode switching from the on-state to the off-state, because its

stored minority charges must be removed, either actively via

negative current, or passively via recombination inside the

device. There are three dynamic parameters listed in the

datasheet for diode reverse recovery:

t

rr

: body diode reverse recovery time

I

RM

: body diode reverse peak current

Q

rr

: Body diode reverse recovery charge, defined by

=

trr

sd rr

dt t i Q ) (

the area within the negative portion of the diode current

waveform.

The above parameters vary with test condition, such as applied

voltage V

DS

and di/dt etc. The parameter definitions and test

circuit are shown in Figure 11.

Figure 11: Diode reverse recovery test circuit &

waveforms

The gate and source of DUT are shorted to test the body diode.

A control device is subjected to a double pulse. The current

ramps in the lower control device, and freewheels through the

DUT body diode when the control device turns off. When it is

turned on again by the second pulse, the DUT body diode

must recover before the control FET voltage can drop.

During diode reverse recovery, its reverse current also goes to

the lower FET in Figure 11, along with the load current; in

addition, the reverse recovery di/dt can cause large voltage

overshoots (Ldi/dt) due to circuit stray inductance. These

voltage overshoots are minimized if the di/dt during the

second phase of the t

rr

(after crossing I

RM

) is kept low. Such a

diode is said to have soft recovery. Lower Q

RR

leads to lower

switching loss. This is often the largest single component of

switching loss in a switching converter.

AOS SDMOS and SRFET have been designed with advanced

technology specifically to improve body diode reverse

recovery performance with low Q

rr

and good softness

coefficient compare to regular MOSFETs, which can greatly

reduce the voltage overshoot, and improve the overall

efficiency.

10.

Avalanche capability and ratings

Physics of avalanche breakdown

As the voltage of a power MOSFET is increased, the electric

field increases at the body-epi junction. When this field

reaches a critical value E

C

(about 3E5V/cm in Si), avalanche

multiplication of carriers occurs, leading to an abrupt increase

in current. Avalanche multiplication is not a destructive

process. However, since the current flow path involves hole

current flow I

H

(=I

D

) in the path shown in Figure 12, there is

the possibility at high current density of turning on the

parasitic bipolar when V

BE

=I

H

*(Rp+Rc)>0.7V. When this

occurs, the gate can no longer turn-off the FET current. Also,

since the BVCEO is typically lower than the MOSFET

breakdown, current filaments into the weakest cell where local

non-uniformities first cause the parasitic bipolar to turn-on.

From this basic description it follows that:

Failure occurs above a critical current density (even

for short low energy high voltage pulses)

High values of Rp (body pinch resistance under the

source) and Rc (contact resistance) degrade UIS

capability

High density cell construction reduces the length of

the current path. This decreases Rp, and increases the

critical current density at which failure occurs.

Since both Rp and Rc increase with temperature, and

the emitter-base turn on voltage V

BE

decreases with

temperature, UIS capability decreases with

temperature.

If avalanche capability is tested at lower currents over a long

duration, the energy dissipated I

pk

/2*BV*t

AV

heats the device.

The failing current is therefore determined by the peak

temperature the device reaches during this event. Since large

chips have a greater heat capacity, they have higher UIS

capability in this mode of operation.

N

+

P-body

N

-

Epi

N

+

Substrate

Source

Gate

Drain

Rp

Rc

N

+

P-body

N

-

Epi

N

+

Substrate

Source

Gate

Drain

Rp

Rc

Figure 12: Trench MOSFET cell construction. Parasitic

NPN is shown, along with parasitic base resistances Rp

and Rc

6

Avalanche ratings

Power MOSFETs may be driven to voltages in excess of rated

V

DS(MAX)

due to inductive spikes during circuit operation.

Therefore, manufacturers commonly specify single and

repetitive ratings, and many perform 100% single pulse testing

on shipped units.

Typical single pulse ratings are captured using time in

avalanche curves as shown in figure 13. These are guaranteed

performance data, and the actual point of destruction is above

this level. As expected, avalanche capability decreases with

temperature for the same time duration. The current capability

decreases with longer times in avalanche at a given starting

junction temperature due to heating during the avalanche

event.

These curves are generated using the circuit in figure 14,

where the current is ramped up in the device under test

through an inductor. When the device turns off, since the

inductor current cannot be interrupted, the device voltage flies

up to the breakdown voltage of the device. When the device

turns off, the switch in series with the supply V

dd

is also turned

off, forcing the current to freewheel though the diode. Now

the voltage across the inductor is BV, which causes the

current to ramp down to zero. Using different inductors, one

may obtain different times in avalanche. The basic equations

relating Energy, current, time and inductance are listed below:

L i dt V i E

pk DS L ar

= =

2

2

1

BV

L i

t

pk

av

=

Figure 13: Time in avalanche vs. Peak current as a

function of temperature

Figure 14: Test circuit used for UIS (avalanche)

measurements

Repetitive ratings:

If a power MOSFET is subjected to repetitive UIS pulses, its

junction temperature undergoes an increase in average value,

based on the average power dissipated as well as peaks of

temperature with each pulse. When the current density is high

enough, and the peak temperature is high enough, the device

can fail from the same mechanisms as described for single

pulse avalanche.

No common standard is being used for specifying repetitive

avalanche ratings. Two methods are described here.

Method 1: Select a small inductor, say L=1H, with duty

cycle of 0.01, f=100kHz. Increase the current until average

temperature reaches T

J

=150C to set I

AR

. Or increase current

until destruction occurs and de-rate to establish the I

AR

rating.

This method has the disadvantage that it only relates to one

inductor and one frequency. If the frequency is raised, I

AR

drops. If the inductor is higher, I

AR

drops. In fact, if the

frequency is low enough such that the device returns to its

starting T

J

(25C) after each pulse, well designed power

MOSFETs will have E

AR

=E

AS

, and I

AR

=I

AS

.

Method 2: Do not distinguish E

AR

, E

AS

, and I

AR

,

I

AS

since

they

are the same at low enough frequency. The user may use the

time in avalanche curves for short time durations to estimate

the maximum allowable current in avalanche, beginning with

an estimate of starting T

J

from the average power dissipation P

and thermal resistance.

2

5 . 0 fLI P =

JA

J

R

P

T

=

11.

7

dV/dt ratings

Power MOSFETs fail from excessive drain source dV/dts

under various scenarios. In each case, the failure is caused by

displacement or conduction current flow via Rp+Rc, leading

to turn-on of the parasitic bipolar, and consequent failure of

the device by the same mechanism described before for

avalanche failures.

If the gate is shorted to source via a resistor, and a

fast dV/dt applied between Drain and source, the

displacement current C

oss

*dV/dt flows under the

source, and can develop sufficient voltage drop

across Rp+Rc to exceed the V

BE

(0.7V) of the

parasitic bipolar. Due to the low Coss values of most

modern power MOSFETs, this current is low even

for dV/dts of 10-50V/ns, and is not considered a

major failure mode. If however, the resistance

shorting the gate to source is large, the C

rss

*dV/dt

current will develop enough voltage drop across it to

turn on the gate, leading to current flow which if

unconstrained, can lead to device failure.

During body diode reverse recovery, hole current

flows out of the source contact via R

p

+Rc. This

current adds to and often far exceeds the C

oss

*dV/dt

current at also flows as the voltage develops across

the body diode of the FET. Since the diode stored

charge and its removal is non-uniform, the diode

recovery dV/dt failure is seen at lower values of

dV/dt. The failure mechanism is again caused by

turn-on of the parasitic bipolar. If the gate-source

shorting resistor is too large, there is the further

possibility of exacerbating the dV/dt current by

turning on the gate of the MOSFET by developing

sufficient voltage across the resistor as it sinks the

C

rss

*dV/dt current.

Both modes of dV/dt failure get worse with

temperature.

12.

Thermal Resistance Characterization

Junction Calibration

Before the thermal resistance of any device is to be measured,

a calibration curve must be made. Each silicon device has its

own unique calibration, but once determined, is valid for any

package it may be put into.

The calibration curve is measured by treating the device as a

diode and forcing a 10mA sense current (I

S

) and measuring the

forward voltage drop (V

FSD

) at each junction temperature. A

sample calibration curve for a device is shown in Figure 15.

On subsequent thermal resistance tests, the same 10mA sense

current will be forced through the device and the junction

temperature will be calculated from the resulting forward

voltage drop.

Figure 15: Sample Temperature Calibration Curve.

Junction-to-Ambient/Lead/ Case Thermal Resistance

The junction-to-ambient thermal resistance R

JA

is defined as

the thermal resistance from the device junction to the ambient

environment. The junction-to-lead thermal resistance R

JL

is

the thermal resistance from the device junction to the drain

lead of the device. For larger devices (Ultra SO8 and bigger)

with a back exposed drain pad, the R

JC

must also be

measured. R

JC

is defined as the thermal resistance from the

device junction to the device case. Both can be calculated

from the following equation:

D

X J

JX

P

T T

R

=

Where T

J

is the junction temperature of the device, it can be

read out from junction calibration curve by measuring forward

voltage drop at different junction temperature. T

X

is the

ambient, lead or case temperature depending on whether R

JA,

R

JL

or R

JC

is being measured, and P

D

is the power dissipation

of the device, which is calculated by input voltage and current.

8

Transient Thermal Heating Curve, Junction to Ambient/

Case

Transient thermal curves can be used to estimate instantaneous

temperatures resulting from power loss on a transient basis.

These curves can be Junction to Ambient or Case based.

Namely they are characterizing transient thermal impedance

form device junction to ambient or case.

The thermal measurement machine applies a single pulse with

various durations; junction temperature is read again by

measuring forward voltage drop after each single pulse. This

measures the single pulse transient thermal curve. Based on

single pulse curve, a 3 or 4 stages RC network is simulated to

generate the rest curves in Transient Thermal Heating curve

group, as show in Figure 16.

0.001

0.01

0.1

1

10

0.00001 0.0001 0.001 0.01 0.1 1 10 100 1000

Pulse Widt h (s)

Z

J

A

N

o

r

m

a

l

i

z

e

d

T

r

a

n

s

i

e

n

t

T

h

e

r

m

a

l

R

e

s

i

s

t

a

n

c

e

Figure 16: Sample Transient Thermal Heating Curve

based on Junction-to-Ambient measurements.

13.

Power Dissipation

Power dissipation P

D

and P

DSM

are the maximum power that is

allowed for device safe operation. Power dissipation is

calculated using the following formula:

(max)

(max)

JC

C J

D

R

T T

P

=

(max)

(max)

JA

A J

DSM

R

T T

P

=

P

D

is based on junction to case thermal resistance. To achieve

power dissipation of P

D

, case temperature needs to be

maintained at 25

o

C.

P

DSM

is based on junction to ambient thermal resistance. The

device is mounted on a 1 square inch 2 oz. copper PCB, and

P

DSM

is the power that raises T

j

to 150

o

C

14. Safe-Operating Area

SOA (FBSOA) curves define the maximum value of drain to

source voltage and drain current which guarantees safe

operation when the device is in forward bias.

Figure 17: Maximum Forward Biased Safe Operating

Area

The right hand vertical boundary is maximum drain to source

voltage (V

DS

).

The upper horizontal limit is maximum pulsed drain current

(I

DM

).

The slope on left had side is limited by drain to source on

resistance (R

DS(ON)

)

The paralleled lines in the middle are the maximum drain to

source current for different pulse widths. These currents are

determined by the transient thermal impedance.

15.

9

Current Ratings

Continuous Drain current - I

D

and I

DSM

Excluding package limitations, the continuous Drain Current

I

D

and I

DSM

is the maximum drain current corresponding to P

D

and P

DSM.

(max) max ) (

@

J on DS

D

D

T R

P

I =

I

D

will be de-rated with increasing case temperature, as shown

in Figure 18, based on the reduced power dissipation allowed.

Figure 18: Current rating vs. case temperature

Package Limitation

Continuous current rating is limited by two factors:

1. thermal resistance

2. package limitation

Package limitation usually refers to bond wire current

handling capability. The conventional way to rate bond wire

current limit is based on bond wire fusing temperature, which

is not correct because:

1. Wire temperature can not exceed 220

o

C, or it

will cause the degradation of the plastic molding

compound.

2. In most cases the silicon resistance is ~10 times

higher than wire resistance. Most of the heat is

generated on the silicon surface. The hottest spot

is on silicon.

Silicon maximum junction temperature is lower than 220

o

C,

thats why bond wire fusing problem doesnt exist in most of

the cases. Bond wires fuse only when devices fail. Please refer

to application note [MOS-006] on AOS website.

Pulsed Drain Current - I

DM

Pulsed Drain Current is rated for 260s current pulse. The

value on datasheet is the lower value of the following two:

1. Actual single pulse current measurement with

260s current pulse.

2. Calculation based on transient thermal resistance

at 260s pulse duration.

Reference:

[1] B. J. Baliga, Fundamentals of Power Semiconductor

Devices, 2008.

[2] Application notes MOS-006, Power MOSFET

Continuous Drain current rating and Bonding wire limitation,

www.aosmd.com.

10

You might also like

- Ecler PAM1360 Service ManualDocument98 pagesEcler PAM1360 Service ManualChris67% (3)

- Abc of Capacitors: Basic PrinciplesFrom EverandAbc of Capacitors: Basic PrinciplesWürth ElektronikNo ratings yet

- 3 Power MosfetDocument23 pages3 Power MosfetSayan DasNo ratings yet

- REN An7244 APN 19980812Document5 pagesREN An7244 APN 19980812Jeff PalaganasNo ratings yet

- Power MOSFET Basics Understanding Superjunction Technology: MosfetsDocument5 pagesPower MOSFET Basics Understanding Superjunction Technology: Mosfetsfsilassie8012No ratings yet

- Unit 01Document21 pagesUnit 01mathanstar77No ratings yet

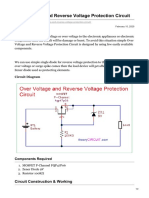

- Over Voltage and Reverse Voltage Protection CircuitDocument2 pagesOver Voltage and Reverse Voltage Protection CircuitfabiobonadiaNo ratings yet

- Banner - Introduction To MOSFETDocument1 pageBanner - Introduction To MOSFETAviral ChaurasiaNo ratings yet

- Amplificadores Cascode MosfetDocument5 pagesAmplificadores Cascode MosfetlucianoNo ratings yet

- GROUP 3 - MOSFET Working Principle - NSESP 2021Document15 pagesGROUP 3 - MOSFET Working Principle - NSESP 2021Sisilia Anabina TariganNo ratings yet

- Power MosfetsDocument11 pagesPower MosfetsSoudip KUNDUNo ratings yet

- Mosoft Circuit ApplicationDocument16 pagesMosoft Circuit Applicationkaran007_mNo ratings yet

- Design and Application Guide For High Speed MOSFET Gate Drive CircuitsDocument37 pagesDesign and Application Guide For High Speed MOSFET Gate Drive CircuitswewNo ratings yet

- Lectura 3 M PDFDocument12 pagesLectura 3 M PDFFlakita S MelcOchitaNo ratings yet

- Design of Cmos Multistage High Gain Differential Amplifier Using CadenceDocument4 pagesDesign of Cmos Multistage High Gain Differential Amplifier Using CadenceAbdulrahman behiryNo ratings yet

- Power Mosfet DetailsDocument66 pagesPower Mosfet DetailsCan IlicaNo ratings yet

- Understanding The Differences Between Standard Mosfets and Avalanche Energy Rated MosfetsDocument10 pagesUnderstanding The Differences Between Standard Mosfets and Avalanche Energy Rated MosfetscalinvaNo ratings yet

- Assignment FET 2Document3 pagesAssignment FET 2shobanraj1995No ratings yet

- Unit - 3Document8 pagesUnit - 3AgnathavasiNo ratings yet

- Eee421: Power Electronics: Power Semiconductor Devices: MOSFETDocument9 pagesEee421: Power Electronics: Power Semiconductor Devices: MOSFETRafat ShamsNo ratings yet

- MosfetDocument13 pagesMosfetSristick100% (3)

- Power MOSFET BasicsDocument13 pagesPower MOSFET BasicsTim PriceNo ratings yet

- Application Note AN-1084: Power MOSFET BasicsDocument13 pagesApplication Note AN-1084: Power MOSFET Basicshardcore18No ratings yet

- Power Mosfet ExplanationDocument12 pagesPower Mosfet ExplanationAntony RousosNo ratings yet

- LM2727/LM2737 N-Channel FET Synchronous Buck Regulator Controller For Low Output VoltagesDocument26 pagesLM2727/LM2737 N-Channel FET Synchronous Buck Regulator Controller For Low Output Voltagesdavid.gjeorgevskiNo ratings yet

- Mofet - IGBT - SCR - Traic - Snubber CKTDocument17 pagesMofet - IGBT - SCR - Traic - Snubber CKTTejas krishnakanthNo ratings yet

- Ecler Pam1400 1000 600 300Document183 pagesEcler Pam1400 1000 600 300Lluis Reparacion ElectronicaNo ratings yet

- EEE111+ (Exp+7) +Study+of+Switching+CharacteristicsDocument5 pagesEEE111+ (Exp+7) +Study+of+Switching+CharacteristicsFaria SharifNo ratings yet

- Electronics Chapter 4Document16 pagesElectronics Chapter 4YidnekachewNo ratings yet

- Project 1 FullDocument10 pagesProject 1 FullSaratul AkmaNo ratings yet

- Sesi II 2021 Topicd Lect3Document29 pagesSesi II 2021 Topicd Lect3mbagavan 0712No ratings yet

- Controlled Devices FET, BJT, IGBTDocument51 pagesControlled Devices FET, BJT, IGBTHolloGramNo ratings yet

- Course Name: Basic Electronics Engineering Course Code: EC101 Metal Oxide Semiconductor Field Effect Transistor (MOSFET)Document37 pagesCourse Name: Basic Electronics Engineering Course Code: EC101 Metal Oxide Semiconductor Field Effect Transistor (MOSFET)Dr Sunipa RoyNo ratings yet

- Jfet and Mosfet Characterization 5aae458a1723dd235e70b7d9Document23 pagesJfet and Mosfet Characterization 5aae458a1723dd235e70b7d9hasan mubinNo ratings yet

- Power MOSFET: Basic StructureDocument10 pagesPower MOSFET: Basic StructureDomagoj ProphectusNo ratings yet

- Mosfets BasicsDocument7 pagesMosfets Basicsodl_123No ratings yet

- Vincotech TP 2018 05 The Challenges of Using SiC MOSFET-based Power Modules For Solar Inverters Tauer MatthiasDocument5 pagesVincotech TP 2018 05 The Challenges of Using SiC MOSFET-based Power Modules For Solar Inverters Tauer MatthiasCan IlicaNo ratings yet

- Irf An-940Document5 pagesIrf An-940jamesjunNo ratings yet

- Field Effect Transistors: Submitted To: Ma'am FarwahDocument25 pagesField Effect Transistors: Submitted To: Ma'am FarwahjawadNo ratings yet

- Ed Unit 4Document32 pagesEd Unit 4Deepa.J DeeNo ratings yet

- FETs 11Document55 pagesFETs 11بلسم محمود شاكرNo ratings yet

- EECE 453-Unit 2-Amplifiers-Part 1Document20 pagesEECE 453-Unit 2-Amplifiers-Part 1Mashruha Binte NoorNo ratings yet

- No - EE331-Lab-3 - 2023-05-23T103126.278Document9 pagesNo - EE331-Lab-3 - 2023-05-23T103126.278Def AbcNo ratings yet

- Tuen Voltage AmplifirDocument8 pagesTuen Voltage Amplifirkaran007_mNo ratings yet

- EDID632C: Elementary Studies: Transistor FundamentalsDocument87 pagesEDID632C: Elementary Studies: Transistor Fundamentalsakash kumarNo ratings yet

- Power Electronics Lecture-2BDocument46 pagesPower Electronics Lecture-2BIbrahim MehmoodNo ratings yet

- Btran White Paper CURRENT 12april2016Document11 pagesBtran White Paper CURRENT 12april2016Wilkins CedanoNo ratings yet

- Fet01 PDFDocument16 pagesFet01 PDFPierce Denver DayotNo ratings yet

- Lecture11!11!12284 MosfetDocument28 pagesLecture11!11!12284 Mosfetshivali.vannarathNo ratings yet

- Passive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2From EverandPassive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2No ratings yet

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10From EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- 1.K&H Pe-5000Document12 pages1.K&H Pe-5000FARUQ SAMNo ratings yet

- Xlpe Cable CatalogueDocument88 pagesXlpe Cable CatalogueNishantha AriyadasaNo ratings yet

- AN2731Document26 pagesAN2731WayneNo ratings yet

- Problems On Synchronous MachineDocument9 pagesProblems On Synchronous MachineypobuleshNo ratings yet

- Wiring DiagramDocument12 pagesWiring DiagramUlises Andres MartinesNo ratings yet

- Physics X Rays QuestionsDocument8 pagesPhysics X Rays Questionskirki pNo ratings yet

- TTB 709017 172718 172718dei 65FDocument1 pageTTB 709017 172718 172718dei 65FДмитрийNo ratings yet

- CL - Omkar ElectronicsDocument16 pagesCL - Omkar ElectronicsSazzad Hossan RaselNo ratings yet

- Assembly Instructions: Conventional Motor (Beakman's Motor Kit)Document7 pagesAssembly Instructions: Conventional Motor (Beakman's Motor Kit)pmufmsNo ratings yet

- Funai 29a-250-450 Service ManualDocument70 pagesFunai 29a-250-450 Service Manualgnaks58No ratings yet

- EEC Sample Paper SolutionDocument29 pagesEEC Sample Paper Solutionpranav mawale100% (2)

- Lightning Protection System ExplainedDocument2 pagesLightning Protection System Explainedabuzar12533No ratings yet

- Pod Using HVDCDocument31 pagesPod Using HVDCRajeev JhaNo ratings yet

- Jecet.v3i3c 7Document11 pagesJecet.v3i3c 7Jose LunaNo ratings yet

- 5641AHDocument4 pages5641AHEdgarNo ratings yet

- Resin RichDocument2 pagesResin Richsupriya rakshitNo ratings yet

- EM5203 SeriesDocument12 pagesEM5203 Seriesprakash_sasikalaNo ratings yet

- 1g Mitsubishi 6G72 - FusesDocument5 pages1g Mitsubishi 6G72 - Fusesaren_mendoza75% (4)

- IEEE-519 Harmonic StandardDocument2 pagesIEEE-519 Harmonic StandardDavid GuevaraNo ratings yet

- ABB Catalogue IMZ 24Document4 pagesABB Catalogue IMZ 24Ieremeiov VladimirNo ratings yet

- 3rd SEM EDI LAB Manual (18ECL37)Document48 pages3rd SEM EDI LAB Manual (18ECL37)Shreesha KalkoorNo ratings yet

- Owner'S Instruction Manual: Tractor Driven AlternatorDocument16 pagesOwner'S Instruction Manual: Tractor Driven Alternatormarvin17No ratings yet

- Waqad Qayyum CH.: PEC # 47035 Nationality: Pakistani CNIC No.: 35202-9066649-9Document2 pagesWaqad Qayyum CH.: PEC # 47035 Nationality: Pakistani CNIC No.: 35202-9066649-9Naveed Nazir0% (1)

- How To Select The Right FuseDocument1 pageHow To Select The Right FuseLaurentiu IacobNo ratings yet

- Chapter 5 Voltage RegulatorDocument38 pagesChapter 5 Voltage RegulatorLizhe KhorNo ratings yet

- Power Quality Improvement TechniquesDocument7 pagesPower Quality Improvement TechniquesSathu Yaduvamsee ee23e007No ratings yet

- 06 - MCP - Current Transformers (6.71 - 6.72)Document2 pages06 - MCP - Current Transformers (6.71 - 6.72)ThilinaNo ratings yet

- FCCL PCB What Is Flexible Copper Clad LaminateDocument8 pagesFCCL PCB What Is Flexible Copper Clad LaminatejackNo ratings yet

- Technical Specification 2xy CableDocument13 pagesTechnical Specification 2xy CablejamilNo ratings yet

- Calculation of Backflashover Outage Rate of Transmission Lines: A Discussion On Traditional Methodologies and Recent AdvancesDocument5 pagesCalculation of Backflashover Outage Rate of Transmission Lines: A Discussion On Traditional Methodologies and Recent AdvancesWallison CarvalhoNo ratings yet