Professional Documents

Culture Documents

DCH34xx Security

Uploaded by

aurodenCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DCH34xx Security

Uploaded by

aurodenCopyright:

Available Formats

5

+3.3V +3.3V

R1000

1K_s

R1003

100_s

J1000

header_5pins_2rows

1

2

3

4

5

6

7

8

9

10

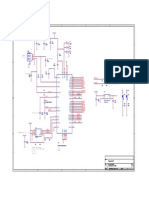

Altera EP2C5/ EP2C8

U1001B

R1004

1K_s

+3.3V

+1.2V

R1017

100_s

+3.3V

B1001

ferrite_1206

R1024

R1008

4_7K_s

R1007

10K_s

+3.3V

+3.3V

F3

J4

VREFB1N0

VREFB1N1

TP1007

TP1001

C11

D8

VREFB2N0

VREFB2N1

G9

H7

H10

J7

J10

K8

VCCINT

VCCINT

VCCINT

VCCINT

VOID/NC/VCCINT

VOID/NC/VCCINT

GND

GND

GND

GND

GND

GND

G8

H8

H9

J8

J9

K9

B1

G3

K3

R1

VCCIO1

VCCIO1

VCCIO1

VCCIO1

GND

GND

GND

GND

B2

H3

J3

R2

A2

A15

C7

C10

E7

E10

VCCIO2

VCCIO2

VCCIO2

VCCIO2

VCCIO2

VCCIO2

GND

GND

GND

GND

GND

GND

A1

A16

C8

C9

E8

E9

+3.3V

U1001A

R3

H2

D3

M1

K2

K1

TP1002

+3.3V

18 MHIF_CFG_CLK

18 MHIF_CFG_N

R1006

R1012 150_s

150_s R1013

150_s

MHIF_CFG_CLK (BCM7038 GPIO pin)

must be configured as input after FPGA

configuration, because FPGA pin H4

becomes an output after configuration

F1

H4

J5

G5

J13

K12

F2

G2

G1

H5

P2

P1

cfg_data

cfg_dclk

nConfig

nCE

msel[0]

msel[1]

M13

L13

C1

F4

C3

FPGA Config.

nStatus

Conf_Done

CRC_ERROR

nCSO

ASDO

R1005

10K_s

R1009

1K_s

R1010

10K_s

C1006

1U_s

C1024

0_01U_s

C1004

0_01U_s

C1025

0_01U_s

C1007

0_01U_s

C1026

0_01U_s

C1028

1U_s

C1008

0_01U_s

C1009

0_01U_s

C1010

0_01U_s

C1011

0_01U_s

C1012

0_01U_s

C1013

0_01U_s

C1014

0_01U_s

C1016

1U_s

C1017

0_01U_s

C1018

0_01U_s

C1019

0_01U_s

C1020

0_01U_s

C1021

0_01U_s

C1022

0_1U_s

C1023

0_01U_s

TP1047 TP1010

C1027

10U

MHIF_SDO 18

MHIF_IRQ_N 18

+3.3V

MHIF_CFG_STATUS 18

MHIF_CFG_DONE

18

C1015

10U_c

MSEL = 00 (Active Serial Configuration, 20 MHz)

MSEL = 01 (Passive Serial Configuration)

MSEL = 10 (Active Serial Configuration, 40 MHz)

MSEL = 11 (JTAG only)

+1.2V

U1001D

MHIF/ EP2C5/ EP2C8

PLL1_OUTp/mpodo_clk

mpodo_syn

MPOD

mpodo_d0

mpodo_d1

9 7038_MPODO_CLK

7038_MPODO_SYNC

7038_MPODO_DATA0

7038_MPODO_DATA1

6

6

6

BCM325x_OOB_CLK

BCM325x_OOB_SYNC

BCM325x_OOB_DATA

P15

P16

P14

325xoob_clk

325xoob_syn

325xoob_data

BCM325x_US_CLK

N16

325xoob_ctx

mpodi_clk

mpodi_syn

mpodi_d0

mpodi_d1

B1002

ferrite_0603

RP503

51_4

9,11

9,11

18

C1005

10U_c

+3.3V

MHIF/ EP2C5/ EP2C8

dev_oe

TCK

clk27

TDO

MHIF_resetb MHIF Control / JTAG

TMS

MHIF_sclk

TDI

MHIF_sdi

MHIF_sdo

MHIF_sctrl

MHIF_int

MHIF_EP2C5_EP2C8

J2

N1

L2

N2

MHIF/ EP2C5/ EP2C8

Power, Clocks

VREFB3N0

VREFB3N1

TP1005

TP1003

11,15 MHIF_CLK27MHz

18 MHIF_RESET_N

18 MHIF_SCLK

18 MHIF_SDI

18 MHIF_SCTL_CFG_DATA

7038oob_clk

7038oob_syn

7038oob_dat

OOB Switch

325xoob_etx

325xoob_itx

325xoob_qtx

L4

L1

M3

L3

5

6

7

8

C1029

10U_c

4

3

2

1

Motorola Host Interface FPGA (MHIF)

Cable Card Interface

+3.3V

R1002

1K_s

+1.2V

7038_MPODI_CLK 18

7038_MPODI_SYNC

18

7038_MPODI_DATA0 18

7038_MPODI_DATA1 18

E3

E1

E2

MHIF_OOB_CLK 9

MHIF_OOB_SYNC

9

MHIF_OOB_DATA 9

M16

N15

M15

BCM325x_US_EN 6

BCM325x_US_I 6

BCM325x_US_Q 6

C1030

0_01U_s

C1031

0_1U_s

C1032

0_1U_s

B1003

ferrite_0603

VCCA_PLL1

2

C1033

10U_c

+1.2V

C1034

0_1U_s

TP1011

TP1015

TP1014

TP1017

TP1000

VCCA_PLL2

MHIF_EP2C5_EP2C8

C1036

10U_c

C1037

0_1U_s

TP1006

TP1004

N11

N8

TP1008

TP1009

B16

G14

K14

R16

VCCIO3

VCCIO3

VCCIO3

VCCIO3

GND

GND

GND

GND

B15

H14

J14

R15

M7

M10

P7

P10

T2

T15

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO4

GND

GND

GND

GND

GND

GND

M8

M9

P8

P9

T1

T16

GND_PLL1

GND_PLL1

GND_PLL2

GND_PLL2

GNDA_PLL1

GNDA_PLL2

N5

L5

D12

F12

M6

E11

PLL1_OUTn

PLL2_OUTp

PLL2_OUTn

M4

E14

D14

L6

F11

VCCD_PLL1

VCCD_PLL2

M5

E12

VCCA_PLL1

VCCA_PLL2

C2

H1

J1

H16

J15

J16

CLKUSR

CLK1

CLK3

CLK4

CLK6

CLK7

C1035

100P_s

B1000

ferrite_0603

VREFB4N0

VREFB4N1

H13

M14

C1038

100P_s

TP1012

TP1016

TP1018

MHIF_EP2C5_EP2C8

M-Mode Only

Please refer to the "Cyclone II Device Handbook, Volume

1" on Page 7-30 for the "Partitioned VCCA Island Within

the VCCINT Plane" layout guideline.

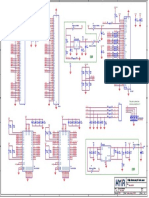

CRD_MDO[7:0]

J1001

M-Card Only

CRD_MDI[7:0]

U1001E

MHIF/ EP2C5/ EP2C8

18

18

18

CRD_MDO0

CRD_MDO1

CRD_MDO2

CRD_MDO3

CRD_MDO4

CRD_MDO5

CRD_MDO6

CRD_MDO7

CRD_MOCLK

A4

B3

A3

A14

B14

A13

B13

B12

H15

B5

cc_mdi[0]

cc_mdi[1]

cc_mdi[2]

cc_mdi[3]

cc_mdi[4]

cc_mdi[5]

cc_mdi[6]

cc_mdi[7]

cc_miclk

cc_mistrt

CRD_ITX

CRD_QTX

CRD_ETX

D11

B10

B11

cc_itx

cc_qtx

cc_etx

P4

P5

R4

C5

MPOD_SCLK

MPOD_SCTL

MPOD_SDO

mspi_clk

mspi_ctl

mspi_sdi

cc_sdi

Cable Card

(M-Card)

MSPI

MHIF_EP2C5_EP2C8

CRD_MISTRT

CRD_MDI0

CRD_MDI1

CRD_MDI2

CRD_MDI3

CRD_MDI4

CRD_MDI5

CRD_MDI6

CRD_MDI7

CRD_MDI0

A12

CRD_MDI1

A11

CRD_MDI2

A10

CRD_MDI3

A9

CRD_MDI4

A8

CRD_MDI5

A7

CRD_MDI6

A6

CRD_MDI7

A5

33_s

C12 R1020

C13

CRD_MICLK

CRD_MISTRT

cc_reset

cc_crx

cc_drx

cc_ctx

B7

D16

D15

D10

CRD_RESET

CRD_CRX

CRD_DRX

CRD_CTX

cc_sclk

cc_sctl

cc_sdo

mspi_sdo

C6

D6

B6

P3

cc_mdo[0]

cc_mdo[1]

cc_mdo[2]

cc_mdo[3]

cc_mdo[4]

cc_mdo[5]

cc_mdo[6]

cc_mdo[7]

cc_moclk

cc_mostrt

CRD_SCLK

CRD_SCTL

CRD_SDI

MPOD_SDI

CRD_MOSTRT

+3.3V

18

CRD_MDO0

CRD_MDO1

CRD_MDO2

CRD_MDO3

CRD_MDO4

CRD_MDO5

CRD_MDO6

CRD_MDO7

R1011

10K_s

CRD_SDO

B

20

19

46

47

48

49

50

53

54

55

56

NC

NC

MISTRT

MDI0

MDI1

MDI2

MDI3

MDI4

MDI5

MDI6

MDI7

14

62

63

64

65

66

37

38

39

40

41

NC

NC

MOSTRT

MDO0

MDO1

MDO2

MDO3

MDO4

MDO5

MDO6

MDO7

61

7

42

9

15

44

45

60

16

NC

NC

NC

NC

NC

NC

NC

SDO

NC

68

35

34

1

69

70

GND

GND

GND

GND

BRACKET1

BRACKET2

NC

NC

NC

NC

NC

NC

NC

NC

30

31

32

2

3

4

5

6

SDI

SCLK

SCTL

NC

CTX

ITX

ETX

QTX

CRX

DRX

NC

NC

MICLK

MOCLK

29

28

27

26

25

24

23

22

12

11

8

10

21

13

CD1#

CD2#

VS1#

VS2#

NC

MDET

VPP2

VPP1

36

67

43

57

59

33

52

18

RESET

58

VCC

VCC

BRACKET3

BRACKET4

51

17

71

72

U1001F

TP1019

TP1020

TP1026

TP1021

CRD_SDI

CRD_SCLK

CRD_SCTL

CRD_CTX

CRD_ITX

CRD_ETX

CRD_QTX

CRD_CRX

CRD_DRX

TP1028

TP1029

+3.3V

+3.3V

R1014

100K_s

CRD_MICLK

R1021

33_s

R1018

10K_s

R1019

10K_s

R1022

10K_s

R1023

10K_s

TP1031

TP1030

CRD_MOCLK

CRD_CD1_N

18

CRD_CD2_N

18

CRD_VS1_N 18

CRD_VS2_N 18

CRD_MDET

TP1032

TP1033

18

CRD_VPP1

TP1035

TP1037

CRD_RESET

C1001

0_1U_s

CRD_VCC

+3.3V

+3.3V

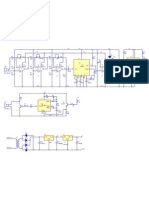

U1001C

MHIF_EP2C5_EP2C8

C1039

4_7U_s

Samtec_FSI_I40_L_D_M_AD_K_TR

C1040

0_1U_s

CRD_VCC

R1015

4_7K_s

+5VD

F16

C1046

1000P_s

CRD_VPP2

C1002

0_1U_s

CRD_VCC

R1025

200_s

C1003

0_01U_s

Place caps

close to J1001

pins 51

[070524_update] R1025 is the R_200 to replace C1047

DMR052: C1047 change from C_1000P to R_200, but now

only change P\N number (520520-057-18).

C1048

1000P_s

C1045

1U_s

AVCC

AVCC

AVPP

17

18

19

BVCC

BVCC

BVPP

7

16

20

22

23

6

NC

NC

NC

NC

NC

NC

pwr_alrmb

cc_vpp1

D13

pwr_lat

pwr_clk

pwr_dat

pwr_shdnb

E16

G16

F15

G15

+3.3V

3.3V_In

3.3V_In

13

14

5V_In

5V_In

5V_In

1

2

24

4_7U_c

/SHDN

/RESET

DATA

CLOCK

LATCH

21

12

3

4

5

CRD_PWR_SHDN_N

/OC

15

CRD_OC_IRE_N

GND

11

C1041

CRD_VCC_DATA

CRD_VCC_CLK

CRD_VCC_LATCH

C1042

0_1U_s

R1016

4_7K_s

BCM7038_RESETB

IO10_D4

IO10_D5

IO10_E4

IO10_E5

IO11_K4

IO11_K5

IO11_M2

B9

F9

F10

G10

G11

B4

C4

E6

F6

F7

F8

G6

G7

IO20_B9

IO20_F9

IO20_F10

IO20_G10

IO20_G11

IO21_B4

IO21_C4

IO21_E6

IO21_F6

IO21_F7

IO21_F8

IO21_G6

IO21_G7

C14

G12

G13

H11

H12

J11

J12

K15

K16

L14

L15

L16

M12

N12

N13

N14

IO30_C14

IO30_G12

IO30_G13

IO30_H11

IO30_H12

IO30_J11

IO30_J12

IO31_K15

IO31_K16

IO31_L14

IO31_L15

IO31_L16

IO31_M12

IO31_N12

IO31_N13

IO31_N14

MHIF/ EP2C5/ EP2C8

D1

D2

G4

F5

H6

J6

VOID/NC/IO10_D1

VOID/NC/IO10_D2

VOID/NC/IO10_G4

VOID/NC/IO10_F5

VOID/NC/IO10_H6

VOID/NC/IO10_J6

N3

N4

VOID/NC/IO11_N3

VOID/NC/IO11_N4

D9

VOID/NC/IO20_D9

B8

D7

VOID/NC/IO21_B8

VOID/NC/IO21_D7

11,15

Unused IO's

IO40_K10

IO40_K11

IO40_L9

IO40_L10

IO40_L11

IO40_M11

IO40_N9

IO40_N10

IO40_P11

IO40_P12

IO40_P13

IO40_R10

IO40_R11

IO40_R12

IO40_R13

IO40_R14

IO40_T10

IO40_T11

IO40_T12

IO40_T13

IO40_T14

IO41_L7

IO41_L8

IO41_R5

IO41_R7

IO41_R8

IO41_R9

IO41_T7

IO41_T8

IO41_T9

IO41_T4

IO41_T6

IO41_T5

IO41_T3

VOID/NC/IO30_C15

VOID/NC/IO30_C16

VOID/NC/IO30_E13

VOID/NC/IO30_E15

VOID/NC/IO30_F13

VOID/NC/IO30_F14

VOID/NC/IO31_K13

VOID/IO40/IO31_L12

VOID Pins

VOID/NC/IO41_K6

VOID/NC/IO41_K7

VOID/NC/IO41_N6

VOID/NC/IO41_N7

VOID/NC/IO41_P6

VOID/NC/IO41_R6

K10

K11

L9

L10

L11

M11

N9

N10

P11

P12

P13

R10

R11

R12

R13

R14

T10

T11

T12

T13

T14

TP1024

TP1023

L7

L8

R5

R7

R8

R9

T7

T8

T9

T4

T6

T5

T3

TP1041

TP1043

C15

C16

E13

E15

F13

F14

K13

L12

K6

K7

N6

N7

P6

R6

MHIF_EP2C5_EP2C8

25

C1043

0_01U_s

Place caps

close to J1001

pins 17

9

10

8

GND_PWP

U1004

TPS2223APWP

CRD_VCC

AVPP is implemented

in FPGA as

CRD_VPP1.

Power

Control

D4

D5

E4

E5

K4

K5

M2

pin 25 = PowerPAD heat slug

MOTOROLA CONFIDENTIAL PROPRIETARY (Level 3)

Title

16: CableCARD_FPGA

Name

533385-001-C.DSN

Size

Document Number

533385-001

D

Date:

5

Thursday, September 20, 2007

1

Rev

C

Sheet

16

of

18

You might also like

- BT 812 KPFDocument4 pagesBT 812 KPFMiloud ChouguiNo ratings yet

- Daewoo Hy338-0265-09c DVD Power-Supply SCHDocument3 pagesDaewoo Hy338-0265-09c DVD Power-Supply SCHBetoRodalfNo ratings yet

- 300w SchematicDocument1 page300w Schematicr96221029No ratings yet

- SPWM Driver Circuit SchematicDocument1 pageSPWM Driver Circuit Schematicbnn123No ratings yet

- Compact title for circuit diagram documentDocument3 pagesCompact title for circuit diagram documentAdrian PeterNo ratings yet

- Roadrunner 2 0 SCHDocument1 pageRoadrunner 2 0 SCHLam Duy TienNo ratings yet

- R5, R11 and R6, R12 For Currentr 2,5A KD (R5+R6) /R6 Ud VCC/KD (VCC 5V)Document1 pageR5, R11 and R6, R12 For Currentr 2,5A KD (R5+R6) /R6 Ud VCC/KD (VCC 5V)sporttech2100% (1)

- Top-Level Diagram: SHEET 13-18Document21 pagesTop-Level Diagram: SHEET 13-18Aref MGHNo ratings yet

- GT S5360Document51 pagesGT S5360radiobrunoNo ratings yet

- DOP7Document2 pagesDOP7Nghia Do100% (1)

- Jtronics Atmega328 GRBL Controller SchematicDocument1 pageJtronics Atmega328 GRBL Controller SchematicanhxcoNo ratings yet

- L289N ModuleDocument1 pageL289N ModuleHùng NguyenNo ratings yet

- Conector Tipo B: Rxleda# TCK TDI TDO TMS NTRST RTCK RST DBGRQ Dbgack Acbus1Document2 pagesConector Tipo B: Rxleda# TCK TDI TDO TMS NTRST RTCK RST DBGRQ Dbgack Acbus1juenkkinNo ratings yet

- Computer-Generated Circuit DiagramDocument1 pageComputer-Generated Circuit Diagramatomo33No ratings yet

- Ultra Low Power Wireless Transmitter and Receiver CircuitDocument1 pageUltra Low Power Wireless Transmitter and Receiver CircuitNaman TamrakarNo ratings yet

- RTD2280DLW PCB design documentDocument5 pagesRTD2280DLW PCB design documentpasmanteriabellaNo ratings yet

- IRswitchDocument1 pageIRswitchAbhijit PattnaikNo ratings yet

- Rane Ac 22b Circa 2003 Active Crossover SchematicDocument3 pagesRane Ac 22b Circa 2003 Active Crossover SchematicRoby Adi WibowoNo ratings yet

- R13 VCC5V 220 D2 A K LED-BLUE_DACDocument1 pageR13 VCC5V 220 D2 A K LED-BLUE_DACJuan Galarza100% (1)

- Step Motor DriveDocument1 pageStep Motor DriveCesar QuinterosNo ratings yet

- TLH19Document16 pagesTLH19Christopher ScottNo ratings yet

- BEE Shield SchematicDocument1 pageBEE Shield Schematicđiện tử điều khiểnNo ratings yet

- ADV Main SchematicDocument1 pageADV Main Schematicgerardobrandao100% (1)

- Ti Tas5630 EvmDocument1 pageTi Tas5630 EvmTrenton Astley IslaNo ratings yet

- Evens C-500S: TitleDocument1 pageEvens C-500S: TitleLeosonido Reyes100% (1)

- 1Document1 page1Ulul AzmiNo ratings yet

- SDR BPFDocument2 pagesSDR BPFRavindran KodakkattilNo ratings yet

- 6012 SchematicsDocument24 pages6012 SchematicsDexter DanielNo ratings yet

- 500w Pro Audio-SchemaDocument1 page500w Pro Audio-SchemausernamescuNo ratings yet

- ®MCI Electronics WWW - Olimex.cl: 3V3 3V3 RssiDocument1 page®MCI Electronics WWW - Olimex.cl: 3V3 3V3 Rssiefx8100% (1)

- Samsung GT-C3322 Metro Duos SchematicsDocument3 pagesSamsung GT-C3322 Metro Duos SchematicsTerry MetamorfosaNo ratings yet

- Samsung Galaxy S2 SchematicDocument9 pagesSamsung Galaxy S2 SchematicJavier VallenillaNo ratings yet

- 17ips61-3 V1Document2 pages17ips61-3 V1BoKi PoKiNo ratings yet

- Schematic - Pic ModuleDocument1 pageSchematic - Pic ModuleDuc Le100% (1)

- LCD GraphicDocument1 pageLCD GraphicnhanbachkhoalyNo ratings yet

- RS2653 Main Schematic (1-4 of 4Document5 pagesRS2653 Main Schematic (1-4 of 4Hugo Ernesto Garcia NuñezNo ratings yet

- My Lcd70tp Myir 7 Inch LCD SchematicsDocument1 pageMy Lcd70tp Myir 7 Inch LCD SchematicsMilruwan PereraNo ratings yet

- Art 300 ADocument7 pagesArt 300 AhashashashasNo ratings yet

- Reflow Toaster v2 SchematicDocument1 pageReflow Toaster v2 SchematicBest PC BoxNo ratings yet

- IO Door Board SchematicDocument2 pagesIO Door Board Schematicvilla1960No ratings yet

- Marcas Varias DVD Con Procesador Zoran Manual de ServicioDocument44 pagesMarcas Varias DVD Con Procesador Zoran Manual de ServicioVicente MalvicaNo ratings yet

- Vin IC2Document1 pageVin IC2Harish Kumar MNo ratings yet

- Camera module with OV7670 and AL422B FIFODocument1 pageCamera module with OV7670 and AL422B FIFOMuhammad Alfiansyah100% (3)

- Charger SchematicDocument2 pagesCharger SchematicYori Hadi PutraNo ratings yet

- Mp3 Decoder GPD2846 - DatasheetDocument1 pageMp3 Decoder GPD2846 - DatasheetSveto SlNo ratings yet

- G5 SchematicDocument1 pageG5 Schematicjkifnoin100% (1)

- Heart Rate DisplayDocument1 pageHeart Rate DisplayGopikrishna EmbadiNo ratings yet

- Conversor RS232 RS485Document1 pageConversor RS232 RS485Feyyaz Kurt100% (2)

- LPC Xpresso SchematicDocument5 pagesLPC Xpresso SchematicHội Ngô VănNo ratings yet

- Schematic Multi-Input Module WM8805Document3 pagesSchematic Multi-Input Module WM8805aleksa64No ratings yet

- Electronic Circuit Design Ideas: Edn Series for Design EngineersFrom EverandElectronic Circuit Design Ideas: Edn Series for Design EngineersRating: 5 out of 5 stars5/5 (2)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- 110 Semiconductor Projects for the Home ConstructorFrom Everand110 Semiconductor Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- VIP 32 Hybrid VentDocument8 pagesVIP 32 Hybrid VentsagarNo ratings yet

- Cengage Eco Dev Chapter 13 - The Environment and Sustainable Development in AsiaDocument32 pagesCengage Eco Dev Chapter 13 - The Environment and Sustainable Development in AsiaArcy LeeNo ratings yet

- BC Sample Paper-3Document4 pagesBC Sample Paper-3Roshini ANo ratings yet

- TM T70 BrochureDocument2 pagesTM T70 BrochureNikhil GuptaNo ratings yet

- Factory Test Report For OPzS 800 EED-20041724 2VDocument3 pagesFactory Test Report For OPzS 800 EED-20041724 2VmaherNo ratings yet

- IT-02 Residential StatusDocument26 pagesIT-02 Residential StatusAkshat GoyalNo ratings yet

- Gfk-1383a 05012Document108 pagesGfk-1383a 05012occhityaNo ratings yet

- IEC61508 GuideDocument11 pagesIEC61508 Guidesrbehera1987No ratings yet

- Unit Rates and Cost Per ItemDocument213 pagesUnit Rates and Cost Per ItemDesiree Vera GrauelNo ratings yet

- Reprocessing Guide: Shaver Handpiece TrayDocument198 pagesReprocessing Guide: Shaver Handpiece TrayAnne Stephany ZambranoNo ratings yet

- 2023 Catalog Score SummerDocument65 pages2023 Catalog Score Summermadhudasa0% (2)

- ArchimedesDocument22 pagesArchimedessharfexNo ratings yet

- Mycophenolic Acid Chapter-1Document34 pagesMycophenolic Acid Chapter-1NabilaNo ratings yet

- Deutsche BankDocument4 pagesDeutsche BankMukesh KumarNo ratings yet

- Introduction to Globalization ExplainedDocument27 pagesIntroduction to Globalization ExplainedMichael Ron DimaanoNo ratings yet

- The Beggar's Opera by Gay, John, 1685-1732Document50 pagesThe Beggar's Opera by Gay, John, 1685-1732Gutenberg.orgNo ratings yet

- Bài Tập Phần Project ManagementDocument11 pagesBài Tập Phần Project ManagementhunfgNo ratings yet

- Construction Materials and Testing: "WOOD"Document31 pagesConstruction Materials and Testing: "WOOD"Aira Joy AnyayahanNo ratings yet

- ECE SAR OldDocument168 pagesECE SAR OldNagaraja RaoNo ratings yet

- Finding The Answers To The Research Questions (Qualitative) : Quarter 4 - Module 5Document39 pagesFinding The Answers To The Research Questions (Qualitative) : Quarter 4 - Module 5Jernel Raymundo80% (5)

- Sem Iii Sybcom Finacc Mang AccDocument6 pagesSem Iii Sybcom Finacc Mang AccKishori KumariNo ratings yet

- School of Education, Arts and Sciences General Education Area 1 SEMESTER S.Y 2021-2022Document4 pagesSchool of Education, Arts and Sciences General Education Area 1 SEMESTER S.Y 2021-2022JaylordPalattaoNo ratings yet

- An Introduction To Log ShootingDocument10 pagesAn Introduction To Log ShootingSorin GociuNo ratings yet

- Community HelpersDocument3 pagesCommunity Helpersapi-252790280100% (1)

- Format of Synopsis - Project - 1Document5 pagesFormat of Synopsis - Project - 1euforia hubNo ratings yet

- Consumer Behavior PP Chapter 4Document36 pagesConsumer Behavior PP Chapter 4tuongvyvyNo ratings yet

- Assessmentof Safety Cultureand Maturityin Mining Environments Caseof Njuli QuarryDocument12 pagesAssessmentof Safety Cultureand Maturityin Mining Environments Caseof Njuli QuarryAbdurrohman AabNo ratings yet

- Ncm110nif Midterm Laboratory NotesDocument12 pagesNcm110nif Midterm Laboratory NotesMicah jay MalvasNo ratings yet

- ASIA IVALUE Business ProfileDocument9 pagesASIA IVALUE Business ProfileDidiek PriambudiNo ratings yet

- Andromeda Council About The 4th DimensionDocument11 pagesAndromeda Council About The 4th DimensionWonderlust100% (1)