Professional Documents

Culture Documents

N. The Least Significant Bit of The Multiplier Register (Q0)

N. The Least Significant Bit of The Multiplier Register (Q0)

Uploaded by

rajesh_r4500 ratings0% found this document useful (0 votes)

3 views1 pageA multiplier is a key component in digital systems that performs multiplication. Researchers are trying to design multipliers that offer high speed, low power consumption, regular layout to reduce area, or combinations of these traits. One such multiplier is the shift-and-add multiplier, which obtains the product by shifting and adding the multiplicand to the product register based on the least significant bit of the multiplier. It initializes registers for the multiplicand, multiplier, and product, then shifts the multiplicand left and adds it to the product if the least significant bit of the multiplier is 1. This process repeats until the full product is calculated.

Original Description:

Abstract

Original Title

Abstract

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentA multiplier is a key component in digital systems that performs multiplication. Researchers are trying to design multipliers that offer high speed, low power consumption, regular layout to reduce area, or combinations of these traits. One such multiplier is the shift-and-add multiplier, which obtains the product by shifting and adding the multiplicand to the product register based on the least significant bit of the multiplier. It initializes registers for the multiplicand, multiplier, and product, then shifts the multiplicand left and adds it to the product if the least significant bit of the multiplier is 1. This process repeats until the full product is calculated.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

3 views1 pageN. The Least Significant Bit of The Multiplier Register (Q0)

N. The Least Significant Bit of The Multiplier Register (Q0)

Uploaded by

rajesh_r450A multiplier is a key component in digital systems that performs multiplication. Researchers are trying to design multipliers that offer high speed, low power consumption, regular layout to reduce area, or combinations of these traits. One such multiplier is the shift-and-add multiplier, which obtains the product by shifting and adding the multiplicand to the product register based on the least significant bit of the multiplier. It initializes registers for the multiplicand, multiplier, and product, then shifts the multiplicand left and adds it to the product if the least significant bit of the multiplier is 1. This process repeats until the full product is calculated.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 1

ABSTRACT

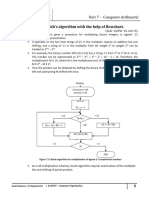

A multiplier is one of the key hardware blocks in most

digital and high performance systems such as FIR filters,

digital signal processors and microprocessors etc. With

advances in technology, many researchers have tried and are

trying to design multipliers which offer either of the

following- high speed, low power consumption, regularity of

layout and hence less area or even combination of them is

multiplier. Thus making them suitable for various high speed,

low power and compact VLSI implementations. The shift and

add multiplier obtains product by shifting and adding

multiplicand to the product based upon the LSB of multiplier.

The shift-and-add multiplication method for two n-bit

numbers. The 2n-bit product register (A) is initialized to 0.

Since the basic algorithm shifts the multiplicand register (B)

left one position each step to align the multiplicand with the

sum being accumulated in the product register, we use a 2n-

bit multiplicand register with the multiplicand placed in the

right half of the register and with 0 in the left half. The

algorithm starts by loading the multiplicand into the B

register, loading the multiplier into the Q register, and

initializing the A register to 0. The counter N is initialized to

n. The least significant bit of the multiplier register (Q0)

determines whether the multiplicand is added to the product

register. The left shift of the multiplicand has the effect of

shifting the intermediate products to the left and LSB of

product is verified. Depending upon LSB value it is decided

whether to add and shift or just shift. This process is

continued to obtain product of the numbers.

You might also like

- Practical-1 AIM: Implement Register Transfer Operation in Logisim SimulatorDocument23 pagesPractical-1 AIM: Implement Register Transfer Operation in Logisim SimulatorDigvijay Sinh ChauhanNo ratings yet

- Cao AnswersDocument10 pagesCao AnswersSri Vishnu RamNo ratings yet

- Synopsys Booth MultiplierDocument6 pagesSynopsys Booth Multiplierbipin123456789No ratings yet

- Unit-3 PPT CoDocument24 pagesUnit-3 PPT CobrsreddyNo ratings yet

- CH-2.Multiplication AlgorithmDocument11 pagesCH-2.Multiplication AlgorithmDevanshi GudsariyaNo ratings yet

- Vlsi CKTSDocument17 pagesVlsi CKTSMoin PashaNo ratings yet

- Module-2 - Lecture 2: Alu - Signed Addition/SubtractionDocument44 pagesModule-2 - Lecture 2: Alu - Signed Addition/SubtractionWINORLOSENo ratings yet

- Study of Combinational and Booth Multiplier: Neha Goyal, Khushboo Gupta, Renu SinglaDocument4 pagesStudy of Combinational and Booth Multiplier: Neha Goyal, Khushboo Gupta, Renu SinglajdNo ratings yet

- Unit - 3 of Computer ArchitectureDocument59 pagesUnit - 3 of Computer ArchitectureShweta mauryaNo ratings yet

- Computer Arithmetic-1Document46 pagesComputer Arithmetic-1Bam NoiceNo ratings yet

- Implementation of Booth Multiplier and Modified Booth MultiplierDocument8 pagesImplementation of Booth Multiplier and Modified Booth Multiplierlokesh kadagalaNo ratings yet

- Listening To Booths Algorithm Using Rust and OrcaDocument17 pagesListening To Booths Algorithm Using Rust and OrcaMuhammad Areeb KazmiNo ratings yet

- Design and Implementation of 256 256 Booth Multiplier and Its ApplicationsDocument4 pagesDesign and Implementation of 256 256 Booth Multiplier and Its ApplicationssurbhiNo ratings yet

- Unit - 5 Computer Arithmetic: 5.1 Addition and SubtractionDocument16 pagesUnit - 5 Computer Arithmetic: 5.1 Addition and SubtractionKeshav NaganathanNo ratings yet

- Chapter 10 Morris ManoDocument15 pagesChapter 10 Morris ManoRaj MitulNo ratings yet

- ASM Design Example Bin MultDocument11 pagesASM Design Example Bin MultMudumby KulashekarNo ratings yet

- COA Module 3 UpdatedDocument93 pagesCOA Module 3 UpdatedB G JEEVANNo ratings yet

- Radix-4 and Radix-8 Multiplier Using Verilog HDLDocument6 pagesRadix-4 and Radix-8 Multiplier Using Verilog HDLIJARTETNo ratings yet

- ECE222 DP1 Binary MultiplierDocument8 pagesECE222 DP1 Binary Multiplierprasad357No ratings yet

- COMP NotesDocument32 pagesCOMP NotessreelayaNo ratings yet

- Computer Organization and Architecture: Shaik Suhil Irshad 18BEC2007 C1 + TC1Document17 pagesComputer Organization and Architecture: Shaik Suhil Irshad 18BEC2007 C1 + TC1Suhil IrshadNo ratings yet

- Design of Low Power Approximate Radix 8 Booth Multiplier IJERTCONV5IS17004Document5 pagesDesign of Low Power Approximate Radix 8 Booth Multiplier IJERTCONV5IS17004ManojNo ratings yet

- Low Power VLSI Design of Modified Booth MultiplierDocument6 pagesLow Power VLSI Design of Modified Booth MultiplieridescitationNo ratings yet

- PaperID 74S201921Document7 pagesPaperID 74S201921Christopher crNo ratings yet

- 5EC3-01: Computer Architecture: UNIT-2Document17 pages5EC3-01: Computer Architecture: UNIT-2Himanshi SainiNo ratings yet

- Configruable Booth MultiplierDocument11 pagesConfigruable Booth MultiplierSyed HyderNo ratings yet

- Unit-2 Arithmetic Logic Unit (ALU)Document13 pagesUnit-2 Arithmetic Logic Unit (ALU)Shubham KumarNo ratings yet

- OrganisationsDocument10 pagesOrganisationsRaj MajiNo ratings yet

- Document 2 6mZM 06032016Document7 pagesDocument 2 6mZM 06032016Dai LewisNo ratings yet

- COA Lab ManualDocument13 pagesCOA Lab Manualsravanicharitha MamidiNo ratings yet

- Implementation of Modified Booth Algorithm (Radix 4) and Its Comparison With Booth Algorithm (Radix-2)Document18 pagesImplementation of Modified Booth Algorithm (Radix 4) and Its Comparison With Booth Algorithm (Radix-2)THIRUCHANOORU SREENATHNo ratings yet

- Imp, BLTDocument3 pagesImp, BLTNARENDRANo ratings yet

- N-Bit Parallel AddersubDocument8 pagesN-Bit Parallel Addersubvarshini yogarajanNo ratings yet

- Atmel-megaAVR-ATmega48-Learning Centre MCU-Application Notes-Atmel - Application - Notes - 30 PDFDocument4 pagesAtmel-megaAVR-ATmega48-Learning Centre MCU-Application Notes-Atmel - Application - Notes - 30 PDFMaPitufinaNo ratings yet

- ArchitectureDocument112 pagesArchitectureKrishnaveni DhulipalaNo ratings yet

- Module 2 NotesDocument28 pagesModule 2 NotesKrithika KNo ratings yet

- FPGA Implementation of IEEE-754 Karatsuba MultiplierDocument4 pagesFPGA Implementation of IEEE-754 Karatsuba MultiplierSatyaKesavNo ratings yet

- BoothsDocument2 pagesBoothsRajesh AdhikariNo ratings yet

- Thesis Phase 1 ReportDocument7 pagesThesis Phase 1 ReportDhanya Geethanjali SasidharanNo ratings yet

- Comparative Analysis of Multiplier in Quaternary Logic: Shweta Hajare, Dr.P.K.DakholeDocument6 pagesComparative Analysis of Multiplier in Quaternary Logic: Shweta Hajare, Dr.P.K.DakholeDivya MokaraNo ratings yet

- Project ReportDocument4 pagesProject ReportNaushad AlamNo ratings yet

- Computational Building Blocks of DSPDocument28 pagesComputational Building Blocks of DSPVasantha Chandrasekaran80% (5)

- Csa Unit IDocument15 pagesCsa Unit IumeshNo ratings yet

- CH 10Document5 pagesCH 10utkarsh.shrivastava.ug21No ratings yet

- Micro OperationsDocument15 pagesMicro OperationsRaju SinghNo ratings yet

- Radix-4 and Radix-8 Multiplier Using Verilog HDL: (Ijartet) Vol. 1, Issue 1, September 2014Document6 pagesRadix-4 and Radix-8 Multiplier Using Verilog HDL: (Ijartet) Vol. 1, Issue 1, September 2014RalucaJulaNo ratings yet

- CO UNIT-4 NotesDocument25 pagesCO UNIT-4 NotesAmber HeardNo ratings yet

- Implementation of ALU Using Modified Radix-4 Modified Booth MultiplierDocument15 pagesImplementation of ALU Using Modified Radix-4 Modified Booth MultiplierIJRASETPublicationsNo ratings yet

- Advanced Logic Circuits ProjectDocument13 pagesAdvanced Logic Circuits ProjectLymen LagumbayNo ratings yet

- 4 SaSrivastavndeepDocument3 pages4 SaSrivastavndeepAshok Siva Kumar PoojalaNo ratings yet

- Cao Class NotesDocument16 pagesCao Class NotesPavan KalyanNo ratings yet

- Architectures For Programmable Digital Signal Processing DevicesDocument24 pagesArchitectures For Programmable Digital Signal Processing DevicesShibani SanaNo ratings yet

- Approaches To Low-Power Implementations of DSP SystemsDocument22 pagesApproaches To Low-Power Implementations of DSP SystemsHarish KumarNo ratings yet

- Ijarece Vol 2 Issue 11 872 874Document3 pagesIjarece Vol 2 Issue 11 872 874hkakashi93No ratings yet

- Unit 02 - MicrooperationsDocument16 pagesUnit 02 - MicrooperationsBijay MishraNo ratings yet

- Vlsi Architecture of Parallel Multiplier - Accumulator BasedDocument8 pagesVlsi Architecture of Parallel Multiplier - Accumulator BasedganeshlavetiNo ratings yet

- MultiplicationDocument18 pagesMultiplicationApurv MauryaNo ratings yet

- 1.1 MotivationDocument95 pages1.1 MotivationVijayNo ratings yet

- Python Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibFrom EverandPython Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibNo ratings yet