Professional Documents

Culture Documents

Schematics Dell Vostro 1500

Schematics Dell Vostro 1500

Uploaded by

samiceriOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Schematics Dell Vostro 1500

Schematics Dell Vostro 1500

Uploaded by

samiceriCopyright:

Available Formats

A

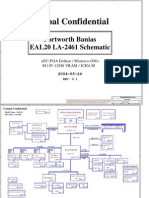

COMPAL CONFIDENTIAL

1

MODEL NAME : BDW00

COMPAL P/N : DA8DW00L110/DA8DW00L410

PCB NO : LA-1452

Revision : 1C

DATE :

Abacus/TangII Schematics Document

uFCBGA/uFCPGA Northwood

2003-02-24

3

REV: 1C

Dell-Compal Confidential

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D ate:

A

SCHEMATIC, M/B LA-1452

Document Number

R ev

1B

401230

P , 25, 2003

Sheet

E

of

47

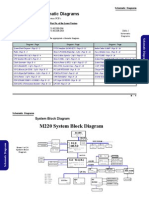

Block Diagram

Compal confidential

Model Name : ABACUS/TangII

File Name : LA-1452

CPU Bypass

& CPUVID

page 7,

Fan Control

page 7

+1.2VP

DT & Mobile Northwood

uFCBGA/uFCPGA CPU

+CPU_CORE

Thermal Sensor

+3VS

page 5,6

HA#( 3..31)

Clock Generator

ADM1032

ICS950810

+3VS

page 6

page 15

HD#(0..63)

System Bus

400/533 MHz

DT/BD-PE/ICH4/EXT VGA

DT/BD-GL/ICH4/INT VGA

INTEL

BROOKDALE-GL/PE

760 BGA

CRT Connector

page 17

INT. CRT

(PIRQE#,G_GNT#,G_REQ#) FOR EXT.

+1.5VS

EXT. CRT

+2.5V

AGP4X(1.5V)

AGP GRAPHIC/CHRONTEL

AGP Conn

LVDS Connector

TV OUT

DDR-DIMM X2

BANK 0, 1, 2, 3

+2.5V 200/266MHz

+2.5V

+1.25VS

page 12,13,14

+1.25VS

+CPU_CORE

page 9,10,11

page 16

Memory

BUS(DDR)

page 17

HUB LINK

+1.5VS

66MHz

IDSEL:AD18

(PIRQC#D#,GNT#1,REQ#1)

Minipci CONN

WIRELESS

+3VALW

+3V

+3VS

page 26

IDSEL:AD17

(PIRQB#,GNT#0,REQ#0)

page 22

+1.5VALW

+CPU_CORE

24.576MHz

+3V

page 23,24,25

Card Bus

SLOT

page 24

AC-LINK

page 18,19,20

MDC

+3VALW

+3V page 29

LPC BUS

+3VS

33MHz

1394

IDE

CD-ROM

IDE HDD

CONN

+5VALW

page 21

page 23

NS EC87591L

Embedded

Controller

845PE / PCI4510

845GL / PCI1510

+3VS

+3VALW

+5VS page 21

SIDE IRQ15

Cable

AC97 Codec

STAC9750

page 27

page 30

+5VALW page 28

Touch Pad

Int.KBD

LED Status

LID Switch

+5VS

+5VALW

+3VALW

4

page

34,35,36,37,38,39,40

DC/DC Interface

Suspend

Power On/Off

Reset & RTC

page 33

page 32

page 29

RJ11

+5VDDA

PIDE IRQ14

AMP & INT.

Speaker

Power Circuit

DC/DC

page 32

ATA100

VCC5REF

VCC5REFSUS

+3VALW

+5VALW

PCI4510/PCI1510

page 22

RJ45

+1.5VS

2 USB Ports

48MHz

INTEL

ICH4

421 BGA

+3VALW

IDSEL:AD20

(PIRQA#,GNT#2,REQ#2)

CardBus

& 1394

LAN

BCM-4401L

+3VS

+3VALW

+3VS

PCI BUS

+3VS 33MHz

BIOS

+3VALW

HeadPhone

& MIC Jack

+5VDDA

page 28

page 31

page 31

4

EC I/O Buffer

+5VALW

EC DEBUG

page 31

+3VALW

page 30

Dell-Compal Confidential

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

A

SCHEMATIC, M/B LA-1452

Document Number

R ev

1B

401230

, 25, 2003

Sheet

E

of

47

Schematics Rev

PCB Rev

0.1

0.1

0.2

0.2

CHIPS Rev

+3VS

Signal

845PE Rev B0

845GL Rev B1

ICH4 Rev B0

PT-Build

Power Managment table

Revision List

SST-Build

State

+3VALW

+3V

+5VALW

+5V

+12VALW

+2.5V

+5VS

+1.5VS

+1.2VP

D

+CPU_CORE

+1.25VS

ST-Build

S0

ON

ON

ON

S1

ON

ON

ON

S3

ON

ON

OFF

S5 S4/AC

ON

OFF

OFF

S5 S4/AC don't exist

OFF

OFF

OFF

QT-Build

Ceramic Capacitor Spec Guide:

C

Temperature Characteristics:

Symbol

CODE

Z5U

Z5V

Z5P

Y5U

Y5V

NP0

C0G

H

UJ

BJ

CH

5

Y5P

X5R

X7R

CJ

CK

SH

SJ

UK

SL

Tolerance:

Symbol

B

CODE

K

+-10%

+-0.05PF +-0.1PF +-0.25PF +-0.5PF

M

+-20%

+-30%

+-1PF

+-2%

H

+-3%

J

B

+-5%

+100,-0% +30,-10% +20,-10% +40,-20% +80,-20%

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

NS 87591

SMB_EC_CK2

SMB_EC_DA2

NS 87591

SMB_CLK

SMB_DATA

ICH4

INVERTER

BATT

SERIAL

EEPROM

THERMAL THERMAL

SENSOR

SENSOR

SODIMM

(CPU)

(U57)

(U25/U23)

NOTE1:

CLK CHIP

MINI PCI

@XX :

Depop component

1@XX : Pop for INT, Depop for EXT

(1010)

2@XX : Pop for EXT, Depop for INT

Dell-Compal Confidential

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D ate:

5

Compal Electronics, Inc.

SCHEMATIC, M/B LA-1452

Document Number

R ev

1B

401230

P , 25, 2003

Sheet

1

of

47

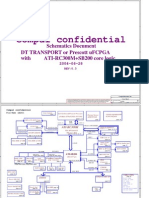

PQ26

+1.5VALW

SUSP#

SHDN#

+5VS

SUSP#

+5VALW

+1.5VS

page 35

page 35

page 31

SIDEPWR

+5VSHDD

page 21

SUSP#

MAX1632

+5VDDA

page 25

page 36

SYSON

+3VALW

+3V

page 31

VR_ON#

page 34

SUSP#

AC

+3VS

page 31

B+

CM2843

+12VALW

Battery

+1.2V

page 38

VR_ON#

page 34

+5VS

Mobile

+3VS

ISL6215

DT

+CPU_CORE

+1.5VS

VGA Conn.

180 pin

+2.5V

+3V

page 38

ISL6219

+5VALW

(Either one by CPU)

+12VALW

B+

SUSP#

A

SYSON

page 16

+1.25VS

ISL6225

+2.5V

page 36

Dell-Compal Confidential

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

5

SCHEMATIC, M/B LA-1452

Document Number

R ev

1B

401230

, 25, 2003

Sheet

1

of

47

<9> H_REQ#[0..4]

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

J1

K5

J4

J3

H3

G1

H _REQ#[0..4]

H_ADS#

5

+CPU_CORE

<9>

<9>

<9>

<9>

K2

K4

L6

K1

L3

M6

L2

M3

M4

N1

M1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

W1

T5

U4

V3

W2

Y1

AB1

H_BREQ0#

H_BPRI#

H_BNR#

H_LOCK#

<15> CLK_CPU_BCLK

<15> CLK_CPU_BCLK#

For Mobile

R284

1

@4.7K_0402_5%

2

2

R301

1

200_0402_5%

CLK_CPU_BCLK

CLK_CPU_BCLK#

AC1

V5

AA3

AC3

H6

D2

G2

G4

AF22

AF23

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

ADS#

AP#0

AP#1

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

CPU CORE

DT/Mobile

NorthWood

CONTROL SIGNAL

<9>

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HOST ADDRESS

U19A

HOST DATA

H A#[3..31]

BCLK0

BCLK1

GND

F3

E3

E2

H_HIT#

H_HITM#

H_DEFER#

CPU CORE

HIT#

HITM#

DEFER#

H1

H4

H23

H26

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

VSS_0

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

<9>

<9>

<9>

2

HD#[0..63]

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_80

VCC_79

VCC_78

VCC_77

VCC_76

VCC_75

VCC_74

HA#[3..31]

F13

F15

F17

F19

F9

F11

E8

E20

E18

E16

E14

E12

<9>

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

A10

A12

A14

A16

A18

A20

A8

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

B7

B9

C10

C12

C14

C16

C18

C20

C8

D11

D13

D15

D17

D19

D7

D9

E10

+CPU_CORE

B21

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

HD#[0..63] <9>

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

NorthWood

7

+CPU_CORE

Dell-Compal Confidential

8

Title

Compal Electronics, Inc.

SCHEMATIC, M/B LA-1452

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

Document Number

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

401230

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Custom

, 25, 2003

Date:

R ev

1B

Sheet

of

47

D

2

R267

H_SKTOCC#

1

@33_0402_5%

+CPU_CORE

2

R288

1

300_0402_5%

H_PWRGD

<9>

<9>

<15>

H_THERMDA

H_THERMDC

+CPU_CORE

Place resistor <100mils from

CPU pin

<8>

<8>

ITP_PRDY#

ITP_PREQ#

R207

0_0603_5%

<8>

<8>

<8>

<8>

<8>

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

2

L24

1

L25

1

LQG21F4R7N00_0805

H_VCCA

2

LQG21F4R7N00_0805

1

H_VCCIOPLL

2

TP2

1

1

1

Murata LQG21F4R7N00

C321

C305

C320

1U_0603_10V4Z

22U_1206_10V4Z

2

2

2

H_VSSA 22U_1206_10V4Z

RP61

CLK_CPU_ITTP

1

4

<15> CLK_CPU_ITP

CLK_CPU_ITTP#

2

3

<15> CLK_CPU_ITP#

5

RP62

1

2

CLK_ITP#

CLK_ITP

51.1_0603_1%

1 51_0402_5%

1 51_0402_5%

ITP_PREQ#

ITP_PRDY#

R262 2

R272 2

1 51_0402_5%

1 51_0402_5%

ITP_BPM0

ITP_BPM1

R268 2

R296 2

1 51_0402_5%

1 51_0402_5%

ITP_BPM2

ITP_BPM3

1

R313

1

R305

1

R314

2

@1.5K_0402_5%

2

@1.5K_0402_5%

2

680_0402_5%

ITP_TDI

NC7

NC8

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

PROCHOT#

MCERR#

SLP#

ITP_CLK0

ITP_CLK1

GND

R300

51.1_0603_1%

NC3

NC4

56_0402_5%

R293 1

R276 1

R294 1

2 56_0402_5%

2 56_0402_5%

2 56_0402_5%

H _GHI#

H_DSTBN#[0..3]

H_DSTBN#[0..3] <9>

H_DSTBP#[0..3]

H_DSTBP#[0..3] <9>

H_ADSTB#0 <9>

H_ADSTB#1 <9>

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

E21

G25

P26

V21

H_DBI#[0..3] <9>

2

1

@0_0402_5%

SYSRST# <19>

H_ITP_DBR# <8>

C3

V6

AB26

H_PROCHOT# 1

R311

H_SLP#

AD22

A4

H_VSSA

2

62_0402_5%

+3VS

<8,40>

<8,40>

<8,40>

<8,40>

<8,40>

+CPU_CORE

C317

0.1U_0402_16V4Z

R303

1K_0402_5%

49.9_0603_1%

<34,36> SHDN_1632#

VDD1

D-

ALERT#

SMB_EC_CK2

SCLK

SMB_EC_DA2

SDATA

R261

R_B

THERM#

GND

100_0603_1%

C319

1U_0603_10V4Z

3

47K_0402_5%

Q62

2N7002_SOT23

D+

2

Q64

MMBT3904_SOT23

C318

220P_0603_50V8J

Title

CPU Temperature Sensor

2 1

H_THERMTRIP#

Q59

MMBT3904_SOT23

Compal Electronics, Inc.

SCHEMATIC, M/B LA-1452

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

Document Number

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

401230

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Custom

, 25, 2003

Date:

R320

470_0402_5%

Dell-Compal Confidential

ADM1032ARM_RM8

H_PROCHOT# <37>

R316

Trace width>=7mil

H_PROCHOT#

1. Place R_A and R_B near CPU (Within 1.5").

2. Place decoupling cap 220PF near CPU.(Within

50 0mils)

2

H_THERMDC

2

Q26

MMBT3904_SOT23

<10,16,18,22,23,25,26,30,33> PCIRST#

Layout note :

+H_GTLREF1

U57

2

R_A

VL

1

R337

@10K_0402_5%

C174

0.1U_0402_16V4Z

8.2K_0402_5%

C470

2200P_0603_50V7K

R265

+CPU_CORE

R307

470_0402_5%

<19,31> PROCHOT#

+5VS

R333

<18>

AD2

AD3

GTL Reference Voltage

R334

+CPU_CORE

H_SLP#

ITP_TMS

H_THERMDA

R266

H_DBR#

AE25

56_0402_5%

NorthWood

CPU_VID4

CPU_VID3

CPU_VID2

CPU_VID1

CPU_VID0

ITP_TRST#

Width 10mil , Spacing 10mil

TP1

8.2K_0402_5%

<8,30> SMB_EC_DA2

+1.2VP

+5VS

<8,30> SMB_EC_CK2

VSSA

VSSSENSE

COMP0

COMP1

If used ITP port must depop

L5

R5

ITPCLKOUT0

ITPCLKOUT1

TESTTHI8_10

R278 2

R291 2

0_4P2R_0402_5%

+CPU_CORE

ADSTB#0

ADSTB#1

H_D BI#[0..3]

AF25

AF3

R302

4

3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

<8>

<8>

F21

J23

P23

W23

TCK

TDI

TDO

TMS

TRST#

VCCA

VCCSENSE

VCCIOPLL

L24

P1

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

NorthWood

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

AD20

A5

AE23

AC26

AD26

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

THERMTRIP#

@0_4P2R_0402_5%

D4

C1

D5

F7

E6

E22

K22

R22

W22

R275

For

Mobile

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

1

R285

TESTTHI2_7

2

G

@0_0603_5%

A2

ITP_BPM0 AC6

ITP_BPM1 AB5

ITP_BPM2 AC4

ITP_BPM3

Y6

ITP_PRDY# AA5

ITP_PREQ# AB4

1

R206

<19> H_THERMTRIP#

<8>

ITP_BPM0

<8>

ITP_BPM1

+CPU_CORE

+1.2VP

H_THERMTRIP#

2

62_0402_5%

1

R315

DT/Mobile

THERMDA

THERMDC

1

51.1_0603_1%

DBSY#

DRDY#

BSEL0

BSEL1

2

R279

B3

C4

H_RESET#

H5

H2

AD6

AD5

H_DBSY#

H_DRDY#

H_BSEL0

TESTTHI0_1

H_DPSLPR#

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

1

200_0402_5%

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

ITPCLKOUT0

ITPCLKOUT1

TESTHI8

TESTHI9

TESTHI10

GHI#

+CPU_CORE

2

R271

+H_GTLREF1

AA21

AA6

F20

F6

A22

A7

VCCVID

<18>

H_INTR

<18>

H_NMI

<18>

H_INIT#

<8,9> H_RESET#

J26

K25

K26

L25

GTLREF0

GTLREF1

GTLREF2

GTLREF3

NC1

NC2

AF4

@0_0402_5%

2

1

NC5

NC6

H_DPSLP#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

DPSLP#

LINT0

LINT1

INIT#

RESET#

AE21

AF24

R269

<18>

H_A20M#

C6

H_FERR#

B6

H_IGNNE#

B2

H_SMI#

B5

H_PWRGD AB23

H_STPCLK#

Y4

H_DPSLPR# AD25

H_INTR

D1

H_NMI

E5

H_INIT#

W5

H_RESET# AB25

<18>

H_A20M#

<18>

H_FERR#

<18> H_IGNNE#

<18>

H_SMI#

<18> H_PWRGD

<18> H_STPCLK#

+CPU_CORE

PM_CPUPERF# <19>

For Mobile

DP#0

DP#1

DP#2

DP#3

GND

VID0

VID1

VID2

VID3

VID4

H_TRDY#

RS#0

RS#1

RS#2

RSP#

TRDY#

AE5

AE4

AE3

AE2

AE1

For

Mobile

<9>

F1

G5

F4

AB2

J6

F8

G21

G24

G3

G6

J2

J22

J25

J5

K21

K24

K3

K6

L1

L23

L26

L4

M2

M22

M25

M5

N21

N24

N3

N6

P2

P22

P25

P5

R1

R23

R26

R4

T21

T24

T3

T6

U2

U22

U25

U5

V1

V23

V26

V4

W21

W24

W3

W6

Y2

Y22

Y25

Y5

H_BSEL0

2

1.5K_0402_5%

1

R19

H_RS#0

H_RS#1

H_RS#2

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

+3VS

<9>

<9>

<9>

2

56_0402_5%

2 PM_CPUPERF#

@0_0402_5%

1

R317

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

SKTOCC#

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

U19B

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF26

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

B4

B8

C11

C13

C15

C17

C19

C2

C22

C25

C5

C7

C9

D10

D12

D14

D16

D18

D20

D21

D24

D3

D6

D8

E1

E11

E13

E15

E17

E19

E23

E26

E4

E7

E9

F10

F12

F14

F16

F18

F2

F22

F25

F5

1

R318

H _GHI#

R ev

1B

Sheet

of

47

Layout note :

+CPU_CORE

Layout note :

Place close t o CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

Place close to CPU power and

gr ound pin as possible

(<1inch)

For Desktop's CPU:

C407

10U_1206_6.3V7K

1

C391

10U_1206_6.3V7K

1

C63

10U_1206_6.3V7K

1

C65

10U_1206_6.3V7K

C412

10U_1206_6.3V7K

C376

10U_1206_6.3V7K

1

C290

10U_1206_6.3V7K

C294

10U_1206_6.3V7K

C406

10U_1206_6.3V7K

1

C400

10U_1206_6.3V7K

C266

330U_D_2.5VM

2

PLACE ON CPU SIDE

0.22U_0603_10V7K

1

C111

2

0.22U_0603_10V7K

1

C258

10U_1206_6.3V7K

C262

330U_D_2.5VM

C113

C117

2

0.22U_0603_10V7K

0.22U_0603_10V7K

1

C119

C120

2

0.22U_0603_10V7K

0.22U_0603_10V7K

1

C110

C112

2

0.22U_0603_10V7K

0.22U_0603_10V7K

1

C116

C118

2

0.22U_0603_10V7K

C293

10U_1206_6.3V7K

+12VALW

3

1

C408

10U_1206_6.3V7K

C265

330U_D_2.5VM

2

0.22U_0603_10V7K

1

C104

C150

@470U_D4_2.5VM

2

+

C152

@330U_D2E_2.5VM

2

1

+CPU_CORE

C388

10U_1206_6.3V7K

C149

470U_D4_2.5VM

2

+CPU_CORE

C151

330U_D_2.5VM

1

C282

10U_1206_6.3V7K

C148

@470U_D4_2.5VM

+CPU_CORE

Please place these cap on the socket north side

C263

470U_D4_2.5VM

2

C259

470U_D4_2.5VM

2

1

1

C147

470U_D4_2.5VM

2

C352

470U_D4_2.5VM

+

1

C261

470U_D4_2.5VM

2

ESR total=1.875m ohm

C total=2590uF

+CPU_CORE

C371

470U_D4_2.5VM

+CPU_CORE

For Mobile's CPU:

1

C390

470U_D4_2.5VM

ESR total=0.75m ohm

C total=6350uF

+CPU_CORE

For DT

Please place these cap in the socket cavity area

C257

10U_1206_6.3V7K

C402

10U_1206_6.3V7K

Fan1 Control circuit

Q29

SI2303DS_SOT23

1

C401

10U_1206_6.3V7K

+12VS

2

R376

+5VS

Q10

FMMT619_SOT23 C

2

B

E

1

3.48K_0603_1%

C410

10U_1206_6.3V7K

C411

10U_1206_6.3V7K

D14

1SS355_SOD323

C291

10U_1206_6.3V7K

<30>

EN_FAN1

C99

10U_1206_6.3V7K

R385

13K_0603_1%

3 1

O

+5VFAN_1

JP12

C566

@1000P_0402_50V7K

Q12

2SA1036K_SOT23

U10

LMV321M7_SC70-5

D21

1

2

3

ACES_85205-0300

C405

10U_1206_6.3V7K

C403

10U_1206_6.3V7K

C578

0.1U_0402_16V4Z

5

2

+CPU_CORE

C574

0.1U_0402_16V4Z

D22

+5VS

1N4148_SOT23

SUSP

<17,33>

+CPU_CORE

1N4148_SOT23

2

1

2

R340 10K_0402_5%

+3VS

Please place these cap on the socket south side

R381

7.32K_0603_1%

+CPU_CORE

1

C122

10U_1206_6.3V7K

1

C121

10U_1206_6.3V7K

1

C356

10U_1206_6.3V7K

1

C62

10U_1206_6.3V7K

Fan2 Control circuit

C404

10U_1206_6.3V7K

Q8

@2SC2411K_SOT23

C

2

B

E

+5VS

6

2

R11

D11

@1SS355_SOD323

+12VS

1

@3.48K_0603_1%

2

+CPU_CORE

FAN1_TACH <30>

EN_FAN2

2

+CPU_CORE

2

1

D6

U1

@LMV321M7_SC70-5

Q1

@2SA1036K_SOT23

+5VFAN_2

JP19

C235

@1000P_0402_50V7K

C68

10U_1206_6.3V7K

C66

10U_1206_6.3V7K

1

2

3

@ACES_85205-0300

@1N4148_SOT23

1

R6

@7.32K_0603_1%

1

R200

Q63

@SM05_SOT23

2

+3VS

10K_0402_5%

FAN2_TACH <30>

3

C64

10U_1206_6.3V7K

1

2

C409

10U_1206_6.3V7K

C234

@0.1U_0402_16V4Z

O

-

R10

@13K_0603_1%

<30>

D20

@1N4148_SOT23

+5VS

C296

10U_1206_6.3V7K

3 1

1

C100

10U_1206_6.3V7K

1

C368

10U_1206_6.3V7K

1

C292

10U_1206_6.3V7K

1

C351

10U_1206_6.3V7K

Dell-Compal Confidential

8

Title

Compal Electronics, Inc.

SCHEMATIC, M/B LA-1452

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

Document Number

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

401230

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Custom

, 25, 2003

Date:

R ev

1B

Sheet

of

47

10

Mobile CPU

MO/DT_CPU

H

+3VS

<6,40> CPU_VID0

<6,40> CPU_VID1

<6,40> CPU_VID2

<6,40> CPU_VID3

<6,40> CPU_VID4

CPU_VID0

2

R260

1

1K_0402_5%

CPU_VID1

2

R259

1

1K_0402_5%

CPU_VID2

2

R258

1

1K_0402_5%

CPU_VID3

2

R257

1

1K_0402_5%

CPU_VID4

2

R256

1

1K_0402_5%

VID

VCC

1.750V

1.700V

1.650V

1.600V

1.550V

1.500V

1.450V

1.400V

1.350V

1.300V

1.250V

1.200V

1.150V

1.100V

1.050V

1.000V

0.975V

0.950V

0.925V

0.900V

0.875V

0.850V

0.825V

0.800V

0.775V

0.750V

0.725V

0.700V

0.675V

0.650V

0.625V

0.600V

+CPU_CORE

+CPU_CORE

1

C200

@10U_1206_6.3V7K

1

C199

@0.1U_0402_16V4Z

C560

@0.1U_0402_16V4Z

JP15

<6>

ITP_BPM0

<6>

ITP_BPM1

<6> ITP_PRDY#

<6> ITP_PREQ#

<6,9> H_RESET#

<6>

ITP_TCK

<6> CLK_ITP

<6> CLK_ITP#

1

C201

@2.2P_0402_16VCJ

1

3

5

7

9

11

13

15

17

19

21

23

25

2

4

6

8

10

12

14

16

18

20

22

24

K

2

4

6

8

10

12

14

16

18

20

22

24

26

2

1.5K_0603_1%

2

75_0603_1%

2

39_0603_1%

2

150_0603_1%

2

R373

1

@33_0402_5%

ITP_TDI

<6>

ITP_TMS <6>

ITP_TRST# <6>

ITP_TCK <6>

ITP_TDO

@2MM SMT KEY26

C198

@2.2P_0402_16VCJ

<6>

R304

27.4_0603_1%

2

AGP_BUSY# <16,19>

H_ITP_DBR# <6>

1

3

5

7

9

11

13

15

17

19

21

23

25

1

R184

1

R183

1

R372

1

R310

ITP Debug Connector

1

2

Desktop CPU

0 0 0 0 0

0 0 0 0 1

0 0 0 1 0

0 0 0 1 1

0 0 1 0 0

0 0 1 0 1

0 0 1 1 0

0 0 1 1 1

0 1 0 0 0

0 1 0 0 1

0 1 0 1 0

0 1 0 1 1

0 1 1 0 0

0 1 1 0 1

0 1 1 1 0

0 1 1 1 1

1 0 0 0 0

1 0 0 0 1

1 0 0 1 0

1 0 0 1 1

1 0 1 0 0

1 0 1 0 1

1 0 1 1 0

1 0 1 1 1

1 1 0 0 0

1 1 0 0 1

1 1 0 1 0

1 1 0 1 1

1 1 1 0 0

1 1 1 0 1

1 1 1 1 0

1 1 1 1 1

VRM output off

0

2

0

0

0

0

0

0

1

1

1

1

1

1

1

1

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1

0

0

1

1

1

1

0

0

0

0

1

1

1

1

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1

C

+5VS

C394

@0.1U_0402_16V4Z

C482

@0.1U_0402_16V4Z

SDA

SCL

OS#

GND

U23

VCC

A0

A1

A2

8

7

6

5

1

2

3

4

<6,30> SMB_EC_DA2

<6,30> SMB_EC_CK2

1

R351

2

@1K_0402_5%

@LM75CIMMX-5_MSOP8

SDA

SCL

OS#

GND

VCC

A0

A1

A2

8

7

6

5

@LM75CIMMX-5_MSOP8

1

R308

2

@10K_0402_5%

+5VS

B

1

U25

1

2

3

4

<6,30> SMB_EC_DA2

<6,30> SMB_EC_CK2

Address:1001_000X

R306

@1K_0402_5%

Address:1001_000X

Dell-Compal Confidential

A

Title

Compal Electronics, Inc.

SCHEMATIC, M/B LA-1452

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

Document Number

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

401230

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Custom

, 25, 2003

Date:

10

R ev

1B

Sheet

of

47

H A#[3..31]

DD R_SDQS[0..7]

<12> DDR_SDQS[0..7]

HD#[0..63] <5>

DDR_SDM[0..7]

<12> DDR_SDM[0..7]

HA#[3..31] <5>

DDR_SMA[0..12]

<12,13> DDR_SMA[0..12]

U12A

T30

R33

R34

N34

R31

L33

L36

P35

J36

K34

K36

M30

M35

L34

K35

H36

G34

G36

J33

D35

F36

F34

E36

H34

F35

D36

H35

E33

E34

B35

G31

C36

D33

D30

D29

E31

D32

C34

B34

D31

G29

C32

B31

B32

B30

B29

E27

C28

B27

D26

D28

B26

G27

H26

B25

C24

B23

B24

E23

C22

G25

B22

D24

G23

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

L31

J34

E29

E25

N31

G33

C30

D25

<6,8> H_RESET#

D22

<6>

<6>

<6>

<6>

<6>

<6>

<6>

<6>

K30

J31

D27

H24

H30

AD30

P30

<15> CLK_MCH_BCLK

<15> CLK_MCH_BCLK#

<11> MCH_GTLREF

1

C335

0.1U_0402_10V6K

HOST,HUB

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

W31

AA33

AB30

V34

Y36

AC33

Y35

AA36

AC34

AB34

Y34

AB36

AC36

AC31

AF35

AD36

AD35

AE34

AD34

AE36

AF36

AE33

AF34

AG34

AG36

AE31

AH35

AG33

AG31

HADSTB0#

HADSTB1#

AB35

AF30

H_ADSTB#0 <6>

H_ADSTB#1 <6>

P36

M36

T36

T34

M34

U33

U31

N36

U36

V30

T35

H_HIT#

<5>

H_HITM# <5>

H_ADS# <5>

H_BNR# <5>

H_BPRI# <5>

H_BREQ0# <5>

H_DBSY# <6>

H_DEFER# <5>

H_DRDY# <6>

H_TRDY# <6>

H_LOCK# <5>

C26

B33

C35

N33

H_DBI#3

H_DBI#2

H_DBI#1

H_DBI#0

<6>

<6>

<6>

<6>

V36

AA31

W33

AA34

W35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

HI[0..10]

<5>

<5>

<5>

<5>

<5>

<18>

HIT#

HITM#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HTRDY#

HLOCK#

DINV3

DINV2

DINV1

DINV0

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HI10

HI9

HI8

HI7

HI6

HI5

HI4

HI3

HI2

HI1

HI0

HI_STBS

HI_STBF

RS2#

RS1#

RS0#

AF2

AE2

AF3

AE5

AE4

AF4

AD8

AC5

AC7

AB8

AA7

HX_RCOMP

HY_RCOMP

HX_SWING

HY_SWING

HI_VREF

HI_RCOMP

HI_SWING

H I10

HI9

HI8

HI7

HI6

HI5

HI4

HI3

HI2

HI1

HI0

HUB_PSTRB <18>

HUB_PSTRB# <18>

P34

U34

R36

H_RS#2

H_RS#1

H_RS#0

B28

V35

H28

Y30

AD3

AC2

AD2

DDR_CLK2#

DDR_CLK2

DDR_CLK1#

DDR_CLK1

DDR_CLK0#

DDR_CLK0

DDR_CLK3 <13>

DDR_CLK3# <13>

DDR_CLK4 <13>

DDR_CLK4# <13>

DDR_CLK5 <13>

DDR_CLK5# <13>

U12B

AD4

AC4

CPURST#

HCLK

HCLK#

HD_VREF2

HD_VREF1

HD_VREF0

HA_VREF

HCC_VREF

<12>

<12>

<12>

<12>

<12>

<12>

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

<6>

<6>

<6>

R18 2

1

24.9_0603_1%

HX_RCOMP 10 mil

R263 2

1

10 mil

HY_RCOMP

24.9_0603_1%

DDR_SDQ0 AN4

DDR_SDQ1 AP2

DDR_SDQ2 AT3

DDR_SDQ3 AP5

DDR_SDQ4 AN2

DDR_SDQ5 AP3

DDR_SDQ6 AR4

DDR_SDQ7 AT4

DDR_SDQ8 AT5

DDR_SDQ9 AR6

DDR_SDQ10 AT9

DDR_SDQ11 AR10

DDR_SDQ12 AT6

DDR_SDQ13 AP6

DDR_SDQ14 AT8

DDR_SDQ15 AP8

DDR_SDQ16 AP10

DDR_SDQ17 AT11

DDR_SDQ18 AT13

DDR_SDQ19 AT14

DDR_SDQ20 AT10

DDR_SDQ21 AR12

DDR_SDQ22 AR14

DDR_SDQ23 AP14

DDR_SDQ24 AT15

DDR_SDQ25 AP16

DDR_SDQ26 AT18

DDR_SDQ27 AT19

DDR_SDQ28 AR16

DDR_SDQ29 AT16

DDR_SDQ30 AP18

DDR_SDQ31 AR20

DDR_SDQ32 AR22

DDR_SDQ33 AP22

DDR_SDQ34 AP24

DDR_SDQ35 AT26

DDR_SDQ36 AT22

DDR_SDQ37 AT23

DDR_SDQ38 AT25

DDR_SDQ39 AR26

DDR_SDQ40 AP26

DDR_SDQ41 AT28

DDR_SDQ42 AR30

DDR_SDQ43 AP30

DDR_SDQ44 AT27

DDR_SDQ45 AR28

DDR_SDQ46 AT30

DDR_SDQ47 AT31

DDR_SDQ48 AR32

DDR_SDQ49 AT32

DDR_SDQ50 AR36

DDR_SDQ51 AP35

DDR_SDQ52 AP32

DDR_SDQ53 AT33

DDR_SDQ54 AP34

DDR_SDQ55 AT35

DDR_SDQ56 AN36

DDR_SDQ57 AM36

DDR_SDQ58 AK36

DDR_SDQ59 AJ36

DDR_SDQ60 AP36

DDR_SDQ61 AM35

DDR_SDQ62 AK35

DDR_SDQ63 AK34

SDQ_0

SDQ_1

SDQ_2

SDQ_3

SDQ_4

SDQ_5

SDQ_6

SDQ_7

SDQ_8

SDQ_9

SDQ_10

SDQ_11

SDQ_12

SDQ_13

SDQ_14

SDQ_15

SDQ_16

SDQ_17

SDQ_18

SDQ_19

SDQ_20

SDQ_21

SDQ_22

SDQ_23

SDQ_24

SDQ_25

SDQ_26

SDQ_27

SDQ_28

SDQ_29

SDQ_30

SDQ_31

SDQ_32

SDQ_33

SDQ_34

SDQ_35

SDQ_36

SDQ_37

SDQ_38

SDQ_39

SDQ_40

SDQ_41

SDQ_42

SDQ_43

SDQ_44

SDQ_45

SDQ_46

SDQ_47

SDQ_48

SDQ_49

SDQ_50

SDQ_51

SDQ_52

SDQ_53

SDQ_54

SDQ_55

SDQ_56

SDQ_57

SDQ_58

SDQ_59

SDQ_60

SDQ_61

SDQ_62

SDQ_63

BROOKDALE-GL/PE

DDR

SMAA12/BS0

SMAA11/DQS8

SMAA10/DQ31

SMAA9/SMA3

SMAA8/SMA4

SMAA7/SMA6

SMAA6/SDQ29

SMAA5/SMA8

SMAA4/SMA11

SMAA3/SMA7

SMAA2/SMA9

SMAA1/SDQ19

SMAA0/SMA12

SMAB5

SMAB4

SMAB2

SMAB1

AN15

AL15

AK26

AK16

AN17

AP17

AP19

AL17

AL19

AK20

AP23

AN25

AL25

AK18

AN19

AN23

AP25

DDR_SMA12

DDR_SMA11

DDR_SMA10

DDR_SMA9

DDR_SMA8

DDR_SMA7

DDR_SMA6

DDR_SMA5

DDR_SMA4

DDR_SMA3

DDR_SMA2

DDR_SMA1

DDR_SMA0

DDR_SMAB5

DDR_SMAB4

DDR_SMAB2

DDR_SMAB1

SBA1

SBA0

AP27

AN27

DDR_SBS1

DDR_SBS0

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

AR2

AT7

AT12

AT17

AR24

AT29

AT34

AL36

DDR_SDQS0

DDR_SDQS1

DDR_SDQS2

DDR_SDQS3

DDR_SDQS4

DDR_SDQS5

DDR_SDQS6

DDR_SDQS7

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

AP4

AR8

AP12

AR18

AT24

AP28

AR34

AL34

DDR_SDM0

DDR_SDM1

DDR_SDM2

DDR_SDM3

DDR_SDM4

DDR_SDM5

DDR_SDM6

DDR_SDM7

AL13

AK14

AN13

AP13

DDR_CKE3

DDR_CKE2

DDR_CKE1

DDR_CKE0

AL29

AP31

AK30

AN31

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

AK28

AN29

AP29

DDR_SRAS#

DDR_SCAS#

DDR_SWE#

AK24

AL23

RDCLKO

R DCLKI

SCKE3/SCK#5

SCKE2/RSVD

SCKE1/SDQ58

SCKE0/RSVD

SCS#0/SCKE2

SCS#1/RSVD

SCS#2/SCK#2

SCS#3/SCAS#

SRAS#/SCKE0

SCAS#/RSVD

SWE#/SDQ5

SRCVEN_OUT#

SRCVEN_IN#

SMY_RCOMP

SM_VREF

DDR_SMAB5

DDR_SMAB4

DDR_SMAB2

DDR_SMAB1

<13>

<13>

<13>

<13>

DDR_SBS1 <12,13>

DDR_SBS0 <12,13>

DDR_CKE3

DDR_CKE2

DDR_CKE1

DDR_CKE0

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

<13>

<13>

<12>

<12>

<12>

<12>

<13>

<13>

DDR_SRAS# <12,13>

DDR_SCAS# <12,13>

DDR_SWE# <12,13>

2

R297

1

@0_0603_5%

RDCLKI & RDCLKO 100mils

LENGTH 5mils WIDTH

AJ34

AM2

1

1

BROOKDALE-GL/PE_760P

+2.5V

R298

60.4_0603_1%

SDREF

R299

0_0603_5%

C364

0.1U_0402_10V6K

R292

60.4_0603_1%

C357

0.1U_0402_10V6K

H_XY_SWING <11>

HUB_VREF <11,18>

2

+1.5VS

68_0603_1%

HUB_VSWING <11,18>

1

R295

C274 BROOKDALE-GL/PE_760P

C304

2

BROOKDALE-GL/PE

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

AL21

AK22

AN11

AP11

AM34

AL33

AP21

AN21

AP9

AN9

AP33

AN34

HD#[0..63]

DD R_SDQ[0..63]

<12> DDR_SDQ[0..63]

SCMD_CLK0

SCMD_CLK0#

SCMD_CLK1

SCMD_CLK1#

SCMD_CLK2

SCMD_CLK2#

SCMD_CLK3

SCMD_CLK3#

SCMD_CLK4

SCMD_CLK4#

SCMD_CLK5

SCMD_CLK5#

0.1U_0402_10V6K

82845GL-INT VGA

0.1U_0402_10V6K

82845PE-EXT VGA

1

C302

0.1U_0402_10V6K

Close to H28

C327

0.1U_0402_10V6K

Close to Y30

Layout note :

1. HX_RCOMP, HY_RCOMP Trace width 10 mil.

2. Terminator Max 500 mil.

Dell-Compal Confidential

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATIC, M/B LA-1452

Document Number

R ev

1B

401230

, 25, 2003

Sheet

1

of

47

+1.5VS

AGP_AD[0..31]

AGP_SBA[0..7]

Place close to pin D14

+2.5V

ANALOG DISPLAY

R241

36.5_0603_1%

2

INTCRT_B <16>

+CPU_CORE

INTCRT_G <16>

INTCRT_R <16>

BROOKDALE-GL/PE_760P

R273

8.2K_0402_5%

C324

0.1U_0402_10V6K

2

R17

137_0603_1%

CLK_MCH_DISPLAY <15>

PM_PWROK <19,30,32>

H_SEL0

<15>

R270

1

2

8.2K_0402_5%

INTCRT_B

INTCRT_B#

INTCRT_G

INTCRT_G#

INTCRT_R

INTCRT_R#

G15

H16

E15

F16

C15

D16

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

CLK_MCH_66M <15>

RSTIN#

PSBSEL

*

FSB FREQUENCY

400 MHZ

533 MHZ

B18

C18

D18

H18

B19

C19

D19

E19

G19

J19

B20

C20

D20

F20

H20

F18

K18

K20

K22

K26

M28

T28

Y28

AD28

VTTFSB0

VTTFSB1

VTTFSB2

VTTFSB3

VTTFSB4

VTTFSB5

VTTFSB6

VTTFSB7

VTTFSB8

VTTFSB9

VTTFSB10

VTTFSB11

VTTFSB12

VTTFSB13

VTTFSB14

VTTFSB15

VTTFSB16

VTTFSB17

VTTFSB18

VTTFSB19

VTTFSB20

VTTFSB21

VTTFSB22

VTTFSB23

R277

L3

KC FBM-L11-201209-221LMAT_0805

VCCA_DPLL

1

2

1

1

1

+

C29

C22

22U_1206_10V4Z

150U_D2_6.3VM

2

2

2

+1.5VS

R43

0_0402_5%

2

1

RSTIN#

PCIRST#

C251

0.1U_0402_10V6K

L4

KC FBM-L11-201209-221LMAT_0805

VCCA_FSB

1

2

+1.5VS

1

C27

0.1U_0402_10V6K

1

C28

22U_1206_10V4Z

AB2

Y2

1.5K_0402_5%

<6,16,18,22,23,25,26,30,33>

C69

@15P_0402_50V8J

+1.5VS

C33

0.1U_0402_10V6K

A37

AB3

AA2

AA3

AA4

AA5

Y4

Y8

W7

AU37

AU36

AT37

AU2

AU1

AT1

AJ35

AH34

A3

A7

C1

D4

D6

G1

K6

L1

L9

P6

R1

R9

W9

V6

P10

V10

AB10

BROOKDALE-GL/PE

POWER

VCCA_SM0

VCCA_SM1

VCCQSM0

VCCQSM1

VCCQSM2

VTTDECAP0

VTTDECAP1

VTTDECAP2

VTTDECAP3

VTTDECAP4

TESTIN#

MEM_SEL

VCCA_FSB

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

VCCA_HI

VCCHI0

VCCHI1

VCCHI2

VCCHI3

VCCA_DPLL

VCCGPIO

VCCA_DAC0

VCCA_DAC1

NC

NC

NC

NC

NC

NC

NC

NC

SMX_RCOMP

NC

NC

NC

NC

100U_D2_6.3VM

L27

KC FBM-L11-201209-221LMAT_0805

B

+1.5VS

C334

4.7U_0805_10V4Z

R281

1_0402_5%

AG1

AG2

VCCA_SM

1

0.1U_0402_10V6K

1

1

AT20

AT21

AU21

C640

C353

A31

AC37

R37

L37

G37

A17

VCCA_DAC

1

+ C336

100U_D2_6.3VM

2

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

C

VCCA_FSB

1

C277

AD10

AD6

AC9

AC1

AE3

A13

B6

B14

A15

C159

100U_D2_6.3VM

2

+1.5VS

1

C297

0.1U_0402_10V6K

1

C316

1

C332

C32

0.1U_0402_10V6K

2

0.1U_0402_10V6K

VCCA_DPLL

+3VS

VCCA_DAC

AF10

A2

A36

B37

B1

R287

60.4_0603_1%

R283

60.4_0603_1%

+2.5V

2

C270

0.1U_0402_10V6K

C344

0.1U_0402_10V6K

BROOKDALE-GL/PE_760P

+

C399

C267

HSYNC

VSYNC

DDCA_CLK

DDCA_DATA

REFSET

<16> INT_HSYNC

<16> INT_VSYNC

<16> INTDDCCK

<16> INTDDCDA

B7

C6

D7

C7

B16

+

C340

0.01U_0402_25V4Z

47.5_0603_1%

R215 1

2

1

2

R214

47.5_0603_1%

100U_D2_6.3VM

1

C268

L2

W2

+AGPREF

AE7

AJ31

D14

E7

Y3

C333

10P_0402_50V8K

0.1U_0402_10V6K

AGP_C/BE#3

AGP_C/BE#2

AGP_C/BE#1

AGP_C/BE#0

R286

22_0402_5%

AH8

AK8

AG9

AJ9

AL9

AM22

AJ23

AL37

AU9

AK10

AJ11

AL11

AU25

AM26

AU13

AM14

AJ27

AJ1

AL1

AJ15

AP15

AU29

AH2

AJ2

AK2

AL2

AM30

AH3

AJ3

AK3

AL3

AH4

AJ4

AK4

AL4

AU17

AJ5

AL5

AU5

AM18

AJ19

AK32

AU33

AH6

AK6

AP20

AG7

AJ7

AL7

AP7

AH10

AH12

AH14

AH18

AH22

AH26

M4

N7

N5

P2

N2

D5

P4

B5

H2

M2

N4

R4

CLK_MCH_66M

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

<16> AGP_FRAME#

<16> AGP_IRDY#

<16> AGP_TRDY#

<16> AGP_STOP#

<16> AGP_DEVSEL#

<16> AGP_REQ#

<16>

AGP_PAR

<16> AGP_GNT#

<16> AGP_C/BE#3

<16> AGP_C/BE#2

<16> AGP_C/BE#1

<16> AGP_C/BE#0

Place close to pin AE7

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

L28

KC FBM-L11-201209-221LMAT_0805

V8

U7

M8

L7

F4

E5

Y19

AA19

W20

U21

W21

AA21

A9

B9

C9

D9

E9

B10

C10

D10

F10

H10

A11

B11

C11

D11

E11

G11

J11

B12

C12

D12

F12

H12

G13

J13

H14

J15

AA17

W17

U17

W18

V19

U19

K10

K12

K14

K16

W19

<16> AGP_ADSTB0

<16> AGP_ADSTB0#

<16> AGP_ADSTB1

<16> AGP_ADSTB1#

<16> AGP_SBSTB

<16> AGP_SBSTB#

C4

B4

B3

C249

5P_0402_50V8C

AGP_ST0

AGP_ST1

AGP_ST2

AGP_ST0

AGP_ST1

AGP_ST2

R234

10_0402_5%

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

V4

V2

W4

W5

U5

U4

U2

V3

T2

T3

T4

R2

R5

R7

T8

P3

P8

K4

K2

J2

M3

L5

L4

H4

G2

K3

J4

J5

J7

H3

K8

G4

GAD0/DVOBHSYNC

GAD1/DVOBVSYNC

GAD2/DVOBD1

GAD3/DVOBD0

GAD4/DVOBD3

GAD5/DVOBD2

GAD6/DVOBD5

GAD7/DVOBD4

GAD8/DVOBD6

GAD9/DVOBD9

GWBF#

GAD10/DVOBD8

GRBF#

GAD11/DVOBD11

BROOKDALE-GL/PE GAD12/DVOBD10

GST0

GAD13/DVOBCCLKINT#

GST1

GAD14/DVOBFLDSTL

GST2

GAD15/MDDC CLK

GAD16/DVOCVSYNC

GAD_STB0/DVOBCLK

GAD17/DVOCHSYNC

GAD_STB0#/DVOBCLK#

GAD18/DVOCBLANK#

GAD_STB1/DVOCCLK

GAD19/DVOCD0

GAD_STB1#/DVOCCLK#

GAD20/DVOCD1

GSBSTB

GAD21/DVOCD2

GSBSTB#

GAD22/DVOCD3

GAD23/DVOCD4

G_FRAME#/MDVI DATA

GAD24/DVOCD7

G_IRDY#/MI2C CLK

GAD25/DVOCD6

G_TRDY#/MDVI CLK

GAD26/DVOCD9

G_STOP#/MDDC DATA

GAD27/DVOCD8

G_DEVSEL#/MI2C DATA

GAD28/DVOCD11

G_REQ#

GAD29/DVOCD10

G_PAR/ADD_DETECT

GAD30/DVOBCINTR#

G_GNT#

GAD31/DVOCFLDSTL

GCBE3#/DVOCD5

GCBE2#

GCBE1#/DVOBBLANK#

GCLKIN

GCBE0#/DVOBD7

RSTIN#

DREFCLK

AGP RCOMP/DVOBCRCOMP

PWROK

AGP_VREF

PSBSEL

<16>

<16>

<16>

AGP/DVO

C385

G5

G7

<16> AGP_WBF#

<16> AGP_RBF#

GPIPE#

GSBA0/ADDIN0

GSBA1/ADDIN1

GSBA2/ADDIN2

GSBA3/ADDIN3

GSBA4/ADDIN4

GSBA5/ADDIN5

GSBA6/ADDIN6

GSBA7/ADDIN7

H8

C3

C2

D3

D2

E4

E2

F3

F2

AGP_PIPE#

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

<16> AGP_PIPE#

U12D

VCCAGP0

VCCAGP1

VCCAGP2

VCCAGP3

VCCAGP4

VCCAGP5

VCCAGP6

VCCAGP7

VCCAGP8

VCCAGP9

VCCAGP10

VCCAGP11

VCCAGP12

VCCAGP13

VCCAGP14

VCCAGP15

VCCAGP16

CLK_MCH_DISPLAY

U12C

0.1U_0402_10V6K

<16> AGP_AD[0..31]

<16> AGP_SBA[0..7]

INTCRT_B#

INTCRT_G#

+1.5VS

INTCRT_R#

1

C343

0.1U_0402_10V6K

C341

0.1U_0402_10V6K

NEAR AA1

NEAR AE1

Dell-Compal Confidential

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

A

SCHEMATIC, M/B LA-1452

Document Number

R ev

1B

401230

, 25, 2003

Sheet

E

10

of

47

HUB_VSWING <9,18>

R264

226_0603_1%

2

0.01U_0402_25V4Z

R312

100_0603_1%

2

BROOKDALE-GL/PE_760P

VSSA_DAC0

VSSA_DAC1

NEAR MCH

0.1U_0402_10V6K

NEAR ICH

NEAR MCH

Within 250mil

C125

0.01U_0402_25V4Z

NEAR ICH

Within 250mil

10 mil Trace,

7 mil Space

1

R245

+CPU_CORE

2

49.9_0603_1%

MCH_GTLREF <9>

1

R244

100_0603_1%

C299

0.1U_0402_10V6K

FSB DECOUPLING

+CPU_CORE

NEAR MCH

10U_1206_6.3V7K

1

0.1U_0402_10V6K

1

C245

1

C246

1

C255

10U_1206_6.3V7K

0.1U_0402_10V6K

1

C253

1

C254

1

C252

0.1U_0402_10V6K

C250

0.1U_0402_10V6K

10 mil Trace,

7 mil Space

0.1U_0402_10V6K

R246

2

+CPU_CORE

H_XY_SWING <9>

301_0603_1%

0.1U_0402_10V6K

1

1

C281

1

C279

0.1U_0402_10V6K

R247

150_0603_1%

1

C284

0.1U_0402_10V6K

1

C288

C289

0.1U_0402_10V6K

C309

0.01U_0402_25V4Z

0.1U_0402_10V6K

SYSTEM MEMORY DECOUPLING

+2.5V

0.1U_0402_10V6K

1

1

C345

0.1U_0402_10V6K

1

C346

1

C367

0.1U_0402_10V6K

1

C380

0.1U_0402_10V6K

1

C383

1

C384

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C338

1

C354

0.1U_0402_10V6K

0.1U_0402_10V6K

C366

C358

0.1U_0402_10V6K

C382

1

C361

0.1U_0402_10V6K

C381

1

C374

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C373

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C362

0.1U_0402_10V6K

C379

1

C363

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C347

0.1U_0402_10V6K

C378

1

C359

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C370

0.1U_0402_10V6K

C360

2

1

C350

0.1U_0402_10V6K

1

1

C349

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C348

C365

0.1U_0402_10V6K

0.1U_0402_10V6K

GMCH DECOUPLING

+1.5VS

0.1U_0402_10V6K

1

1

C326

B15

C14

R309

C392

PLACE NOTE:

C339

CAP PLACE

0.1U_0402_10V6K

AT MIDPOINT

2

2

OF THE BUS. 100_0603_1%

C17

B17

AM16

W3

U3

R3

D17

N3

L3

J3

G3

E3

AT2

F30

AR29

AJ29

AG29

AE29

AC29

AA29

W29

R29

U29

N29

L29

J29

C29

A29

AU15

AR15

D15

B2

AR1

AN1

AE1

AA1

U1

N1

J1

E1

AM28

F28

AU27

AR27

AL27

F14

AR13

AJ13

J27

C27

A27

E13

D13

C13

B13

AM12

AK12

F26

AR25

AJ25

J25

AU11

AR11

AR37

AN37

C25

AJ37

AG37

AE37

AA37

U37

AH28

AF28

AB28

V28

P28

K28

K24

J37

E37

C37

AT36

AH36

VSS

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

1

C393

AR9

AR17

AJ17

Y17

AG4

AB4

AU3

AR3

AN3

AM3

AG3

AC3

C31

AH30

V17

J17

G17

E17

BROOKDALE-GL/PE

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

C126

0.1U_0402_10V6K

1

C329

1

C322

C331

0.1U_0402_10V6K

0.1U_0402_10V6K

1

0.1U_0402_10V6K

1

C308

0.1U_0402_10V6K

1

C330

1

C328

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C271

2

1

C278

C298

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C256

0.1U_0402_10V6K

1

C342

C280

0.1U_0402_10V6K

0.1U_0402_10V6K

N35

R35

U35

AA35

AC35

AE35

AG35

AL35

AN35

AR35

AU35

B36

W36

AF8

AM8

G9

J9

N9

U9

AA9

AE9

A23

C23

D23

J23

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

U12E

AM10

AR23

AU23

F24

AM24

A25

C16

N37

U18

V18

Y18

AA18

AL31

AR31

AU31

F32

H32

K32

M32

P32

T32

V32

Y32

AB32

AD32

AF32

AH32

AM4

A5

C5

AG5

AN5

AR5

AR19

AM32

A33

C33

AJ33

AN33

AR33

F6

H6

M6

T6

Y6

AB6

AF6

AM6

U20

V20

Y20

AA20

AM20

A21

B21

C21

D21

E21

G21

J21

D34

W34

A35

E35

G35

J35

L35

AN7

AR7

AU7

B8

C8

D8

F8

V21

Y21

AJ21

AR21

F22

H22

M10

T10

Y10

AH16

AH20

AH24

HUB_VREF <9,18>

1

C337

0.01U_0402_25V4Z

10 mil Trace,

7 mil Space

0.01U_0402_25V4Z

1

+1.5VS

0.1U_0402_10V6K

1

1

C301

0.1U_0402_10V6K

1

C300

2

1

C285

0.1U_0402_10V6K

1

C269

2

1

C276

0.1U_0402_10V6K

1

C275

2

1

C260

0.1U_0402_10V6K

1

C307

2

1

C295

0.1U_0402_10V6K

1

C287

1

C311

1

C286

C283

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

Dell-Compal Confidential

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

Size

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

5

SCHEMATIC, M/B LA-1452

Document Number

R ev

1B

401230

, 25, 2003

Sheet

1

11

of

47

+2.5V

DDR_SDQ4

DDR_SDQ0

RP32

1

2

10_4P2R_0402_5%

DDR_DQ4

4

DDR_DQ0

3

DDR_SDQ30

DDR_SDQ26

RP46

1

2

RP42

DDR_SDQ1

1

DDR_SDQ5

2

10_4P2R_0402_5%

DDR_DQ1

4

DDR_DQ5

3

RP37

DDR_SDQ31

1

DDR_SDQ27

2

RP33

1

2

10_4P2R_0402_5%

DDR_DQ6

4

DDR_DQ2

3

DDR_SDM0

DDR_SDM1

R124

2

2

R117

10_0402_5%

DDR_DM0

1

DDR_DM1

1

10_0402_5%

RP43

DDR_SDQ3

1

DDR_SDQ7

2

10_4P2R_0402_5%

DDR_DQ3

4

DDR_DQ7

3

R126

DDR_SDM2

2

DDR_SDM3

2

R121

10_0402_5%

DDR_DM2

1

DDR_DM3

1

10_0402_5%

DDR_SDQ9

DDR_SDQ8

RP20

1

2

10_4P2R_0402_5%

DDR_DQ9

4

DDR_DQ8

3

DDR_SDM4

DDR_SDM5

R108

2

2

R113

10_0402_5%

DDR_DM4

1

DDR_DM5

1

10_0402_5%

DDR_SDQ13

DDR_SDQ12

RP31

1

2

10_4P2R_0402_5%

DDR_DQ13

4

DDR_DQ12

3

DDR_SDM6

DDR_SDM7

R115

2

2

R118

10_0402_5%

DDR_DM6

1

DDR_DM7

1

10_0402_5%

DDR_SDQ6

DDR_SDQ2

1

JP22

DDR_DQ5

DDR_DQ1

10_4P2R_0402_5%

DDR_DQ31

4

DDR_DQ27

3

DDR_DQS0

DDR_DQ2

DDR_DQ6

DDR_DQ8

DDR_DQ9

DDR_DQS1

DDR_DQ14

DDR_DQ15

<9> DDR_CLK1

<9> DDR_CLK1#

DDR_DQ20

DDR_DQ16

DDR_DQS2

DDR_DQ18

DDR_DQ22

DDR_DQ24

DDR_DQ28

DDR_DQS3

DDR_SDQ15

DDR_SDQ14

RP21

1

2

10_4P2R_0402_5%

DDR_DQ15

4

DDR_DQ14

3

DDR_SDQ37

DDR_SDQ32

RP16

1

2

10_4P2R_0402_5%

DDR_DQ37

4

DDR_DQ32

3

DDR_SDQ11

DDR_SDQ10

RP40

1

2

10_4P2R_0402_5%

DDR_DQ11

4

DDR_DQ10

3

DDR_SDQ36

DDR_SDQ33

RP28

1

2

10_4P2R_0402_5%

DDR_DQ36

4

DDR_DQ33

3

DDR_SDQ16

DDR_SDQ20

RP41

1

2

10_4P2R_0402_5%

DDR_DQ16

4

DDR_DQ20

3