Professional Documents

Culture Documents

Asic Back-End: Physical Design For Standard Cells

Asic Back-End: Physical Design For Standard Cells

Uploaded by

SriramNaiduGorleOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Asic Back-End: Physical Design For Standard Cells

Asic Back-End: Physical Design For Standard Cells

Uploaded by

SriramNaiduGorleCopyright:

Available Formats

Physical Design for Standard Cells | asic back-end

https://usebackend.wordpress.com/2012/10/25/as...

asic back-end

H O ME

AB O U T

after verication

Physical Design for Standard Cells

October 25, 2012 by arunodayanjohn

BACK-END LIBRARIES

RECENT POSTS

CTS (Clock Tree Synthesis)

Clock Routing Algorithms

Libraries are the most critical parts of complete ASIC design

because the measure of accuracy of these libraries has great

Blockages and Halos

impact on both success and failure of ASIC design. Three types

of cells to be placed in physical design stage are

Physical Design for Standard Cells

1) standard cells

2) macro cells

ASIC Floor Planning

ARCHIVES

3) I/O pads

Among these Standard cell library and I/O pad library are

December 2012

typically used in ASIC physical design. The second cell to be

placed will be in the form of GDS (Graphical Data Stream) or

hard IPs. The macro cells all violations regarding timing and

October 2012

physical are already xed and there is no need to touch the

internal part of the cell.Macros are the outcome of block level

designs.

STANDARD CELL PHYSICAL DESIGN

Standard cell is a specic design for each gate. Special care

need to be taken during the process of physical design of such

libraries in-order to achieve optimum die size and performance.

Optimum area can be achieved by minimizing the routing area

rather than minimizing the number of transistors. This is

because of ASICs complexity due to shrinking and scaling.

Routing within standard cells have to be minimized because of

most of the ASICs routing is done automatically by tool itself.

So optimized design can be achieved by making the standard

cells routing as optimized. Main parameters to be considered in

standard cell library designing is

1) spacing rules

2) height of the cell

3) I/O ports location

November 2012

CATEGORIES

ASIC Back-End

Uncategorized

META

Register

Log in

Entries RSS

Comments RSS

WordPress.com

1) Spacing Rules

Basic step in spacing rules begins with horizontal and vertical

wire track determination. Wire tracks are nothing but horizontal

and vertical lines drawn on the layout area. Wire tracks acts like

guidelines for making the interconnections. Spacing, width are

xed to avoid spacing related issues in the further stages. In

three ways wire track spacing is done as mentioned below

i) lint to line > d1

ii) via to line (or) line to via > d2

iii) via to via > d3

The spacing is as mentioned below in gure-1.

Follow

1 of 4

Monday 15 June 2015 12:29 PM

Physical Design for Standard Cells | asic back-end

https://usebackend.wordpress.com/2012/10/25/as...

g-1: Three ways of spacing

Among the three ways, choosing the appropriate one and xing

it as common spacing throughout the library is the challenge.

Choosing one appropriate spacing for the library will be

eective only if the condition d3> d2> d1 is followed.

Fixing the via to via (d3) spacing distance for all designs in a

library leads to more spacing and as a result of this routing will

not be optimum. xing line to line (d1) spacing distance for all

designs in a library leads to less spacing between metals and

logic and as a result of this routing will face DRC violations.

Therefore xing via to line (d2) for all design within a library

satises both line to line and via to via spacing constraints.

Routing will be optimum by using via to line (d2) for all

conducting layer spacing rules and compact routing can be

achieved. Since most of the ASICs routing is carried out

automatically by software tool itself, optimized routing will be

achieved by eective routing of interconnects of standard cell.

2) Height of the cell

unit tile: It is a minimum height and width of the cell to be

placed. These measures are available in the technology library.

Unit tile is also known as site.

g-2: unit tile

From the unit tile it is clear that the height of the standard cells

to be placed should be the same, because these cells are to be

placed on the placement rows in block-level or chip-level

designs. Generally height of the standard cell is equal to the

height of placement rows.. various width of the cell is available

according to functionality and the drive strength of the cell and

the width of the standard cell should be the multiple of width of

the unit tile.

A Complementary Metal Oxide Semiconductor (CMOS) design

has a height equal to the sum of Vdds width, pmos channel

width, diusion spacing between pull-up and pull-down

transistors, nmos channel width and the width of Vss metal

layer. Clear picture of this is shown below in gure-3.

Follow

2 of 4

Monday 15 June 2015 12:29 PM

Physical Design for Standard Cells | asic back-end

https://usebackend.wordpress.com/2012/10/25/as...

g-3: height of cell

Once wire tracks and height of the cell are determined it is

given to the standard cell layout in the form of wire track

template. This wire track template is laid on the layout (g-4) to

ensure whether it meets all requirements of software tool or

not. Width of the Vdd and Vss should be considerably stable

in-order to provide proper current ow capability. Less width of

Vdd and Vss will provide degraded 1 and 0 to power and ground

respectively which in turn aects the overall performance of the

design and relatively more width will aect the standard cells

height. Width should be stable enough to provide strong 1 and 0

to vdd and vss respectively. High resistance in Vdd and Vss

metal leads to latch-up phenomena.

Todays EDA tool provide high exibility in choosing the metal

layer such as rst metal traverse in vertical direction and

second metal traverse in horizontal direction. This is an added

advantage in standard cell physical design. Internal node

capacitance need to be kept minimum, especially with nodes

close to Vdd and Vss in-order avoid body eect.

3) Fixing I/O Pin or Ports

Another factor in standard cell physical design need to be taken

care is xing the physical location of I/O ports. It is advisable to

use M1 for routing between the transistors.Placing the ports

where exactly horizontal and vertical wire tracks cross each

other yields better results because of reduce in routing

complexity. This is called Port accessibility. This improves

execution time during routing and produces better quality

results. Pictorial representation of port accessibility is shown

below in gure-4.

g-4: port accessibility and port location

If routing is done with the help of wire track

lines geometrical regularities withing same type of cells will be

the same. Maintaining the geometrical regularities among the

standard cells of same type has two main advantages.

allows size reduction to another process node or another set

of DRC rules

common electrical characteristics helps in deciding the pmos

and nmos channel width within the library.

Placing nmos transistors near Vss and placing pmos transistors

near Vdd will also reduce the routing resources considerably

Follow

3 of 4

Monday 15 June 2015 12:29 PM

Physical Design for Standard Cells | asic back-end

https://usebackend.wordpress.com/2012/10/25/as...

because of CMOS designs nature.

g-5: Abstract view of a cell

The nal outcome of standard cell physical design is available in

the form of lef(Layout Exchange Format). It is a very popular

format for abstract view of library. Otherwise called as physical

library.

Share this:

Like

Be the rst to like this.

This entry was posted in Uncategorized. Bookmark the permalink.

ASIC FLOOR PLANNING

Leave a Reply

Create a free website or blog at WordPress.com. | The Ascetica Theme.

Follow

4 of 4

Monday 15 June 2015 12:29 PM

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- SII ManualDocument47 pagesSII ManualMike SharpeNo ratings yet

- TitanSMA GettingStartedGuide 17203R3Document2 pagesTitanSMA GettingStartedGuide 17203R3Gianfranco Taco100% (1)

- Chapter3 Op Amp (1) 80911Document62 pagesChapter3 Op Amp (1) 80911Azman Mat HussinNo ratings yet

- No Lab Next Week Midterm On FR Febr 19 6:30-8pm in Review Session: TBA (Most Likely On TH)Document20 pagesNo Lab Next Week Midterm On FR Febr 19 6:30-8pm in Review Session: TBA (Most Likely On TH)SriramNaiduGorleNo ratings yet

- Encounter Library Characterizer User Guide: Product Version 12.0 December 2012Document212 pagesEncounter Library Characterizer User Guide: Product Version 12.0 December 2012SriramNaiduGorleNo ratings yet

- No Figures in This Chapter... : Here AreDocument2 pagesNo Figures in This Chapter... : Here AreSriramNaiduGorleNo ratings yet

- Post Synthesis Simulation: "Source /cad/digital/bashrc "Vsim"Document2 pagesPost Synthesis Simulation: "Source /cad/digital/bashrc "Vsim"SriramNaiduGorleNo ratings yet

- Chapter10 AbstractDocument8 pagesChapter10 AbstractSriramNaiduGorleNo ratings yet

- Signalstorm ProblemsDocument9 pagesSignalstorm ProblemsSriramNaiduGorleNo ratings yet

- Arm BookDocument164 pagesArm BookSriramNaiduGorleNo ratings yet

- USB Floppy Drive Floppy Disk Drive To USB Floppy Drive To USBDocument3 pagesUSB Floppy Drive Floppy Disk Drive To USB Floppy Drive To USBhclraj406100% (1)

- Bharat Heavy Elelctricals Limited: Operation & Maintenance Manual of Bhelscan Flame Scanner System (Bn10)Document25 pagesBharat Heavy Elelctricals Limited: Operation & Maintenance Manual of Bhelscan Flame Scanner System (Bn10)Deepak Gupta100% (1)

- Apache 2.0 License - EnglishDocument5 pagesApache 2.0 License - Englishbabuchas69No ratings yet

- Converter Circuits University of Colorado, Boulder Prof. Robert EricksonDocument4 pagesConverter Circuits University of Colorado, Boulder Prof. Robert EricksonThinh NguyenNo ratings yet

- MICRO22 - FPGA - DL - Deep Learning Optimized FPGA ArchitecturesDocument230 pagesMICRO22 - FPGA - DL - Deep Learning Optimized FPGA Architecturesmuhammadakhtar201No ratings yet

- Antennas and PropagationDocument37 pagesAntennas and PropagationGeza FirmansyahNo ratings yet

- Rtu - SasDocument19 pagesRtu - SasNitin KumarNo ratings yet

- 558 1 4 01 - r21Document37 pages558 1 4 01 - r21Abubakar SidikNo ratings yet

- Applied Physics AssignmentDocument3 pagesApplied Physics AssignmentareejNo ratings yet

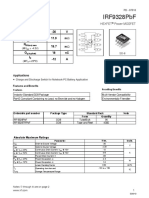

- IRF9328PBFDocument8 pagesIRF9328PBFΚΩΝΣΤΑΝΤΙΝΟΣ ΚΟΝΤΟΜΙΣΙΟΣNo ratings yet

- EEE 1002 Module 8 Self and Mutual InductanceDocument37 pagesEEE 1002 Module 8 Self and Mutual InductanceGnanavignesh RNo ratings yet

- NCP1203 PDFDocument15 pagesNCP1203 PDFLotteDomineNo ratings yet

- Grade 12 Second ExamDocument2 pagesGrade 12 Second ExamKen SisonNo ratings yet

- Concepts Involving Digital Circuits Binary Numbers ReportDocument6 pagesConcepts Involving Digital Circuits Binary Numbers ReportElmae AringaNo ratings yet

- Cajas AcusticasDocument65 pagesCajas AcusticasAntonio Perez PerezNo ratings yet

- Commutation Torque Ripple Reduction in BLDC Motor Using Modified SEPIC Converter and ThreeDocument2 pagesCommutation Torque Ripple Reduction in BLDC Motor Using Modified SEPIC Converter and ThreestarboyNo ratings yet

- ICT Five Generations of Computers PDFDocument24 pagesICT Five Generations of Computers PDFPaula BautistaNo ratings yet

- Brother WORD PROCESSOR dp525cj - Service - ManualDocument194 pagesBrother WORD PROCESSOR dp525cj - Service - ManualJan SoukupNo ratings yet

- Computer Power VT 6 y 10 KvaDocument4 pagesComputer Power VT 6 y 10 KvacristianNo ratings yet

- V V V V ... Etc: Inductors in ParallelDocument6 pagesV V V V ... Etc: Inductors in ParallelSitty GuNo ratings yet

- Datablad Solivia 20 EU G4Document2 pagesDatablad Solivia 20 EU G4Lars MaesNo ratings yet

- Noise in Analog CommunicationDocument21 pagesNoise in Analog CommunicationMyana Sai NathNo ratings yet

- Samsung Ks1aDocument78 pagesSamsung Ks1aummu aqiellaNo ratings yet

- 5200 Eng A 2Document2 pages5200 Eng A 2api-124560989No ratings yet

- Setup and Hold Time Violation Static Timing Analysis (STA) Basic (Part 3b) VLSI ConceptsDocument14 pagesSetup and Hold Time Violation Static Timing Analysis (STA) Basic (Part 3b) VLSI ConceptsĐứcĐỗNo ratings yet

- KCL and KVLDocument113 pagesKCL and KVLmanjuvenammaNo ratings yet

- ECSS Q ST 60 13C (21october2013)Document100 pagesECSS Q ST 60 13C (21october2013)jsadachiNo ratings yet