Professional Documents

Culture Documents

DR - NGP Institute of Technology Coimbatore - 48: Department of Cse & It

Uploaded by

Parandaman Sampathkumar SOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DR - NGP Institute of Technology Coimbatore - 48: Department of Cse & It

Uploaded by

Parandaman Sampathkumar SCopyright:

Available Formats

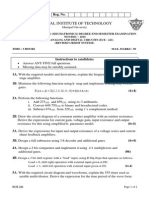

Dr.

NGP Institute of Technology

Coimbatore 48

QUESTION PAPER FOR MODEL TEST- I

DEPARTMENT OF CSE & IT

Semester & Branch: II & Common to CSE & IT

Date / Session: .04.15/AN

Subject: DPSD

Max. Marks: 100 Marks

Subject code: CS6201

Max. Time: 3 hrs

ANSWER ALL THE QUESTIONS

PART A

(10 x 2 = 20)

1. State and Prove Consensus Theorem.

2. Reduce A'B'C' + A'BC' + ABC.

3. Implement the function G=(0,3) using 2*4 decoder.

4. Write the Excitation table and equation of JK and T flip flop.

5. Write any four applications of shift register.

6. A shift register comprises of JK flip-flops. How will you complement the contents of the register?

7. Define race condition.

8. Define ASIC and List the types of Hazards.

9. What is memory decoding?

10. What is meant by static and dynamic memories?

PART B

(5 x 16 = 80)

11. (a) Simplify the following functions using K-map technique.

G=M (0, 1, 3, 7, 9, 11)

(8)

F(W,X,Y,Z)= m ( 0, 7, 8, 9, 10, 12) + d ( 2, 5, 13).

(8)

(OR)

(b) Minimize the expression using Quine Mc Cluskey method

(16)

F= m ( 0, 1, 9, 15, 24, 29, 30) + d ( 8, 11, 31).

12. (a) Design the circuit that converts 8421 BCD code to Excess -3 code.

(OR)

(b) Implement the following Boolean function using 8 to 1 Multiplexer

F(A,B,C,D) = ABD + ACD + BCD + ACD and also implement the function

Using 16 to 1 Multiplexer.

(16)

Dr.NGP Institute of Technology

Coimbatore 48

QUESTION PAPER FOR MODEL TEST- I

13. (a) Implement T flip flop using D flip flop and JK flip flop using D flip flop.

(16)

(OR)

(b) Design synchronous counter which counts in the sequence 000, 001, 010, 011, 100

(16)

101, 110, 111, 000 using D flip flop.

14. (a) Design an asynchronous sequential circuit with inputs xl and x2 and one

output z.

(16)

Initially and at any time if both the inputs are 0, output is equal to 0.

When xl or x2

becomes 1, z becomes 1. When second input also becomes 1, z = 0;

The output stays

at 0 until circuit goes back to initial state.

(OR)

(b) Implement the switching function F= m (1, 3, 5, 7, 8, 9, 14, 15) by a static hazard

(16)

free two level AND OR gate network.

15. (a) Implement the following function using PLA

(16)

A(x, y, z) = (1, 2, 4, 6)

B(x, y, z) = (0, 1, 6, 7)

C(x, y, z) = (2, 6).

(OR)

(b) The following messages have been coded in a even parity Hamming code and

transmitted through a noisy channel. Decode the messages, assuming that at most

a single error has occurred in each code word.

(i) 1001001

(ii) 0111001

(iii) 1110110

(iv) 0011011.

(16)

Dr.NGP Institute of Technology

Coimbatore 48

QUESTION PAPER FOR MODEL TEST- I

Prepared by

Staff Name and Signature

Approved by

HOD Name and Signature

You might also like

- EC8392-Digital EletronicsDocument2 pagesEC8392-Digital Eletronicssyed1188No ratings yet

- Cs PaperDocument37 pagesCs PaperAshish BokilNo ratings yet

- Sir Padampat Singhania University Digital Electronics ExamDocument5 pagesSir Padampat Singhania University Digital Electronics ExamIyyakutti GanapathiNo ratings yet

- 10CS33 QBDocument11 pages10CS33 QBbharath5911No ratings yet

- DLD question bankDocument5 pagesDLD question bankHarshad ThiteNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Monica NareshNo ratings yet

- DE PaperDocument4 pagesDE Paperbhaveshgupta098No ratings yet

- Model ImpDocument3 pagesModel ImpjeevaNo ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- Epc Questions - Cs8351 Digital Principles and System DesignDocument2 pagesEpc Questions - Cs8351 Digital Principles and System DesignaltaNo ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- Digital Logic CircuitsDocument7 pagesDigital Logic CircuitsMATHANKUMAR.SNo ratings yet

- 6C0065Document4 pages6C0065Joshua prabuNo ratings yet

- EC 6302 2-Marks and 16 Marks QuestionsDocument12 pagesEC 6302 2-Marks and 16 Marks QuestionsskaruppaiaheceNo ratings yet

- EC6302 Digital ElectronicsDocument12 pagesEC6302 Digital ElectronicsJabeen BanuNo ratings yet

- Digital Logic Circuits Tutorial (2014-2015) ODD SemDocument7 pagesDigital Logic Circuits Tutorial (2014-2015) ODD SemSai Er SaravananNo ratings yet

- Tutorial 1 15Document13 pagesTutorial 1 15Charan Kanwal SinghNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- Question Bank: Ec6302 Digital ElectronicsDocument14 pagesQuestion Bank: Ec6302 Digital ElectronicsBarry SmithNo ratings yet

- D L C Question BankDocument11 pagesD L C Question BankLeka AmuNo ratings yet

- Deld QB EndsemDocument4 pagesDeld QB EndsemUV New MoviesNo ratings yet

- Digital Logic CircuitsDocument15 pagesDigital Logic CircuitsskblkoNo ratings yet

- Digital Logic CircuitsDocument20 pagesDigital Logic CircuitsrameshsophidarlaNo ratings yet

- STLD3 - Question BankDocument6 pagesSTLD3 - Question Bankvidhya_bineeshNo ratings yet

- Sathyabama: Register NumberDocument3 pagesSathyabama: Register NumberBoopalanElumalaiNo ratings yet

- Ec1312 QBDocument7 pagesEc1312 QBGopinathan MuthusamyNo ratings yet

- Assignment 1 DSDDocument2 pagesAssignment 1 DSDsarala tNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Ia1 DPSDDocument2 pagesIa1 DPSDRaja BenitaNo ratings yet

- 4 EEE EE2255-ModelDocument2 pages4 EEE EE2255-ModelBIBIN CHIDAMBARANATHANNo ratings yet

- 21 - 2010 - Nov - R09 - STLDDocument8 pages21 - 2010 - Nov - R09 - STLDvasuvlsiNo ratings yet

- 3CS3 04 PDFDocument3 pages3CS3 04 PDFprashantvlsiNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- Ap9212 AdsdDocument12 pagesAp9212 AdsdKartheeswaran Arumugam33% (3)

- United International University (UIU) : Dept. of Computer Science& Engineering (CSE)Document2 pagesUnited International University (UIU) : Dept. of Computer Science& Engineering (CSE)mahbub mitulNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- STLD Question BankDocument6 pagesSTLD Question Bankrachasaikiran0% (1)

- Digital Logic Circuits Exam QuestionsDocument3 pagesDigital Logic Circuits Exam QuestionsecessecNo ratings yet

- Switching Theory and Logic Design QuestionsDocument8 pagesSwitching Theory and Logic Design QuestionsvasuvlsiNo ratings yet

- DLC Series IaDocument1 pageDLC Series IaAnusha NatarajanNo ratings yet

- Question Bank - ADSD ET7101Document7 pagesQuestion Bank - ADSD ET7101karthikamageshNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- Sample Question Paper - Principles of Digital Techniques-12069Document4 pagesSample Question Paper - Principles of Digital Techniques-12069Jackson AnthonyNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- KEE401 ASSIGNMENTS and QUESTION BANKDocument17 pagesKEE401 ASSIGNMENTS and QUESTION BANKPrince VermaNo ratings yet

- 15es3gcdec Jan 2018Document2 pages15es3gcdec Jan 2018MAHESHA GNo ratings yet

- Signature of Invigilator, Examiner, Marks, NAME, ROLL NO, Logic Circuits MCQDocument4 pagesSignature of Invigilator, Examiner, Marks, NAME, ROLL NO, Logic Circuits MCQsreekantha2013No ratings yet

- EC207 Logic Circuit Design Question Bank Part ADocument6 pagesEC207 Logic Circuit Design Question Bank Part AReshna ShowkathNo ratings yet

- Question Bank For DLCDocument8 pagesQuestion Bank For DLCAvina AshNo ratings yet

- Analog and Digital CircuitsDocument2 pagesAnalog and Digital CircuitsNipun JainNo ratings yet

- April 2005 WithsloutionDocument21 pagesApril 2005 Withsloutionapi-3755462No ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- Bharath Niketan Engineering College: HoursDocument2 pagesBharath Niketan Engineering College: HourseeeNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Javascript DOMDocument67 pagesJavascript DOMParandaman Sampathkumar SNo ratings yet

- DBMS Question BankDocument4 pagesDBMS Question Banksree_lakshmiNo ratings yet

- Symbol TableDocument3 pagesSymbol TableParandaman Sampathkumar SNo ratings yet

- File IO OperationsDocument2 pagesFile IO OperationsParandaman Sampathkumar SNo ratings yet

- Lossless Join and Dependency PreservingDocument1 pageLossless Join and Dependency PreservingParandaman Sampathkumar SNo ratings yet

- DBMS Question BankDocument4 pagesDBMS Question Banksree_lakshmiNo ratings yet

- Javascript Programs QuestionsDocument4 pagesJavascript Programs QuestionsParandaman Sampathkumar SNo ratings yet

- HTML Assignment 1: Your Page Must Contain The FollowingDocument2 pagesHTML Assignment 1: Your Page Must Contain The FollowingParandaman Sampathkumar SNo ratings yet

- STL Containers & IteratorsDocument36 pagesSTL Containers & IteratorsParandaman Sampathkumar SNo ratings yet

- Introduction to XML and Web ServicesDocument6 pagesIntroduction to XML and Web ServicesParandaman Sampathkumar SNo ratings yet

- 16 DOMTreeDocument30 pages16 DOMTreeParandaman Sampathkumar SNo ratings yet

- Assignment QuestionsDocument2 pagesAssignment QuestionsParandaman Sampathkumar SNo ratings yet

- Ryptography and Etwork Ecurity: Advanced Encryption Standard (Aes)Document23 pagesRyptography and Etwork Ecurity: Advanced Encryption Standard (Aes)Parandaman Sampathkumar SNo ratings yet

- Cs6301 PQT MCQ II ItDocument9 pagesCs6301 PQT MCQ II ItParandaman Sampathkumar SNo ratings yet

- OOPS & DS Question BankDocument5 pagesOOPS & DS Question BankParandaman Sampathkumar SNo ratings yet

- Introduction To Big Data & Basic Data AnalysisDocument47 pagesIntroduction To Big Data & Basic Data Analysissuyashdwivedi23No ratings yet

- CS Engineering Computer Programming Assignment Binary Octal Hex ConversionsDocument1 pageCS Engineering Computer Programming Assignment Binary Octal Hex ConversionsParandaman Sampathkumar SNo ratings yet

- Object Oriented Programming and Data Structures Assignment QuestionsDocument2 pagesObject Oriented Programming and Data Structures Assignment QuestionsParandaman Sampathkumar SNo ratings yet

- Digital Electronics VivaDocument23 pagesDigital Electronics VivaParandaman Sampathkumar SNo ratings yet

- Muffling of Cell Phones at Constrained LocaleDocument1 pageMuffling of Cell Phones at Constrained LocaleParandaman Sampathkumar SNo ratings yet

- OOPS & DS Virtual LabDocument50 pagesOOPS & DS Virtual LabParandaman Sampathkumar SNo ratings yet

- Pass 2 Direct Linking LoaderDocument4 pagesPass 2 Direct Linking LoaderParandaman Sampathkumar SNo ratings yet

- Module 3: Programmable Logic Devices (PLDS) Introduction To Micro-Processors and Micro-ControllersDocument36 pagesModule 3: Programmable Logic Devices (PLDS) Introduction To Micro-Processors and Micro-ControllersDhanish KumarNo ratings yet

- EENG212 - Algorithms & Data Structures: StacksDocument5 pagesEENG212 - Algorithms & Data Structures: StacksMuhammad Waqas SheikhNo ratings yet

- Pass 2 Direct Linking LoaderDocument4 pagesPass 2 Direct Linking LoaderParandaman Sampathkumar SNo ratings yet

- C Programming Viva 3 QuestionDocument2 pagesC Programming Viva 3 QuestionParandaman Sampathkumar SNo ratings yet

- Develop A Template of Linked List Class and Its MethodsDocument7 pagesDevelop A Template of Linked List Class and Its MethodsParandaman Sampathkumar SNo ratings yet

- C Programming Viva Questions for InterviewsDocument5 pagesC Programming Viva Questions for InterviewsParandaman Sampathkumar SNo ratings yet

- Lab PDS QuestionDocument1 pageLab PDS QuestionParandaman Sampathkumar SNo ratings yet