Professional Documents

Culture Documents

Digital Logic Circuits Exam Questions

Uploaded by

ecessecOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Logic Circuits Exam Questions

Uploaded by

ecessecCopyright:

Available Formats

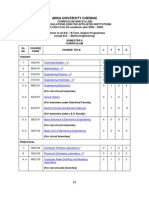

Reg. No.

Question Paper Code:

E3090

B.E./B.Tech. DEGREE EXAMINATION, APRIL/MAY 2010 Fourth Semester

Electrical and Electronics Engineering

EE2255 DIGITAL LOGIC CIRCUITS (Regulation 2008) Time: Three hours Answer ALL Questions PART A (10 2 = 20 Marks) 1. Show that (a) (b) 2.

a + a' b = a + b

x ' y' z + x ' yz + xy' = x ' z + xy' .

Draw the Truth table and logic circuit of half adder. Draw the circuit of SR Flip flop.

3. 4. 5. 6. 7. 8.

What are synchronous sequential circuits?

Give the characteristic equation and state diagram of JK flip flop. What is a self starting counter? What is the advantage of PLA over ROM? Which IC family offers (a) low propagation delay, and (b)low power dissipation? Write HDL for half adder. What are the various modeling techniques in HDL?

22 9

9. 10.

22

22 9

Maximum: 100 Marks

PART B (5 16 = 80 Marks) 11. (a) (i) Simplify using k-map

F (w, x , y, z ) = (0,1, 2, 4, 5, 6, 8, 9,12,13,14 ) .

(ii)

Design a BCD to Excess-3 code converter. Or

(b)

(i) (ii)

Solve g (w, x , y, z ) = m (1, 3, 4, 6,11) + d (0, 8,10,12,13) . Design a decimal adder to add two decimal digits.

12.

(a)

Design a synchronous sequential circuit using JK for the given state diagram. (16)

(b) 13. (a)

Design a BCD counter using T flip flop.

22

Or a b c d e f g h f d f g d f g g b c e a c b h a 2

9

Or (16) (16) Design BCD ripple counter using JK flip flop. (b) (i) Reduce the number of states in the following state table. Next state Output Present state x=0 x=1 x=0 x=1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 1 0 (12)

22 9

(ii)

Starting from a, find the output sequence generated with input sequence 01110010011. (4)

22 9

(8) (8) (8) (8)

E 3090

14.

(a)

(i)

(ii)

Repeat the above problem using PLA. Or

(b)

(i)

Compare all the IC logic families based on (1) (2) (3) (4) (5) (6) Power consumption Fan out Power dissipation Propagation delay Switching speed Noise margin.

15.

(a)

Write HDL program for full adder and 4 bit comparator. Or

9

3

(ii)

Describe the different types of memories.

(ii)

Draw the logic diagram for the following module. module seqcrt (A, B, C, Q, CLK) ; input A, B, C, CLK ; output Q ; reg Q, E ;

22

(b)

(i)

Write an HDL behavioral description of JK flip flop using if-else statement based on the value of present state. (8) (8)

always @ (Posedge CLK) begin E<=A&B;

22 9

Q < = E/C ; end

end module

22 9

(8) (8) (8) (16)

Design a combinatorial circuit using ROM. The circuit accepts 3-bit number and generates an output binary number equal to square of input number. (8)

E 3090

You might also like

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- Digital Logic Circuits Model Exam QuestionsDocument2 pagesDigital Logic Circuits Model Exam QuestionsreporterrajiniNo ratings yet

- December 2011: Amiete - Et (Old Scheme)Document4 pagesDecember 2011: Amiete - Et (Old Scheme)Anurag RanaNo ratings yet

- B.E./B.Tech. Degree Examination, Novembewdecember 2007Document3 pagesB.E./B.Tech. Degree Examination, Novembewdecember 2007vsalaiselvamNo ratings yet

- apr - may 2023Document3 pagesapr - may 2023Pandyselvi BalasubramanianNo ratings yet

- Cs PaperDocument37 pagesCs PaperAshish BokilNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- STLD Regular Jntu Question Papers 2008Document9 pagesSTLD Regular Jntu Question Papers 2008anjaneyulud100% (1)

- Question Bank For DLCDocument8 pagesQuestion Bank For DLCAvina AshNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument3 pages3 Hours / 70 Marks: Seat NoFack AccountNo ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- 4 EEE EE2255-ModelDocument2 pages4 EEE EE2255-ModelBIBIN CHIDAMBARANATHANNo ratings yet

- CS 2202 - Digital Principles and Systems DesignDocument3 pagesCS 2202 - Digital Principles and Systems DesignDhilip PrabakaranNo ratings yet

- Me2255 Electronics and MicroprocDocument2 pagesMe2255 Electronics and MicroprocBalaji PalanisamyNo ratings yet

- 6C0065Document4 pages6C0065Joshua prabuNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- Signature of Invigilator, Examiner, Marks, NAME, ROLL NO, Logic Circuits MCQDocument4 pagesSignature of Invigilator, Examiner, Marks, NAME, ROLL NO, Logic Circuits MCQsreekantha2013No ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- DLCDocument1 pageDLCrjvenkiNo ratings yet

- Digital Techniques Sample Question PaperDocument5 pagesDigital Techniques Sample Question PaperAshutosh PatilNo ratings yet

- EC8392-Digital EletronicsDocument2 pagesEC8392-Digital Eletronicssyed1188No ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Ee2255 - Digital Logic Circuits April-May 2010Document3 pagesEe2255 - Digital Logic Circuits April-May 2010kibrom atsbhaNo ratings yet

- Ec2203-Digital Electronics Question BankDocument22 pagesEc2203-Digital Electronics Question BankRamadhuraiNo ratings yet

- Principles of Digital Techniques On Web PDFDocument5 pagesPrinciples of Digital Techniques On Web PDFmdwalunjkar3095No ratings yet

- DLC Model IDocument2 pagesDLC Model IEEE DEPTNo ratings yet

- Ac03 At03Document4 pagesAc03 At03Navaneeth NairNo ratings yet

- 21 - 2010 - Nov - R09 - STLDDocument8 pages21 - 2010 - Nov - R09 - STLDvasuvlsiNo ratings yet

- DLD question bankDocument5 pagesDLD question bankHarshad ThiteNo ratings yet

- DLC Series IaDocument1 pageDLC Series IaAnusha NatarajanNo ratings yet

- nov - dec 2021Document3 pagesnov - dec 2021Pandyselvi BalasubramanianNo ratings yet

- Q 6Document3 pagesQ 6Saranya MohanNo ratings yet

- r05321404 Linear and Digital Ic ApplicationsDocument7 pagesr05321404 Linear and Digital Ic ApplicationsSRINIVASA RAO GANTANo ratings yet

- JanuaryFebruary 2021Document1 pageJanuaryFebruary 2021vishwatejkachu944No ratings yet

- 2007 Anna University B.E Electrical and Electronics Digital Systems Question PaperDocument3 pages2007 Anna University B.E Electrical and Electronics Digital Systems Question PapernarencharuNo ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- EE3302-DLC MODEL QP UpdatedDocument3 pagesEE3302-DLC MODEL QP UpdatedKeerthana SahadevanNo ratings yet

- Electrical, Digital and Industrial Circuits: IT IL IcDocument4 pagesElectrical, Digital and Industrial Circuits: IT IL IcNGOUNENo ratings yet

- Rr311901 Digital Systems DesignDocument8 pagesRr311901 Digital Systems DesignSrinivasa Rao GNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Monica NareshNo ratings yet

- EE8351 Iq 16 Marks PDFDocument7 pagesEE8351 Iq 16 Marks PDFdeepika senthilNo ratings yet

- Sample Question Paper - Principles of Digital Techniques-12069Document4 pagesSample Question Paper - Principles of Digital Techniques-12069Jackson AnthonyNo ratings yet

- 08AC304 - DIGITAL ELECTRONICSDocument3 pages08AC304 - DIGITAL ELECTRONICSChandru RamaswamyNo ratings yet

- Bharath Niketan Engineering College: HoursDocument2 pagesBharath Niketan Engineering College: HourseeeNo ratings yet

- 3CS3 04 PDFDocument3 pages3CS3 04 PDFprashantvlsiNo ratings yet

- Ec2203 Digital Electronics r8Document3 pagesEc2203 Digital Electronics r8jenifar777No ratings yet

- Switching Theory and Logic Design QuestionsDocument8 pagesSwitching Theory and Logic Design QuestionsvasuvlsiNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- R5 210504 Digital Logic DesignDocument1 pageR5 210504 Digital Logic DesignsivabharathamurthyNo ratings yet

- Digital Electronics QBDocument7 pagesDigital Electronics QBvinaytmkNo ratings yet

- E Mic ND06Document3 pagesE Mic ND06bhagyampNo ratings yet

- Univ Question Paper LICDocument8 pagesUniv Question Paper LICVishnu Priya A KNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- SyllabusDocument118 pagesSyllabusecessecNo ratings yet

- Digital Implementation of Sinusoidal Pulse Width Modulation GeneratorDocument4 pagesDigital Implementation of Sinusoidal Pulse Width Modulation GeneratorecessecNo ratings yet

- Hardware Implementation of A Digital Watermarking System For Video AuthenticationDocument13 pagesHardware Implementation of A Digital Watermarking System For Video Authenticationaasraj_saraNo ratings yet

- Lab Requirements of Ece: Infrastructure Requirement As Per Aicte NormsDocument4 pagesLab Requirements of Ece: Infrastructure Requirement As Per Aicte NormsecessecNo ratings yet

- Digital Implementation of Sinusoidal Pulse Width Modulation GeneratorDocument4 pagesDigital Implementation of Sinusoidal Pulse Width Modulation GeneratorecessecNo ratings yet

- Jpeg 2000 PDFDocument5 pagesJpeg 2000 PDFecessecNo ratings yet

- Hardware Implementation of A Digital Watermarking System For Video AuthenticationDocument13 pagesHardware Implementation of A Digital Watermarking System For Video Authenticationaasraj_saraNo ratings yet

- VLSI Implementation of A Low-Cost High-Quality Image Scaling ProcessorDocument5 pagesVLSI Implementation of A Low-Cost High-Quality Image Scaling ProcessorManish BansalNo ratings yet

- M.E. Degree Examination, April-May 201177907Document2 pagesM.E. Degree Examination, April-May 201177907Joshua DuffyNo ratings yet

- Adaptive Computationally Scalable Motion Estimation For The Hardware H.264AVC Encoder PDFDocument11 pagesAdaptive Computationally Scalable Motion Estimation For The Hardware H.264AVC Encoder PDFecessecNo ratings yet

- VHDL FirDocument21 pagesVHDL FirSiva ChaitanyaNo ratings yet

- Low Power Vlsi Question PaperDocument2 pagesLow Power Vlsi Question Paperustadkrishna100% (3)

- A High Performance Video Transform Engine by PDFDocument10 pagesA High Performance Video Transform Engine by PDFecessecNo ratings yet

- Jpeg 2000 PDFDocument5 pagesJpeg 2000 PDFecessecNo ratings yet

- Solution Manual of Statistical Digital Signal Processing Modeling by MonsonHDocument315 pagesSolution Manual of Statistical Digital Signal Processing Modeling by MonsonHManuel Dominguez83% (29)

- Ec 2 Simulation Lab manuALDocument56 pagesEc 2 Simulation Lab manuALecessecNo ratings yet

- DLC Question BankDocument9 pagesDLC Question BankecessecNo ratings yet

- Orcad Pspice 16Document86 pagesOrcad Pspice 16Hailin ArumigaNo ratings yet

- AnalogDocument38 pagesAnalogecessecNo ratings yet

- DLC Question BankDocument9 pagesDLC Question BankecessecNo ratings yet

- Ec 2 Simulation Lab manuALDocument56 pagesEc 2 Simulation Lab manuALecessecNo ratings yet

- 2nd Sem - Anna UnivDocument27 pages2nd Sem - Anna UnivDeepak RamaswamyNo ratings yet

- 2nd Sem - Anna UnivDocument27 pages2nd Sem - Anna UnivDeepak RamaswamyNo ratings yet

- Electrical Circuit Lab ManualDocument38 pagesElectrical Circuit Lab Manualecessec67% (3)

- 2nd Sem - Anna UnivDocument27 pages2nd Sem - Anna UnivDeepak RamaswamyNo ratings yet