Professional Documents

Culture Documents

Digital Implementation of Sinusoidal Pulse Width Modulation Generator

Uploaded by

ecessecCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Implementation of Sinusoidal Pulse Width Modulation Generator

Uploaded by

ecessecCopyright:

Available Formats

INTERNATIONAL JOURNAL OF TECHNOLOGY ENHANCEMENTS AND EMERGING ENGINEERING RESEARCH, VOL 2, ISSUE 4 27

ISSN 2347-4289

Copyright 2014 IJTEEE.

Digital Implementation Of Sinusoidal Pulse Width

Modulation Generator

R.Sriram, P.Muthu Kumaran

P.G Student, Department of Electronics and Communication Engineering, Sree Sakthi Engineering College, Coimbatore, India;

Asst.Prof, Department of Electronics and Communication Engineering, Sree Sakthi Engineering College, Coimbatore, India.

sriram.ctp@gmail.com, muthukumaran23@gmail.com

ABSTRACT: This is the digital implementations of Sinusoidal Pulse Width Modulation (SPWM) generators based on analog circuits. The FPGA based

SPWM generator is capable to operate at switching frequencies up to 3 MHz, thus it is capable to support the high switching frequency requirements of

modern single-phase dc/ac power converters. The Existing design the switching operation is in 1 MHz. Additionally, in this proposed project it is modified

to increase the switching frequency upto 3 MHz and flexible architecture that can be tuned to a variety of single-phase dc/ac inverter applications which

exhibits much faster switching frequency, lower power consumption, and higher accuracy of generating the desired SPWM waveform.

Keywords: Sinusoidal Pulse Width Modulation (SPWM), Field Programmable Gate Array (FPGA), Direct Digital Synthesis (DDS), Digital Clock Manager

(DCM)

1 INTRODUCTION

THE dc/ac converters (inverters) are the major power electron-

ic conversion units in renewable energy production, motor

drive, and uninterruptible power supply applications. A simpli-

fied block diagram of a single-phase, full bridge dc/ac power

converter (inverter) is depicted. The Sinusoidal Pulse Width

Modulation (SPWM) technique is widely employed in order to

adjust the dc/ac inverter output voltage amplitude and fre-

quency to the desired value. In this case, the power converter

switches are set to the ON or OFF state according to the result

of the comparison between a high-frequency, constant-

amplitude triangular wave (carrier) with two low-frequencies

(e.g., 50 Hz) reference sine waves of adjustable amplitude

and/or frequency.

2 EXISTING SYSTEM

The unipolar SPWM technique generate pulses are either pos-

itive or negative during each half period of the SPWM wave.

Increasing the switching frequency of the triangular wave f

c

results in a reduction of the dc/ac inverter output filter size and

cost. Depending on their nominal power rating, the dc/ac in-

verters typically operate at switching frequencies in the range

of 1100 kHz. This trend of increasing the operating switching

frequency is expected to continue in the near future due to the

recent development of Silicon Carbide power semiconductors,

such as JFETs, MOSFETs and Schottky diodes which are ca-

pable to operate at switching frequencies up to 3 MHz with

low-power losses .The digital SPWM generator implementa-

tions have dominated over their counterparts based on analog

circuits, since they offer higher noise immunity and less sus-

ceptibility to voltage and temperature variations.

Fig 1: Single-phase DC/AC power converter

Fig 2: Unipolar SPWM Techniques

2.1 ALGORITHM TECHNIQUE

Targeting at the reduction of the SPWM generator memory

requirements, the sinusoidal wave is produced in using an

FPGA-based implementation of the Coordinate Rotation Digi-

tal Computer (CORDIC) algorithm. A 5-kHz switching frequen-

cy has been achieved in this case. Although this implementa-

tion does not require the use of a hardware multiplier, it is cha-

racterized by a slower speed compared to the LUT-based

SPWM units. The CORDIC algorithm has also been applied

for the development of an integrated circuit performing the

generation of a 5-kHz SPWM wave using 0.18-m CMOS

technology. An LUT is used to store the reference sine-wave

digital values corresponding to the time instants of the peaks

and nadirs of the triangular wave. The width of each pulse is

calculated using an equation based on the similarity of the

triangles ABC and ADF depicted in Fig. 3.1. (b). This design

method has been validated in case of a 1-kHz switching fre-

quency.

2.2 Direct Digital Synthesis (DDS)

The SPWM pulse train is produced by comparing the sinu-

soidal and triangular signals generated according to the direct

digital synthesis (DDS) technique. The comparison is per-

formed using a high-speed analog comparator. The DDS ap-

proach is also used for the development of a digital SPWM

generator chip using 0.35-m CMOS technology. The maxi-

mum clock frequency of this chip is 50 MHz. The SPWM unit is

composed of a DSP chip accomplishing the calculation of the

widths of the individual pulses comprising the SPWM wave,

INTERNATIONAL JOURNAL OF TECHNOLOGY ENHANCEMENTS AND EMERGING ENGINEERING RESEARCH, VOL 2, ISSUE 4 28

ISSN 2347-4289

Copyright 2014 IJTEEE.

which communicates through a parallel port with an FPGA-

based unit producing the SPWM control signals. The regular-

sampled PWM technique presented targets to reduce the

amount of computation time required in order to facilitate the

generation of higher switching frequencies online and in real

time. In this technique, the pulse width is calculated once and

used over N consecutive switching edges of the SPWM wave

pulses. Then, a new sample of the reference sine wave is ac-

quired. Thus, the sampling frequency f

s

is reduced by an in-

teger factor of N, resulting in the following relationship with the

corresponding carrier frequency f

c

f

s

= f

c

N

Consequently, the number of calculations required to produce

the complete SPWM waveform is N times less than in the con-

ventional SPWM generation methods. A common disadvan-

tage of the previously proposed SPWM generators described

previously is that they have been designed to operate at low-

switching frequencies, f

c

(i.e., 120 kHz), while their operation

at higher switching frequencies has not been explored yet. In

this paper, an FPGA-based SPWM generator is presented,

which is capable to operate at switching frequencies up to 1

MHz; thus, it is capable to support the high switching frequen-

cy requirements of modern single-phase dc/ac power conver-

ters. Compared to the past-proposed SPWM generators, in

the proposed architecture the values of both the reference

sine and triangular waves are stored in the FPGA device Block

RAMs (BRAMs) in order to exploit their one-clock cycle access

time, thus providing a much higher switching frequency capa-

bility. The proposed design exhibits architectural flexibility fea-

tures, enabling the change of the SPWM switching frequency

and modulation index either internally, or externally. The pro-

posed SPWM unit has been implemented in a single chip in

order to enable the reduction of the complexity, cost, and de-

velopment time of the dc/ac inverter control unit.

2.3 SPWM Generator

The architecture of the proposed SPWM generation unit is

presented. The system inputs are the modulation index of the

output SPWM wave M in single precision floating point arith-

metic ranging from 0 to 1, as well as the clock and reset

signals. The architecture of the proposed system has been

built using 8-bit fixed-point arithmetic and it consists of five

subsystems, which implement the SPWM generation algo-

rithm.

Fig 3: Architecture of the proposed SPWM generation unit.

3 SPWM GENERATOR SUBSYTEM

3.1 Clock Generator Subsystem

The Clock generator subsystem takes as input the FPGA

input clock and produces a new clock signal used by the digi-

tal circuits of the proposed SPWM generator, such that the

desired SPWM switching frequency fc specified by the de-

signer/user is generated. A two-state finite state machine

(FSM) is initially used to set the input clock frequency f clk to f

clk/2 and then a Digital Clock Manager module adapts this

frequency to the desired value. The Very high speed inte-

grated circuit Hardware Description Language (VHDL) code of

the DCM module. The FSM is kept constant for every different

switching frequency, while only the operational parameters

CLKFX_MULTIPLY and CLKFX_DIVIDE of the DCM mod-

ule are changed according to the switching frequency re-

quirements of the SPWM output waveform. Thus, the pro-

posed SPWM generator is flexible to be adapted to the gener-

ation of any operating switching frequency specified by the

system designer/user.

3.2 Sine-Carrier Subsystem

The Sine-Carrier subsystem consists of the control unit, two

BRAMs, which contain samples of the sinusoidal and triangu-

lar (i.e., carrier) waves and two multiplexers that produce the

two constant-amplitude reference sine waves used for the

production of the SPWM output signals. The BRAMs of the

sine wave and carrier operate as LUTs. Both the sinusoidal

and triangular waves are sampled and quantized with the

same sampling frequency fs using MATLAB (e.g., fs = 4, 8

MHz, etc.). In order to minimize the utilization of the FPGA

resources, only the values of the first quarter of the constant-

amplitude sine-wave period (i.e., during the time interval 0

/2) are stored in the corresponding BRAM, while the values

of the sine wave during the time interval /2 2 are calcu-

lated by mirroring and inverting the values of the first quarter.

The BRAM of the carrier contains the values of a complete

period of the reference triangular wave. Consecutive ad-

dresses of both memories (Sine address and Carrier ad-

dress, respectively) are generated in every clock cycle by the

control unit. The control unit also produces a flag signal,

which is responsible.

3.3 Adjustable Amplitude Sine Subsystem

The Adjustable amplitude sine subsystem takes as input the

constant-amplitude reference sinusoidal values produced by

the Sine-Carrier subsystem and generates a sinusoidal digi-

tal signal ya with amplitude adjustable according to the value

of the modulation index M which is an input in the proposed

SPWM generation system. The value of ya is in the range 0

255 and it is calculated and the value of the constant-

amplitude reference sine wave and Index is the output of the

Modulation Index subsystem.

3.4 Comparison Subsytem

The Comparison subsystem implements the comparison

between the high-frequency constant-amplitude triangular

waves (carrier) with the two low-frequency reference sine

waves, using two comparators (COMP). The control signals

Ta+, Ta, Tb+, and Tb of the single-phase dc/ac inverter

power switches depicted are generated from the outputs of

the corresponding comparators of this subsystem, thus form-

ing the SPWM wave (Vspwm ) at the dc/ac inverter output

INTERNATIONAL JOURNAL OF TECHNOLOGY ENHANCEMENTS AND EMERGING ENGINEERING RESEARCH, VOL 2, ISSUE 4 29

ISSN 2347-4289

Copyright 2014 IJTEEE.

terminals. The outputs of the comparators in the Comparison

subsystem (i.e., control signals Ta+ and Tb+) are equal to one

when the corresponding output of the Adjustable amplitude

sine subsystem described in Section II- by inverting Ta+ and

Tb+, respectively. C is equal to or greater than the current digi-

tal value of the carrier signal. The DC/AC inverter control sig-

nals Ta and Tb are produced

4 PROPOSED SYSTEM

An FPGA-based SPWM generator has been presented, which

is capable to operate at switching frequencies up to 1 MHz,

thus it is able to support the high switching frequency require-

ments of modern single-phase dc/ac inverters. The proposed

design occupies a small fraction of a medium sized FPGA and,

thus, can be incorporated in larger design, while it has a flexi-

ble architecture can be adapted to a variety of single-phase

dc/ac inverter applications. Both post place and route simula-

tion results and experimental verification results on actual

hardware were presented, demonstrating the successful oper-

ation of the proposed SPWM generator at high switching fre-

quencies. The proposed SPWM generation techniques were

also implemented and their performance was compared. The

post layout simulation and experimental results confirm that

the proposed SPWM generator exhibits much faster switching

frequency, lower power consumption, and higher accuracy of

generating the desired SPWM waveform.

5 SIMULATION RESULTS

The proposed network design configured with a 4-bit data

width is simulated by using ModelSim SE 6.3 tool. The 4-bit

data width is chosen mainly for testing purpose, data width

can be easily sized according to the requirements of real ap-

plications. Three kinds of switches are designed for the pro-

posed on-chip network. These switches are all based on

common switch architecture and the single switch simulation

result is shown.

Fig 4: sine wave generation

Fig 5: Triangular (Carrier) wave generation

Fig6: Output waveform of Comparison of Sine wave with ref-

erence carrier waveform

6 FUTURE WORK

In the existing work by Improvement in Design of Control Cir-

cuit to increase the frequency up to 3Mhz and reduce power

consumption of Sinusoidal Pulse Width Modulation (SPWM)

Generator.

7 CONCLUSION

The SPWM principle is widely used in dc/ac inverters in ener-

gy conversion and motor drive applications. The past pro-

posed SPWM generators have been designed to operate at

low switching frequencies (i.e., 120 kHz), while their opera-

tion at higher switching frequencies had not been explored so

far.

INTERNATIONAL JOURNAL OF TECHNOLOGY ENHANCEMENTS AND EMERGING ENGINEERING RESEARCH, VOL 2, ISSUE 4 30

ISSN 2347-4289

Copyright 2014 IJTEEE.

REFERENCES

[1]. M. Lakka, E. Koutroulis, and A. Dollas, Development

of an FPGA-Based SPWM Generator for High Switch-

ing Frequency DC/AC Inverters, IEEE Trans.Pwr.

Electron, vol.. 29, NO. 1, Jan 2014.

[2]. M. Hava and N. O. C etin, A generalized scalar

PWM approach with easy implementation features for

three-phase, three-wire voltage-source inverters,

IEEE Trans. Power Electron., vol. 26, no. 5, pp.1385

1395, May 2011.

[3]. L. Lei, W. Tian-yu, and X. Wen-guo, Application of

sinusoidal pulse width modulation algorithm in the

grid-connected photovoltaic system, in Proc. Int.

Conf. Inf. Technol., Comput. Eng. Manage. Sci.,

2011, vol. 2, pp. 254257.

[4]. Maiti, S. Choudhuri, J. Bera, T. Banerjee, and S. Mai-

tra, Development of microcontroller based single

phase SPWM inverter with remote control facility, in

Proc. Joint Int. Conf. Power Electron., Drives Energy

Syst./Power India, 2010.

[5]. D. Navarro, O. Lucic, L. A. Barragan, J. I. Artigas, I.

Urriza, and O. Jimennez, Synchronous FPGA-based

high-resolution implementations of digital pulse-width

modulators, IEEE Trans. Power Electron., vol. 27,

no. 5, pp. 25152525, May 2012.

[6]. N. D. Patel and U. K. Madawala, A bit-stream-based

PWM technique for sine-wave generation, IEEE

Trans. Ind. Electron., vol. 56, no. 7, pp. 25302539,

Jul. 2009.

[7]. R. K. Pongiannan, S. Paramasivam, and N. Yadaiah,

Dynamically reconfigurable PWM controller for three-

phase voltage-source inverters, IEEE Trans. Power

Electron., vol. 26, no. 6, pp. 17901799, Jun. 2011.

[8]. J. Valle-Mayorga, C. P. Gutshall, K. M. Phan, I. Es-

corcia-Carranza, H. A. Mantooth, B. Reese, M.

Schupbach, and A. Lostetter, Hightemperature sili-

con-on-insulator gate driver for SiC-FET powermo-

dules, IEEE Trans. Power Electron., vol. 27, no. 11,

pp. 44174424, Nov. 2012.

[9]. S. A. Saleh andM. A. Rahman, Experimental perfor-

mances of the singlephase wavelet-modulated inver-

ter, IEEE Trans. Power Electron., vol. 26, no. 9, pp.

26502661, Sep. 2011.

[10]. J. Valle-Mayorga, C. P. Gutshall, K. M. Phan, I. Es-

corcia-Carranza, H. A. Mantooth, B. Reese, M.

Schupbach, and A. Lostetter, Hightemperature sili-

con-on-insulator gate driver for SiC-FET powermo-

dules, IEEE Trans. Power Electron., vol. 27, no. 11,

pp. 44174424, Nov. 2012.

You might also like

- Hardware Implementation of A Digital Watermarking System For Video AuthenticationDocument13 pagesHardware Implementation of A Digital Watermarking System For Video Authenticationaasraj_saraNo ratings yet

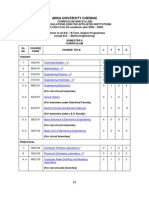

- Lab Requirements of Ece: Infrastructure Requirement As Per Aicte NormsDocument4 pagesLab Requirements of Ece: Infrastructure Requirement As Per Aicte NormsecessecNo ratings yet

- Digital Implementation of Sinusoidal Pulse Width Modulation GeneratorDocument4 pagesDigital Implementation of Sinusoidal Pulse Width Modulation GeneratorecessecNo ratings yet

- SyllabusDocument118 pagesSyllabusecessecNo ratings yet

- Jpeg 2000 PDFDocument5 pagesJpeg 2000 PDFecessecNo ratings yet

- VLSI Implementation of A Low-Cost High-Quality Image Scaling ProcessorDocument5 pagesVLSI Implementation of A Low-Cost High-Quality Image Scaling ProcessorManish BansalNo ratings yet

- A High Performance Video Transform Engine by PDFDocument10 pagesA High Performance Video Transform Engine by PDFecessecNo ratings yet

- Hardware Implementation of A Digital Watermarking System For Video AuthenticationDocument13 pagesHardware Implementation of A Digital Watermarking System For Video Authenticationaasraj_saraNo ratings yet

- Jpeg 2000 PDFDocument5 pagesJpeg 2000 PDFecessecNo ratings yet

- DLC Question BankDocument9 pagesDLC Question BankecessecNo ratings yet

- Adaptive Computationally Scalable Motion Estimation For The Hardware H.264AVC Encoder PDFDocument11 pagesAdaptive Computationally Scalable Motion Estimation For The Hardware H.264AVC Encoder PDFecessecNo ratings yet

- Low Power Vlsi Question PaperDocument2 pagesLow Power Vlsi Question Paperustadkrishna100% (3)

- M.E. Degree Examination, April-May 201177907Document2 pagesM.E. Degree Examination, April-May 201177907Joshua DuffyNo ratings yet

- VHDL FirDocument21 pagesVHDL FirSiva ChaitanyaNo ratings yet

- DLC Question BankDocument9 pagesDLC Question BankecessecNo ratings yet

- Digital Logic Circuits Exam QuestionsDocument3 pagesDigital Logic Circuits Exam QuestionsecessecNo ratings yet

- Ec 2 Simulation Lab manuALDocument56 pagesEc 2 Simulation Lab manuALecessecNo ratings yet

- 2nd Sem - Anna UnivDocument27 pages2nd Sem - Anna UnivDeepak RamaswamyNo ratings yet

- Orcad Pspice 16Document86 pagesOrcad Pspice 16Hailin ArumigaNo ratings yet

- AnalogDocument38 pagesAnalogecessecNo ratings yet

- Solution Manual of Statistical Digital Signal Processing Modeling by MonsonHDocument315 pagesSolution Manual of Statistical Digital Signal Processing Modeling by MonsonHManuel Dominguez83% (29)

- 2nd Sem - Anna UnivDocument27 pages2nd Sem - Anna UnivDeepak RamaswamyNo ratings yet

- 2nd Sem - Anna UnivDocument27 pages2nd Sem - Anna UnivDeepak RamaswamyNo ratings yet

- Ec 2 Simulation Lab manuALDocument56 pagesEc 2 Simulation Lab manuALecessecNo ratings yet

- Electrical Circuit Lab ManualDocument38 pagesElectrical Circuit Lab Manualecessec67% (3)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Philippine Christian University Graduate School of Business and Management Integrated Syllabi ModuleDocument5 pagesPhilippine Christian University Graduate School of Business and Management Integrated Syllabi ModuleRoselle Anne Luna GuatatoNo ratings yet

- Crash of Air France ConcordeDocument11 pagesCrash of Air France ConcordeAhmad Aimi SafuanNo ratings yet

- Safety Data Sheet: Flexa SoftDocument9 pagesSafety Data Sheet: Flexa SoftSercan şahinkayaNo ratings yet

- Manhole bill of materialsDocument1 pageManhole bill of materialsjalNo ratings yet

- Apparent Dip PDFDocument2 pagesApparent Dip PDFanon_114803412No ratings yet

- Som-Ii Uqb 2019-20Document23 pagesSom-Ii Uqb 2019-20VENKATESH METHRINo ratings yet

- CAPS LESSON PLAN, KAHOOT QUIZ, PPT VIDEODocument3 pagesCAPS LESSON PLAN, KAHOOT QUIZ, PPT VIDEOMandisa MselekuNo ratings yet

- B1 UDO Trace LogDocument14 pagesB1 UDO Trace LogCh M KashifNo ratings yet

- LinAlg CompleteDocument331 pagesLinAlg Completes0uizNo ratings yet

- LFJ All OrdersDocument195 pagesLFJ All Orderskate jackNo ratings yet

- HistoryDocument20 pagesHistoryAlexandru RomînuNo ratings yet

- Company Electronics Appliances Semiconductors South Korea's: SamsungDocument61 pagesCompany Electronics Appliances Semiconductors South Korea's: Samsunghaseeb ahmedNo ratings yet

- Report-Teaching English Ministery of EduDocument21 pagesReport-Teaching English Ministery of EduSohrab KhanNo ratings yet

- WordPress Introduction: CMS BasicsDocument21 pagesWordPress Introduction: CMS BasicsNgô Ngọc Hải phươngNo ratings yet

- SECURED TRANSACTION BAR CHECKLISTDocument4 pagesSECURED TRANSACTION BAR CHECKLISTatw4377100% (1)

- Vol 14, No 4 RHADocument20 pagesVol 14, No 4 RHAKawchhar AhammedNo ratings yet

- ACP Programs ListDocument3 pagesACP Programs ListShreeya BhatNo ratings yet

- HackSpace - June 2021Document116 pagesHackSpace - June 2021Somnath100% (1)

- The Electricity Wiring RegulationDocument239 pagesThe Electricity Wiring Regulationgodson50% (2)

- Chapter 2Document5 pagesChapter 2Ayush Hooda class 12 ANo ratings yet

- Telangana Energy Dept Contact NumbersDocument27 pagesTelangana Energy Dept Contact Numbersstarpowerzloans rjyNo ratings yet

- E46 Climate ControlDocument40 pagesE46 Climate Controltykunas100% (3)

- 水印AMSCO® Advanced Placement® European History, 水印2nd Edition (Perfection Learning Authors)Document764 pages水印AMSCO® Advanced Placement® European History, 水印2nd Edition (Perfection Learning Authors)Cherry panNo ratings yet

- A Very Rare Type of NeuralgiaDocument2 pagesA Very Rare Type of NeuralgiarosaNo ratings yet

- EEE111_Multisim_ManualDocument14 pagesEEE111_Multisim_ManualSHADOW manNo ratings yet

- Cognitive Load Theory (John Sweller) : Information ProcessingDocument2 pagesCognitive Load Theory (John Sweller) : Information ProcessingNik ZazlealizaNo ratings yet

- AmboooDocument39 pagesAmboooTesfaye DegefaNo ratings yet

- The 9 Building Blocks of Business ModelsDocument3 pagesThe 9 Building Blocks of Business ModelsTobeFrankNo ratings yet

- VariablesDocument11 pagesVariablesKzy ayanNo ratings yet