Professional Documents

Culture Documents

555 Timer IC: The Important Features of The 555 Timer Are

555 Timer IC: The Important Features of The 555 Timer Are

Uploaded by

Chara GalaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

555 Timer IC: The Important Features of The 555 Timer Are

555 Timer IC: The Important Features of The 555 Timer Are

Uploaded by

Chara GalaCopyright:

Available Formats

555 Timer IC

1.

The output of a 555 timer can drive a transistortransistor logic (TTL) due to its high current

output.

The duty cycle of the timer is adjustable.

The maximum power dissipation per package

is 600 mW and its trigger and reset inputs have

logic compatibility. More features are listed in the

datasheet.

Turn-off time less than 2 s

Max. operating frequency greater than 500

kHz

Timing from microseconds to hours

Operates in both astable and monostable

modes

High output current

Adjustable duty cycle

TTL compatible

Temperature stability of 0.005% per C

Introduction

The 555 timer IC was introduced in the year 1970 by Signetic

Corporation and gave the name SE/NE 555 timer. It is

basically a monolithic timing circuit that produces accurate and

highly stable time delays or oscillation. When compared to the

applications of an op-amp in the same areas, the 555IC is also

equally reliable and is cheap in cost. Apart from its applications

as a monostable multivibrator and astable multivibrator, a

555 timer can also be used in dc-dc converters, digital logic

probes, waveform generators, analog frequency

meters &

tachometers, temperature measurement and control devices,

voltage regulators etc. The timer IC is setup to work in either

of the two modes one-shot or monostabl or as a free-running

or astable multivibrator. The SE 555 can be used for

temperature ranges between 55C to 125. The NE 555 can

be used for a temperature range between 0 to 70C.

DESCRIPTION:

The 555 monolithic timing circuits is a highly

stable controller capable of producing accurate time

delays, or oscillation. In the time delay mode of

operation, the time is precisely controlled by one

external resistor and capacitor. For a stable

operation as an oscillator, the free running

The important features of the 555 timer are:

frequency and the duty cycle are both accurately

It operates from a wide range of power

supplies ranging from + 5 Volts to + 18 Volts

supply voltage.

Sinking or sourcing 200 mA of load current.

The external components should be selected

properly so that the timing intervals can be made

into several minutes along with the frequencies

exceeding several hundred kilo hertz.

controlled with two external resistors and one

capacitor. The circuit maybe triggered and reset on

falling waveforms, and the output structure can

source or sink up to 200 mA.

2.

IC Pin Configuration

the 555 IC output gets a high voltage, and thus a

quasi stable state.

Pin 3: Output Terminal: Output of the timer is available at this pin. There are two ways in which a load can

be connected to the output terminal. One way is to

connect between output pin (pin 3) and ground pin (pin

1) or between pin 3 and supply pin (pin 8). The load

connected between output and ground supply pin is

called the normally on load and that connected

between output and ground pin is called the normally

off load.

Pin 4: Reset Terminal: Whenever the timer IC is to

The 555 Timer IC is available as an 8-pin metal can, an 8pin mini DIP (dual-in-package) or a 14-pin DIP. The pin

configuration is shown in the figures.

This IC consists of 23 transistors, 2 diodes and

16 resistors. The use of each pin in the IC is explained

below. The pin numbers used below refers to the 8-pin DIP

and 8-pin metal can packages.

be reset or disabled, a negative pulse is applied to pin 4,

and thus is named as reset terminal. The output is reset

irrespective of the input condition. When this pin is not to

be used for reset purpose, it should be connected to +

VCC to avoid any possibility of false triggering.

Pin 5: Control Voltage Terminal: The threshold and

trigger levels are controlled using this pin. The pulse

width of the output waveform is determined by

connecting a POT or bringing in an external voltage to

this pin. The external voltage applied to this pin can also

be used to modulate the output waveform. Thus, the

amount of voltage applied in this terminal will decide

when the comparator is to be switched, and thus

changes the pulse width of the output. When this pin is

not used, it should be bypassed to ground through a

0.01 micro Farad to avoid any noise problem.

Pin 6: Threshold Terminal: This is the non-inverting

input terminal of comparator 1, which compares the

voltage applied to the terminal with a reference voltage

of 2/3 VCC. The amplitude of voltage applied to this

terminal is responsible for the set state of flip-flop. When

the voltage applied in this terminal is greater than

2/3Vcc, the upper comparator switches to +Vsat and the

output gets reset.

Pin

Pin 1: Grounded Terminal: All the voltages are measured

with respect to the Ground terminal.

Pin 2: Trigger Terminal: The trigger pin is used to

feed the trigger input hen the 555 IC is set up as a

monostable multivibrator. This pin is an inverting input

of a comparator and is responsible for the transition

of flip-flop from set to reset. The output of the timer

depends on the amplitude of the external trigger

pulse applied to this pin. A negative pulse with a dc

level is greater than Vcc/3 is applied to this terminal.

In the negative edge, as the trigger passes through

Vcc/3, the output of the lower comparator becomes

high and the complimentary of Q becomes zero. Thus

7: Discharge

Terminal: This

pin is

connected internally to the collector of transistor and

mostly a capacitor is connected between this

terminal and ground. It is called discharge terminal

because when transistor saturates, capacitor

discharges through the transistor. When the

transistor is cut-off, the capacitor charges at a rate

determined by the external resistor and capacitor.

Pin 8: Supply Terminal: A supply voltage of + 5

V to + 18 V is applied to this terminal with respect to

ground (pin 1).

3. 555 Timer Basics

value of Q to go high. A high value of R input resets

the value of Q to low. Output Q remains in a given

state until it is triggered into the opposite state.

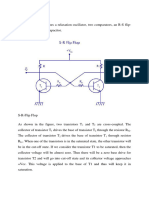

The 555 timer combines a relaxation oscillator, two

comparators, an R-S flip-flop, and a discharge

capacitor. As shown in the figure, two transistors T1

and T2 are cross coupled. The collector of transistor

T1 drives the base of transistor T2 through the

resistor Rb2. The collector of transistor T2 drives the

base of transistor T1 through resistor Rb1. When

one of the transistors is in the saturated state, the

other transistor will be in the cut-off state. If we

consider the transistor T1 to be saturated, then the

collector voltage will be almost zero. Thus there will

be a zero base drive for transistor T2 and will go into

cut-off state and its collector voltage approaches

+Vcc. This voltage is applied to the base of T1 and

thus will keep it in saturation.

Now, if we consider the transistor T1 to be in the cutoff state, then the collector voltage of T1 will be

equal to +Vcc. This voltage will drive the base of the

transistor T2 to saturation. Thus, the saturated

collector output of transistor T2 will be almost zero.

This value when fedback to the base of the transistor

T1 will drive it to cut-off. Thus, the saturation and

cut-off value of anyone of the transistors decides the

high and low value of Q and its compliment. By

adding more components to the circuit, an R-S flipflop is obtained. R-S flip-flop is a circuit that can set

the Q output to high or reset it low. Incidentally, a

complementary (opposite) output Q is available from

the collector of the other transistor. The schematic

symbol for a S-R flip flop is also shown above. The

circuit latches in either the Q state or its

complimentary state. A high value of S input sets the

The block diagram of a 555 timer is shown in the

above figure. A 555 timer has two comparators, which

are basically 2 op-amps), an R-S flip-flop, two

transistors and a resistive network.

Resistive network consists of three equal

resistors and acts as a voltage divider.

Comparator 1 compares threshold voltage

with a reference voltage + 2/3 VCC volts.

Comparator 2 compares the trigger voltage

with a reference voltage + 1/3 VCC volts.

Output of both the comparators is supplied to the flipflop. Flip-flop assumes its state according to the

output of the two comparators. One of the two

transistors is a discharge transistor of which collector

is connected topin 7. This transistor saturates or

cuts-off according to the output state of the flip-flop.

The saturated transistor provides a discharge path to

a capacitor connected externally. Base of another

transistor is connected to a reset terminal. A pulse

applied to this terminal resets the whole timer

irrespective of any input.

You might also like

- Burglar Alarm ProjectDocument4 pagesBurglar Alarm ProjectAvik PathakNo ratings yet

- Inverter Explanation Cd4047Document7 pagesInverter Explanation Cd4047Sruthi Reddy0% (1)

- Currency ListDocument5 pagesCurrency Listanon_878976340100% (1)

- ROI - TCO Calculator v0.4Document29 pagesROI - TCO Calculator v0.4samiransdcNo ratings yet

- SE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orDocument12 pagesSE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orEFraim Manzano FranciscoNo ratings yet

- The Important Features of The 555 Timer AreDocument7 pagesThe Important Features of The 555 Timer ArePathella SudhakarNo ratings yet

- 555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetDocument13 pages555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetΔημητριος ΣταθηςNo ratings yet

- 555 Timer Integrated CircuitDocument8 pages555 Timer Integrated CircuitTalha WaqarNo ratings yet

- IC555 TimerDocument8 pagesIC555 TimerRaflysyah PutraNo ratings yet

- 6.1 IC555 TIMER: Circuit ComponentsDocument8 pages6.1 IC555 TIMER: Circuit ComponentsManish PradhanNo ratings yet

- Timer 555 - ManualDocument20 pagesTimer 555 - ManualXen XeonNo ratings yet

- IC 555 TimerDocument6 pagesIC 555 Timeraditya pandeyNo ratings yet

- 555-Timer Class NotesDocument1 page555-Timer Class NotesPraveen KumarNo ratings yet

- List The Features of 555 TimersDocument3 pagesList The Features of 555 TimersDivyesh DivakarNo ratings yet

- LIC Mod 2Document15 pagesLIC Mod 2Sona PrakashNo ratings yet

- Operation 555 Timer/OscillatorDocument7 pagesOperation 555 Timer/OscillatoryuvakiraniNo ratings yet

- 555 TimerDocument3 pages555 TimerchandrakanthNo ratings yet

- Report IC 555 TimerDocument17 pagesReport IC 555 TimerSantosh YadavNo ratings yet

- Tutorial Timmer 555Document9 pagesTutorial Timmer 555gabrielamedeletNo ratings yet

- Multivibrator CircuitsDocument11 pagesMultivibrator CircuitsSatyaki ChowdhuryNo ratings yet

- Lab#10: Design and Study of IC 555 Multivibrator Circuits (2 Turns)Document11 pagesLab#10: Design and Study of IC 555 Multivibrator Circuits (2 Turns)Ayushman ChoudharyNo ratings yet

- Ic555 TimerDocument5 pagesIc555 Timerps1976No ratings yet

- 555 Integrated Circuit (Timer Operation)Document5 pages555 Integrated Circuit (Timer Operation)Geet SehgalNo ratings yet

- 1 Ic 555Document6 pages1 Ic 555Harish PatilNo ratings yet

- E.C.E - 210Document18 pagesE.C.E - 210xxkkassNo ratings yet

- Multivibrador Com Ci 555Document11 pagesMultivibrador Com Ci 555joselito1juniorNo ratings yet

- Introduction To 555 Timer ICDocument3 pagesIntroduction To 555 Timer ICSruthi ReddyNo ratings yet

- 3.1555 TIMER:: Schematic SymbolDocument10 pages3.1555 TIMER:: Schematic SymbolnagpradasNo ratings yet

- IC 555 Multivibrator CircuitsDocument11 pagesIC 555 Multivibrator CircuitsKaran YadavNo ratings yet

- Ic Applications Lab NewDocument12 pagesIc Applications Lab NewSandy RonaldoNo ratings yet

- N555e Intergrated CircuitDocument6 pagesN555e Intergrated CircuitGeorge Boman SethNo ratings yet

- 555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITDocument21 pages555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITRupsa SahaNo ratings yet

- IC 555 TimerDocument32 pagesIC 555 TimerAmaradi KondababuNo ratings yet

- University of Engineering and Technology, Lahore Department of Electrical EngineeringDocument5 pagesUniversity of Engineering and Technology, Lahore Department of Electrical EngineeringMuhammad SameerNo ratings yet

- University of Engineering and Technology, Lahore Department of Electrical EngineeringDocument5 pagesUniversity of Engineering and Technology, Lahore Department of Electrical EngineeringMuhammad SameerNo ratings yet

- The 555 Timer: Monostable Bistable AstableDocument10 pagesThe 555 Timer: Monostable Bistable AstableSrikanth ThulluriNo ratings yet

- Dsa 265104Document20 pagesDsa 265104foxx034No ratings yet

- 555 Timer ExplainedDocument27 pages555 Timer ExplainedThe Lost WolfNo ratings yet

- 555 TimerDocument3 pages555 TimerPraveen KumarNo ratings yet

- 4 555timer 120916082406 Phpapp02Document14 pages4 555timer 120916082406 Phpapp02sunil1237No ratings yet

- Bistable MultivibratorDocument28 pagesBistable MultivibratorMansi JaisinghNo ratings yet

- ME 455/555 - Lab 2 - 555 TimersDocument10 pagesME 455/555 - Lab 2 - 555 TimersGustavo KernNo ratings yet

- Opamp Applicationpart30Document31 pagesOpamp Applicationpart30KUNTALA DASNo ratings yet

- 555 Timer TutorialDocument12 pages555 Timer Tutorialrowell ramosNo ratings yet

- UNIT-4 Special Ics The 555 Timer IcDocument10 pagesUNIT-4 Special Ics The 555 Timer IcVerloves LoveNo ratings yet

- Introduction To IC 555 TimerDocument66 pagesIntroduction To IC 555 TimermuraliNo ratings yet

- 555 TimerDocument76 pages555 TimerSai Krishna KodaliNo ratings yet

- Monostable MultivibratorDocument4 pagesMonostable MultivibratorSakshi GosaviNo ratings yet

- Theory:The 555 Timer Configured For Monostable OperationDocument3 pagesTheory:The 555 Timer Configured For Monostable OperationkumararguruNo ratings yet

- Electronics Exercise 2: The 555 Timer and It's Applications: ObjectiveDocument5 pagesElectronics Exercise 2: The 555 Timer and It's Applications: ObjectiveMichael AjayiNo ratings yet

- Experiment No.4: FM Using 555 IcDocument3 pagesExperiment No.4: FM Using 555 IcSree DhanyaNo ratings yet

- 555 TimerDocument28 pages555 TimerNisha Kotyan G RNo ratings yet

- 555Document80 pages555elpasanteNo ratings yet

- 555 Timer PDFDocument76 pages555 Timer PDFronaldo19940% (1)

- Multi VibratorDocument6 pagesMulti VibratorAhie CherianNo ratings yet

- Ic 555Document25 pagesIc 555Ahmed SaȜed El-HadyNo ratings yet

- Integrated Circuits:) of Flip-Flop ThroughDocument13 pagesIntegrated Circuits:) of Flip-Flop ThroughShubh MishraNo ratings yet

- Module IV-Part 1 Astable and MonostableDocument39 pagesModule IV-Part 1 Astable and Monostablegowri thumburNo ratings yet

- Presentation On Ic 555 Timer: BY: Sandeep KumarDocument24 pagesPresentation On Ic 555 Timer: BY: Sandeep KumarSandeep Kamti BrzeeNo ratings yet

- 555 Timers Modi12Document21 pages555 Timers Modi12jewixe8466No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- 10 Manufacturers Hanover Trust Vs GuerreroDocument157 pages10 Manufacturers Hanover Trust Vs GuerreroChara GalaNo ratings yet

- Rizal Technological UniversityDocument5 pagesRizal Technological UniversityChara GalaNo ratings yet

- Aliasing: Aliasing Is An Effect That Causes Different Signals To Become Indistinguishable FromDocument6 pagesAliasing: Aliasing Is An Effect That Causes Different Signals To Become Indistinguishable FromChara GalaNo ratings yet

- Instrument Landing System Documantation1Document15 pagesInstrument Landing System Documantation1Chara GalaNo ratings yet

- Mongol Invasion in IndiaDocument4 pagesMongol Invasion in IndiaIsabella HannahNo ratings yet

- Functions of The InfinitiveDocument62 pagesFunctions of The InfinitiveАнгелина ПрибыльскаяNo ratings yet

- Eth Convert To Usdt - Google SearchDocument1 pageEth Convert To Usdt - Google SearchLily KoayNo ratings yet

- Inception Digest - 75 Days Plan For 44th BCS PreliminaryDocument7 pagesInception Digest - 75 Days Plan For 44th BCS Preliminaryদুর্জয় দুর্বারNo ratings yet

- Slinky GuideDocument24 pagesSlinky GuidepusicantonijeNo ratings yet

- VMStudy GuideDocument15 pagesVMStudy GuideSrinivas KumarNo ratings yet

- Robin Kuckyr Selling Your Accounting Practice NewsletterDocument16 pagesRobin Kuckyr Selling Your Accounting Practice NewsletterWard WichtNo ratings yet

- CG ProgrammingDocument429 pagesCG ProgrammingAdi Nouashcinci100% (1)

- How To Be A Pilot Junior WebDocument16 pagesHow To Be A Pilot Junior WebNextgen AviationNo ratings yet

- Cjmo 2023Document2 pagesCjmo 2023ferrousweiNo ratings yet

- AntidotesDocument29 pagesAntidotesjyothisahadevanNo ratings yet

- Chapter I IntroductionDocument17 pagesChapter I IntroductionAdnan MazariNo ratings yet

- Biology ProjectDocument14 pagesBiology ProjectfloraNo ratings yet

- Places in The Philippines That Are Prone To DangerDocument62 pagesPlaces in The Philippines That Are Prone To DangerSavion Sander AlinaNo ratings yet

- مشروع عبدالرحمن +زيدDocument15 pagesمشروع عبدالرحمن +زيدAbdulrahman AlsalawiNo ratings yet

- What Is The Difference Between A1, A2, B1 EtcDocument1 pageWhat Is The Difference Between A1, A2, B1 EtcGlory-Beast JrNo ratings yet

- Elmer TutorialsDocument152 pagesElmer TutorialsfabianoconbrasNo ratings yet

- Bay AniDocument6 pagesBay Aniphelenaphie menodiado panlilioNo ratings yet

- 3 Assumptions and ApproximationsDocument5 pages3 Assumptions and ApproximationsJack RyderNo ratings yet

- UntitledDocument6 pagesUntitledÂn LyNo ratings yet

- Research Paper Topics About Computer ProgrammingDocument8 pagesResearch Paper Topics About Computer ProgrammingyhclzxwgfNo ratings yet

- Ground Floor Plan: General NotesDocument1 pageGround Floor Plan: General NotesChaturbhuj Ikat FabricsNo ratings yet

- New City Catering PackageDocument1 pageNew City Catering PackageThirdy Quibranza SimanganNo ratings yet

- Individual Performance Commitment and Review (Ipcr) Form: DPWH Spms Form No.1ADocument2 pagesIndividual Performance Commitment and Review (Ipcr) Form: DPWH Spms Form No.1AMae Ann GonzalesNo ratings yet

- 05 Dislocation TheoryDocument37 pages05 Dislocation TheoryLuiz MaleckNo ratings yet

- Kabala Unveiled by Frater Aquarius (1933)Document190 pagesKabala Unveiled by Frater Aquarius (1933)Valerio777No ratings yet

- Introduction TitrationDocument30 pagesIntroduction TitrationlacaranjaredNo ratings yet

- 01 - Power System Protection-Basics and Breakers v2 (Revised) PDFDocument55 pages01 - Power System Protection-Basics and Breakers v2 (Revised) PDFJawwad Sadiq Ayon100% (1)