Professional Documents

Culture Documents

DLD2010

Uploaded by

Param Wasson0 ratings0% found this document useful (0 votes)

21 views1 pageCopyright

© Attribution Non-Commercial (BY-NC)

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

21 views1 pageDLD2010

Uploaded by

Param WassonCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 1

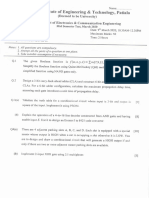

Krishna Institute of Management & Technology, Moradabad

2nd Sessional Examination (Odd Semester)2010-2009

Subject: Digital Logic Design Time Duration: 1.30 Hrs.

Subject Code: ECS-301 Max marks: 15

Branch / Section : CSE–IT / A-C

Note: Attempt any five Questions. (5X3)

Q1: Convert the RS flip flop to JK flip flop.

Q2: Derive the state table and state diagram for the sequential circuit shown in the figure below

Q3: A sequential circuit has one input and one output and its state diagram is shown in figure below

.Derive the sequential circuit using D flip flop.

Q4: Design Mod 4 counter using JK flip flop and implement it.

Q5: A Combinational circuit is define by the function s

F1= ∑m (1,5,7)

F2= ∑m(5,6,7)

Implement the circuit with a PLA.

Q6: Implement the following boolean expression using ROM.

F1(ABC) = ∑m(0,2,4,7) and F2(ABC)= ∑m(1,3,5,7).

Q7: Define a 4 bit shift register. Explain modes of operations of shift registers.

~~~~~~~~~~~(Best of Luck)~~~~~~~~~~~

You might also like

- CS433 hw1 Fall 07Document3 pagesCS433 hw1 Fall 0798140207No ratings yet

- Control System & PLC Old Qns PaperDocument4 pagesControl System & PLC Old Qns PaperJaya Rajesh RaajNo ratings yet

- DSM Eq 2022 NabDocument4 pagesDSM Eq 2022 NabnarendraNo ratings yet

- 9A15502 Digital System DesignDocument4 pages9A15502 Digital System Designsivabharathamurthy100% (1)

- Surya College of Business Management: End Semester Examination, (PGDM Ii Sem) SESSION 2012-2013Document4 pagesSurya College of Business Management: End Semester Examination, (PGDM Ii Sem) SESSION 2012-2013Mohd ImtiazNo ratings yet

- BCA (5) AssignmentDocument8 pagesBCA (5) AssignmentJijin JohnNo ratings yet

- Deld QB EndsemDocument4 pagesDeld QB EndsemUV New MoviesNo ratings yet

- Sathyabama University: Semester: IV Max - Marks: 80Document5 pagesSathyabama University: Semester: IV Max - Marks: 80GAURAVKINHANo ratings yet

- Principles of Computer Architecture and MaintenanceDocument2 pagesPrinciples of Computer Architecture and MaintenanceShilpa DasanNo ratings yet

- DE PaperDocument4 pagesDE Paperbhaveshgupta098No ratings yet

- Kannanalloor P.O Kollam: Name..................................Document2 pagesKannanalloor P.O Kollam: Name..................................Santhanu SurendranNo ratings yet

- 6C0065Document4 pages6C0065Joshua prabuNo ratings yet

- Answer All Questions: 4 Semester - B.E. / B.Tech Second Internal Assesment Test - March 2013Document2 pagesAnswer All Questions: 4 Semester - B.E. / B.Tech Second Internal Assesment Test - March 2013BIBIN CHIDAMBARANATHANNo ratings yet

- Structured Digital System Design Question PaperDocument1 pageStructured Digital System Design Question PaperSatish Bojjawar0% (1)

- Answer The Following 3 X2 6MDocument1 pageAnswer The Following 3 X2 6Mkrishna_marlaNo ratings yet

- Control Systems and PLC-sample-question-paper (Msbte-Study-Resources)Document5 pagesControl Systems and PLC-sample-question-paper (Msbte-Study-Resources)shubhampawaskar1313No ratings yet

- (3hours) : CompulsoryDocument7 pages(3hours) : CompulsorySaima ZainabNo ratings yet

- 3409Document5 pages3409Sohail AhmadNo ratings yet

- Test No: 2: Department of Electronics & Communication EngineeringDocument2 pagesTest No: 2: Department of Electronics & Communication EngineeringKishore KrishnaNo ratings yet

- Computer Hardware & MaintenanceDocument4 pagesComputer Hardware & MaintenancemanishkalshettyNo ratings yet

- Sns College of Technology: Reg NoDocument1 pageSns College of Technology: Reg NoAnonymous JnvCyu85No ratings yet

- Assembly 1stDocument3 pagesAssembly 1stawos80No ratings yet

- UEC612Document1 pageUEC612wizard01.2022No ratings yet

- (Answer ALL Questions) (Answer ALL Questions)Document1 page(Answer ALL Questions) (Answer ALL Questions)jubairNo ratings yet

- Exper-5 Karnaugh MapDocument3 pagesExper-5 Karnaugh MapMohammed Dyhia AliNo ratings yet

- Tutor Marked Assignment #1: The Open University of Sri LankaDocument8 pagesTutor Marked Assignment #1: The Open University of Sri LankaUditha MuthumalaNo ratings yet

- DCM-302 DIGITAL ELECTRONICS GRAND TEST-1 As On 19.09.2023Document2 pagesDCM-302 DIGITAL ELECTRONICS GRAND TEST-1 As On 19.09.2023Dhana lakshmiNo ratings yet

- R5 210204 Switching Theory & Logic DesignDocument1 pageR5 210204 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Sahyadri: College of Engineering & ManagementDocument1 pageSahyadri: College of Engineering & ManagementsaralabitmNo ratings yet

- 2012 Microprocessor & Microcontroller: CS/B.Tech (EE) (N) /SEM-5/EE-504C/2012-13Document4 pages2012 Microprocessor & Microcontroller: CS/B.Tech (EE) (N) /SEM-5/EE-504C/2012-13Aniruddha MondalNo ratings yet

- Question Bank For Mid-2 r13 (Vlsi) .Document6 pagesQuestion Bank For Mid-2 r13 (Vlsi) .rppvchNo ratings yet

- Unit-Wise Question Bank: 8M QuestionsDocument13 pagesUnit-Wise Question Bank: 8M Questionssivaranjani sivaranjaniNo ratings yet

- Ei2353:Digital System Design: Question BankDocument3 pagesEi2353:Digital System Design: Question BanknithyadeceNo ratings yet

- New Microsoft Word DocumentDocument2 pagesNew Microsoft Word Documentece gptplptNo ratings yet

- Bapatla Engineering College, BapatlaDocument6 pagesBapatla Engineering College, BapatlaKishan ChandNo ratings yet

- Embedded Internal 1 - 2 - Sets IV ECE CDocument2 pagesEmbedded Internal 1 - 2 - Sets IV ECE CjubairNo ratings yet

- Industrial Automation PDFDocument4 pagesIndustrial Automation PDFRohit Shinde RSNo ratings yet

- MSC Tech Indus MathsDocument135 pagesMSC Tech Indus MathsjayantbildaniNo ratings yet

- 1415 CMPE331 Logic Design Final-DDocument3 pages1415 CMPE331 Logic Design Final-DcNo ratings yet

- SDSD Question PaperDocument1 pageSDSD Question PaperSatish BojjawarNo ratings yet

- RT 21053112016Document4 pagesRT 21053112016RaunaqNo ratings yet

- PGDCMDocument18 pagesPGDCMMohit ChatapNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Narasus'S Sarathy Institute of Technology, Salem Internal Test - I (Common To ECE/EEE/IT)Document2 pagesNarasus'S Sarathy Institute of Technology, Salem Internal Test - I (Common To ECE/EEE/IT)Dhivya DuraisamyNo ratings yet

- Questions 4 1Document95 pagesQuestions 4 1Anik PaulNo ratings yet

- Datta Meghe Institute of Engineering, Technology & Research, Sawangi (M), Wardha Assignment No.2Document3 pagesDatta Meghe Institute of Engineering, Technology & Research, Sawangi (M), Wardha Assignment No.2Lukesh BarapatreNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- MP Lab ManualDocument51 pagesMP Lab ManualdevirpasadNo ratings yet

- Principles of Digital Techniques On Web PDFDocument5 pagesPrinciples of Digital Techniques On Web PDFmdwalunjkar3095No ratings yet

- Digital ElectronicsDocument2 pagesDigital ElectronicsVaso RanaNo ratings yet

- It 2354Document1 pageIt 2354Nijin VinodNo ratings yet

- CSC520 - Test 1 - Answer SchemeDocument3 pagesCSC520 - Test 1 - Answer SchemeAl Firdauz100% (1)

- Computer & Network TechnologyDocument4 pagesComputer & Network TechnologyJessica TiffanyNo ratings yet

- HT TP: //qpa Pe R.W But .Ac .In: 2012 Microprocessor & MicrocontrollerDocument7 pagesHT TP: //qpa Pe R.W But .Ac .In: 2012 Microprocessor & MicrocontrollerAbhishek DasNo ratings yet

- Vaigai College of Engineering: Therkutheru, Melur (TK), Madurai - 625122Document4 pagesVaigai College of Engineering: Therkutheru, Melur (TK), Madurai - 625122Rajesh LingamNo ratings yet

- Bfm2313-Digital Electronics 11213Document4 pagesBfm2313-Digital Electronics 11213MysteryNo ratings yet

- HT TP: //qpa Pe R.W But .Ac .In: 2013 Computer NetworksDocument7 pagesHT TP: //qpa Pe R.W But .Ac .In: 2013 Computer NetworksNitin NileshNo ratings yet

- Illinois Exam2 Practice Solfa08Document4 pagesIllinois Exam2 Practice Solfa08bittronicNo ratings yet

- Krishna Institute of Management & Technology Moradabad: Total Marks: 15Document1 pageKrishna Institute of Management & Technology Moradabad: Total Marks: 15Param WassonNo ratings yet

- Cover LetterDocument1 pageCover LetterParam WassonNo ratings yet

- EDocument1 pageEParam WassonNo ratings yet

- GraphicsDocument2 pagesGraphicsParam WassonNo ratings yet

- Cover LetterDocument1 pageCover LetterParam WassonNo ratings yet

- MySQL Terminal CommandsDocument1 pageMySQL Terminal CommandsParam WassonNo ratings yet

- New Text DocumentDocument1 pageNew Text DocumentParam WassonNo ratings yet

- AssignmentDocument2 pagesAssignmentParam WassonNo ratings yet

- Following Paper ID and Roll No. To Be Filled in Your Answer Book)Document3 pagesFollowing Paper ID and Roll No. To Be Filled in Your Answer Book)Param WassonNo ratings yet

- Salient Features of Jan Lokpal Bill (New)Document1 pageSalient Features of Jan Lokpal Bill (New)Param WassonNo ratings yet

- Direct Recruitment-4 18112010Document10 pagesDirect Recruitment-4 18112010topotopNo ratings yet